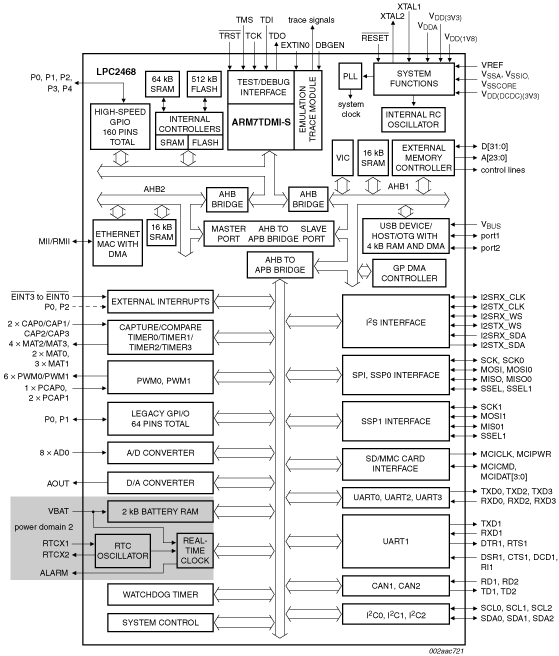

恩智浦采用16位/32位Arm7TDMI-S™ CPU内核设计LPC2468微控制器,搭载实时调试接口,同时包含JTAG和嵌入式跟踪。LPC2468拥有一个512 kB片上高速Flash存储器。该Flash存储器包括一个特殊的128位宽度存储接口和加速架构,使得CPU可以执行Flash存储器中的顺序指令,其系统时钟速率最高可达72 MHz。该功能仅在LPC2000 Arm®系列微控制器产品上提供。LPC2468可执行32位Arm和16位Thumb指令。支持两种指令集意味着工程师可以选择在子程序的水平上优化应用程序的性能或代码大小。当内核在Thumb状态下执行指令时,能够以很小的性能损失换取超过30%的代码压缩,而在Arm状态下执行指令时,则可最大限度地提高内核性能。

LPC2468微控制器是多用途通信应用的理想选择。它集成了1个10/100M以太网媒体访问控制器(MAC)、1个带4 KB端点RAM的USB全速设备/主机/OTG控制器、4个UART、2个控制器局域网络(CAN)通道、1个SPI接口、2个同步串行端口(SSP)、3个I²C接口,以及1个I²S接口。这种串行通信接口的集合支持以下功能部件:一个片上4 MHz内部精密振荡器;总大小98 KB的RAM,包含64 KB本地SRAM、16 KB以太网SRAM、16 KB通用DMA SRAM和2 kB电池供电SRAM;以及一个外部存储器控制(EMC)。这些特性使得该器件最适用于通信网关和协议转换器。作为很多串行通信控制器,通用定时功能和存储功能的补充,它还拥有各种32位定时器、一个改进的10位ADC和10位DAC、2个PWM单元、4个外部中断引脚,以及多达160个通用IO线路。LPC2468将64个GPIO引脚与基于硬件的矢量中断控制器(VIC)连接,这意味着外部输入可以产生边沿触发的中断。所有这些特性使得LPC2468特别适用于工业控制和医疗系统应用。