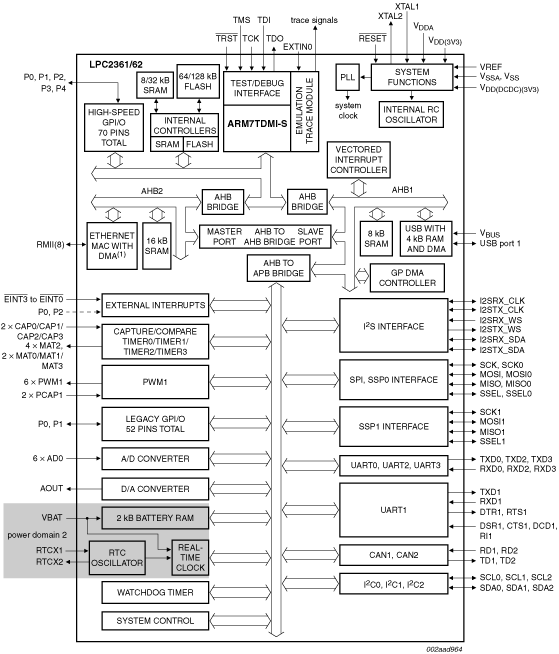

LPC2361/2362微控制器基于16位/32位Arm7TDMI-S™ CPU,其实时仿真功能将该微控制器与高达128KB的嵌入式高速Flash存储器结合在一起。128位宽存储器接口和独特的加速器架构能以最大时钟速率执行32位代码。在中断服务例程和DSP算法的关键性能上,它在Thumb模式下的性能最高可提升30%。对于代码大小攸关的应用程序,备用16位Thumb模式可用最小的性能损失换取超过30%的代码压缩。

LPC2361/2362是多用途串行通信应用的理想之选。产品集成10/100M以太网媒体访问控制器(MAC) (仅限LPC2362)、带4 KB端点RAM的USB全速设备、4个UART、2个CAN通道、1个 SPI接口、2个同步串行端口(SSP)、3个I²C接口,以及1个I²S接口。这种混合串行通信接口结合片上4 MHz内部振荡器、高达32 KB的SRAM、用于以太网的16 KB SRAM、用于USB和通用应用的8 KB SRAM,以及一个2 KB电池供电SRAM,使得这些器件非常适合通信网关和协议转换器。各种32位定时器、1个改进的10位ADC、10位DAC、1个PWM单元、1个CAN控制单元、最多70个快速通用IO线路,配合多达12个边沿或电平敏感型外部中断引脚,以上特性使得这些微控制器特别适合工业控制和医疗系统。