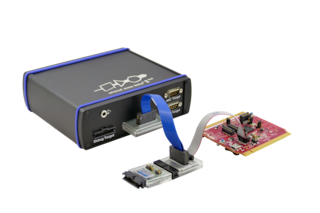

设计文件

2 设计文件

-

模型

BSDL for LPC18xx and LPC43xx

-

符号和尺寸

LPC43xx/LPC18xx Eagle symbols

The LPC18S37JBD144 is a Arm Cortex-M3 based microcontroller for embedded applications. The Arm Cortex-M3 is a next generation core that offers system enhancements such as low power consumption, enhanced debug features, and a high level of support block integration.

The LPC18S37JBD144 operates at CPU frequencies of up to 180 MHz. The Arm Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals. The Arm Cortex-M3 CPU also includes an internal prefetch unit that supports speculative branching.

The LPC18S37JBD144 includes 1 MB of flash and 136 kB of on-chip SRAM, 16 kB of EEPROM memory, a quad SPI Flash Interface (SPIFI), a State-configurable Timer/PWM (SCTimer/PWM) subsystem, two High-speed USB controllers, Ethernet, an external memory controller, and multiple digital and analog peripherals.

部件编号包含: LPC18S37JBD144.

快速参考 文档类别.

1-5 / 13 文件

安全文件正在加载,请稍等

2 设计文件

安全文件正在加载,请稍等

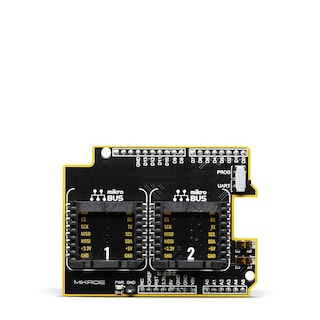

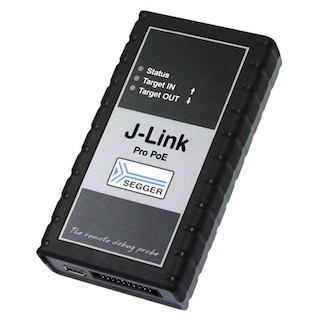

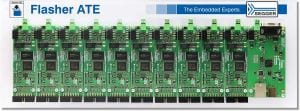

1-5 / 7 硬件

其他可用硬件. 查看我们的精选合作伙伴解决方案.

1-5 / 23 硬件

查找支持此产品的所有合作伙伴,请参阅 合作伙伴市场.

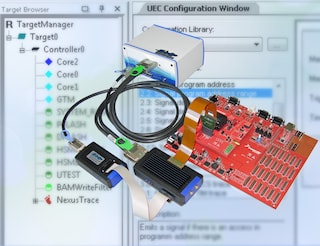

1-5 / 6 软件文件

可访问其他软件。 查看我们的精选合作伙伴解决方案.

注意: 推荐在电脑端下载软件,体验更佳。

安全文件正在加载,请稍等

1-5 / 47 软件产品

查找支持此产品的所有合作伙伴,请参阅 合作伙伴市场.

1-5 / 6 工程服务

There are no results for this selection.

查找支持此产品的所有合作伙伴,请参阅 合作伙伴市场.