Building on NXP Semiconductors's continued innovation and performance leadership in the high-performance host processor market, the MPC7457 achieves two major milestones in the embedded world: It delivers 1.3 GHz of performance—making it Our fastest processor available for embedded applications. It also dissipates less than 10W while running at 1 GHz—a critical threshold for many power-sensitive embedded designs.

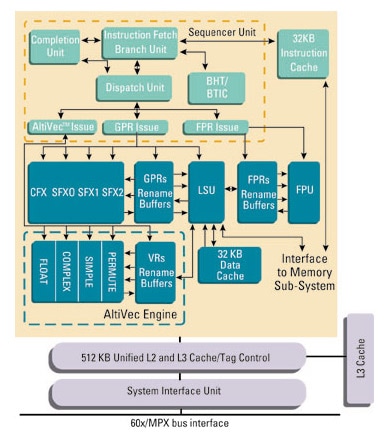

The MPC7457 host processor is a high-performance, low-power 32-bit implementation of the RISC architecture with a full 128-bit implementation of Our AltiVec

®™ technology. Delivering a high level of performance with efficient power consumption across virtually all speeds, this innovative processor built on Power Architecture technology provides networking and computing product OEMs with a great solution for a wide range of host processor applications—including high-performance network infrastructure and telecommunications equipment, computing products and embedded systems.

Offered in a 483-pin CBGA package, the MPC7457 processor is footprint-compatible with Our award-winning MPC7455/45 processors, providing an easy migration path for OEMs seeking higher performance for their new or existing Power Architecture processor-based applications. The MPC7457 can reach speeds of 1.3 GHz with a core voltage of 1.3V and includes 512KB of on-chip L2 cache (a 2X increase over the MPC7455's L2 cache), with support for up to 2MB of backside L3 cache. A lower-power version of the MPC7457 is available, operating at speeds of up to 1 GHz with a core voltage of 1.0V.

The MPC7457 is manufactured on Our 0.13-micron HiPerMOS silicon-on-insulator (SOI) copper interconnect process technology, enabling it to deliver superior performance over bulk CMOS technology. In addition to increased performance, SOI technology offers excellent low power capability, making the devices ideal for embedded applications in the wired and wireless telecommunications, networking and imaging arenas.

In addition to achieving a new clock speed milestone, the MPC7457 processor offers the following features designed to optimize performance and functionality in embedded applications:

-

AltiVec™ technology

— All members of Our G4 family of processors include a full 128-bit implementation of Our advanced AltiVec Single Instruction Multiple Data (SIMD) vector processing technology. AltiVec technology allows designers to leverage existing code and add AltiVec performance as market and customers' requirements change—helping speed time-to-market and increase system performance without upgrading hardware.

-

Block address translation (BAT) registers

— The MPC7457 offers 8 instruction BAT and data BAT registers to support efficient embedded operating systems through high-speed mapping of additional large blocks of data.

-

Cache locking

— The L1 cache supports cache way locking, allowing key performance algorithms and code to be locked in the L1 cache.

-

L3 cache support

— Continued support of the L3 cache on the MPC7457 helps ensure system compatibility for customers of Our MPC745x processor products.

-

Full symmetric multiprocessing (SMP) support

— SMP capability enables customers to achieve significantly higher system performance by scaling their embedded system designs with multiple NXP processors.