产品简介 (1)

-

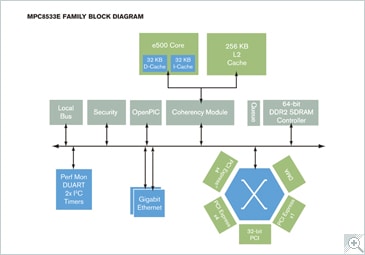

MPC8533E Product Brief[MPC8533EPB]亮点

参考手册 (5)

-

PowerPC ™ e500 Core Family - Reference Manual[E500CORERM]

-

MPC8533E Reference Manual[MPC8533ERM]亮点

封装信息 (2)

-

MPC8544E and MPC8533E Thermal Simulation Report and Models[MPC8544FLOTHERM]

应用笔记 (28)

-

恩智浦微控制器故障排除清单[AN13461]

-

Understanding SYSCLK Jitter[AN4056]

-

PowerQUICC®™ UPM Configuration[AN2810]

-

PowerQUICC™ Data Cache Coherency[AN3544]

应用笔记软件 (4)

支持信息 (2)

数据手册 (1)

白皮书 (4)

-

Understanding Cryptographic Performance[CRYPTOWP]

-

Comparison of DDRx and SDRAM[DDRSDRAMWP]

-

Understanding Public-Key Performance[PUBLICKEYPERFWP]

简介 (2)

-

MPC8533E Application Summary[MPC8533EAS]

-

MPC8533E Fact Sheet[MPC8533EFS]亮点