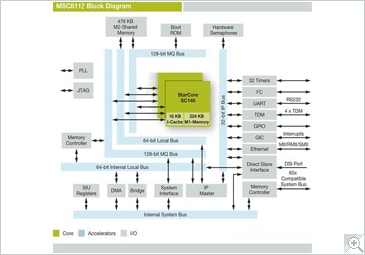

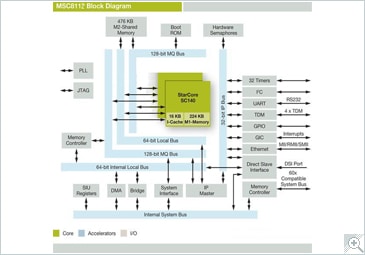

The MSC8112 is a highly integrated system-on-chip that combines two StarCore® SC140 extended cores with a RS-232 serial interface, four time division multiplexed (TDM) serial interfaces, 32 general-purpose timers, a flexible system interface unit (SIU), an Ethernet interface and a multi-channel DMA controller. The two extended cores can deliver a total 2400 DSP MMACS performance at 300 MHz.

Each core has four arithmetic logic units (ALUs), internal memory, a write buffer and two interrupt controllers. The MSC8112 targets high-bandwidth highly computational DSP applications and is optimized for wireless transcoding and packet telephony as well as high-bandwidth base station applications. The MSC8112 delivers enhanced performance while maintaining low-power dissipation and greatly reduces system cost.

The MSC8112 device is designed to provide an optimal solution for 3G wireless base stations to help eliminate many of the costly and power-hungry ASICs and FPGAs required in today's systems for both symbol rate and for chip rate assist. In addition, the MSC8112 allows you to add next-generation features that efficiently use available frequencies and higher bit rates in 3G systems.

Efficient application software development is key in Our strategy to expedite your time-to-market. Developers have access to development tools and real-time operating systems (RTOS) from NXP® and third-party suppliers. NXP partners with third-party vendors to provide integrated systems solutions that include GSM, CDMA, TDMA, and ITU G.7xx speech coders, hybrid echo cancellation, fax, modem and xDSL software.