# **MSC8112 Design Checklist**

This application note provides a set of recommendations to assist you in a first-time design with the MSC8112 device. This document can also be useful as a general guideline for designing new systems because it highlights the aspects of a design that merit special attention during initial system start-up.

### 1 Getting Started

During the first phase of designing a system with the MSC8112 device, your main tasks are to make the pin assignments and configure the reset parameters. Before you get started, you should be familiar with the available documentation, silicon revisions, software, models, and tools. Refer to **Section 9**, *Related Reading*, on page 18.

### CONTENTS

| 1   | Getting Started                         | 1  |

|-----|-----------------------------------------|----|

| 1.1 | Pin Assignments                         |    |

| 1.2 | Configuring Reset Parameters            |    |

| 2   | Power                                   | 5  |

| 3   | Clocks                                  | 5  |

| 4   | Reset                                   | 6  |

| 4.1 | Power-On-Reset Circuit                  | 6  |

| 4.2 | Reset Configuration Pins                | 6  |

| 4.3 | Boot                                    | 7  |

| 5   | Bit and Byte Lane Ordering              | 8  |

| 6   | Memory                                  | 10 |

| 6.1 | 60x Bus Signals and Memory Transactions |    |

| 6.2 | BADDRx in 60x Mode                      | 10 |

| 6.3 | Bank Selects Versus Address Lines       | 11 |

| 6.4 | Bank Versus Page Interleaving           | 11 |

| 7   | EOnCE/JTAG Interface                    |    |

| 8   | Signal Terminations                     | 13 |

| 9   | Related Reading                         |    |

### 1.1 Pin Assignments

Some MSC8112 pins are multiplexed, depending on the device programming. Take care in programming MSC8112 registers to configure these multiplexed pins as needed for your system design. A signal function should be routed to a single pin, so any other pins providing that signal functionality should have it turned off. Pin multiplexing is configured in the following registers:

- Hard Reset Configuration Word (HRCW)

- SIU module configuration register (SIUMCR)

- Memory controller registers ORx and BRx

- GPIO port registers.

Some signals have one function during reset but switch to another multiplexed function during regular operation. These signals include SWTE, DSISYNC, DSI64, MODCK[1–2], and CNFGS. These signals switch to DSI functionality after the system exits the reset state.

**Table 1** shows an overview of the multiplex options for the TDM interface, DSI bus, system bus, and Ethernet controller. The pins are chosen based on the settings of the DSI reset configuration pin, the ETHSEL bit in the Hard Reset Configuration Word, and the EN and IFMODE bits in the Ethernet MIIGSK configuration registers. There are two options for the location of the Ethernet pins: exposed on the low part of the DSI/system bus or exposed on the GPIO pins. Even though the pins are repeated in each option, the options cannot be mixed. All Ethernet pins must be from the DSI/system bus or from the GPIO pins. You cannot choose some of the Ethernet pins from the DSI/system bus and the others from the GPIO pins. The SMII mode of the Ethernet controller is available only on the GPIO pins. **Table 1** also indicates which TDMs are available on the GPIO pins when the different Ethernet options are chosen.

| Configuration           |                  |                    |                         |                   |                  | Pins                   |                                  |                             |

|-------------------------|------------------|--------------------|-------------------------|-------------------|------------------|------------------------|----------------------------------|-----------------------------|

| DSI64<br>(Reset<br>Pin) | ETHSEL<br>(HRCW) | EN<br>(MIIGSK_ENR) | IFMODE<br>(MIIGSK_CFGR) | TDMs<br>Available | DSI Bus<br>Width | System<br>Bus<br>Width | Ethernet on<br>DSI/System<br>Bus | Ethernet<br>on GPIO<br>Pins |

| 0                       | 0                | 0                  | хх                      | 0,1,2,3           | 32 bit           | 64 bit                 | —                                | _                           |

| 0                       | 0                | 1                  | 00                      | 0,1               | 32 bit           | 64 bit                 | —                                | MII                         |

| 0                       | 0                | 1                  | 10                      | 0,1,3             | 32 bit           | 64 bit                 | —                                | RMII                        |

| 0                       | 0                | 1                  | 01                      | 0,1,3             | 32 bit           | 64 bit                 | —                                | SMII                        |

| 0                       | 1                | 0                  | хх                      | 0,1,2,3           | 32 bit           | 32 bit                 | —                                | —                           |

| 0                       | 1                | 1                  | 00                      | 0,1,2,3           | 32 bit           | 32 bit                 | MII                              | —                           |

| 0                       | 1                | 1                  | 10                      | 0,1,2,3           | 32 bit           | 32 bit                 | RMII                             | —                           |

| 0                       | 1                | 1                  | 01                      | 0,1,2,3           | 32 bit           | 32 bit                 | —                                | —                           |

| 1                       | 0                | 0                  | хх                      | 0,1,2,3           | 64 bit           | 32 bit                 | —                                | —                           |

| 1                       | 0                | 1                  | 00                      | 0,1               | 64 bit           | 32 bit                 | _                                | MII                         |

| 1                       | 0                | 1                  | 10                      | 0,1,3             | 64 bit           | 32 bit                 | —                                | RMII                        |

| 1                       | 0                | 1                  | 01                      | 0,1,3             | 64 bit           | 32 bit                 | —                                | SMII                        |

| 1                       | 1                | х                  | хх                      | 0,1,2,3           | 64 bit           | 32 bit                 |                                  | —                           |

|  | Table 1. | Multiplexing | Overview |

|--|----------|--------------|----------|

|--|----------|--------------|----------|

### **1.2 Configuring Reset Parameters**

Review the HRCW to determine initial power-on-reset parameters, such as single MSC8112 bus mode versus 60x–compatible bus mode, boot port size, and on, and then set the bits for your application (see **Table 2**).

| Name                 | Reset | Description                                                                                                                                          |                      | Settings                                                                                                                                                                         |

|----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>EARB</b><br>0     | 0     | External Arbitration<br>Defines the initial value for ACR[EARB].                                                                                     | 0<br>1               | Internal arbitration is performed.<br>External arbitration is assumed.                                                                                                           |

| <b>EXMC</b><br>1     | 0     | <b>External MEMC</b><br>Defines the initial value of BR0[EMEMC].                                                                                     | 0<br>1               | No external memory controller is<br>assumed.<br>External memory controller is<br>assumed.                                                                                        |

| INTOUT<br>2          | 0     | <b>INT_OUT or IRQ7 Selection</b><br>Defines the initial value of SIUMCR[INTOUT].                                                                     | 0<br>1               | IRQ7/INT_OUT is IRQ7.<br>IRQ7/INT_OUT is INT_OUT.                                                                                                                                |

| <b>EBM</b><br>3      | 0     | External 60x-compatible Bus Mode<br>Defines the initial value of BCR[EBM].                                                                           | 0<br>1               | Single MSC8122 bus mode.<br>60x-compatible bus mode.                                                                                                                             |

| <b>BPS</b><br>4–5    | 00    | <b>Boot Port Size</b><br>Defines the initial value of BR0[PS], the port size<br>for memory controller bank 0.                                        | 00<br>01<br>10<br>11 | 64-bit port size.<br>8-bit port size.<br>16-bit port size.<br>32-bit port size.                                                                                                  |

| SCDIS<br>6           | 0     | SC140 Cores Disabled<br>Enables/disables the SC140 cores.                                                                                            | 0<br>1               | SC140 cores enabled.<br>SC140 cores disabled.                                                                                                                                    |

| ISPS<br>7            | 0     | Internal Space Port Size<br>Defines the initial value of BCR[ISPS]. Setting<br>ISPS enables a 32-bit master to access the<br>MSC8122 internal space. | 0                    | MSC8122 acts as a 64-bit slave to<br>external masters access to its<br>internal space.<br>MSC8122 acts as a 32-bit slave to<br>external masters access to its<br>internal space. |

| IRPC<br>8            | 0     | Interrupt Pin Configuration<br>Defines the initial value of SIUMCR[IRPC].                                                                            | 0<br>1               | IRQ2, IRQ3, IRQ5 active.<br>BADDR29, BADDR30, BADDR31<br>active.                                                                                                                 |

| 9                    | 0     | Reserved. Cleared to zero for future compatibility                                                                                                   | '.<br>'              |                                                                                                                                                                                  |

| <b>DPPC</b><br>10–11 | 00    | <b>Data Parity Pin Configuration</b><br>Defines the initial value of SIUMCR[DPPC].                                                                   | 00<br>01<br>10<br>11 | IRQ[1-7] active.         DP[0-7] active.         DREQ[1-4], DACK[1-4] active.         EXT_BR[2-3], EXT_BG[2-3],         EXT_DBG[2-3], and IRQ[6-7] active.                       |

| <b>NMI OUT</b><br>12 | 0     | <b>NMI OUT</b><br>Defines whether the host or one of the SC140<br>cores handles a non-maskable interrupt (NMI)<br>event.                             | 0<br>1               | NMIis serviced by SC140 cores.NMIis routed to NMI_OUT andserviced by the external host.                                                                                          |

Table 2.

Hard Reset Configuration Word (HRCW)

| Name         Reset         Description |       |                                                                                                                                                                                                                                                                                                                                                                |                                                      | ,                                                                                                                                                                                        |

|----------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                   | Reset | Description                                                                                                                                                                                                                                                                                                                                                    |                                                      | Settings                                                                                                                                                                                 |

| <b>ISBSEL</b><br>13–15                 | 000   | <b>Initial Internal Space Base Select</b><br>Defines the initial value of IMMR[ISB], which<br>determines the base address of the internal<br>memory space. The SC140 internal address<br>space spans from 0x0000000–0x00FFFFF<br>(16 MB). Therefore it is not advisable to map the<br>IMMR in this space, since the SC140s cannot<br>access the SIU registers. | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 0xF0000000.<br>0xF0F000000.<br>0xFF000000.<br>0xFFF00000.<br>Reserved. This option should not be<br>used.<br>Reserved. This option should not be<br>used.<br>0x0F000000.<br>0x0FF000000. |

| <b>BBD</b><br>17                       | 0     | Bus Busy Disable<br>Defines the initial value of SIUMCR[BBD].                                                                                                                                                                                                                                                                                                  | 0<br>1                                               | ABB, DBB active.<br>IRQ[4–5] active.                                                                                                                                                     |

| <b>MMR</b><br>18                       | 0     | Mask Masters Requests<br>Defines the initial value of SIUMCR[MMR].                                                                                                                                                                                                                                                                                             | 0<br>1                                               | No masking on bus request lines.<br>All external bus requests masked<br>(boot master is the one of the internal<br>cores).                                                               |

| ETHSEL<br>19                           | 0     | Ethernet Select<br>Defines whether the Ethernet is exposed on the<br>low part of the DSI/60x data bus lines (when<br>ETHSEL is set and the DSI64 line is sampled<br>low at reset) or the GPIO lines (when ETHSEL is<br>clear).                                                                                                                                 |                                                      |                                                                                                                                                                                          |

| <b>TTPC</b> 20                         | 0     | Transfer Type Pin Configuration<br>Defines the initial value of SIUMCR[TTPC].                                                                                                                                                                                                                                                                                  | 0<br>1                                               | TT[0, 2–4] active.<br>$\overline{CS[5-7]}$ active.                                                                                                                                       |

| <b>CS5PC</b><br>21                     | 0     | Chip Select 5 Pin Configuration<br>Defines the initial value of SIUMCR[CS5PC].                                                                                                                                                                                                                                                                                 | 0<br>1                                               | CS5 active.<br>BCTL1 active.                                                                                                                                                             |

| <b>TCPC</b><br>22–23                   | 0     | Transfer Code Pin Configuration<br>Defines the initial value of SIUMCR[TCPC].                                                                                                                                                                                                                                                                                  | 00<br>10                                             | TC[0–2] active.<br>BNKSEL[0–2] active.                                                                                                                                                   |

| LTLEND<br>24                           | 0     | Little Endian<br>Defines the host Endian mode of operation.                                                                                                                                                                                                                                                                                                    | 0<br>1                                               | Big-Endian.<br>Little-Endian.                                                                                                                                                            |

| PPCLE<br>25                            | 0     | <b>Munged Little Endian</b><br>When the LTLEND bit is set, PPCLE specifies<br>whether the host is a Little-Endian host or a host<br>that works in Munged Little-Endian mode.                                                                                                                                                                                   | 0<br>1                                               | True Little-Endian host.<br>Munged Little-Endian host.                                                                                                                                   |

| <br>26                                 | 0     | Reserved. Cleared to zero for future compatibility                                                                                                                                                                                                                                                                                                             | •                                                    |                                                                                                                                                                                          |

| 27                                     | 1     | Reserved. Must be set to 1.                                                                                                                                                                                                                                                                                                                                    |                                                      |                                                                                                                                                                                          |

| <b>MODCK[3–5]</b><br>28–30             | 0     | <b>MODCK High Order Bits</b><br>High-order bits of the MODCK bus, which<br>determine the clock reset configuration. Refer to<br>the chapter on clocks in the MSC8112<br><i>Reference Manual.</i>                                                                                                                                                               |                                                      |                                                                                                                                                                                          |

|                                        | 0     | Reserved. Cleared to zero for future compatibility                                                                                                                                                                                                                                                                                                             | •                                                    |                                                                                                                                                                                          |

Table 2.

Hard Reset Configuration Word (HRCW) (Continued)

### 2 Power

This section outlines the MSC8112 power supply and power consumption considerations. For information on AC/DC electrical specifications, thermal characteristics, start-up, and power sequencing, refer to the data sheet.

• *Power supply*. The MSC8112 has a core voltage,  $V_{DD}$ , that operates at a lower voltage than the I/O voltage  $V_{DDH}$ . You should supply the MSC8112 core voltage  $V_{DD}$  via a variable power supply (switching supply or regulator) to allow for future compatibility with possible core voltage changes on future silicon revisions. The core voltage is supplied across  $V_{DD}$  and  $V_{SS}$  (GND). The core supply voltage must be between 1.07 V and 1.13 V.

The I/O section of the MSC8112 is supplied with 3.3 V ( $\pm$  5%) across V<sub>DDH</sub> and V<sub>SS</sub> (GND). Typically, this voltage is supplied by a simple linear regulator, which increases system complexity because multiple power supplies are required for the design. External signals on the MSC8112 are not 5 V tolerant. All input signals must meet the V<sub>IN</sub> DC spec (-0.2 V to V<sub>DDH</sub> + 0.2). After the power-up sequence, V<sub>DDH</sub> must not exceed V<sub>DD</sub>/V<sub>CCSYN</sub> by more than 2.6 V. For details on power supply design considerations, consult the MSC8112 *Technical Data* sheet and the application note entitled *MSC8122* and *MSC8126 Power Circuit Design Recommendations and Examples* (AN2937).

- *Power consumption.* The MSC8112 *Technical Data* sheet provides preliminary power dissipation estimates for various configurations. You can take the following steps to reduce power consumption in your design:

- Stop mode for SC140 cores. Any SC140 core can be placed into Stop mode when it is not in use. However, the core can be taken out of Stop mode only through a device reset such as PORESET, HRESET, or SRESET.

- Wait mode for SC140 cores. Any SC140 core can be placed into Wait mode when it is not in use. The SC140 core exits Wait mode when there is an interrupt request as well as a reset or debug request.

- CLKOUT disable. If the system bus clock output is not needed in a system design, it can be

masked by setting the SIUMCR[CLKOD] bit. Masking the clock output not only reduces power

consumption but also noise in the design.

- Disable unused IP peripherals. All IP bus peripherals have a control bit to mask their clock. Any

unused peripherals should be programmed to Stop mode. For details, see the IPBus chapter of the

MSC8112 Reference Manual.

## 3 Clocks

All inputs and outputs except those associated with a serial clock are referenced to REFCLK. There are two modes for clock distribution, Back-Compatibility (with the MSC8102 device) and PLL Skew Elimination mode. PLL Skew Elimination is the recommended mode. In this mode, the REFCLK is CLKIN, which is clocked by an on-board oscillator. The clock mode is determined by the clock mode settings, as follows:

- *MODCK*[1–2]. The MODCK[1–2] pins are sampled at the rising edge of PORESET while HRESET is still asserted. Their value can be set using pull-ups/pull-downs. Therefore, open collector drivers are not needed.

- MODCK[3-5]. MODCK[3-5] can be set in the HRCW, or you can take the default value. Collectively, the MODCK[3-5] and MODCK[1-2] fields define the multiplication of the input clock (CLKIN) to derive the SC140 core and system bus clock ratios. Note that the SPLL multiplication value is set only during an initial HRESET caused by a PORESET, so the SPLL does not change during subsequent assertions of HRESET.

Refer to the MSC8112 Reference Manual for the most up-to-date clock configuration mode tables.

## 4 Reset

This section describes the reset recommendations for configuring the MSC8112 device at reset.

### 4.1 Power-On-Reset Circuit

There is no power-up detector on the MSC8112 device. Optionally, a power-on-reset chip to monitor the power plane and drive PORESET can be used. PORESET must be asserted externally for at least 16 CLKIN cycles after external power to the MSC8112 reaches nominal value.

$\overline{\text{HRESET}}$  is a bidirectional signal and, if driven as an input, should be driven with an open collector or open-drain device. For an open-drain output such as  $\overline{\text{HRESET}}$ , take care when driving many buffers that implement input bushold circuitry. The bus-hold currents can cause enough voltage drop across the pull-up resistor to change the logic level to low. Either a smaller value of pull-up or less current loading from the bus-hold drivers overcomes this issue. To avoid exceeding the MSC8112 output current, the pull-up value should not be too small (a 1 K $\Omega$  pull-up is used in the MSC8112ADS reference design).

**SRESET** is a bidirectional signal and, if driven as an input, should be driven with an open collector or open-drain device. The MSC8112 device drives **SRESET** if the **PORESET** line or the **HRESET** line is asserted. A software watchdog timeout, bus monitor timeout, JTAG reset, or external soft reset can also drive **SRESET**.

### 4.2 Reset Configuration Pins

The default HRCW (0x0000000) can be taken by connecting CNFGS to 0 and  $\overrightarrow{\mathsf{RSTCONF}}$  to a logic 1 on the rising edge of  $\overrightarrow{\mathsf{PORESET}}$ . In this case, no accesses are made to the PROM connected to  $\overrightarrow{\mathsf{CS0}}$ . The default case for the device is single MSC8112 mode. If the configuration word is not written via the 60x system bus during 1024 CLKIN cycles, the MSC8112 gets the default configuration word value.

Initial values other than the default can be obtained by selecting a different combination for the CNFGS and  $\overline{\text{RSTCONF}}$  pins.  $\overline{\text{BCTL0}}$  is active (functioning as W/R) during the HRCW write. Take care to avoid bus contention during this time if buffers on the board are under  $\overline{\text{BCTL0}}$  control.  $\overline{\text{BCTL1}}$  should not be used during the reset configuration procedure. **Table 3** shows the reset configuration mode options. For details, refer to the Reset chapter of the MSC8112 *Reference Manual*.

| CNFGS, RSTCONF | Reset Configuration Word Source                                          |

|----------------|--------------------------------------------------------------------------|

| 00             | Reset configuration via system bus. MSC8112 is the configuration master. |

| 01             | Reset configuration via system bus. MSC8112 is the configuration slave.  |

| 10             | Reset configuration via write through DSI.                               |

| 11             | Reserved.                                                                |

| Table 3. Reset Configuration Modes |

|------------------------------------|

|------------------------------------|

If both CNFGS and  $\overline{\text{RSTCONF}}$  are pulled to logic 0 on the rising edge of  $\overline{\text{PORESET}}$ , the MSC8112 device is a configuration master. The HRCW is read from the PROM connected to  $\overline{\text{CSO}}$  at addresses 0x00, 0x08, 0x10, and 0x18. These four bytes are written to the fields of the HRCW. The MSC8112 device can act as a configuration master to configure up to seven MSC810x configuration slaves by individually connecting the  $\overline{\text{RSTCONF}}$  lines of up to seven slaves to the most significant seven address bits of the configuration master address bus. The master continues to read bytes starting at 0x20, configures the next slave while driving the  $\overline{\text{RSTCONF}}$  line of the slave, and writes a 32-bit configuration word to that slave while the master drives the  $\overline{\text{HRESET}}$  asserted to the slave. This process is repeated from addresses 0x40, 0x60, 0x80, 0xA0, 0xC0, and 0xE0 for the remaining six slaves. The configuration master drives the full 32-bit configuration word on the 60x data bus after each 4-byte read from the PROM. Avoid any contention on the bus that would affect the configuration word. No pull-ups are required on the address bus because it is actively driven during this operation.

If CNFGS is logic 1 and RSTCONF is pulled to logic 0 on the rising edge of PORESET, the MSC8112 slave can be configured to receive the HRCW via the DSI. The host drives the HCID[0–3] signals to indicate which MSC8112 slave it is configuring. These signals can be driven by the host address lines. Alternatively, the host can write the HRCW to all MSC8112 slaves at once using the host broadcast chip select (HBCS). The MSC8112 slave remains in reset state until it receives its HRCW.

### 4.3 Boot

The MSC8112 boots from memory on the system bus, a host on the system bus, a host via the direct slave interface (DSI), or via the time-division multiplexing module (TDM), universal asynchronous receiver/transmitter (UART), or I<sup>2</sup>C ports. The boot source is determined by the state of the BM[0–2] signals sampled at the rising edge of PORESET (see **Table 4**).

| BM[0] | BM[1] | BM[2] | Boot Sequence                       |

|-------|-------|-------|-------------------------------------|

| 0     | 0     | 0     | External Memory on the system bus   |

| 0     | 0     | 1     | External host via DSI or system bus |

| 0     | 1     | 0     | TDM                                 |

| 0     | 1     | 1     | UART                                |

| 1     | 0     | 0     | I <sup>2</sup> C                    |

| 1     | 0     | 1     | Reserved                            |

| 1     | 1     | х     | Reserved                            |

| Table 4. | Boot Mode | e Settings |

|----------|-----------|------------|

|----------|-----------|------------|

### nd Byte Lane Ordering

The MSC8112 device boots from memory that is 8-, 16-, 32-, or 64-bits wide. When an internal memory controller is used, the memory should be attached to  $\overline{CS0}$ , which functions as the global boot select, and be of a type that the GPCM machine controls (EPROM or Flash memory). The HRCW[BPS] bit sets the width of the  $\overline{CS0}$  space. After configuration, SC140 core 0 fetches the address of the boot routine from location 0xFE000110.

If the MSC8112 device boots from a host via the DSI or 60x system bus interface, the host polls the BR10[V] bit to determine when the boot program is finished. The host then begins its initialization procedure by loading code and data to the MSC8112 device. Then it notifies the MSC8112 by sending VIRQ1 to SC140 core 0.

If the MSC8112 device boots via the TDM, the TDM boot master writes blocks of code and data into MSC8112 internal memory. The transaction requires the TDM physical layer to be set up and the TDM logical layer handshake to be implemented. The boot master transmits messages to a single MSC8112 or multiple MSC8112 devices on TDM channel 0. The MSC8112 slave devices transmit back to the host on the TDM channel associated with their CHIP\_ID. When the TDM session is complete, the valid bit of Bank 10 (BR10) is set to 1.

If the MSC8112 device boots from a UART device, a UART boot master writes blocks of code and data into MSC8112 internal memory. Like the TDM boot option, the transaction requires set up of the physical layer and a UART logical layer handshake. When the UART session is complete, the valid bit of Bank 10 (BR10) is set to 1.

If the MSC8112 device boots from an  $I^2C$  slave memory device, it retrieves blocks of code from an external  $I^2C$  device such as a serial EPROM. At the end of the  $I^2C$  process, all SC140 cores jump to address 0x0 of their M1 memory.

For the boot via TDM, UART, and I<sup>2</sup>C options, the boot code configures the GPIO pin multiplexing as required for external communication to boot in these modes. As a result, these GPIO configurations become the default pin multiplexing option for the affected signals. For details, see the "Boot Program" chapter of the MSC8112 *Reference Manual*.

## 5 Bit and Byte Lane Ordering

This section describes the system bus bit and byte lane ordering:

- *Address/data nomenclature*. It is recommended that schematics use documented terminology for the system bus as defined the chapter on "External Signals," in the MSC8112 *Technical Data* sheet.

- *System bus*. The highest-order address bit is A0. The lowest-order address bit is A[31]. All 32 address pins are valid in a byte access. In a 64-bit access, only the upper 29 A[0–28] address pins are valid, and A[29–31] are driven low. For the 60x data bus, the highest-order data bit is D0 and the lowest order data bit is D63.

- Data byte lane ordering. D[0–7] is the highest-order byte lane on the data bus, and D0 is the highest-order bit of that byte lane. D[0–7] corresponds to write enable 0 (PWE0) and byte lane select 0 (PSDDQM0). Table 5 provides the data byte lane ordering for both the system bus and local bus.

|                  |           | , ,                              |

|------------------|-----------|----------------------------------|

| Data Bus Signals | Byte Lane | External Pins (Byte Lane Select) |

| D[0-7]           | 0         | PWE0/PSDDQM0/PBS0                |

| D[8–15]          | 1         | PWE1/PSDDQM1/PBS1                |

| D[16–23]         | 2         | PWE2/PSDDQM2/PBS2                |

| D[24–31]         | 3         | PWE3/PSDDQM3/PBS3                |

| <b>Table 5.</b> 60x Bus Data Byte Lane Ordering |

|-------------------------------------------------|

|-------------------------------------------------|

| Data Bus Signals | Byte Lane | External Pins (Byte Lane Select) |

|------------------|-----------|----------------------------------|

| D[32–39]         | 4         | PWE4/PSDDQM4/PBS4                |

| D[40-47]         | 5         | PWE5/PSDDQM5/PBS5                |

| D[48–55]         | 6         | PWE6/PSDDQM6/PBS6                |

| D[56–63]         | 7         | PWE7/PSDDQM7/PBS7                |

Table 5.

60x Bus Data Byte Lane Ordering

• *Memory controller byte lanes*. The memory controllers can access memories that are 8-, 16-, 32-, and 64-bits wide without creating any "holes" in the memory space on the system bus. All memories should be placed into the most significant byte lanes as shown in **Table 6**.

| Memory Width      | Byte Lanes             |

|-------------------|------------------------|

| Byte (8-bits)     | 0                      |

| 2 Bytes (16-bits) | 0, 1                   |

| 4 Bytes (32-bits) | 0, 1, 2, 3             |

| 8 Bytes (64-bits) | 0, 1, 2, 3, 4, 5, 6, 7 |

Table 6. Byte Lanes for Memory Widths

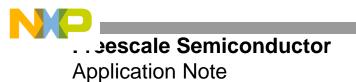

• *Flash Memory Devices*. The data lines of most Flash memory devices connect to the MSC8112 with byte lanes bit-reversed for programming algorithm purposes. A 32-bit example is shown in **Figure 1**. The figure is correct for a Flash SIMM composed of 8-bit Flash devices. Adjust the byte lanes as necessary for the memory in your design. The Flash memory interface requires a reset input that should connect to the MSC8112 PORESET.

Figure 1. MSC8112 to Flash Memory Byte Lane Reversal

Bringing up a board with blank Flash memory and no host processor requires a switch or other method to force  $\overline{\text{RSTCONF}}$  to a logic 1 and CNFGS to 0 to bring up the MSC8112 in the default state. Otherwise, invalid PLL values can be loaded. When the device comes out of reset in the default state, the Flash memory can be programmed. For subsequent resets, the  $\overline{\text{RSTCONF}}$  and CNFGS signals can be set appropriately for resetting from Flash memory.

## 6 Memory

This section provides design considerations for the MSC8112 associated memories.

### 6.1 60x Bus Signals and Memory Transactions

The MSC8112 is not 5 V tolerant. All input signals must meet  $V_{IN}$  DC Spec (-0.2 V to  $V_{DDH}$  + 0.2).

- Partial Data Valid. The memory controller drives PSDVAL for an access to an MSC8112-controlled resource (internal space or chip-selects). PSDVAL is used only by external devices that implement the MSC8112 memory bank-based bus sizing protocol (for example, an external MSC8112). Devices that do not implement this memory bank-based bus sizing do not use PSDVAL.

- *Non*-MSC8112 *masters*. MSC8112 designs incorporating devices that do not implement the MSC8112 memory bank-based bus sizing protocol must either use 64-bit accesses on the system bus or ensure that only MSC8112-initiated transactions can access the 8-, 16-, or 32-bit memory mapped slaves on the system bus.

- *Write enable*. PWE[0–7] should be used to control the R/W lines of memories, due to timing flexibility. For buffer direction control, the BCTL[0–1] signals should be used.

- *Pipelining*. The bus can be pipelined up to two address cycles deep. For example, it can have a TS, an AACK, and another TS before the first TA. Because the address is valid only during the address phase ending with AACK, external latches and multiplexes are necessary for SDRAM, and so on. On accesses to internal slaves, as well as SDRAM page hits, TA can come before AACK. In fact, AACK and TA are not guaranteed to be in order.

- *Single* MSC8112 *mode*. The bus operation is the same as for 60x bus mode, except that the address that is driven on A[0–31] is latched and possibly multiplexed inside the MSC8112. Therefore, the address is valid throughout the data phase of the cycle beginning with AACK and ending with the data phase of the next access. Single MSC8112 mode does not support mastering of the 60x system bus by any other resource, including an additional MSC8112 device.

- *Local bus*. The local bus does not burst when an external master accesses it through the 60x bus bridge. Accesses to the local bus are not snooped by the SC140 core.

- Bursts. Burst accesses by 60x masters to registers or to the local bus are terminated with  $\overline{TEA}$ .

- *Address acknowledge*. The MSC8112 asserts AACK for all accesses to external memory that match a BR/OR range in the memory controller and also drives TA unless programmed otherwise.

### 6.2 BADDRx in 60x Mode

In 60x-bus-compatible mode, the BADDR [27–31] pins must be used—not the standard address A[27–31] pins—to address memories when the GPCM and UPM machines are in use. This is necessary because 60x masters, including the internal SC140 core, do not dynamically adjust the transaction for bus size. The 60x masters drive only the starting address on a burst, and thus the address lines do not increment. The GPCM memory controller accesses the memory as single accesses. Both the GPCM and the UPM increment the BADDRx lines to gather the bytes that the 60x master requests. In single MSC8112 mode, the memory controllers drive the address lines for small port sizes and increments for bursts. Therefore, the BADDRx pins are not needed in this mode.

### 6.3 Bank Selects Versus Address Lines

In single MSC8112 mode, use the BNKSEL lines to interface to SDRAM to support different SDRAM densities without requiring board wiring changes. Also, use the BNKSEL lines and set the BCR[EAV] bit so that logic analyzers can view the nonmultiplexed address of the access.

### 6.4 Bank Versus Page Interleaving

Bank interleaving is the preferred method for connecting to SDRAM. To achieve the highest performance, the MSC8112 SDRAM machine provides an interface to SDRAMs using SDRAM pipelining, bank interleaving, and back-to-back reads or writes in page mode.

## 7 EOnCE/JTAG Interface

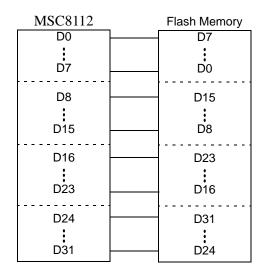

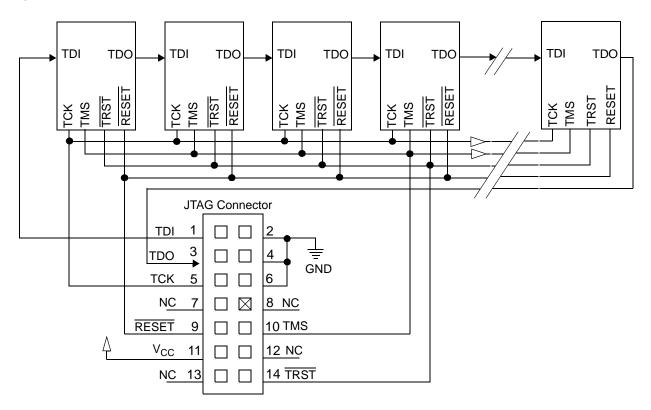

The MSC8112 device includes an Enhanced On-Chip Emulation module (EOnCE), a feature common to all Freescale processors with the SC140 core. EOnCE gives internal access to scan chains for debug purposes and also provides a serial connection to the SC140 core for emulator support. An EOnCE/JTAG connection adds little or no cost to a system but adds significant advantages during early system development. This interface is implemented using a standard 14-pin header as shown in **Figure 2**.

|          |      |      | -    |

|----------|------|------|------|

| TDI      | • 1  | 2 🌒  | GND  |

| TDO      | • 3  | 4 ●  | GND  |

| тск      | • 5  | 6 🔴  | GND  |

| NC       | • 7  | 8 🔴  | KEY  |

| RST      | • 9  | 10   | TMS  |

| $V_{DD}$ | • 11 | 12 🌒 | NC   |

| NC       | • 13 | 14   | TRST |

|          |      |      | 1    |

Figure 2. 14-Pin Header for JTAG/EOnCE Interface

The EOnCE interface connects through the JTAG port on the MSC8112 device with some additional status monitoring signals. **Table 7** shows the pin definitions and recommendations.

| Table 7. | JTAG/EOnCE Interface Pin Definitions |

|----------|--------------------------------------|

|----------|--------------------------------------|

| Pins    | Connection | Description           | Recommendations                                                                                                     |

|---------|------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| 1       | TDI        | Test Data In          | If there are multiple devices on the JTAG chain, connect TDI to the TDO signal of the previous device in the chain. |

| 2,4,6   | GND        | System Ground<br>Plan | Connect to digital ground.                                                                                          |

| 3       | TDO        | Test Data Out         | If there are multiple devices on the JTAG chain, connect TDO to the TDI signal of the next device in the chain.     |

| 5       | TCK        | Test Clock            | Add a 10 K $\Omega$ pull-down resistor.                                                                             |

| 7,13,12 | NC         | No Connect            | Leave unconnected.                                                                                                  |

| 8       | KEY        | Mechanical Keying     | Pin should be removed.                                                                                              |

| 9       | RST        | Reset                 | Can be tied to HRESET.                                                                                              |

| 10      | TMS        | Test Mode Select      | None.                                                                                                               |

| Pins | Connection      | Description      | Recommendations                                                                                                                                                                                                                                                                                                                             |

|------|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | V <sub>DD</sub> | I/O Power Supply | Connect to MSC8112 I/O Voltage $V_{DDH}$ through a 220 $\Omega$ current limiting resistor.                                                                                                                                                                                                                                                  |

| 14   | TRST            | Test Reset       | TRST has an internal pull-up, so no external pull-up or pull-down is required. However, it is recommended to add a 10 k pull-down to GND on this signal to keep the JTAG in reset mode while the device is operating normally. Asserting this signal asynchronously initializes the test controller. TRST must be asserted during power up. |

Table 7. JTAG/EOnCE Interface Pin Definitions (Continued)

Connecting multiple devices via their JTAG port is commonly called *daisy chaining*. Multiple target DSP devices can connect in series so that a single command converter and JTAG connector can control multiple target DSPs. Daisy chaining should be considered for a board with multiple DSPs. In a daisy chain configuration, such as that shown in **Figure 3**, a serial path is formed by the connection of the serial Test Data In (TDI) and Test Data Out (TDO) pins. Essentially, the path formed by TDI and TDO connects the JTAG registers of the devices serially. The input pin to the entire chain is TDI, and the output pin from the entire chain is TDO. The Test Clock (TCK) and Test Mode Select (TMS) pins of all the devices are wired in parallel so that there is a single TCK input and a single TMS input. In this configuration, if a device in the daisy chain is reset, all devices on the chain are reset because the RESET signals are connected.

Figure 3. Multiple Target DSP Connection

Since the MSC8112 is a multi-core device, each SC140 core has its own link on the JTAG chain. Therefore, when you are designing a daisy chain, remember that each MSC8112 device provides two indices to the chain. This is also important to remember when you are setting up JTAG chain initialization in software.

Connecting EE0 and EE1 to an additional header is recommended for debug boards. EE0 is used to enter debug mode and EE1 can be used for logic analyzer triggers and other useful debugging activities. Refer to the "Debugging" chapter of the MSC8112 *Reference Manual* for details.

## 8 Signal Terminations

**Table 8** summarizes the signal connections for the MSC8112. Refer to the data sheet for details on the connection guidelines:

- $xx-yy\Omega VDDH$ . A pull-up resistor to the V<sub>DDH</sub> power supply, with a value between xx and yy  $\Omega$ . You can select the value on the basis of system requirements, such as noise immunity.

- $xx-yy\Omega$  GND. A pull-down resistor to the ground power connection with a value between xx and yy  $\Omega$ . Again, you can specify the value.

- Open. The signal should/must be left unconnected. The Note column in **Table 8** specifies whether it is a requirement.

- As needed. The connection is determined principally by the system. It connects to the system controller logic, whether from Freescale or one of several third-parties who make such logic. If not designated, a pull-up should be between  $1K\Omega-10K\Omega$  and connected to  $V_{DDH}$  and a pull-down between  $100\Omega-1K\Omega$  and connected to GND.

Unused inputs should be tied high or low, but not left floating. Unused inputs can be tied directly to GND but a pull-up resistor is recommended if it is tied high. Generally, it is good practice to tie any unused input to GND or  $V_{DDH}$  through a resistor for board testability purposes.

The following signals are active during the reset configuration period of HRESET: A[0–31], BCTL0, BCTL1, D[0–63], CS0, POE, and BADDRx. All signals can be turned off using the HIGHZ JTAG command. Input-only signals such as PORESET or signals configured in an input-only mode, such as IRQx or EXT\_BRx, do not require pull-up/pull-down resistors if they are actively driven. However, in the interest of caution, pull-up resistors are recommended in **Table 8**. You should exercise discretion. The hard reset signal states provided do not include the states during reset configuration. During the assertion of PORESET, configurable signals have their default configuration (and are therefore tristated or high impedance). During reset configuration, configurable signals still have their default configuration, and certain memory controller signals operate to perform the reset configuration function (A[0–31], BCTL0, BCTL1, D[0–63], CS0, POE, BADDRx).

|                                                                                                                                                                                                                                                    |        |                       | State at                                     | Connection                  |                |                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|----------------------------------------------|-----------------------------|----------------|------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                    | Signal | Function <sup>1</sup> | Hard Reset                                   | If Used                     | lf Not<br>Used | Notes                                                                                    |

| <b>Notes:</b> I = input, O = output, B = bidirectional three-state, OD = open-drain. Most multi-function pins are bidirectional three-state. This does not imply that they are all shared signals—only that they can be used as inputs or outputs. |        |                       |                                              |                             |                |                                                                                          |

| BR                                                                                                                                                                                                                                                 |        | В                     | Tri-stated,<br>EARB = 0<br>High,<br>EARB = 1 | 1–10 ΚΩ V <sub>DDF</sub>    | 1              |                                                                                          |

| BG                                                                                                                                                                                                                                                 |        | В                     | High,<br>EARB = 0<br>Tri-stated,<br>EARB = 1 | 1–10 KΩ<br>V <sub>DDH</sub> | Open           | Pull up if HRCW[EARB] = 1. In<br>Single-Master mode, no pull-up<br>resistor is required. |

Table 8.

Signal States and Recommended Termination

al Terminations

| Table 8. Signal States and Recommended Termination (Conti | nued) |

|-----------------------------------------------------------|-------|

|-----------------------------------------------------------|-------|

|                                                                                         |                       |                                              | Connection                  |                |                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                                                                                  | Function <sup>1</sup> | State at<br>Hard Reset                       | If Used                     | lf Not<br>Used | Notes                                                                                                                                                                                          |

|                                                                                         |                       |                                              |                             |                | multi-function pins are bidirectional they can be used as inputs or outputs.                                                                                                                   |

| ABB/IRQ4                                                                                | В                     | Tri-stated                                   | 1–10 KΩ V <sub>DDI</sub>    | ļ              | Pull up.                                                                                                                                                                                       |

| TS                                                                                      | В                     | Tri-stated                                   | 1–10 ΚΩ<br>V <sub>DDH</sub> | Open           | Pull up. In Single-Master mode, no pull-up resistor is required.                                                                                                                               |

| A[0–31]                                                                                 | В                     | Low                                          | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| TT0/HA7                                                                                 | В                     | Tri-stated                                   | 1–10 ΚΩ<br>V <sub>DDH</sub> | Open           | Pull up in Multi-Master mode. In<br>Single-Master mode, no pull-up<br>resistor is required.                                                                                                    |

| TT1                                                                                     | В                     | Tri-stated                                   | 1–10 ΚΩ<br>V <sub>DDH</sub> | Open           | Pull up in Multi-Master mode. In<br>Single-Master mode, no pull-up<br>resistor is required.                                                                                                    |

| TT[2-4]/CS[5-7]                                                                         | В                     | Tri-stated                                   | 1–10 ΚΩ<br>V <sub>DDH</sub> | Open           | Pull up TT[2–4] in Multi-Master<br>mode. In Single-Master mode, no<br>pull-up resistor is required.                                                                                            |

| TBST                                                                                    | В                     | Tri-stated                                   | 1–10 KΩ V <sub>DDI</sub>    | 4              | Pull up                                                                                                                                                                                        |

| TSZ[0–3]                                                                                | В                     | Tri-stated                                   | As needed                   | Open           | The TSZ bus can be pulled up or<br>down. Pull down TSZ0 (100 $\Omega$ ) for<br>an external master. Otherwise, there<br>is no requirement. In Single-Master<br>mode, these signals can be open. |

| AACK                                                                                    | В                     | Tri-stated                                   | 1–10 KΩ V <sub>DDI</sub>    | 4              | Pull up                                                                                                                                                                                        |

| ARTRY                                                                                   | В                     | Tri-stated                                   | 1–10 KΩ V <sub>DDH</sub>    |                | Pull up                                                                                                                                                                                        |

| DBG                                                                                     | В                     | High,<br>EARB = 0<br>Tri-stated,<br>EARB = 1 | 1–10 ΚΩ<br>V <sub>DDH</sub> | Open           | Pull up. In Single-Master mode, no pull-up resistor is required.                                                                                                                               |

| DBB/IRQ5                                                                                | В                     | Tri-stated                                   | 1–10 KΩ V <sub>DDI</sub>    | 4              | Pull up                                                                                                                                                                                        |

| D[0-31]                                                                                 | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD[32–39]/D[32–39]/<br>HD[44–45]/D[44–45/]<br>HD[50–53]/D[50–53]/<br>HD[61–63]/D[61–63] | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD[40–43]/D[40–43]/<br>ETHRX[0–3]                                                       | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD[46–49]/D[46–49]/<br>ETHTX[0–3]                                                       | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD54/D54/ETHTX_EN                                                                       | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD55/D55/ETHTX_ER                                                                       | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD56/D56/ETHRX_DV/ET<br>HCRS_DV                                                         | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD57/D57/ETHRX_ER                                                                       | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD58/D58/ETHMDC                                                                         | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD59/D59/ETHMDIO                                                                        | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

| HD60/D60/ETHCOL                                                                         | В                     | Tri-stated                                   | As needed                   | Open           | No requirement                                                                                                                                                                                 |

#### **Signal Terminations**

| Table 8. | Signal States and Recommended Termination | on (Continued) |

|----------|-------------------------------------------|----------------|

|          |                                           |                |

|                                                                                                                                                                                                                                            |                       | <b>.</b>                                       | Conne                   | ction          |                                                                                      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|-------------------------|----------------|--------------------------------------------------------------------------------------|--|--|

| Signal                                                                                                                                                                                                                                     | Function <sup>1</sup> | State at<br>Hard Reset                         | If Used                 | lf Not<br>Used | Notes                                                                                |  |  |

| Notes: I = input, O = output, B = bidirectional three-state, OD = open-drain. Most multi-function pins are bidirectional three-state. This does not imply that they are all shared signals—only that they can be used as inputs or outputs |                       |                                                |                         |                |                                                                                      |  |  |

| ETHTX_CLK/<br>ETHREF_CLK                                                                                                                                                                                                                   | I                     | Tri-stated                                     | As needed               | Pull<br>down   |                                                                                      |  |  |

| ETHRX_CLK                                                                                                                                                                                                                                  | Ι                     | Tri-stated                                     | As needed               | Pull<br>down   |                                                                                      |  |  |

| ETHCRS                                                                                                                                                                                                                                     | I                     | Tri-stated                                     | As needed               | Pull<br>down   |                                                                                      |  |  |

| DP0/DREQ1/EXT_BR2                                                                                                                                                                                                                          | В                     | High,<br>DPPC=11<br>Tri-stated<br>Otherwise    | As needed               | Open           | Pull up if used as EXT_BR2.                                                          |  |  |

| IRQ1/DP1/DACK1/<br>EXT_BG2                                                                                                                                                                                                                 | В                     | High,<br>DPPC =11<br>Tri-stated,<br>Otherwise  | As needed               | Open           | Pull up if used as IRQ1 or DACK1.<br>Pull up EXT_BG2 in Multi-Master<br>mode.        |  |  |

| IRQ2/DP2/DACK2/<br>EXT_DBG2                                                                                                                                                                                                                | В                     | High,<br>DPPC = 11<br>Tri-stated,<br>Otherwise | As needed               | Open           | Pull up if used as IRQ2 or DACK2.<br>Pull up EXT_DBG2 in Multi-Master<br>mode.       |  |  |

| IRQ3/DP3/DREQ2/<br>EXT_BR3                                                                                                                                                                                                                 | В                     | High,<br>DPPC = 11<br>Tri-stated,<br>Otherwise | As needed               | Open           | Pull up if used as IRQ3 or EXT_BR3.                                                  |  |  |

| IRQ4/DP4/DACK3/<br>EXT_BG3                                                                                                                                                                                                                 | В                     | High,<br>DPPC = 11<br>Tri-stated,<br>Otherwise | As needed               | Open           | Pull up if <u>used as IRQ4</u> or DACK3.<br>Pull up EXT_BG3 in Multi-Master<br>mode. |  |  |

| IRQ5/DP5/DACK4/<br>EXT_DBG3                                                                                                                                                                                                                | В                     | High,<br>DPPC = 11<br>Tri-stated,<br>Otherwise | As needed               | Open           | Pull up if used as IRQ5 or DACK4.<br>Pull up EXT_DBG3 in Multi-Master<br>mode.       |  |  |

| IRQ6/DP6/DREQ3                                                                                                                                                                                                                             | В                     | High,<br>DPPC = 11<br>Tri-stated,<br>Otherwise | As needed               | Open           | Pull up if used as IRQ6.                                                             |  |  |

| IRQ7/DP7/DREQ4                                                                                                                                                                                                                             | В                     | High,<br>DPPC = 11<br>Tri-stated,<br>Otherwise | As needed               | Open           | Pull up if used as IRQ7.                                                             |  |  |

| PSDVAL                                                                                                                                                                                                                                     | В                     | Tri-stated                                     | 1–10 KΩ V <sub>DD</sub> | H              | Pull up                                                                              |  |  |

| TA                                                                                                                                                                                                                                         | В                     | Tri-stated                                     | 1–10 KΩ V <sub>DD</sub> | Н              | Pull up                                                                              |  |  |

| TEA                                                                                                                                                                                                                                        | В                     | Tri-stated                                     | 1–10 KΩ V <sub>DD</sub> | Н              | Pull up                                                                              |  |  |

| GBL/IRQ1                                                                                                                                                                                                                                   | В                     | Tri-stated                                     | 1–10 KΩ V <sub>DD</sub> | <u>H</u>       | Pull up                                                                              |  |  |

| BADDR29/IRQ5                                                                                                                                                                                                                               | В                     | Low                                            | As needed               | Open           | Pull up if used as IRQ5.                                                             |  |  |

| BADDR30/IRQ2                                                                                                                                                                                                                               | В                     | Low                                            | As needed               | Open           | Pull up if used as IRQ2.                                                             |  |  |

| BADDR31/IRQ3                                                                                                                                                                                                                               | В                     | Low                                            | As needed               | Open           | Pull up if used as IRQ3.                                                             |  |  |

al Terminations

| Table 8. Signal States and Recommended Termination (Continued | Table 8. | Signal States a | and Recommended | Termination | (Continued) |

|---------------------------------------------------------------|----------|-----------------|-----------------|-------------|-------------|

|---------------------------------------------------------------|----------|-----------------|-----------------|-------------|-------------|

|                                                                                                                                                                                                                                            |                       |                        | Connection                                       |                |                                                                                                                                                                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|--------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal                                                                                                                                                                                                                                     | Function <sup>1</sup> | State at<br>Hard Reset | If Used                                          | lf Not<br>Used | Notes                                                                                                                                                                                                           |  |

| Notes: I = input, O = output, B = bidirectional three-state, OD = open-drain. Most multi-function pins are bidirectional three-state. This does not imply that they are all shared signals—only that they can be used as inputs or outputs |                       |                        |                                                  |                |                                                                                                                                                                                                                 |  |

| CS[0-4]                                                                                                                                                                                                                                    | 0                     | High                   | As needed                                        | Open           | No requirement                                                                                                                                                                                                  |  |