# 恩智浦新一代毫米波 雷达芯片解析

杨昌 产品市场部, Radar&V2X MAY 2022

SECURE CONNECTIONS FOR A SMARTER WORLD

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

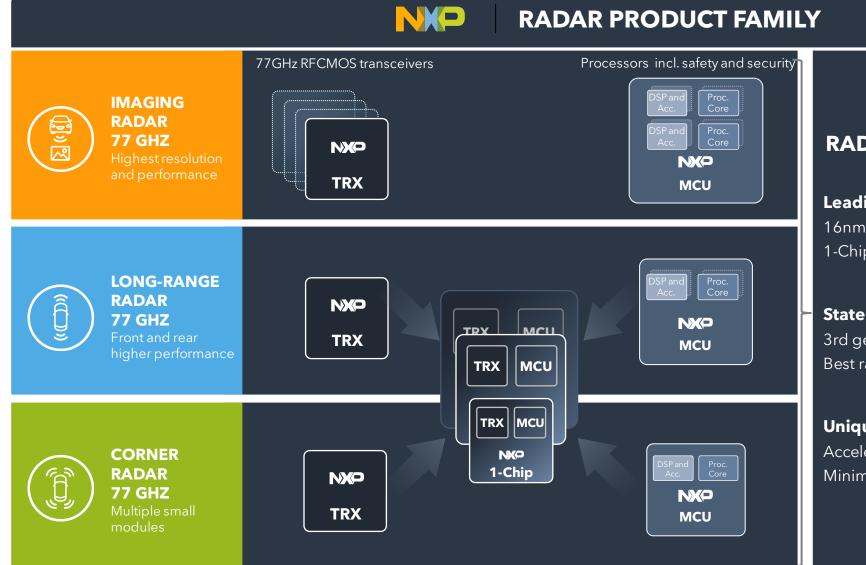

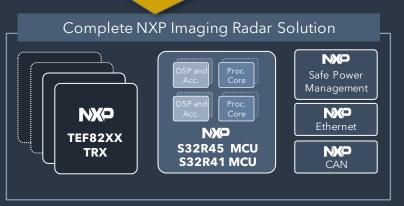

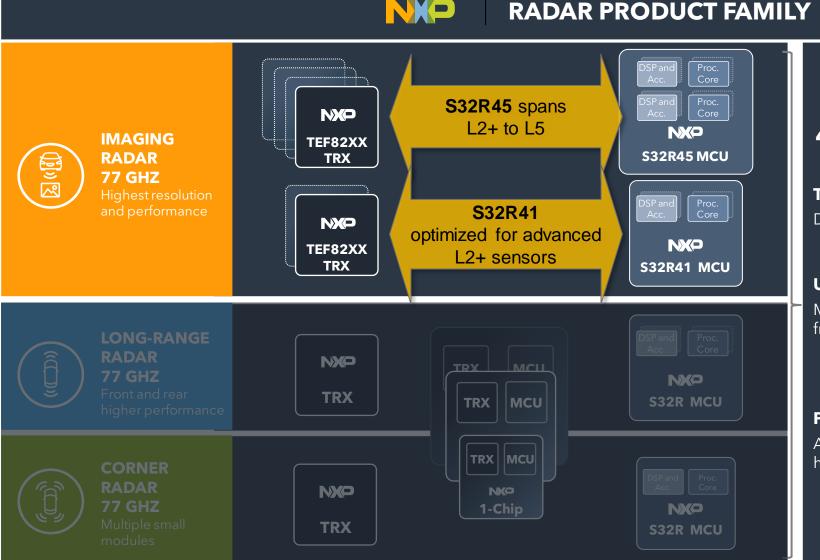

### INDUSTRY'S MOST COMPLETE AUTOMOTIVE RADAR PORTFOLIO

SCALES FROM 1-CHIP TO 4D IMAGING RADAR, ALLOWS TAILORING FOR USE CASE

#### **RADAR TECHNOLOGY LEADERSHIP**

#### Leading edge technology nodes

16nm MCUs and 40nm RFCMOS TRX in production 1-Chip in 28nm RFCMOS coming up

#### State of the art 77GHz RFCMOS performance

3rd gen RF-CMOS

Best range at 2x of first generation

#### **Unique Radar architecture and algorithms**

Accelerators for 64x performance vs. standard cores Minimal power dissipation and footprint

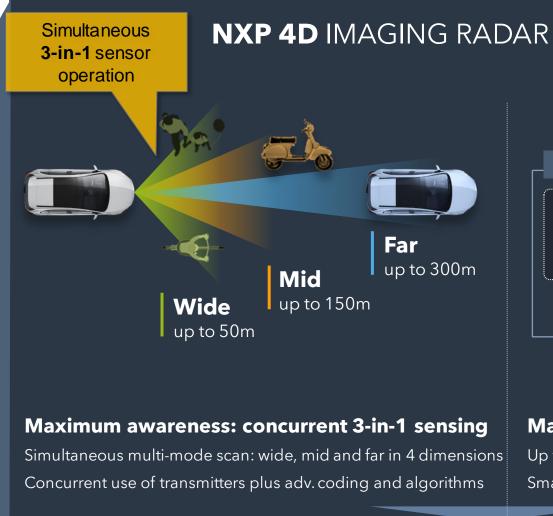

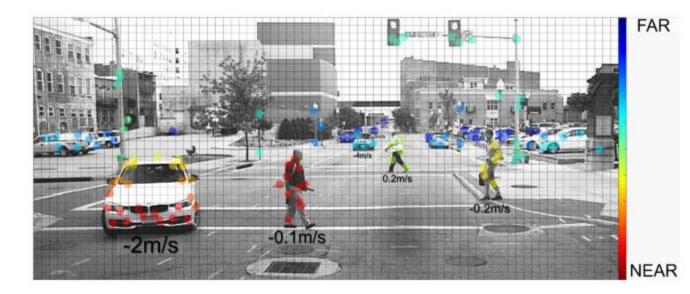

#### S32R4X BOOSTING PERFORMANCE WITH 3-IN-1 IMAGING RADAR FOR L2+ THROUGH L5

- Radar acceleration: 64x ARM A53 equivalent

- Super-resolution radar algorithms

- RF-CMOS: 2x previous Gen RF budget

- Advanced MIMO wave-forms

- 3-in-1 sensor antenna design

### **Maximum efficiency for <1° resolution**

Up to 192 virtual channels and 12x efficiency gain Smart and lean design vs. ordinary antenna count scaling

**ENABLING MASS ADOPTION OF L2+**

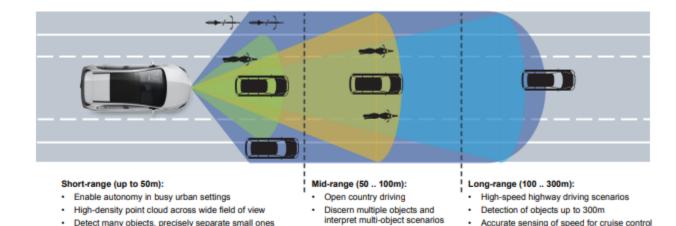

### 4D IMAGING RADAR BIFURCATION REQUIRES OPTIMIZATION FOR USE CASE

SCALABLE S32R4X ARCHITECTURE: EASY SCALING AND MIGRATION

#### **4D IMAGING RADAR**

#### **Tailor-made high-performance processors**

Delivers fast, powerful and efficient processing

#### **Unparalleled scalability on common architecture**

Maximized software reuse for platform development - from advanced corner to 4D imaging radar

#### Performance boost beyond raw HW capability

Advanced radar processing software unleash the full hardware potential

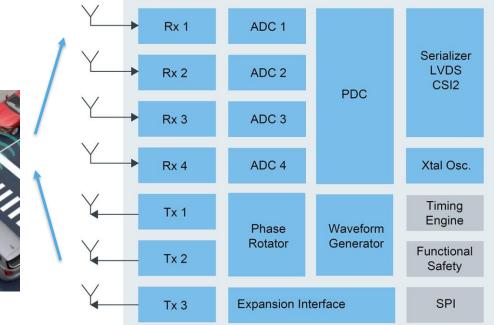

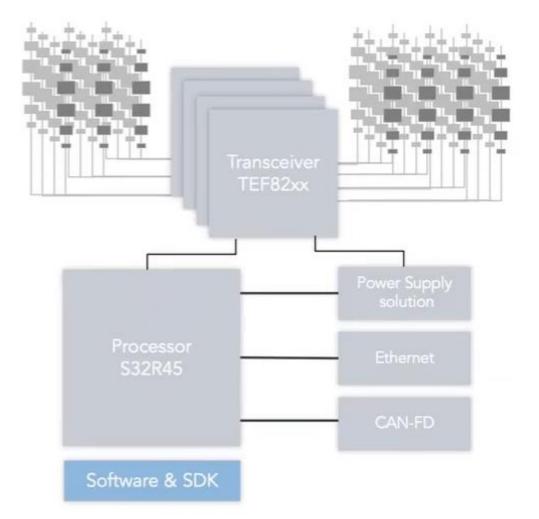

#### **GEN 2 CMOS MMIC - TEF82XX**

#### **OVERVIEW**

The TEF82xx car radar transceiver is a single-chip, low power automotive FMCW radar transceiver for short, medium- and long-range radar applications including cascaded high-resolution imaging radar, covering the full car radar frequency band from 76 GHz to 81 GHz. The fully integrated RFCMOS chip contains 3 transmitters, 4 receivers, ADC conversion, phase rotator and a low-phase-noise VCO. The device also includes built-in safety monitors and external interface capability for MIPI-CSI2 and LVDS.

- Capability: Fully integrated RFCMOS automotive radar transceiver for 76–81 GHz

- Quality: ISO26262 compliant, ASIL Level B

- Functionality: Optimized for fast chirp modulation

- System: Fully compatible with NXP S32R29x and S32R45x radar microcontrollers

**TEF82xx MMIC**

| Channels          | 3 Tx (w/ phase rotator)<br>and 4 Rx | Cascading          | 4 chips for up to 12 Tx<br>and 16 Rx |

|-------------------|-------------------------------------|--------------------|--------------------------------------|

| Frequency Range   | 76–81 GHz                           | Package            | 165 pin eWLB<br>7.5 x 7.5 mm         |

| Output Power      | 13.5 dBm                            | ADC Sample Rate    | 40 MS/s                              |

| Noise Figure      | 11.5 dB                             | Interface          | CSI-2 or LVDS                        |

| Phase Noise       | -95 dBc/Hz                          | Temperature Range  | -40 to 135 °C Tj                     |

| Power Consumption | 1.5 W (2 Tx 50%)                    | Effective Chirp BW | 4 GHz                                |

#### TARGET APPLICATIONS

- · Cascaded imaging radar

- Adaptive cruise control

- · Autonomous emergency braking

- Blind spot detection

- Front/Rear cross-traffic-functions

- Lane change assistance

- Parking

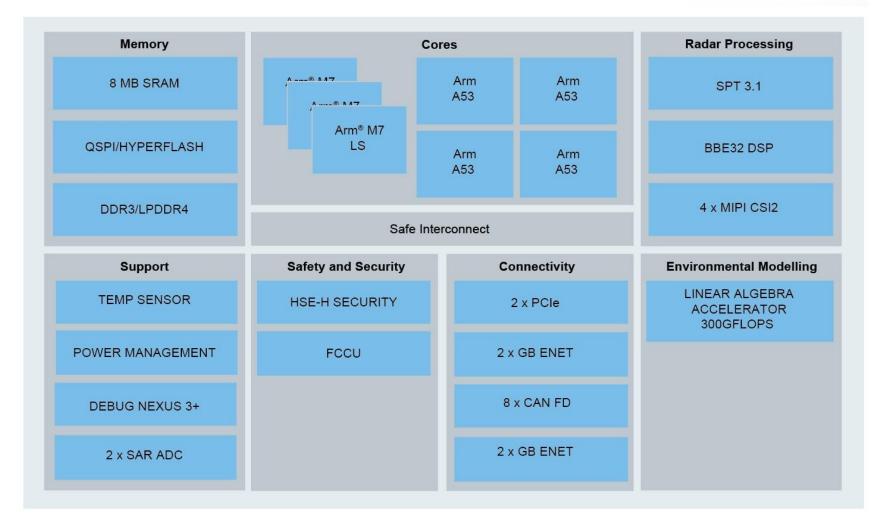

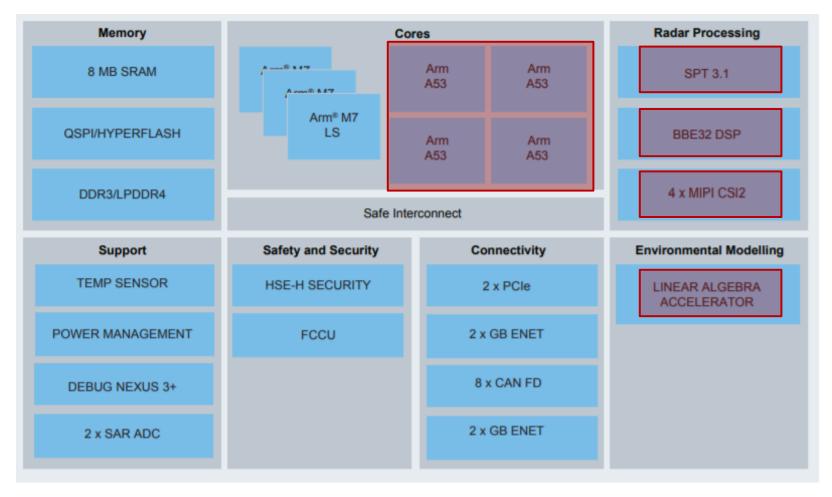

#### **IMAGING RADAR PROCESSOR - S32R45**

#### **KEY FEATURES**

- Quad Arm Cortex-A53 @ 800 MHz, flexible lockstep

- Triple Arm Cortex-M7 lockstep pairs @ 400 MHz

- LAX 1.0: >300 GFLOPS

- SPT 3.1 @ 600 MHz with integrated DSP and multithreading

- . 8 MB SRAM with ECC

- DDR3L-1600 with 16-/32-bit support and LP-DDR4-1600/3200 with 16-/32-bit support

- HSE High

- 2 x SAR ADC 16-ch.

- 4x MIPI CSI2

- PCle 2 x Gen2/3, 2 lanes

- 2 x GbE 10/100/1000 Mbit/s

- 8 x FlexCAN with FD

- ISO26262 SEooC ASIL B(D)

- -40 °C to 150 °C (Tj) AEC-Q100 Grade-1

### **IMAGING RADAR 12TX16RX APPLICATION**

Detect many objects, precisely separate small ones next to large ones and reliably classify in real time

Accurate sensing of speed for cruise control

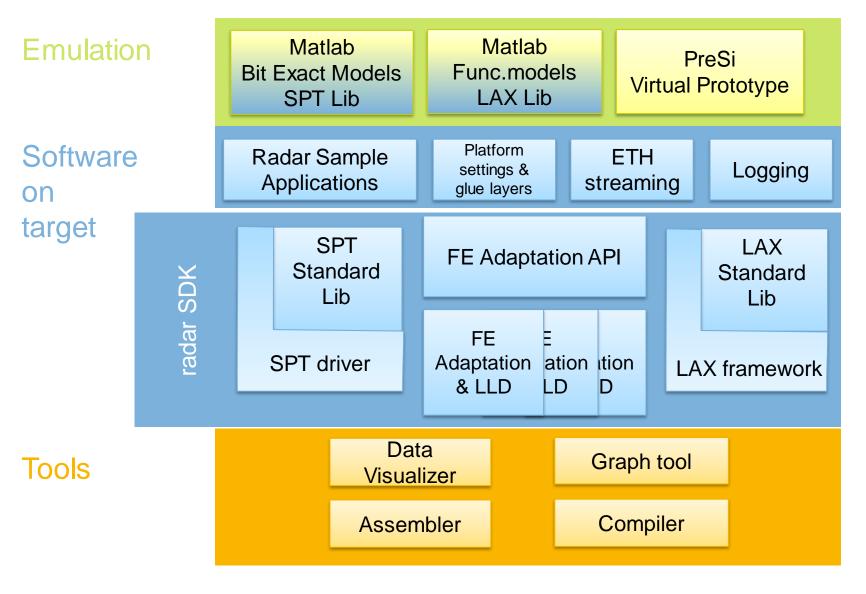

# Radar SDK Scope

SECURE CONNECTIONS FOR A SMARTER WORLD

#### **CONTEXT OF RADAR SDK**

- RF Abstract API for MMIC

- · SPI & CSI2 drivers

- SPT Driver

- SPT Kernels

- DSP Dispatcher (BBE32)

- DSP Algos (examples)

- · LAX framework

- · LAX kernel library

- Sample Apps (with and without RF)

- User Guide (doxy generated)

- Supported platforms: S32R274 S32R372 S32R294 S32R45 S32R41

#### **RADARSDK: SUPPORT FOR S32R45**

- Arm based platform

- Added DDR

- Support for Linux

- Added DSP and LAX accelerators

- Up to 4 frontends

- SPT 3.x supports threads

# Thank you

View more at nxp.com under the <u>Driving</u> <u>Automation and Radar Training Academy</u>

# SECURE CONNECTIONS FOR A SMARTER WORLD