## 5G工业和物联网方案

弋 方 恩智浦半导体高级市场经理

2022年4月28日

SECURE CONNECTIONS FOR A SMARTER WORLD

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

## 内容提要

- 恩智浦在5G领域的成就

- 5G场景与特性

- 5G新技术

- 恩智浦端到端方案

- 开放包容的生态

- 工业和物联网典型场景

## 恩智浦在5G领域的成就

- 1) 恩智浦提供从天线到处理器的完整5G接入方案

- 2) 恩智浦助力和加速5G基站建设

- 3) 恩智浦可编程 Layerscape Access 系列基带处理产品用于 提供更高效的解决方案

- 4) 恩智浦同时提供传统架构和全新ORAN架构,提供有竞争力的5G部署方案

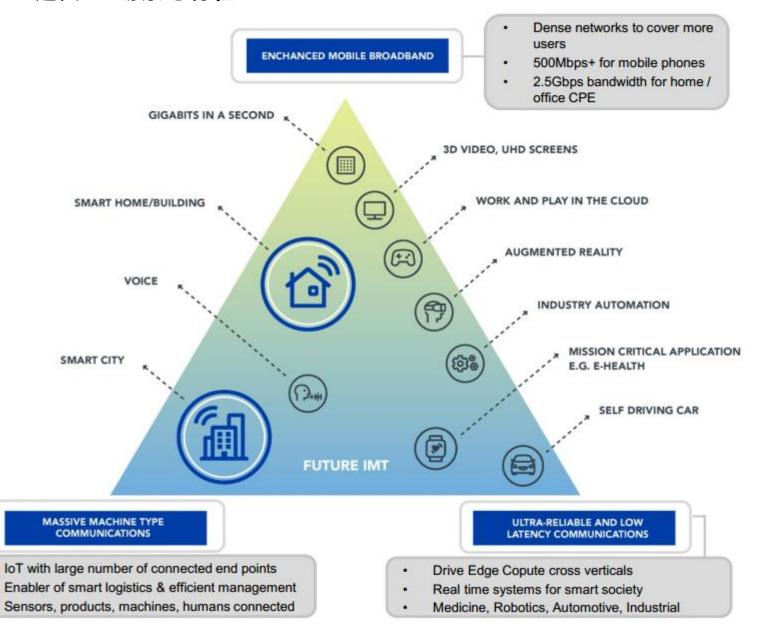

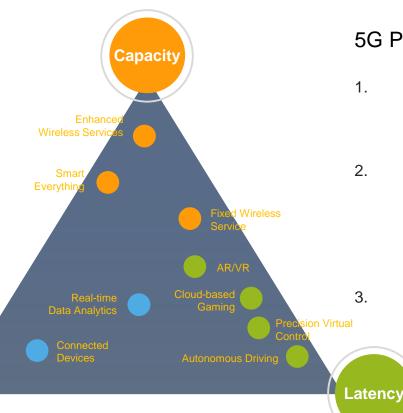

## 3GPP定义5G场景与特性

## 5G Technology Drivers

- ✓ New frequencies & spectrum (new transceivers and front-end modules)

- New 3GPP waveforms (new physical layer and baseband processing)

- ✓ New deployment models (non standalone → stand alone, O-Ran splits)

- ✓ New latency requirements (architectures tuned to applications, Access Edge processing)

## 5G新技术

As the rollout for 5G infrastructures expands, mobile network operators are modifying the existing infrastructure, adding what's needed to support the higher throughputs, greater device density and lower latency we'll need to run advanced 5G use cases, now and in future.

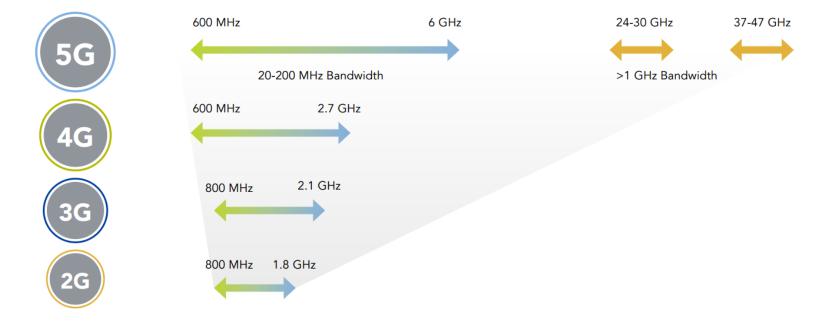

- **New Spectrum**

- **New Antenna Configurations**

- More Code

5G adds new frequency spectrum

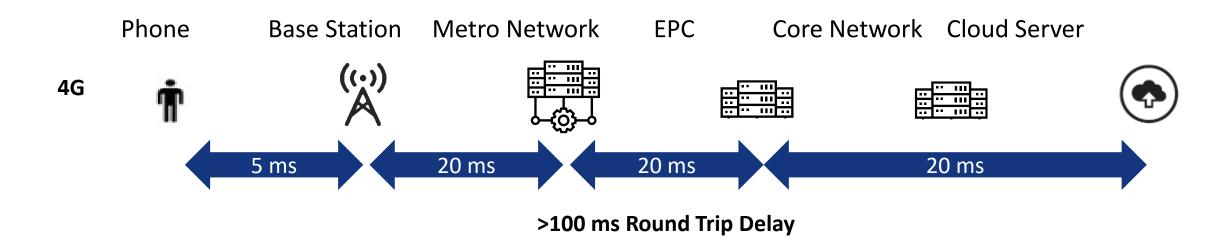

## 低延迟与可靠性

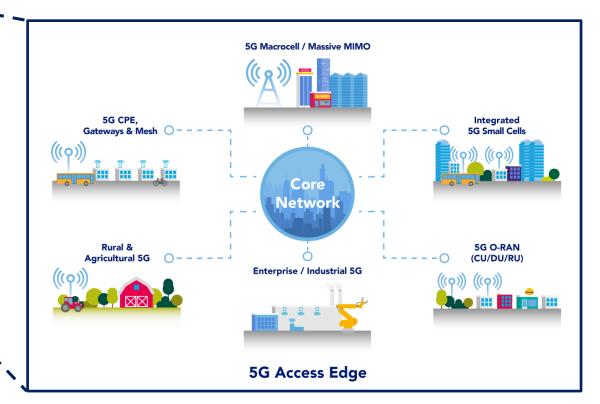

## 基于分层机制设计的5G部署方案

Preparing the infrastructure for 5G operation involves adding different layers of coverage, each providing the capacity / coverage trade-off needed for a given area or use case. Unlike 4G that consisted of high-power macro cells complemented here and there by small cells, the 5G deployments consist of high-power macro cells, mMIMO cells, small cells, with mmWave bridging the gap between them.

#### High-power Macro radios

- 25km

- 2T2R to 8T8R, sub 6 GHz

- Massive MIMO radios

- 1km

- 32T32R to 64T64R, sub 6 GHz

- mmWave radios

- 100 m

- e.g. 256T256R, 24 GHz

- serve as a backhaul for small cells and WiFi6/6E hotspots

- Small Cells

- backpack-sized, low-power base stations that provide targeted capacity in network "hotspots"

- largely driven by the need for 5G operation.

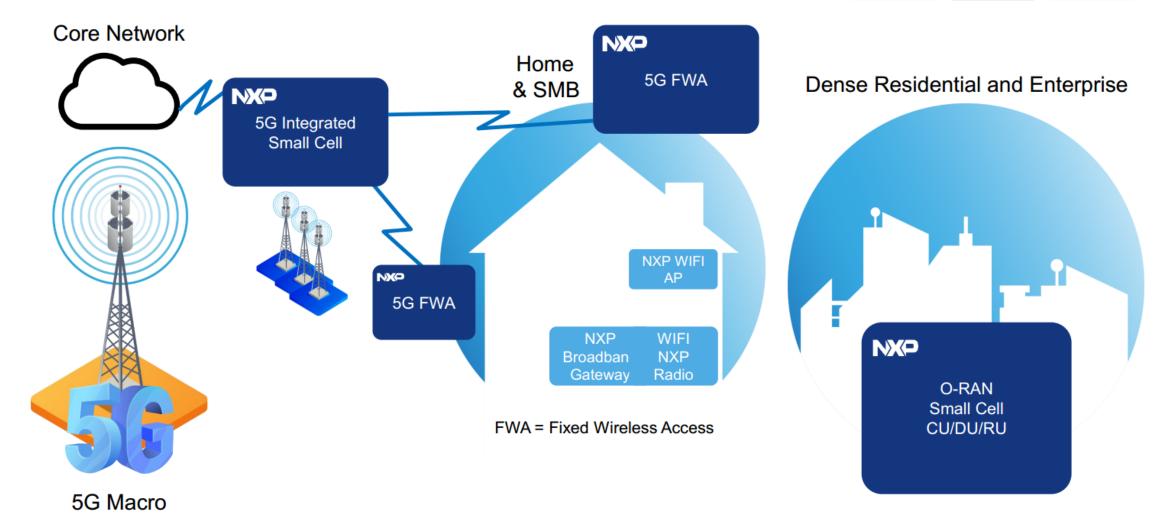

## 恩智浦端到端5G解决方案

Central

Office/Macro

Basestations

Central

5G E

End User (ie Smart Phone)

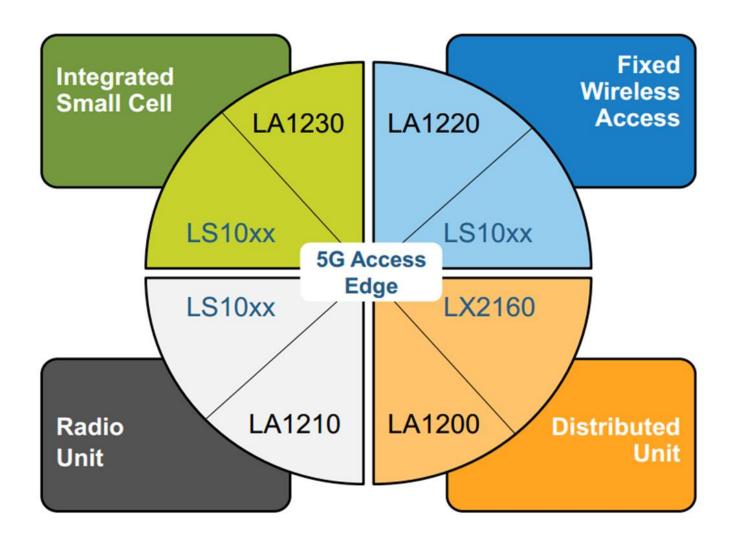

## LAYERSCAPE ACCESS 系列产品应用于多种5G场景

## 四大应用

- 可扩展处理器平台

- 针对应用需求进行特定调优的方案

- 软件赋能

## 广泛的生态合作伙伴方案

- 软件协议栈(Level 1 to Level 2+)

- 支持mmWave 和 sub-6GHz 射频

- 制造商和集成商

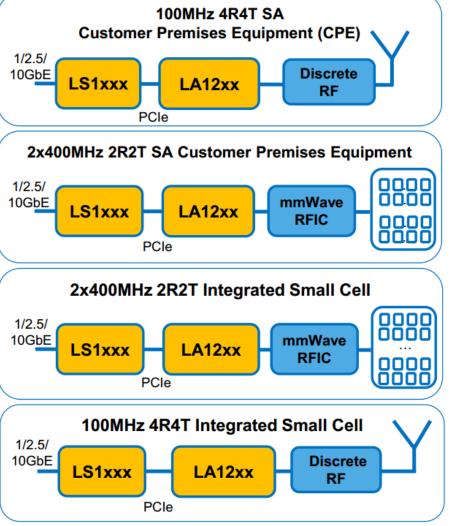

## 针对5G NR FR1 和 FR2 的完整平台

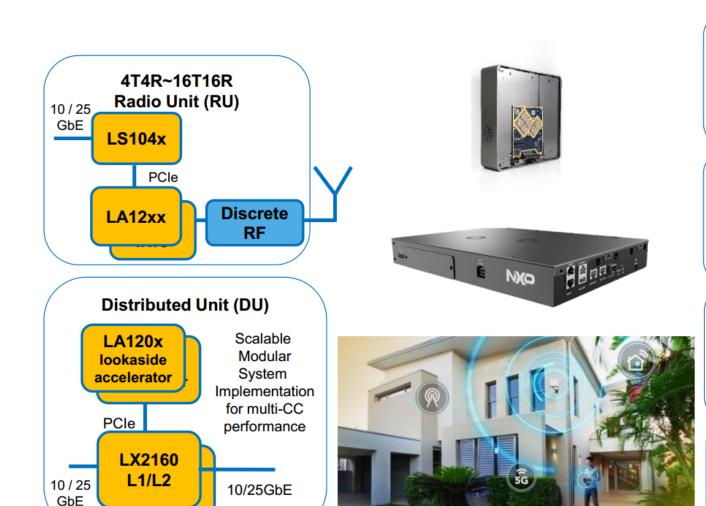

## 灵活扩展的 ORAN架构 DU 基带解决方案

Enclosure Dimensions in inches(15.394 x 10.236 x 1.75) inches 1U Dimensions requirement (in): 16.92in x 11.81in x 1.75in

#### System main components

- 16-Core ARM64b SoC (A72 @2.2GHz) Multicore

- 282GFLOP (32b) or 563 GOP (16b)

- Multiple datapath accelerators

- highspeed PCIe and Ethernet

- High Performance Ethernet subsystem

- 114Gbps Ethernet bandwidth and L2 switching

- Including QoS, IEEE1588, eCPRI classification

- Look-aside FECA accelerator

- 5G DCI/UCI (Polar) encoder and decoder

- 5G Shared Channel (LDPC) encoder and decoder

| SDR /               | Accelerator                      | A72                          | A72    | A72                       | A72                           | A72                       | A72          | A72                                          | A72       |                     |

|---------------------|----------------------------------|------------------------------|--------|---------------------------|-------------------------------|---------------------------|--------------|----------------------------------------------|-----------|---------------------|

| e200<br>MPU         | VSPA<br>Vector DSP<br>IRAM, DRAM | A72                          | A72    | A72                       | A72                           | A72                       | A72          | A72                                          | A72       | 72-bit<br>DDR4      |

|                     | IKAWI, DRAWI                     | 1MB L2                       | IMB L2 | 1MB L2                    | 1MB L2                        | 1MB L2                    | 1MB L2       | 1MB L2                                       | 1MB L2    | with                |

|                     | rconnect                         |                              |        |                           | Interce                       | onnect                    |              |                                              |           |                     |

|                     | ₹ LDPC,                          | 8MB Platform Cache           |        |                           |                               |                           |              |                                              |           |                     |

| PCIe gen3<br>x4/x8  | LDPC,<br>Polar FEC               |                              | -      | O MMU                     | IO MMU                        | IO MMU                    | IO MMU       |                                              |           |                     |

| 80 X                |                                  | Secure Boot<br>Trust Zone    |        | 2MB PEB                   |                               |                           | Lal          | Jalala                                       | a   m   m |                     |

| ž ×                 | 6MB<br>SRAM                      | Power Manageme               | sec-   | -50G                      | WRIOP                         |                           | 2 2          | Gen3 PCIe<br>Gen3 PCIe<br>Gen3 PCIe          | SATA3     | 72-bit              |

| 8 Lane<br>IG SerDes |                                  | SD/WMMC<br>2x DUART          | 0.0    |                           | 114Gbps<br>1/2.5/10/25/40/50/ |                           | en3          | en3 en3                                      | TA3       | DDR4<br>with<br>ECC |

|                     |                                  | 8x I2C<br>SPI, GPIO, JTAG    |        | 1/ 2.5 / 10 / 2<br>100 Et |                               | 25 / 40 / 50 /<br>thernet | x8 Gen3 PCle | x4 Gen3 PCle<br>x4 Gen3 PCle<br>x4 Gen3 PCle |           |                     |

|                     |                                  | 2x USB3.0 + PHY<br>2x CAN-FD |        | 18-<br>tan 24 lanes       |                               | @ up to 25GHz             |              |                                              |           |                     |

| Solution Features   |                                                      |  |  |  |  |

|---------------------|------------------------------------------------------|--|--|--|--|

| Standard            | 3GPP R.15                                            |  |  |  |  |

| BBU Platform        | NXP BonnyRigg LX2160 +<br>LA12xx DU reference design |  |  |  |  |

| Fronthaul interface | Option 7-2x: eCPRI over<br>10GE or 25GE              |  |  |  |  |

| Frequency band      | <6 GHz                                               |  |  |  |  |

| System bandwidth    | Up to 100 MHz, multiple CCs                          |  |  |  |  |

| Duplexing           | TDD and FDD                                          |  |  |  |  |

| Subcarrier spacing  | 15kHz, 30kHz, 60kHz,<br>120KHz                       |  |  |  |  |

| MIMO                | 4x4 spatial multiplexing                             |  |  |  |  |

| System throughput   | Multi-Gbps                                           |  |  |  |  |

| Modulation          | Up to 256QAM                                         |  |  |  |  |

| Layers              | Multi-Layers                                         |  |  |  |  |

| Sync                | GPS, IEEE1588, SyncE                                 |  |  |  |  |

**PUBLIC**

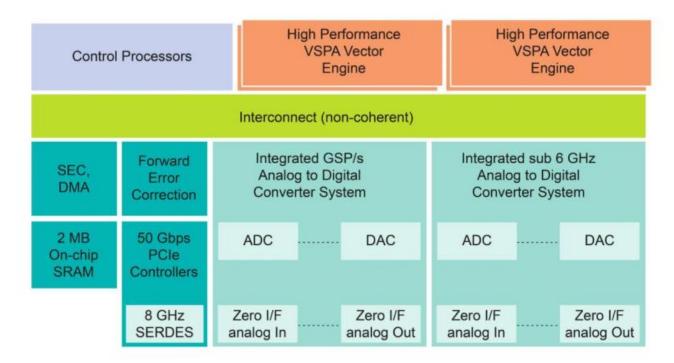

## LA12XX 系列高性能基带处理器

#### **Programmable**

- Faster updates R15 → R16 features vs. FPGA or ASICs

- · Value added features: example: digital front end

- Custom modulation

#### **Flexible**

- mmWave or Sub 6GHz configurations

- CPE, RU, DU, Integrated Small Cell use cases

- · Modem or offload accelerator

#### Scalable

- 2T2R → 16T16R

- Indoor femto to O-RAN infrastructure

- Core complex

- 2-4x e200@ <640MHz (equivalent to ARM M7)

- · Real time management/control

- 4-8x VSPA3-16@ up to 640MHz (=1.3TFLOP)

#### Connectivity and I/O

- · Zero IF Radio interface

- PCle gen3

- 2T2R High Speed ADC/DAC complex

- 4T4R Low Speed ADC/DAC complex

#### **Acceleration**

• Forward Error Correction: LDPC & Polar en/decode

#### mmWave and Sub-6 GHz Baseband Processor

#### Ideal, software defined, open baseband processor for:

- <6GHz or mmWave 5G Small Cell</li>

- <6GHz or mmWave 5G FWA CPE / Mesh</p>

- <6GHz or mmWave 5G RU</li>

- O-RAN CU/DU L1 / Error Correction <u>offload co-processor</u>

- General compute, aerospace/defense, civilian safety SDR

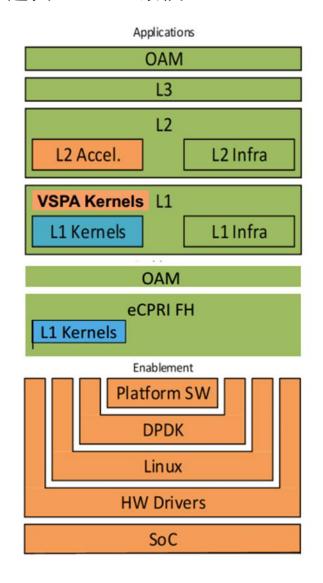

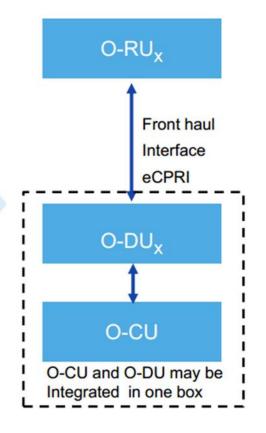

## 软件定义 O-DU 以及 O-RU

Ecosystem

ARM

**NXP**

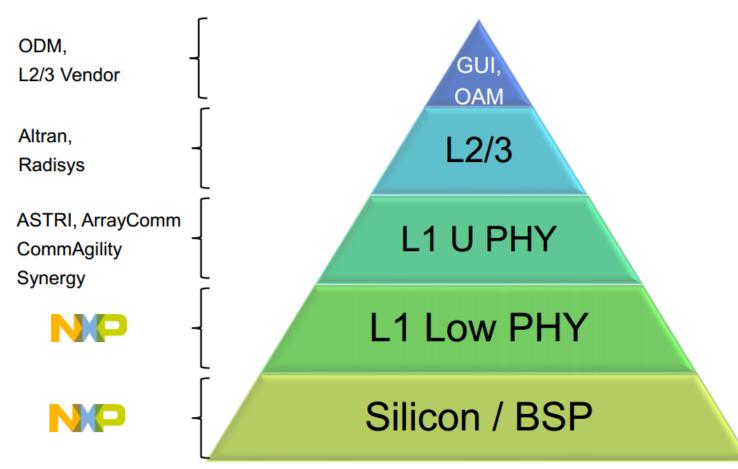

## ISC (INTEGRATED SMALL CELL) 软件体系

NXP has a strong ecosystem with several high-quality options

3<sup>rd</sup> party vendors to supply L1 upper PHY and integration with upper stacks

NXP delivers lower PHY, BSP and libraries

ODM and 3<sup>rd</sup> party software conduct IOT and performance testing

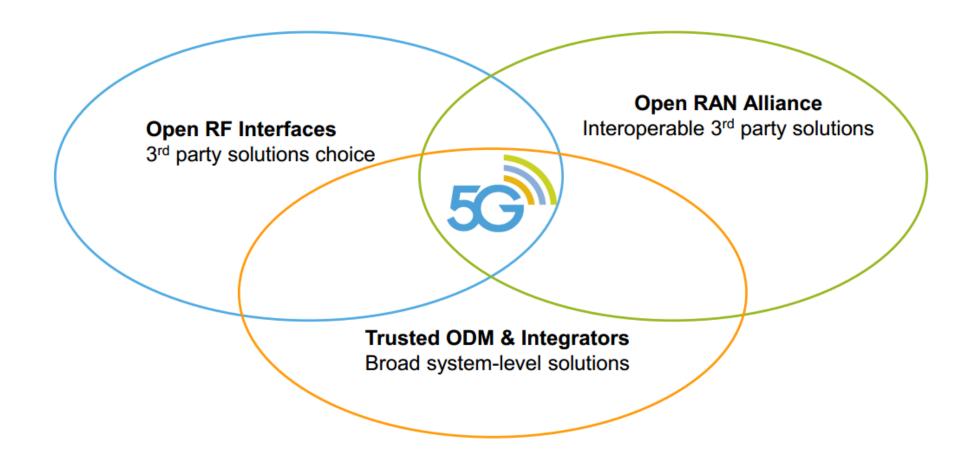

## NXP开放的生态体系

PUBLIC

## NXP开放的生态体系

| Layerscape Pro                                                                                                                                 | cessors                                                                                  | E                                                                                | cosystem Partners             | Reference & Development Designs                        |                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------|---------------------------------------------------|--|

| Layerscape Access Baseband<br>Processors<br>LA12XX                                                                                             | engines • 50Gbps I/O • 8-10W • Integrated ADC/DACs                                       | Software                                                                         | ASTRI ArrayComm.              | Reference Design:<br>LA1224-RDB<br>Development system  | Orderable today as part of<br>Access Program      |  |

| <ul> <li>LA120X – DU coprocessor</li> <li>LA121X – RU FR1, FR2</li> <li>LA122X – CPE FR1, FR2</li> <li>LA123X – Small Cell FR1, FR2</li> </ul> |                                                                                          |                                                                                  | @CommAgility  movandi         | Reference Design:<br>LA12XX CPE<br>Development system  | Proof of Concept and IODT test                    |  |

| Layerscape                                                                                                                                     | • 2-16 Arm v8 CPUs<br>• 2.5-100 GbE I/O                                                  | Hardware                                                                         | SIVERSUMA                     | Reference Design:<br>LA93XX RU Development             | Orderable Q1 2020 as part of Early Access Program |  |

| Communication SoCs:  • LX2160 – CU/DU  • LS10XX – Integrated Small Cell, RU, CPE                                                               | 1-16 PCle lanes     4-30W     eCPRI offload     Integrated Security     & Virtualization | S PCIe lanes OW PRI offload grated Security irtualization Systems Multiple ODM a | Multiple ODM and OEM partners | Reference Design: LX2160 PCIe iNIC CU Reference system | ODM solutions                                     |  |

# 工业和物联网场景

### 5G用于工业场景 - 从公用网络到垂直应用

#### **Example: Automated Guided Vehicle (AGV)**

- Today Layerscape has adoption in AGV solutions for path planning & motion control – e.g. LS1043, LS1046

- Next generation: Smart & Adaptive AGV

- Smart AGV acquires real-time environment information via computer vision technology

- 5G small cell on site link to the cloud, training via environment data

- Inference on the intelligent AGV to achieves autonomous obstacle avoidance increased efficiency & more adaptive AGV solutions

End-to-End latency required at ~5ms

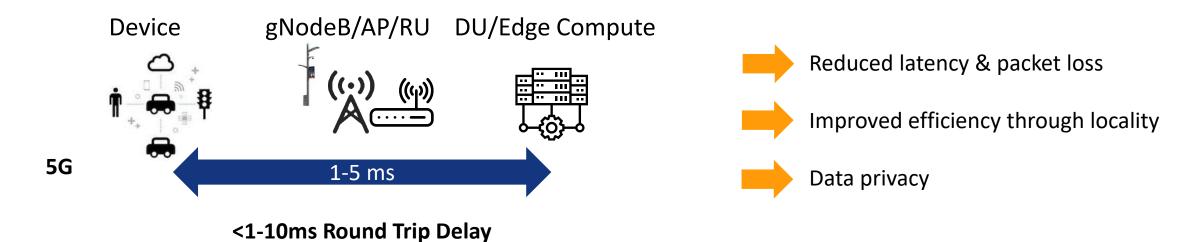

## The Generalized 5G Access Edge & Edge Compute Case

Device NodeB/AP DU/Edge Computer

Overall 1-10

- → Reduced latency & packet loss

- → Improved efficiency through locality

- → Data privacy

**Overall 1-10ms Round Trip Delay**

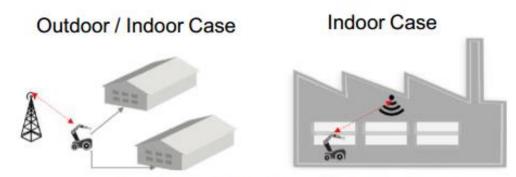

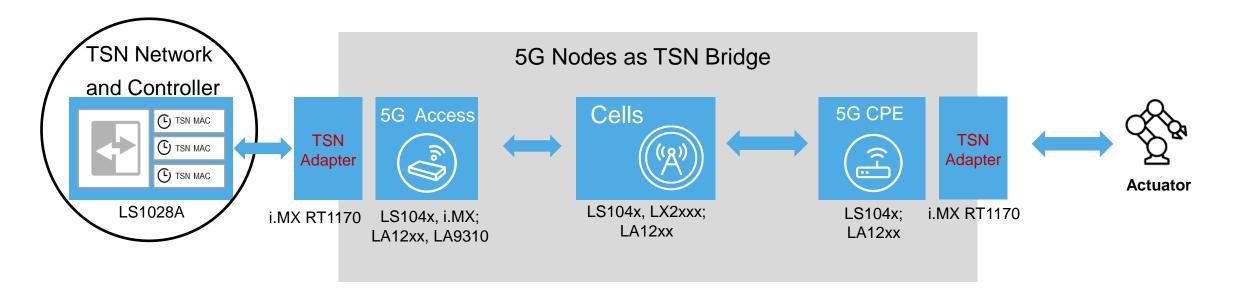

## 5G专用网络扩展了TSN解决方案的覆盖范围

- Combining 5G and TSN for deterministic connectivity end-to-end between end points (e.g. Actuator above)

and controller residing in an edge cloud

- NXP enables the necessary hardware and software platforms for the 5G-TSN integration

- Thus providing the key technology components for combined deployment in private networks

## 5G特性之平衡三角形

#### **5G DEPLOYMENT DRIVERS**

- 100s of thousands of companies to deploy private 5G networks this decade: manufacturing facilities, warehouses, seaports, and mining operations to hospitals, and utilities.

- 100s of millions of connected devices and sensors with massive machine-type communication

- Low latency and wide coverage for automated guided vehicles

- 3GPP provisions for Wi-Fi to 5G, indoor to outdoor hand-off

### 5G Private Networks → efficient edge compute

- . Flexibility and integration options: flexible / scalable system implementations

- Performance and Reliability: the growing number of devices requires high performance networks; Industry 4.0 requires reliable connectivity

- Dense Networks, Coverage, and Control: support growing number of devices and in parallel control data processing and storage

2019+

Enhanced mobile broadband

Coverage

2021+

Ultra-reliable and low latency communications

2023+

Massive machine type communications

NXP

Sources: Jefferies. NXP

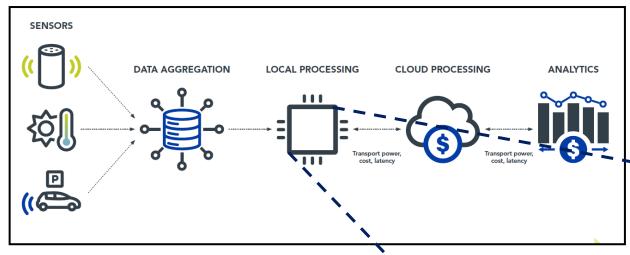

## 边缘计算需求量激增

Power, Processing Cost, Latency

## **Edge Compute Considerations**

- Energy/bit

- Connectivity including WiFi and 5G

- Edge to Cloud Infrastructure

- Security and Lifecycle Management

- Intelligence: ML and AI at the edge

**PUBLIC**

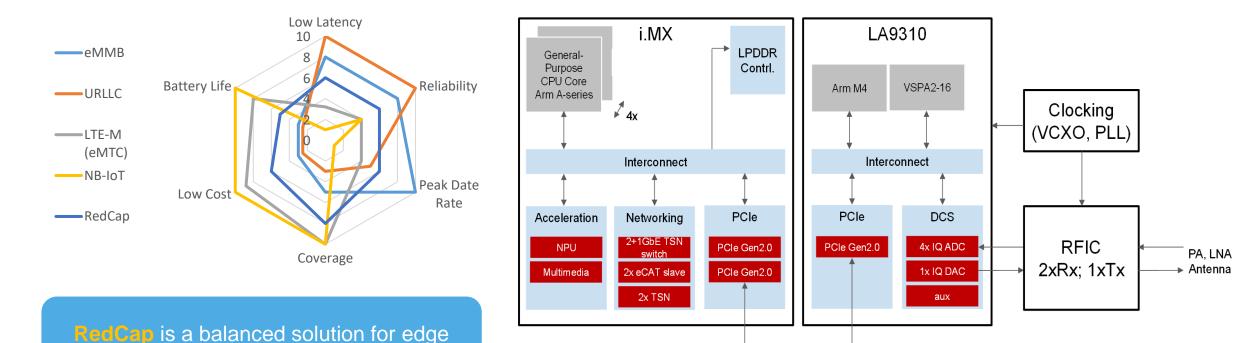

## 5G RedCap 方案 (Reduced Capability, in 3GPP R17)

- Application/host processor = NXP i.MX processor. Responsible both for the Industrial/IoT processing as well as implementing the upper-Phy and L2+ stack components of the 5G RedCap modem

- Low-Phy modem = LA9310; Responsible for the low-Phy processing of the RedCap UE, including ADC/DAC data conversion to analog baseband IQ

- RFIC (3<sup>rd</sup> party) converts analog baseband IQ to RF signals that are fed to/from discrete PA, LNA and antenna pieces of the system

# SECURE CONNECTIONS FOR A SMARTER WORLD