# **UM12355**

## KITFS27-24VEVM evaluation board

Rev. 1.0 — 28 October 2025

**User manual**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FS27, FS2700-B0, KITFS27-24VEVM, KITFS27-24VEVM-REVB, spf-93486, FRDM-KL25Z, SPI, I <sup>2</sup> C, hardware, evaluation, power management, automotive 12 V, transportation 24 V, NXP GUI for Automotive PMIC Families                                                                                                                                                                                           |

| Abstract    | The KITFS27-24VEVM provides a development platform to evaluate the FLYBACK front-end regulator for automotive 12 V and transportation 24 V compatible configurations. The kit can be connected to the NXP GUI through an USB port. This document is intended for engineers involved in evaluation, design, implementation, and validation using the FS27 fail-safe system basis chip with multiple SMPS and LDO. |

KITFS27-24VEVM evaluation board

## 1 Introduction

This document is the user manual for the KITFS27-24VEVM evaluation board. This document is intended for engineers involved in evaluation, design, implementation, and validation using the FS27 12 V/24 V/48 V safety system basis chip (SBC) for automotive safety integrity levels (ASIL) D.

The scope of this document is to provide the user with information to evaluate the FS27. This document covers connecting the hardware, installing the software and tools, configuring the environment and using the kit.

The KITFS27-24VEVM evaluation board allows functional testing with FLYBACK topology front-end regulator and programming of the soldered sample.

The NXP GUI for Automotive PMIC Families allows the user to play with registers, try configurations, and program the part.

#### 1.1 KITFS27-24VEVM evaluation board

#### KITFS27-24VEVM evaluation board

#### **IMPORTANT NOTICE**

## For engineering development or evaluation purposes only

NXP provides the product under the following conditions:

This evaluation kit is for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY.

It is provided as a sample IC pre-soldered to a printed-circuit board to make it easier to access inputs, outputs and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by connecting it to the host MCU computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application heavily depends on proper printed-circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The product provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end device incorporating the product. Due to the open construction of the product, it is the responsibility of the user to take all appropriate precautions for electric discharge. In order to minimize risks associated with the customers' applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

KITFS27-24VEVM evaluation board

## 2 Finding kit resources and information on the NXP website

NXP Semiconductors provides online resources for this evaluation board and its supported devices on <a href="http://www.nxp.com">http://www.nxp.com</a>.

The information page for KITFS27-24VEVM evaluation board is at <a href="http://www.nxp.com/KITFS27-24VEVM">http://www.nxp.com/KITFS27-24VEVM</a>. The information page provides overview information, documentation, software and tools, parametrics, ordering information and a **Getting Started** tab. The **Getting Started** tab provides quick-reference information applicable to using the KITFS27-24VEVM evaluation board, including the downloadable assets referenced in this document.

## 2.1 Collaborate in the NXP community:

The NXP community is for sharing ideas and tips, asking and answering technical questions, and receiving input on just about any embedded design topic.

The NXP community is at <a href="http://community.nxp.com">http://community.nxp.com</a>.

KITFS27-24VEVM evaluation board

## 3 FS27: 12 V/24 V/48 V Safety System Basis Chip for ASIL D

### 3.1 General description

Devices in the FS27 automotive SBC family are designed to support entry and midrange safety 28 nm microcontrollers. FS27 devices have multiple power supplies and the flexibility to work with other microcontrollers targeting automotive electrification. Possible FS27 applications include power train, chassis, safety, and low-end gateway technology.

This family of devices consists of several versions that are pin-to-pin and software compatible. These versions support a wide range of applications with ASIL B or D, offering choices in the number of output rails, output voltage settings, operating frequencies, power-up sequencing, and integrated system-level features.

The FS27 features multiple switch mode regulators and low dropout (LDO) voltage regulators to supply the microcontroller, sensors, peripheral ICs, and communication interfaces. FS27 offers a high-precision reference voltage supply for the system, and for two independent tracking regulators. The FS27 also offers various functionalities for system control and diagnostics, including an analog multiplexer (AMUX), general-purpose input/outputs (GPIOs), and selectable wake-up events from I/O, long duration timer (LDT), serial peripheral interface (SPI), or inter-integrated circuit (I<sup>2</sup>C) communications.

The FS27 is developed in compliance with the ISO 26262 standard, and includes enhanced safety features with multiple fail-safe outputs. FS27 disposes of the latest on-demand latent fault monitoring, and can be part of a safety-oriented system partitioning scheme covering both ASIL B and D safety integrity levels.

#### 3.2 Features and benefits

#### Operating range

- 70 V DC maximum input voltage.

- Support operating voltage range down to battery 3.2 V with VBST in front-end.

- Support operating voltage range down to battery 4.5 V without VBST in front-end.

- Low Power LPOFF mode with 30 µA quiescent current.

- Low-Power *Standby mode* with 32 μA quiescent current with VPRE active. LDO1 or LDO2 activation is selectable via OTP configuration. GPIO1 or GPIO2 activation selectable via SPI/I<sup>2</sup>C communication.

- Low-Power Run mode LPRUN mode with selectable power rails configurable by software.

#### **Power supplies**

- VPRE: Synchronous buck converter with integrated FETs. Configurable output voltage and switching frequency, output DC current capability up to 1.5 A or 2.5 A and PFM mode for Low-Power Standby mode operation.

- VCORE: Synchronous buck converter with integrated FETs. VCORE is dedicated for microcontroller core supply. Output DC current up to 2.5 A or 3.5 A, output voltage range set from 0.8 V to 5.0 V.

- VBST: Asynchronous low-side controller with external low-side switch, diode, and current sense resistor.

VBST is configurable as a front-end supply to withstand low voltage cranking profiles, a back-end supply with configurable output voltage and scalable output DC current capability, FLYBACK controller to withstand 24 V and 48 V applications and flyback controller to withstand 48 V applications.

- LDO1: LDO regulator for microcontroller I/O support with selectable output voltage between 1.0 V and 5.0 V and up to 400 mA current capability.

- LDO2: LDO regulator for system peripheral support with selectable output voltage between 1.0 V and 5.0 V and up to 400 mA current capability.

- VREF: High-precision reference voltage with 0.75 % accuracy for External ADC reference and internal tracking reference.

UM12355

KITFS27-24VEVM evaluation board

• TRK1 and TRK2: Voltage tracking regulators with selectable output voltage between VREF, LDO2, or Internal LDO reference. Support high-voltage protection for ECU off-board operation up to 40 V. Each tracker has a current capability up to 150 mA.

#### System support

- Two wake-up inputs with high-voltage support for system robustness.

- Two programmable GPIOs with wake-up capability or LS driver for GPIO1 and HS/LS driver for GPIO2.

- · Programmable LDT for system shutdown and wake-up control.

- Monitoring of system voltages (including battery voltage monitoring) through the analog multiplexer.

- Selectable wake-up sources from: WAKE/GPIO pins, LDT, or SPI/I<sup>2</sup>C activity.

- Device control via 32-bit SPI or 40-bit I<sup>2</sup>C interface with cyclic redundancy checks (CRC).

- Multi PMIC power-up/down synchronization.

- DCLINK capacitor discharge command with NXP GD31XX.

#### Compliance

- Electromagnetic compatibility (EMC) optimization techniques for switching regulators, including spread spectrum, slew rate control, and manual frequency tuning.

- Electromagnetic interference (EMI) robustness supporting various automotive EMI test standards.

#### **Functional safety**

- Scalable portfolio from automotive safety integrity levels (ASIL) B to D.

- Independent monitoring circuitry, dedicated interface for microcontroller monitoring, simple, or challenger watchdog function.

- · Analog built-in self-test (ABIST1) and logical built-in self-test (LBIST) at startup.

- Analog built-in self-test (ABIST2) on demand.

- Safety outputs with latent fault detection mechanism (RSTB, FS0B/LIMP, FS1B). FS0B/LIMP upon part number.

#### Configuration and enablement

- LQFP48 pins with exposed pad for optimized thermal management.

- Permanent device customization via one-time programmable (OTP) fuse memory.

- OTP emulation mode for hardware development and evaluation.

- Debug mode for software development, MCU programming, and debugging.

KITFS27-24VEVM evaluation board

## 4 Getting ready

Working with the KITFS27-24VEVM requires the kit contents, additional hardware, and a Windows PC workstation with installed software.

#### 4.1 Kit contents

- Assembled and tested evaluation board and preprogrammed FRDM-KL25Z board in an antistatic bag.

- 3.0 ft USB-STD A to USB-B-mini cable.

- Six connectors, terminal block plug, two positions, straight 3.81 mm.

- Two connectors, terminal block plug, three positions, straight 3.81 mm.

- Jumpers mounted on board.

- · Quick start guide.

#### 4.2 Additional hardware

No additional hardware is required for device evaluation. For an in-depth evaluation of power conversion capabilities (power delivery and stability), in addition to the kit contents, the following hardware is required when working with this kit:

Power supply with a range of 8.0 V to 60 V and a current limit set initially to 1.0 A.

#### 4.3 Windows PC workstation

This evaluation board requires a Windows PC workstation. Meeting these minimum specifications should produce great results when working with this evaluation board.

• USB-enabled computer with Windows 7, 10 or 11.

### 4.4 Software

Software must be installed before working with this evaluation board.

· NXP GUI for Automotive PMIC Families.

All listed software is available on the NXP GUI for Automotive PMIC Families information page at <a href="http://www.nxp.com/NXP GUI for Automotive PMIC Families">http://www.nxp.com/NXP GUI for Automotive PMIC Families</a> or from our "Secure Files" portal at <a href="https://www.nxp.com/mynxp/secure-files">https://www.nxp.com/mynxp/secure-files</a> if device is not in production.

KITFS27-24VEVM evaluation board

## 5 Getting to know the hardware

#### 5.1 Kit overview

The KITFS27-24VEVM provides flexibility to play with all the features of the device and make measurements on the main part of the application. The FRDM-KL25Z board connected to the kit, combined with the FS27 NXP GUI for Automotive PMIC Families software allows full configuration and control of the FS27 SBC.

#### FS27 and KITFS27-24VEVM features:

- · VBAT power supply connectors (jack and Phoenix).

- VPRE output 5.0 V to 6.35 V up to 2.5 A.

- VCORE output 0.8 V to 5.0 V, up to 3.5 A.

- LDO1 and LDO2, from 1.0 V or 5.0 V, up to 400 mA.

- TRK1 and TRK2, from 1.0 V or 5.0 V, up to 150 mA.

- VREF accuracy regulator for external ADC reference up to 80 mA.

- FS0B/LIMP, FS1B external safety pins.

- USB to SPI and I<sup>2</sup>C protocol for easy connection evaluation GUI.

- · LEDs that indicate signal or regulator status.

- · OTP fuse programming.

- · Advance system monitoring via AMUX, and ADCs, and digital IOs.

- Analog variable resistor to test external voltage monitoring VMON\_EXT.

#### 5.1.1 Schematic, board layout, and bill of materials

The schematic, board layout, and bill of materials for the KITFS27-24VEVM evaluation board are available at <a href="http://www.nxp.com/KITFS27-24VEVM">http://www.nxp.com/KITFS27-24VEVM</a>.

#### KITFS27-24VEVM evaluation board

## 5.2 Kit featured components

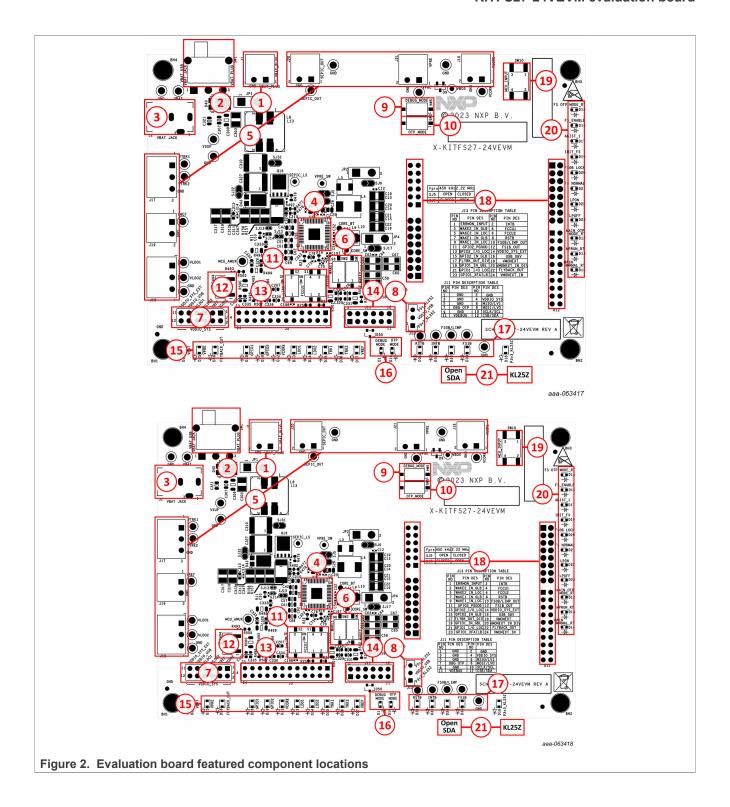

#### Figure 2 identifies the location of the main KIT features:

- 1. VBAT Phoenix connector

- 2. VBAT three position switch

- 3. VBAT jack connector

- 4. Soldered device location

- 5. Regulator outputs

- 6. WAKE1 and WAKE2 input switches

- 7. VDDIO selection

- 8. VDDIO USB voltage level selection

- 9. DEBUG mode switch

- 10. OTP mode switch for emulation and programming

- 11. DC LINK and FCCU switches

- 12. VMONEXT variable resistor

- 13. Signal connector

- 14. Program connector

- 15. Regulators output LED indicators

- 16. DEBUG pin voltage LED indicator

- 17. Safety outputs LED indicators

- 18. FRDM-KL25Z board headers (bottom)

- 19. MCU input switch

- 20. Device state machine status LEDs

- 21. FRDM-KL25Z board USB connections (bottom board)

- 22. Signal connectors compatible with 16-channel logic analyzer (socket board only)

- 23. Safety isolation switches: FS27 safety ↔ LEDs/FRDM-KL25Z board ADCs and IOs

- 24. Communication protocol manual select switch

- 25. VSUP discharge switch (socket board only)

- 26. COM isolation switches: FS27 ↔ communication lines' level shifters

- 27. LEDs isolation switches: FS27 regulators ↔ LEDs/FRDM-KL25Z board ADCs

### KITFS27-24VEVM evaluation board

KITFS27-24VEVM evaluation board

## 5.2.1 Default board configuration

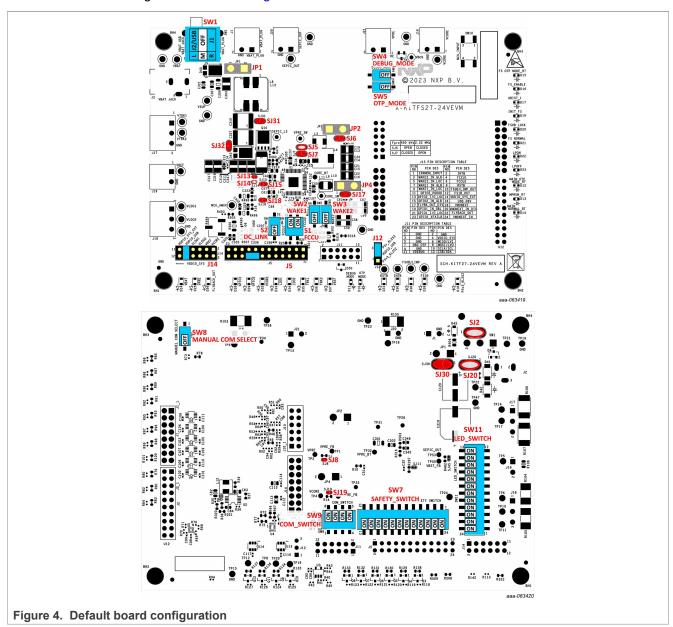

The kit is provided with a default board configuration following the legend on Figure 3.

| Status    | Jumper | Jumper power | Switch  | Solder joint |

|-----------|--------|--------------|---------|--------------|

| OFF/Open  | • ■ Jx | JPx          | OFF SWx | <b>S</b> Jx  |

| ON/Closed | Jx     | JPx          | ON SWx  | SJx          |

|           |        |              |         | aaa-062839   |

Figure 3. Board configuration legend

The default board configuration shown in Figure 4.

## KITFS27-24VEVM evaluation board

Table 1. Default board configuration

| Schematic label | Description                                                                        | Default setting |

|-----------------|------------------------------------------------------------------------------------|-----------------|

| JP1             | FLYBACK front-end regulator input inductor current measurement                     | Open            |

| JP2             | VPRE regulator output inductor current measurement                                 | Open            |

| JP4             | VCORE regulator output inductor current measurement                                | Open            |

| SJ2             | Bypass SW1: VBAT connected to J1                                                   | Closed          |

| SJ6             | Bypass JP2: jumper for VPRE regulator output inductor current measurement          | Closed          |

| SJ7             | Connect VPRE_SW to L4 (inductor F <sub>PRE</sub> = 444 kHz)                        | Closed          |

| SJ8             | Bypass R4: resistor for VPRE regulator stability measurement                       | Closed          |

| SJ11            | Connect GPIO2 pin to GPIO2 input/output external components                        | Closed          |

| SJ13            | Connect GPIO1 pin to GPIO input/output external components                         | Closed          |

| SJ14            | Connect GPIO1 pin to GPIO XFAILB components                                        | Open            |

| SJ15            | Connect VPRE regulator output to TRKIN pin                                         | Closed          |

| SJ17            | Bypass JP4: jumper for VCORE regulator output inductor current measurement         | Closed          |

| SJ18            | Connect VPRE regulator output to LDOIN pin                                         | Closed          |

| SJ19            | Bypass R14: resistor for VCORE regulator stability measurement                     | Closed          |

| SJ20            | Bypass D40: VBAT reverse protection diode                                          | Open            |

| SJ30            | Bypass JP1: jumper for FLYBACK regulator input inductor current measurement        | Open            |

| SJ32            | Opens FLYBACK regulator output diode for current measurement                       | Closed          |

| SJ45            | Bypass R482: resistor for FLYBACK regulator stability measurement                  | Closed          |

| SJ46            | Opens FLYBACK coupled inductor ground connection for secondary current measurement | Closed          |

| SJ47            | Bypass Q21: VBAT and BATSENSE clamp transistor                                     | Closed          |

| SW1             | VBAT supply                                                                        | 2 (middle)      |

| SW2             | WAKE1 switch global                                                                | OFF             |

| SW3             | WAKE2 switch global                                                                | OFF             |

| SW4             | Debug mode                                                                         | OFF             |

| SW5             | OTP mode                                                                           | OFF             |

| SW7             | Safety switch (breaker)                                                            | All ON          |

| SW8             | Communication protocol manual switch                                               | OFF             |

| SW9             | Communication interface switch (breaker)                                           | All ON          |

| SW11            | LED switch (breaker)                                                               | All ON          |

| S1              | FCCU switch                                                                        | All ON          |

| S2              | DC link switch                                                                     | OFF             |

KITFS27-24VEVM evaluation board

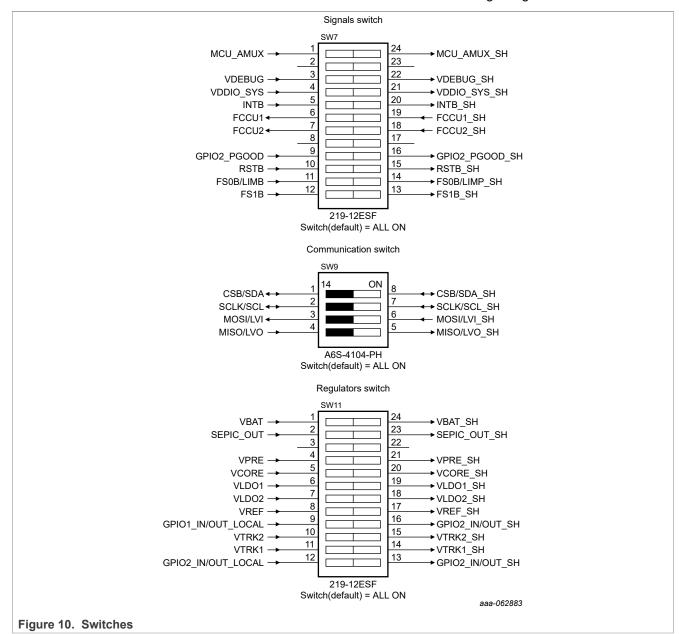

## 5.3 Switches

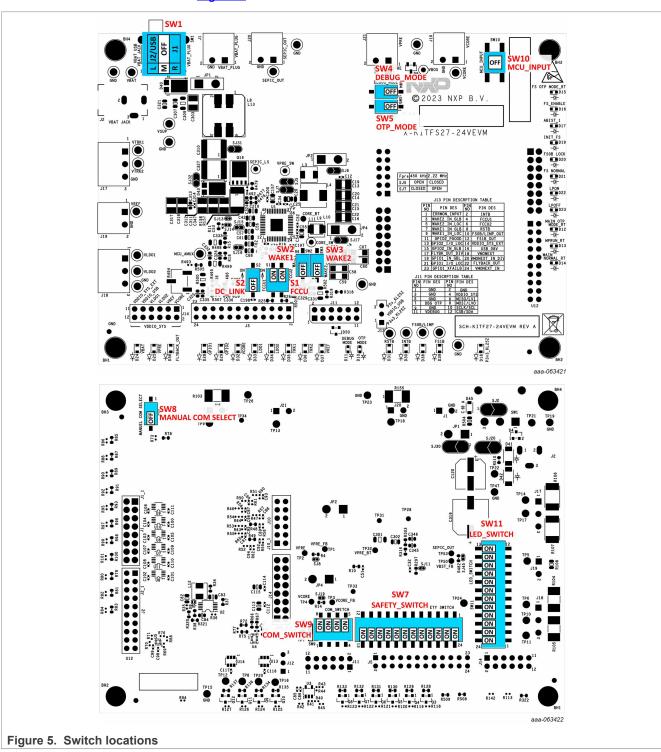

Kit switch locations are shown in Figure 5.

KITFS27-24VEVM evaluation board

### 5.3.1 VBAT switch

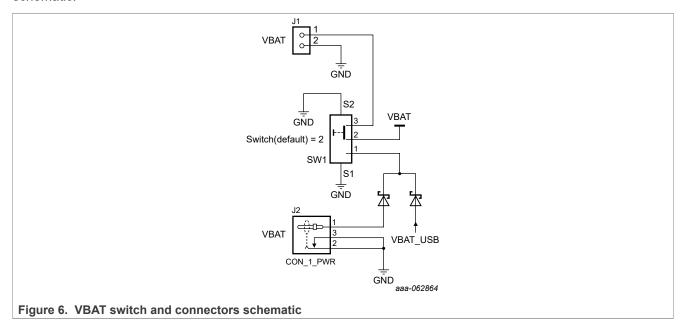

There are three ways of supplying the board main supply VBAT:

- 1. Phoenix connector (J1)

- 2. Jack connector (J2)

- 3. FRDM-KL25Z board USB

The selection of the supplying connector is done using a three-position switch (SW1). Figure 6 shows related schematic.

Table 2. SW1: VBAT three position connector

| Schematic label         | Signal name   | Description                                                                                                           |

|-------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------|

| SW1 position 3 (right)  | VBAT Phoenix  | Board supplied by Phoenix Connector J1                                                                                |

| SW1 position 2 (middle) | -             | Board not supplied                                                                                                    |

| SW1 position 1 (left)   | VBAT jack/USB | Board supplied by jack connector J2 or VBAT_USB (FRDM-KL25Z board USB generated 24 V supply), which voltage is higher |

Nominal VBAT voltage is 24 V, can operate from 8.0 V up to 60 V.

KITFS27-24VEVM evaluation board

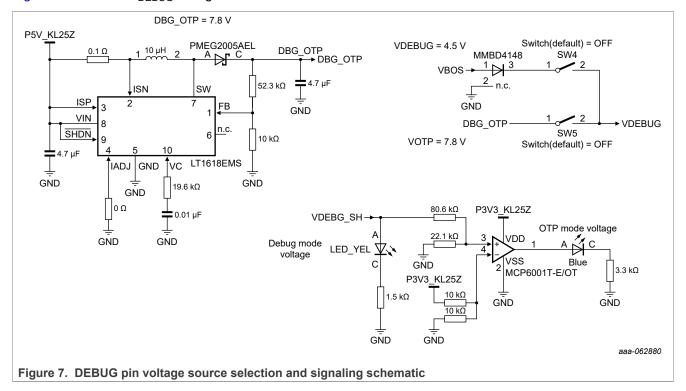

### 5.3.2 DEBUG pin voltage control

The DEBUG pin is used to enable specific device operating modes for evaluation purposes by applying different voltages and power-up sequences.

These modes are:

- Debug mode: to perform debug by disabling safety reactions

- **Test mode**: provide access to protected registers for extended diagnostics, OTP emulation (mirrors manipulation)

- OTP mode + Test mode: for OTP emulation (mirrors manipulation) and OTP programming (burn fuses)

**Note:** OTP emulation (mirrors manipulation) can be done at any state when test mode is enabled. It is recommended to emulate the OTP in OTP mode to observe the impact on the power-up sequence.

**Note:** OTP programming (burn fuses) can be done at any state when test mode is enabled, however OTP programming procedure is **only** guaranteed in OTP mode.

The DEBUG pin voltage V<sub>DEBUG</sub> to be applied before power-up sequence or low-power modes exit, are:

- V<sub>DEBUG</sub> = 0 V: Normal operation mode, run power-up sequence, debug mode not enabled.

- V<sub>DEBUG</sub> = V<sub>DBG</sub> = 4.5 V: Enters debug mode and run power-up sequence.

- V<sub>DEBUG</sub> = V<sub>OTP</sub> = 7.8 V: Enters debug mode, enter OTP mode, and halt before the power-up sequence.

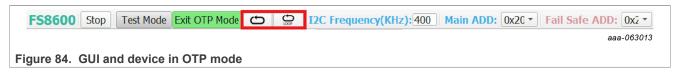

**Note:** When in OTP mode, to run power-up sequence,  $V_{OTP}$  must be removed (SW5 off) or click "Exit OTP mode" on the GUI.

The voltage level to be applied to DEBUG pin at any moment, is:

• V<sub>DEBUG</sub> = V<sub>DBG</sub> or V<sub>OTP</sub> = 7.8 V: In conjunction with the GUI request, enters test mode.

The required voltages are generated on-board, and the  $V_{DEBUG}$  can be controlled manually using SW4 and SW5.

The voltage V<sub>DBG</sub> is generated from the device VBOS pin thought a diode.

The voltage  $V_{OTP}$  is generate with an on-board boost regulator supplied by FRDM-KL25Z board USB 5 V supply. As a result, the FRDM-KL25Z board and USB must be plugged in to enter OTP mode.

The SW4 connects  $V_{DBG}$  while SW5 connects  $V_{OTP}$ .

**Note:** V<sub>OTP</sub> has higher priority than V<sub>DBG</sub>.

The yellow LED D11 indicates that at least V<sub>DBG</sub> is present at DEBUG pin.

The blue LED D10 indicates that V<sub>OTP</sub> is present at DEBUG pin.

<u>Table 3</u> shows the possible output voltage level to apply to the DEBUG pin depending on SW6 and SW7 positions.

Table 3. SW4 and SW5: DBG pin voltage V<sub>DEBUG</sub> selection and associated LED signaling

| <u> </u>                      | O DEDGG |     |     |                   |                                    |

|-------------------------------|---------|-----|-----|-------------------|------------------------------------|

| DEBUG pin voltage applied for | SW5     | SW4 | D11 | D10               | V <sub>DEBUG</sub> voltage (J13.2) |

| Normal operation (default)    | OFF     | OFF | OFF | OFF               | 0 V                                |

| Debug and test mode entry     | OFF     | ON  | OFF | ON <sup>[1]</sup> | 4.5 V                              |

| OTP mode entry                | ON      | Х   | ON  | ON                | 7.8 V                              |

[1] After VBAT (SW1) is ON

Note: SW4 and SW5 must be set before VBAT (SW1) is applied.

JM12355

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

### KITFS27-24VEVM evaluation board

## <u>Figure 7</u> shows the $V_{\text{DEBUG}}$ voltage sources and its selection.

KITFS27-24VEVM evaluation board

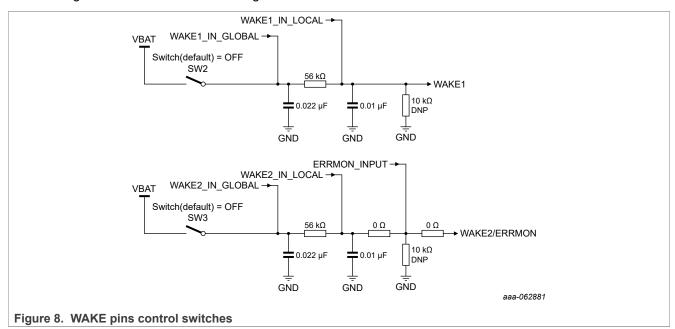

## 5.3.3 Wake input switches

The global wake inputs can be exercised by switches SW2 for WAKE1\_IN\_GLOBAL and SW3 for WAKE2\_IN\_GLOBAL supplied by the battery to VBAT signal.

A local wake command can also be exercised directly on the pin using WAKE1\_IN\_LOCAL and WAKE2\_IN\_LOCAL.

WAKE2 pin can also be used for error monitoring. Error monitoring input ERRMON can be controlled by ERRMON INPUT. R474 must be removed and the pulldown R473 might be populated.

All these signals can be accessed from signal connector J13.

Table 4. SW2: WAKE1 switch global

| Position | Function                  | Description      |

|----------|---------------------------|------------------|

| OFF      | WAKE1 is low logic level  | WAKE1 not active |

| ON       | WAKE1 is high logic level | WAKE1 active     |

Table 5. SW3: WAKE2 switch global

| Position | Function                  | Description      |

|----------|---------------------------|------------------|

| OFF      | WAKE2 is low logic level  | WAKE2 not active |

| ON       | WAKE2 is high logic level | WAKE2 active     |

KITFS27-24VEVM evaluation board

## 5.3.4 MCU input button

The MCU input button is an interface to the KL25Z state machine supervisor (LED\_STATES).

The MCU input button is disabled when "IO PINS" > "State Control Pins" > LED STATES is disabled.

When MCU input button is hit:

- FRDM-KL25Z board sends commands to update the LED STATES,

- if LED\_STATES shows device in main/FS OTP mode, FRDM-KL25Z board sends commands to quit OTP mode.

Note: If device is in standby mode (LPON), device may wake-up if communication activity wake-up is enabled.

Note: If device is in LPOFF mode, LED\_STATES will be reset.

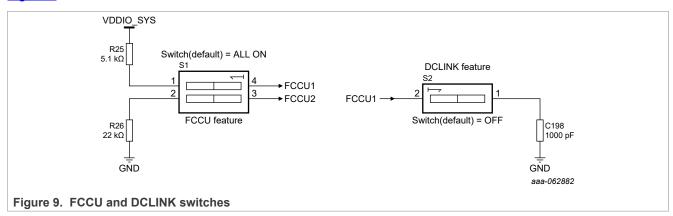

#### 5.3.5 FCCU and DCLINK switches

The FCCU switch S1 can be used to force the non-error state on the FCCU pins.

Note: SW7.6 and SW7.7 must be OFF.

**Note:** When SW7.6 and SW7.7 are ON, FCCU pins states are controlled by the FRDM-KL25Z board using the GUI in the "IO PINS" tab or with script commands.

The DCLINK switch S2 is meant to connect the DC LINK capacitive load to the FCCU1 pin.

Figure 9 shows related schematic.

Table 6. S1: FCCU switches

| Switch | Function                     | Description                                |

|--------|------------------------------|--------------------------------------------|

| 1      | Set FCCU1 to non-error state | Connects FCCU1 to a 5.1 kΩ pullup to VDDIO |

| 2      | Set FCCU2 to non-error state | Connects FCCU2 to a 22 kΩ pulldown to GND  |

Table 7. S2: DCLINK switch

| Position | Function                      | Description                    |

|----------|-------------------------------|--------------------------------|

| OFF      | Remove DCLINK load from FCCU1 | Disconnect C198 from FCCU1 pin |

| ON       | Connect DCLINK load to FCCU1  | Connect C198 to FCCU1 pin      |

KITFS27-24VEVM evaluation board

### 5.3.6 Quiescent current measurements

To perform quiescent current measurements, some switches must be turned off, and some components must be removed. All switches in SW7 and SW11 must be turned off to disable LED signaling.

Table 8. SW7: Signal switches

| Table 6. SW1. Signal Switches |                     |                           |  |  |

|-------------------------------|---------------------|---------------------------|--|--|

| Switch                        | Function            | Description               |  |  |

| 1                             | MCU_AMUX_SH switch  | Disconnects MCU_AMUX net  |  |  |

| 2                             | n.c.                |                           |  |  |

| 3                             | VDEBUG_SH switch    | Disconnects VDEBUG net    |  |  |

| 4                             | VDDIO_SYS_SH switch | Disconnects VDDIO_SYS net |  |  |

| 5                             | INTB_SH switch      | Disconnects INTB net      |  |  |

UM12355

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

Document feedback

## KITFS27-24VEVM evaluation board

Table 8. SW7: Signal switches...continued

| Switch | Function            | Description               |

|--------|---------------------|---------------------------|

| 6      | FCCU1_SH switch     | Disconnects FCCU1 net     |

| 7      | FCCU2_SH switch     | Disconnects FCCU2 net     |

| 8      | n.c.                | Not connected             |

| 9      | n.c.                | Not connected             |

| 10     | RSTB_SH switch      | Disconnects RSTB net      |

| 11     | FS0B/LIMP_SH switch | Disconnects FS0B/LIMP net |

| 12     | FS1B_SH switch      | Disconnects FS1B net      |

### Table 9. SW9: Communication switches

| Switch | Function           | Description              |

|--------|--------------------|--------------------------|

| 1      | CSB/SDA_SH switch  | Disconnects CSB/SDA net  |

| 2      | SCLK/SCL_SH switch | Disconnects SCLK/SCL net |

| 3      | MOSI/LVI_SH switch | Disconnects MOSI/LVI net |

| 4      | MISO/LVO_SH switch | Disconnects MISO/LVO net |

#### Table 10. SW11: Regulators switches

| Switch | Function                | Description                     |

|--------|-------------------------|---------------------------------|

| 1      | VBAT_SH switch          | Disconnects MCU_AMUX net        |

| 2      | FLYBACK_OUT_SH switch   | Disconnects FLYBACK_OUT net     |

| 3      | FLYBACK_OUT_2_SH switch | Disconnects FLYBACK_OUT_2 net   |

| 4      | VPRE_SH switch          | Disconnects VPRE net            |

| 5      | VCORE_SH switch         | Disconnects VCORE net           |

| 6      | VLDO1_SH switch         | Disconnects VLDO1 net           |

| 7      | VLDO2_SH switch         | Disconnects VLDO2 net           |

| 8      | VREF_SH switch          | Disconnects VREF net            |

| 9      | GPIO1_IN/OUT_SH switch  | Disconnects GPIO1_IN/OUT_SH net |

| 10     | VTRK2_SH switch         | Disconnects VTRK2 net           |

| 11     | VTRK1_SH switch         | Disconnects VTRK1 net           |

| 12     | GPIO2_PGOOD_SH switch   | Disconnects GPIO2_PGOOD net     |

KITFS27-24VEVM evaluation board

## 5.4 Jumpers

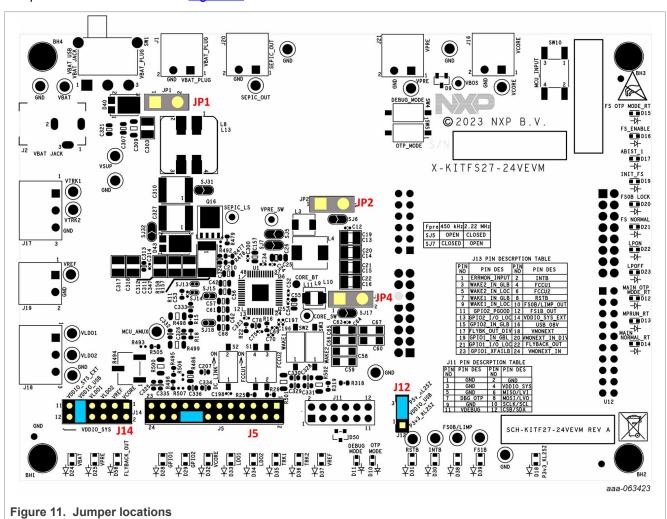

Jumper locations are shown in Figure 11.

Jumpers for current measurement are described in Table 11.

Other jumpers are described in the following sections.

Table 11. Jumpers for current measurement descriptions

| Name | Function                                             | Pin number | Note              |

|------|------------------------------------------------------|------------|-------------------|

| JP1  | FLYBACK regulator input inductor current measurement | 1-2        | SJ20 must be open |

| JP2  | VPRE regulator output inductor current measurement   | 1-2        | SJ6 must be open  |

| JP4  | VCORE regulator output inductor current measurement  | 1–2        | SJ17 must be open |

KITFS27-24VEVM evaluation board

#### 5.4.1 VDDIO selection

VDDIO pin (VDDIO SYS net) can be 1.8 V, 3.3 V, or 5.0 V, depending on the system requirements.

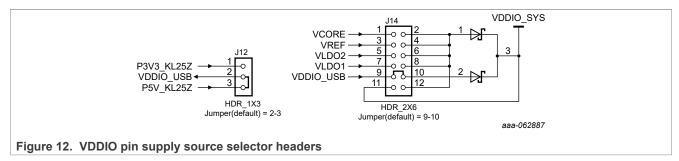

J14 shown in Figure 12 allows to connect VDDIO\_SYS to a device regulator, to a FRDM-KL25Z board rail from USB, or to an external source on VDDIO\_SYS\_EXT (J13.20).

J14 allows selection of the VDDIO\_SYS source, description is shown in Table 12.

The diodes are used to compose an OR supply, two jumpers can be placed on J14, so VDDIO\_SYS is supplied by VDDIO\_SUB and a regulator. As a result, the user can start the device in emulation mode, then disconnect the USB cable, without loosing the VDDIO\_SYS supply. The diodes prevent VDDIO\_USB from supplying the regulator output and the opposite.

The diodes can be bypassed if needed, but then only one supply is then allowed. Position 9-11 is used for VDDIO USB without diode, or any regulator position 1-2, 3-4, 5-6, 7-8 plus 11-12 to bypass the diode.

Table 12. J14: VDDIO\_SYS header

| 14510 12. 014. VBB10_010 1104401 |                                              |  |  |

|----------------------------------|----------------------------------------------|--|--|

| VDDIO_SYS source                 | VDDIO_SYS value                              |  |  |

| VCORE                            | VCORE regulator output voltage through diode |  |  |

| VREF                             | VREF regulator output voltage through diode  |  |  |

| VLDO1                            | LDO1 regulator output voltage through diode  |  |  |

| VLDO2                            | LDO2 regulator output voltage through diode  |  |  |

| VDDIO_USB                        | VDDIO_USB (see J12) through diode            |  |  |

| VDDIO_USB                        | VDDIO_USB (see J12) without diode            |  |  |

| VDDIO_SYS_EXT                    | 1-2, 3-4, 5-6, 7-8 diode bypass              |  |  |

|                                  | VCORE VREF VLDO1 VLDO2 VDDIO_USB VDDIO_USB   |  |  |

J12 allows selection of the VDDIO USB source. The description is shown in Table 13.

Table 13. J12: VDDIO\_USB header

| Jumper position | VDDIO_USB source | VDDIO_USB value |

|-----------------|------------------|-----------------|

| 1-2             | P3V3_KL25Z       | 3.3 V           |

| 2-3 (default)   | P5V_KL25Z        | 5.0 V           |

KITFS27-24VEVM evaluation board

## 5.4.2 VMONEXT: external voltage monitoring

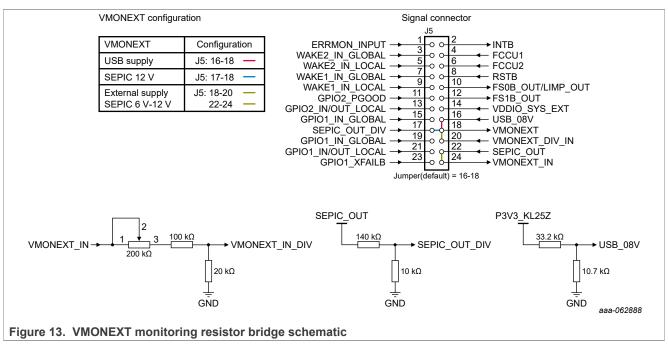

The VMONEXT monitoring pin can monitor 0.8 V and 5.0 V targets. The kit-related scheme is show in Figure 13.

VMONEXT pin can be connected to multiple sources thought J5 shown in <u>Table 14</u>, such as FLYBACK regulator at 12 V with a fixed resistor bridge, the line VMONEXT\_IN in a range from 6.0 V to 12 V with a variable resistor bridge, FRDM-KL25Z board 3.3 V rail with a fixed external resistor bridge (for debug purposes). VMONEXT\_IN can be connected to FLYBACK OUT.

VMONEXT\_IN can be connected to any source or regulator, the variable external bridge must adjusted using a screwdriver on potentiometer. The VMONEXT voltage should around 0.8 V when enabled.

Table 14. J5: Signal connector header (VMONEXT highlight)

| Jumper position | VMONEXT source | VMONEXT value                                                           |

|-----------------|----------------|-------------------------------------------------------------------------|

| 16-18           | USB supply     | 0.8 V for evaluation (no error)                                         |

| 17-18           | FLYBACK_OUT    | FLYBACK regulator at 12 V                                               |

| 18-20<br>22-24  | FLYBACK_OUT    | FLYBACK regulator from 6.0 V to 12 V, adjustable with variable resistor |

KITFS27-24VEVM evaluation board

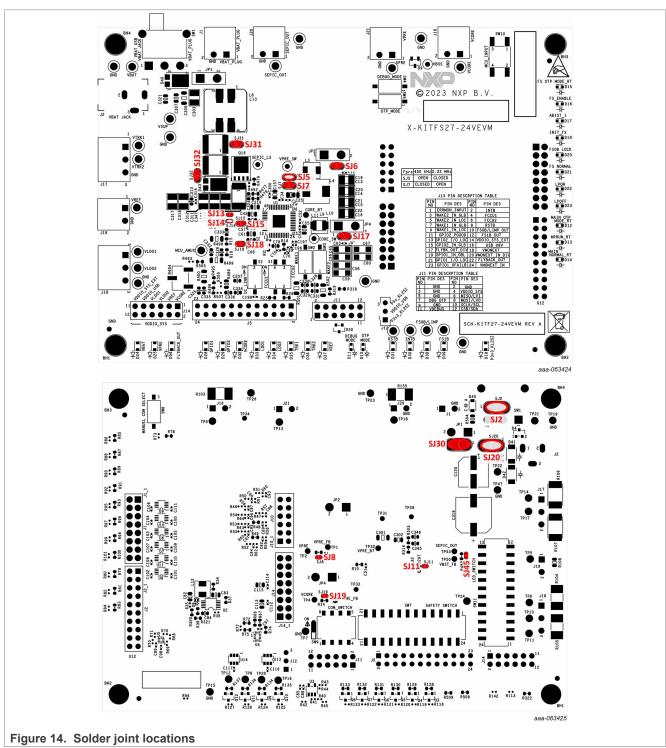

## 5.5 Solder joints

Solder joint locations are shown in Figure 14.

## KITFS27-24VEVM evaluation board

Solder joints are described in <u>Table 15</u>.

#### Table 15. Solder joints descriptions

| Name | Function                                                                              |        | Note              |

|------|---------------------------------------------------------------------------------------|--------|-------------------|

| SJ2  | Bypass SW1: VBAT connected to J1                                                      |        | _                 |

| SJ6  | Bypass JP2: jumper for VPRE regulator output inductor current measurement             | Closed | _                 |

| SJ7  | Connect VPRE_SW to L4 (inductor F <sub>PRE</sub> = 444 kHz)                           | Closed | SJ5 must be open  |

| SJ8  | Bypass R4: resistor for VPRE regulator stability measurement                          | Closed | -                 |

| SJ11 | Connect GPIO2 pin to GPIO2 input/output external components                           | Closed | _                 |

| SJ13 | Connect GPIO1 pin to GPIO1 input/output external components                           | Closed | SJ14 must be open |

| SJ14 | Connect GPIO1 pin to GPIO1 XFAILB components                                          | Open   | SJ13 must be open |

| SJ15 | Connect VPRE regulator output to TRKIN pin                                            | Closed | _                 |

| SJ17 | Bypass JP4: jumper for VCORE regulator output inductor current measurement            |        | _                 |

| SJ18 | Connect VPRE regulator output to LDOIN pin                                            |        | _                 |

| SJ19 | Bypass R14: resistor for VCORE regulator stability measurement                        |        | _                 |

| SJ20 | Bypass D40: VBAT reverse protection diode                                             |        | _                 |

| SJ30 | Bypass JP1: jumper for FLYBACK regulator primary (input) inductor current measurement |        | _                 |

| SJ32 | Opens FLYBACK regulator output diode for current measurement                          |        | _                 |

| SJ45 | Bypass R482: resistor for FLYBACK regulator stability measurement                     |        | _                 |

| SJ46 | Opens FLYBACK coupled inductor ground connection for secondary current measurement    |        | _                 |

| SJ47 | Bypass Q21: VBAT and BATSENSE clamp transistor                                        | Closed | _                 |

KITFS27-24VEVM evaluation board

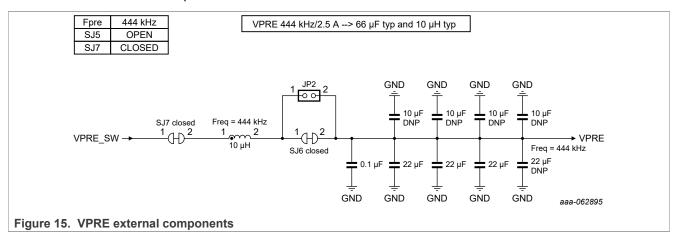

## 5.5.1 VPRE external components

This board is delivered with VPRE external components for 444 kHz. JP2 can be used for inductor current measurements when SJ6 is open.

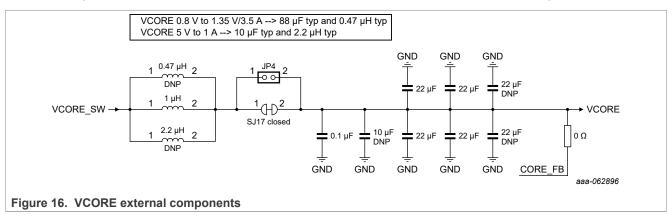

### 5.5.2 VCORE external components

This board is delivered with VCORE external components (inductor 0.47 uH, output capacitor 4x 88 uF) for 0.8 V to 1.35 V up to 3.5 A. JP4 can be used for inductor current measurements when SJ17 is open.

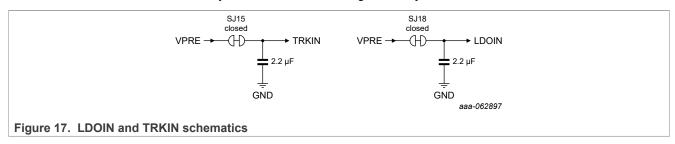

### 5.5.3 LDOIN and TRKIN connection

LDOIN and TRKIN are connected by default to VPRE through solder joints.

UM12355

KITFS27-24VEVM evaluation board

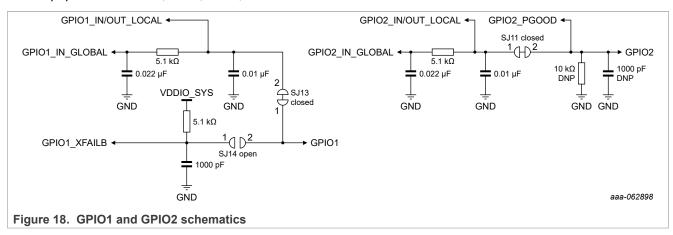

#### 5.5.4 GPIO1 and GPIO2

The GPIO1 and GPIO2 can be used as output, local input and global input (default).

Jumpers J52 and J51 headers, shown in <u>Figure 18</u>, allow to choose between input and output external components.

**Note:** If the internal pullups or pulldowns are not enabled or are not strong enough, external pullups/pulldowns can be populated on R110, R111, R109, and R469.

All input/output access points are available at J13.

**Note:** The external pullups and pulldowns for the GPIO are not populated. If the internal pullups or pulldowns are not enabled by OTP, the user can add external PU/PD through J13.

KITFS27-24VEVM evaluation board

### 5.6 Connectors

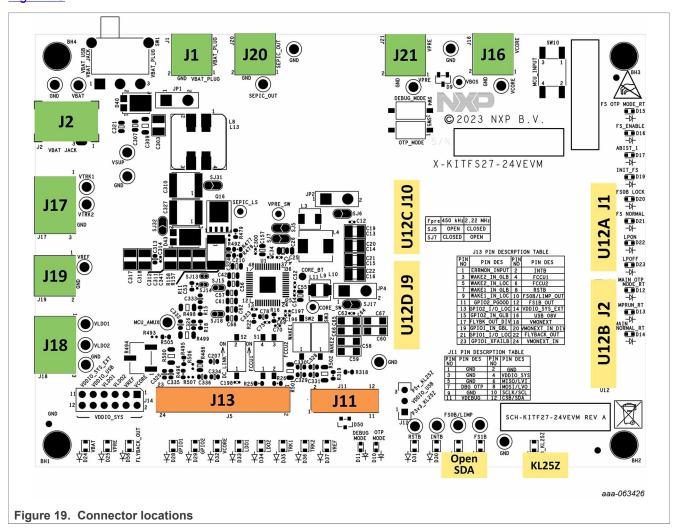

Figure 19 shows the location of connectors on the board.

Table 16. J1: VBAT Phoenix connector

| Pin | Signal name | Description                  |

|-----|-------------|------------------------------|

| 1   | VBAT        | Battery voltage supply input |

| 2   | GND         | Ground                       |

### KITFS27-24VEVM evaluation board

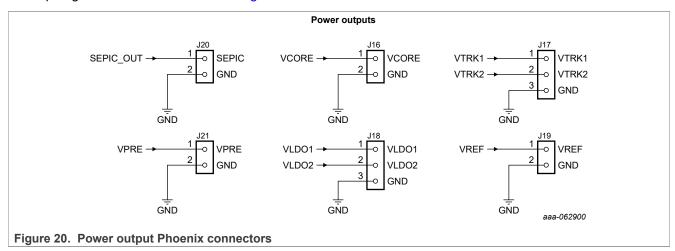

## 5.6.1 Output power supply connectors

Output regulators are accessible through test points and Phoenix connectors to make measurement or plug loads. Male connectors are included on this kit to plug or unplug wires easily. All output regulators are at the left and top edge of the board as shown in Figure 20.

Table 17. J20: FLYBACK connector

| Pin | Signal name | Description              |

|-----|-------------|--------------------------|

| 1   | FLYBACK_OUT | FLYBACK regulator output |

| 2   | GND         | Ground                   |

Table 18. J21: VPRE connector

| Pin | Signal name | Description           |

|-----|-------------|-----------------------|

| 1   | VPRE        | VPRE regulator output |

| 2   | GND         | Ground                |

Table 19. J16: VCORE connector

| Pin | Signal name | Description            |

|-----|-------------|------------------------|

| 1   | VCORE       | VCORE regulator output |

| 2   | GND         | Ground                 |

Table 20. J18: VLDO1/VLDO2 connector

| Pin | Signal name | Description           |

|-----|-------------|-----------------------|

| 1   | LDO1        | LDO1 regulator output |

| 2   | LDO2        | LDO2 regulator output |

| 3   | GND         | Ground                |

## KITFS27-24VEVM evaluation board

### Table 21. J17: VTRK1/VTRK2 connector

| Pin | Signal name | Description            |

|-----|-------------|------------------------|

| 1   | VTRK1       | VTRK1 regulator output |

| 2   | VTRK2       | VTRK2 regulator output |

| 3   | GND         | Ground                 |

#### Table 22. J19: VREF connector

| Pin | Signal name | Description           |

|-----|-------------|-----------------------|

| 1   | VREF        | VREF regulator output |

| 2   | GND         | Ground                |

KITFS27-24VEVM evaluation board

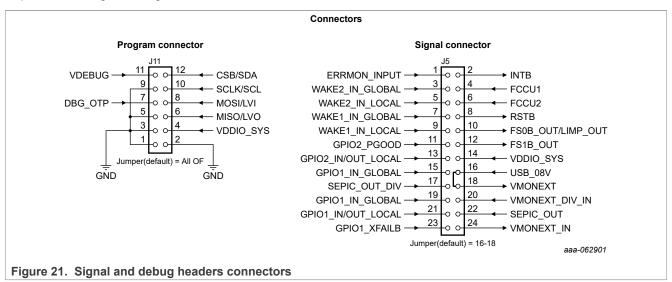

## 5.6.2 Signal and program connectors

Signal and program connectors provide access to most of the device signals to program the device externally or to perform debug and diagnosis.

Table 23. J11: Program connector

| Pin | Signal name | Description                         |

|-----|-------------|-------------------------------------|

| 1   | GND         | Ground                              |

| 2   | GND         | Ground                              |

| 3   | GND         | Ground                              |

| 4   | VDDIO_SYS   | VDDIO pin access                    |

| 5   | GND         | Ground                              |

| 6   | MISO/LVO    | MOSI/LVO pin access                 |

| 7   | DBG_OTP     | DBG_OTP power supply (7.8 V) access |

| 8   | MOSI/LVI    | MOSI/LVI pin access                 |

| 9   | GND         | Ground                              |

| 10  | SCLK/SCL    | SCLK/SCL pin access                 |

| 11  | VDEBUG      | DEBUG pin voltage                   |

| 12  | CSB/SDA     | CSB/SDA pin access                  |

Table 24. J13: Signal connector

| Pin | Signal name     | Description                                                   |

|-----|-----------------|---------------------------------------------------------------|

| 1   | ERRMON_INPUT    | Error monitoring (WAKE2 pin) input                            |

| 2   | INTB            | Interrupt output for MCU                                      |

| 3   | WAKE2_IN_GLOBAL | WAKE2 input connection when used as a global input            |

| 4   | FCCU1           | FCCU1 pin access                                              |

| 5   | WAKE2_IN_LOCAL  | WAKE2 input connection (WAKE2 pin) when used as a local input |

UM12355

## KITFS27-24VEVM evaluation board

Table 24. J13: Signal connector...continued

| Pin | Signal name        | Description                                                                             |

|-----|--------------------|-----------------------------------------------------------------------------------------|

| 6   | FCCU2              | FCCU2 pin access                                                                        |

| 7   | WAKE1_IN_GLOBAL    | WAKE1 input connection when used as a global input                                      |

| 8   | RSTB               | Reset output for MCU                                                                    |

| 9   | WAKE1_IN_LOCAL     | WAKE1 input connection (WAKE1 pin) when used as a local input                           |

| 10  | FS0B_OUT/LIMP_OUT  | Safety output 0 (FS0B pin) access                                                       |

| 11  | GPIO2_PGOOD        | GPIO2 access (GPIO2 pin) when used as PGOOD                                             |

| 12  | FS1B_OUT           | Safety output 1 (FS1B pin) access                                                       |

| 13  | GPIO2_IN/OUT_LOCAL | GPIO2 access (GPIO2 pin) when used as local input or output                             |

| 14  | VDDIO_SYS_EXT      | Optional external supply for VDDIO. A jumper between J14 11-12 pins is required         |

| 15  | GPIO2_IN_GLOBAL    | GPIO2 access (GPIO2 pin) when used as global input                                      |

| 16  | USB_08V            | 0.8 V regulator                                                                         |

| 17  | FLYBACK_OUT_DIV    | FLYBACK regulator voltage divider 15:1. Connect to VMONEXT when FLYBACK is set to 12 V. |

| 18  | VMONEXT            | External voltage monitoring (VMONEXT pin) access                                        |

| 19  | GPIO1_IN_GLOBAL    | GPIO1 access (GPIO1 pin) when used as global input                                      |

| 20  | VMONEXT_IN_DIV     | VMONEXT adjustable divider output. Connect to VMONEXT and input at VMONEXT_IN.          |

| 21  | GPIO1_IN/OUT_LOCAL | GPIO1 access (GPIO1 pin) when used as local input or output                             |

| 22  | FLYBACK_OUT        | FLYBACK regulator output                                                                |

| 23  | GPIO1_XFAILB       | GPIO1 access (GPIO1 pin) when used as XFAILB                                            |

| 24  | VMONEXT_IN         | VMONEXT adjustable divider input                                                        |

## KITFS27-24VEVM evaluation board

### 5.6.3 FRDM-KL25Z board connectors

### Table 25. FRDM-KL25Z board USB connectors

| Schematic label | Signal name | Description                                    |

|-----------------|-------------|------------------------------------------------|

| FRDM-KL25Z      | N/A         | USB connector used to communicate with the GUI |

| OpenSDA         | N/A         | USB connector used to flash the KL25Z MCU      |

### Table 26. U12A: FRDM-KL25Z board safety outputs, IOs, and SPI connector

| Pin | Signal name      | Description                                   |

|-----|------------------|-----------------------------------------------|

| 1   | SPI_MISO_MCU     | SPI MISO connection to KL25Z                  |

| 2   | LVI_MCU          | LVI connection to KL25Z                       |

| 3   | MCU_COM_CTRL     | Not connected                                 |

| 4   | RSTB_MCU         | Reset sense to KL25Z (active low-logic level) |

| 5   | n.c.             | Not connected                                 |

| 6   | n.c.             | Not connected                                 |

| 7   | SPI_CSB_MCU      | SPI CSB connection to KL25Z                   |

| 8   | n.c.             | Not connected                                 |

| 9   | SPI_SCLK_MCU     | SPI SCLK connection to KL25Z                  |

| 10  | FS0B/LIMP_MCU    | FS0B/LIMP sense connection to KL25Z           |

| 11  | SPI_MOSI_MCU     | SPI MOSI connection to KL25Z                  |

| 12  | INTB_MCU         | Interruption (active low-logic level)         |

| 13  | n.c.             | Not connected                                 |

| 14  | n.c.             | Not connected                                 |

| 15  | LVO_MCU          | LVO sense connection to KL25Z                 |

| 16  | INPUT_BUTTON_MCU | Button SW10 connection to KL25Z               |

## Table 27. U12B: FRDM-KL25Z board I<sup>2</sup>C, FCCU, and main states M\_STATEx connector

| Pin    | Signal name | Description                                            |

|--------|-------------|--------------------------------------------------------|

| 1      | FCCU1_MCU   | FCCU1 connection to KL25Z                              |

| 3      | FCCU2_MCU   | FCCU2 connection to KL25Z                              |

| 6      | M_STATE0    | MCU output for LED D12 - MAIN_OTP_MODE_RT              |

| 8      | M_STATE1    | MCU output for LED D13 - LPRUN_RT                      |

| 10     | M_STATE2    | MCU output for LED D14 - MAIN_NORMAL_RT                |

| 14     | GND         | Ground                                                 |

| 18     | I2C_SDA_MCU | I <sup>2</sup> C serial data line connection to KL25Z  |

| 20     | I2C_SCL_MCU | I <sup>2</sup> C serial clock line connection to KL25Z |

| Others | n.c.        | Not connected                                          |

KITFS27-24VEVM evaluation board

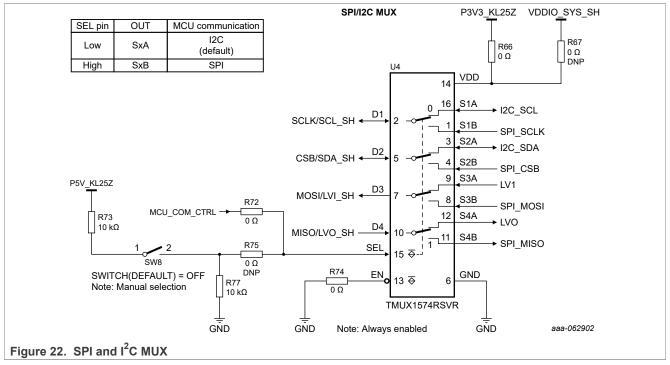

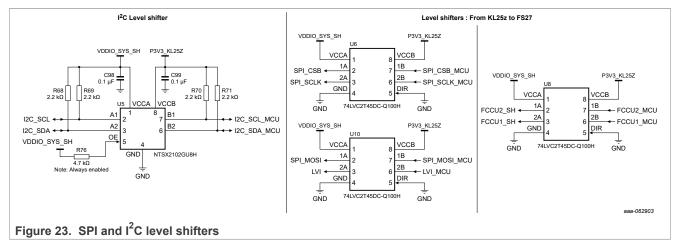

<u>Figure 22</u> shows the MUX used to split SPI and I<sup>2</sup>C signals. The communication protocol is selected automatically by the GUI using the FRDM-KL25Z board output MCU\_COM\_CTRL.

Figure 23 shows the level shifters used to connected SPI and I<sup>2</sup>C signals to the FRDM-KL25Z board inputs.

Table 28. U12C: FRDM-KL25Z board ADC connector

| Table 20. 0 120. I Rolli-Re202 board Abo connector |             |                                    |

|----------------------------------------------------|-------------|------------------------------------|

| Pin                                                | Signal name | Description                        |

| 1                                                  | VLDO2_ADC   | LDO2 regulator output to KL25Z ADC |

| 2                                                  | VPRE_ADC    | VPRE regulator output to KL25Z ADC |

| 3                                                  | VREF_ADC    | VREF regulator output to KL25Z ADC |

| 4                                                  | n.c.        | Not connected                      |

| 5                                                  | VTRK1_ADC   | TRK1 regulator output to KL25Z ADC |

| 6                                                  | VDEBUG_ADC  | DEBUG pin voltage to KL25Z ADC     |

| 7                                                  | VTRK2_ADC   | TRK2 regulator output to KL25Z ADC |

|                                                    |             |                                    |

UM12355

#### KITFS27-24VEVM evaluation board

Table 28. U12C: FRDM-KL25Z board ADC connector...continued

| Pin | Signal name   | Description                         |

|-----|---------------|-------------------------------------|

| 8   | VDDIO_SYS_ADC | VDDIO pin voltage to KL25Z ADC      |

| 9   | n.c.          | Not connected                       |

| 10  | AMUX_ADC      | AMUX_MCU voltage to KL25Z ADC       |

| 11  | VCORE_ADC     | VCORE regulator output to KL25Z ADC |

| 12  | VLDO1_ADC     | LDO1 regulator output to KL25Z ADC  |

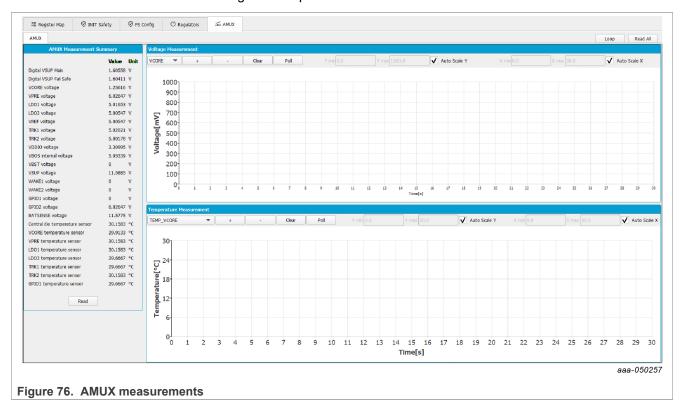

The measurements related to the AMUX are accessible on "ACCESS" > "AMUX".

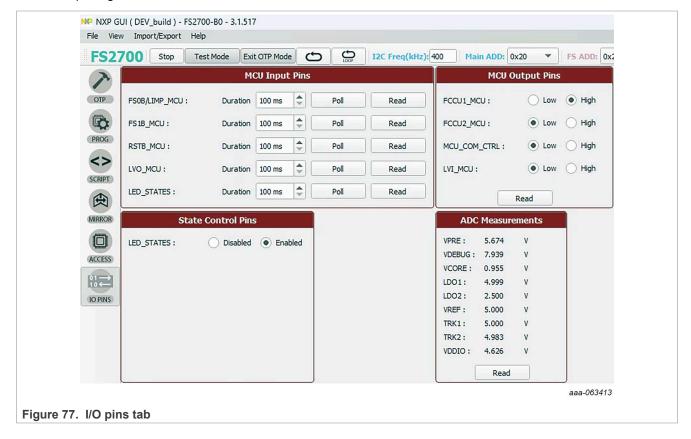

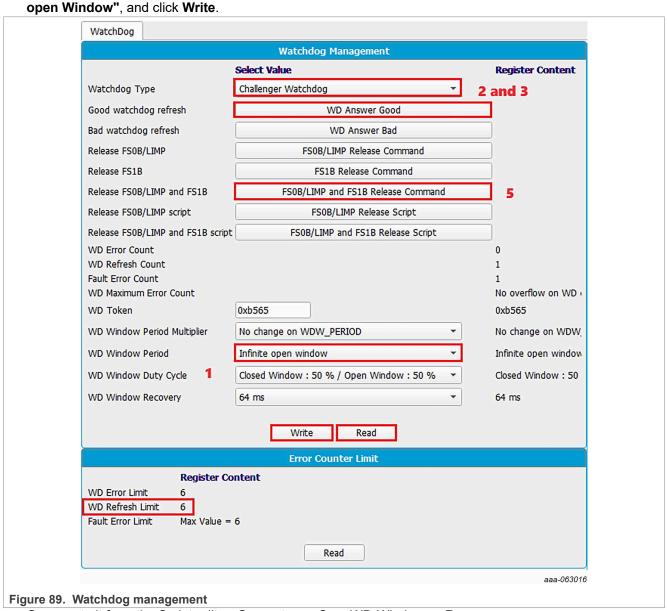

The measurements performed by the FRDM-KL25Z board are accessible on "IO PINS" > "ADC Measurements".

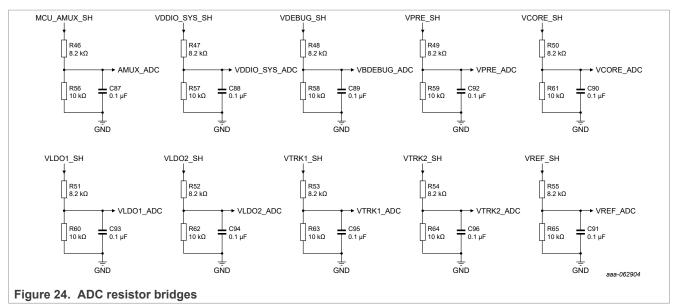

Figure 24 shows the resistors bridge connected to Table 28.

Table 29. U12D: FRDM-KL25Z board supply and fail-safe states FS\_STATEx connector

| Pin | Signal name     | Description                               |

|-----|-----------------|-------------------------------------------|

| 1   | FS_STATE0       | MCU output for LED D15 - FS_OTP_MODE_RT   |

| 2   | n.c.            | Not connected                             |

| 3   | FS_STATE1       | MCU output for LED D16 - FS_ENABLE/ABIST  |

| 4   | P3V3_FRDM-KL25Z | 3.3 V generated from FRDM-KL25Z board USB |

| 5   | FS_STATE2       | MCU output for LED D17 - FS_DBG_MODE_RT   |

| 6   | n.c.            | Not connected                             |

| 7   | FS_STATE3       | MCU output for LED D19 - INIT_FS          |

| 8   | P3V3_FRDM-KL25Z | 3.3 V generated from FRDM-KL25Z board USB |

| 9   | FS_STATE4       | MCU output for LED D20 - FS0B_LOCK        |

| 10  | P5V_FRDM-KL25Z  | 5.0 V from FRDM-KL25Z board USB           |

| 11  | FS_STATE5       | MCU output for LED D21 - FS_NORMAL        |

| 12  | GND             | Ground                                    |

UM12355

## KITFS27-24VEVM evaluation board

Table 29. U12D: FRDM-KL25Z board supply and fail-safe states FS\_STATEx connector...continued

| Pin | Signal name | Description                    |

|-----|-------------|--------------------------------|

| 13  | FS_STATE6   | MCU output for LED D22 - LPON  |

| 14  | GND         | Ground                         |

| 15  | FS_STATE7   | MCU output for LED D23 - LPOFF |

| 16  | n.c.        | Not connected                  |

KITFS27-24VEVM evaluation board

## 5.7 LED indicators

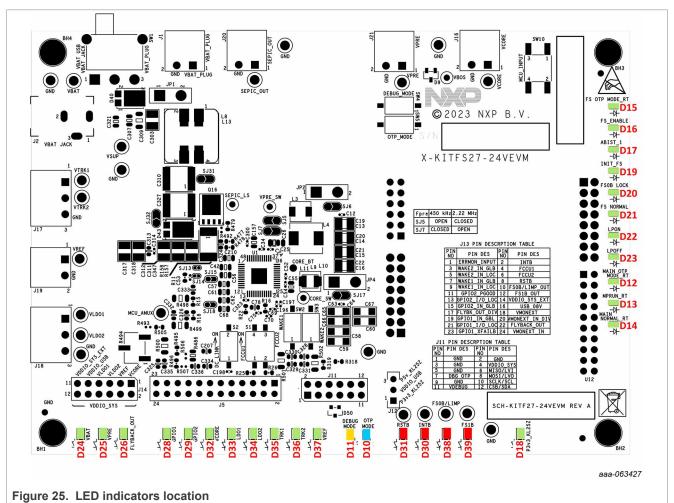

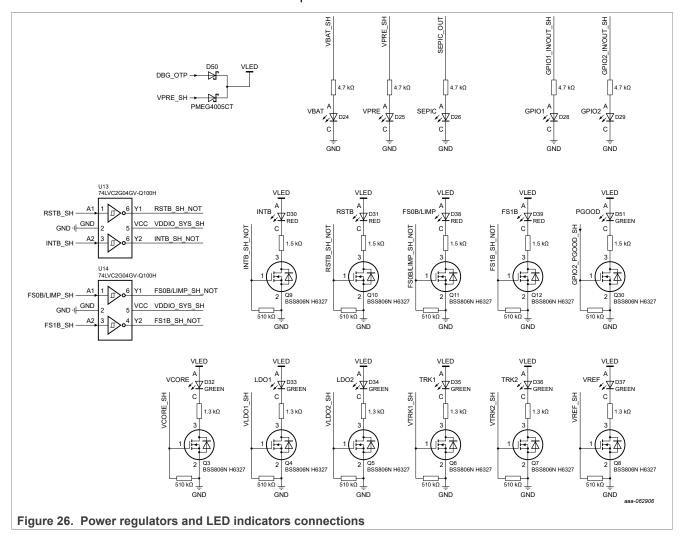

LED indicators present on the board display the status of VBAT, regulators, safety outputs, GPIOs, and device state machines (FSM) states. LEDs are green for VBAT, regulators, and GPIOs, indicating that the rail is powered on. LEDs are green for FSM states. LEDs are red for safety outputs and interrupt, indicating when the pins are asserted.

Figure 25 shows LED indicators location.

The general indicators are listed in <u>Table 30</u>.

Table 30. Safety IO's indicators description

| Label | Name      | Color | Description                   |

|-------|-----------|-------|-------------------------------|

| D30   | INTB      | Red   | INTB pin state indicator      |

| D31   | RSTB      | Red   | RSTB pin state indicator      |

| D38   | FS0B/LIMP | Red   | FS0B/LIMP pin state indicator |

| D39   | FS1B      | Red   | FS1B pin state indicator      |

| D51   | PGOOD     | Green | PGOOD pin state indicator     |

The supply indicators are listed in **Table 31**.

### KITFS27-24VEVM evaluation board

Table 31. Supply indicators description

| Label | Name       | Color  | Description                                 |

|-------|------------|--------|---------------------------------------------|

| D10   | OTP mode   | Blue   | DEBUG pin voltage ≥ 7.8 V (OTP programming) |

| D11   | DEBUG mode | Yellow | DEBUG pin voltage ≥ 3.5 V (debug mode)      |

| D18   | P3V3_KL25Z | Green  | FRDM-KL25Z board 3.3 V rail indicator       |

| D24   | VBAT       | Green  | VBAT rail led                               |

The regulators and GPIOs indicators are listed in Table 32.

Table 32. Regulators and GPIO indicators description

| Label | Name        | Color | Description                        |

|-------|-------------|-------|------------------------------------|

| D25   | VPRE        | Green | VPRE regulator output indicator    |

| D26   | FLYBACK_OUT | Green | FLYBACK regulator output indicator |

| D28   | GPIO1       | Green | GPIO1 pin state indicator          |

| D29   | GPIO2       | Green | GPIO2 pin state indicator          |

| D32   | VCORE       | Green | VCORE regulator output indicator   |

| D33   | LDO1        | Green | LDO1 regulator output indicator    |

| D34   | LDO2        | Green | LDO2 regulator output indicator    |

| D35   | TRK1        | Green | TRK1 regulator output indicator    |

| D36   | TRK2        | Green | TRK2 regulator output indicator    |

| D37   | VREF        | Green | VREF regulator output indicator    |

The states indicators of the two state machines are listed in <u>Table 33</u>. These indicators can be disabled using the GUI on "IO PINS" > "State Control Pins" > LED\_STATES.

Table 33. Main/fail-safe state machines state indicators description

| Label | Name             | Color | Description                                                                                                                                                                                                      |

|-------|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15   | FS_OTP_MODE_RT   | Green | Fail-safe state machine in FS_OTP_MODE_RT (FS_OTP_MODE_RT = 1)                                                                                                                                                   |

| D16   | FS_ENABLE/ABIST  | Green | Fail-safe state machine in:  FS_ENABLE, when main state machine in LPRUN mode or,  waiting ABIST start, if the OTP_MODE switch is ON, or,  RSTB is asserted externally (blinking), if the OTP_MODE switch is ON. |

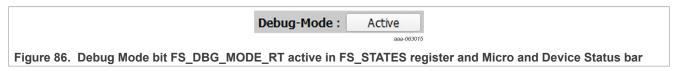

| D17   | FS_DBG_MODE_RT   | Green | Fail-safe state machine DEBUG mode is active (FS_DBG_MODE_RT = 1)                                                                                                                                                |

| D19   | INIT_FS          | Green | Fail-safe state machine in INIT_FS. Fail-safe state machine in MCU flash mode (blinking).                                                                                                                        |

| D20   | FS0B_LOCK        | Green | Fail-safe state machine in FS0B_LOCK                                                                                                                                                                             |

| D21   | FS_NORMAL        | Green | Fail-safe state machine in FS_NORMAL                                                                                                                                                                             |

| D22   | LPON             | Green | Main state machine in LPON (standby) mode                                                                                                                                                                        |

| D23   | LPOFF            | Green | Main state machine in LPOFF mode                                                                                                                                                                                 |

| D12   | MAIN_OTP_MODE_RT | Green | Main state machine in OTP mode (MAIN_OTP_MODE_RT = 1)                                                                                                                                                            |

| D13   | LPRUN_RT         | Green | Main state machine in LPRUN_RT (LPRUN_RT = 1)                                                                                                                                                                    |

| D14   | MAIN_NORMAL_RT   | Green | Main state machine in MAIN_NORMAL (MAIN_NORMAL_RT = 1)                                                                                                                                                           |

| All   | All              | Green | Wake-up from deep fail-safe (blink 2x 2 times with shift)                                                                                                                                                        |

The LED indicators supply is VLED, taken from the USB generated DBG\_OTP supply when the USB is connected, otherwise from VPRE, when powered on. This arrangement allows the LEDs to be powered on when VPRE is off.

### KITFS27-24VEVM evaluation board

These LEDs can be disconnected manually at any time with the switch SW7 and SW11 to avoid undesired losses and obtain more accurate current consumption measurements.

KITFS27-24VEVM evaluation board

## 5.8 Test points

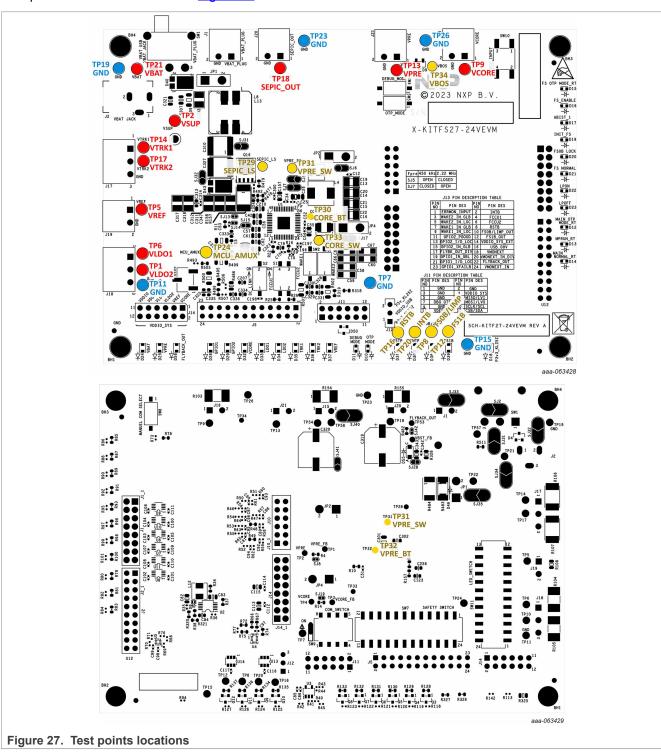

Test point locations are shown in Figure 27.

### KITFS27-24VEVM evaluation board

The test points are color coded:

- · Orange: Test loop access to device signals, such as safety outputs, analog pins, and regulator switch nodes.

- Red: Test loop access for power supplies.

- Black: Test loop access to GND.

- Dark orange: Test pad access to regulator bootstrap capacitor.

The test points connections as shown in Figure 28.

Table 34. Test points description

| Test point name | Signal name | Description                                |

|-----------------|-------------|--------------------------------------------|

| TP5             | VREF        | VREF regulator output (VREF pin) access    |

| TP6             | VLDO1       | LDO1 regulator output (LDO1OUT pin) access |

| TP7             | GND         | Ground                                     |

| TP8             | FS0B/LIMP   | FS0B/LIMP pin access                       |

| TP9             | VCORE       | VCORE regulator output access              |

| TP10            | VLDO2       | LDO2 regulator output (LDO2OUT pin) access |

| TP11            | GND         | Ground                                     |

| TP12            | FS1B        | FS0B pin access                            |

| TP13            | VPRE        | VPRE regulator output (VPRE_FB pin) access |

| TP14            | VTRK1       | TRK1 regulator output (TRK1 pin) access    |

| TP15            | GND         | Ground                                     |

| TP16            | RSTB        | RSTB pin access                            |

| TP17            | VTRK2       | TRK2 regulator output (TRK2 pin) access    |

| TP18            | FLYBACK_OUT | FLYBACK regulator primary output access    |

| TP19            | GND         | Ground                                     |

| TP20            | INTB        | INTB pin access                            |

| TP21            | VBAT        | VBAT access                                |

## KITFS27-24VEVM evaluation board

Table 34. Test points description...continued

| Test point name | Signal name | Description                                            |

|-----------------|-------------|--------------------------------------------------------|

| TP22            | VSUP        | VSUP pin access                                        |

| TP23            | GND         | Ground                                                 |

| TP24            | MCU_AMUX    | MCU_AMUX signal access                                 |

| TP26            | GND         | Ground                                                 |

| TP27            | GND         | Ground                                                 |

| TP28            | FLYBACK_LS  | FLYBACK regulator low-side MOSFET drain access         |

| TP30            | CORE_BT     | VCORE regulator bootstrap pin (CORE_BT pin) access     |

| TP31            | VPRE_SW     | VPRE regulator switching node (VPRE_SW pin) access     |

| TP32            | VPRE_BT     | VPRE regulator bootstrap pin (VPRE_BT pin) access      |

| TP33            | CORE_SW     | VCORE regulator switching node (CORE_SW1/2 pin) access |

| TP34            | VBOS        | VBOS pin access                                        |

KITFS27-24VEVM evaluation board

# 6 Installing and configuring software tools

The software tools are available on <a href="http://www.nxp.com/NXP GUI for Automotive PMIC Families">http://www.nxp.com/NXP GUI for Automotive PMIC Families</a> or from our "Secure Files" portal at <a href="https://www.nxp.com/mynxp/secure-files">https://www.nxp.com/mynxp/secure-files</a> if device is not in production.

The NXP GUI for Automotive PMICs Families is delivered with the EVB firmware. The EVB firmware allows the GUI to connect the device in the EVB, providing access to all device features.

The EVBs are always delivered with the BOOTLOADER and firmware flashed, and if no firmware update is required, these steps can be ignored.

If the firmware is malfunctioning or must be updated, follow the instructions in the next section.

## 6.1 Flashing or updating the Freedom board firmware on Windows 7/10/11

The Freedom board firmware is composed of two items: the BOOTLOADER (\*.SDA) and the firmware file (\*.bin).

If the FRDM-KL25Z board is already operational, that is, the GUI is capable to communicate with the EVB, the BOOTLOADER is installed, so only firmware updated might be required.

### 6.1.1 BOOTLOADER installation steps

BOOTLOADER installation steps are:

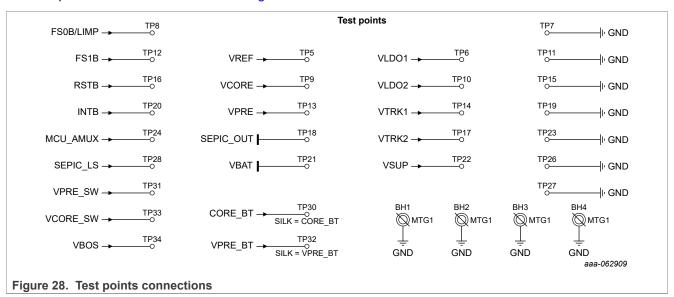

1. Disable the Storage Service and Windows Search: Run Services, double-click, and stop them as shown in Figure 29.

- 2. Press the RST button and connect the USB cable to the SDA port on the Freedom Board.

- A new BOOTLOADER device appears on the left pane of the File Explorer.

- Drag and drop the specific file "MSD-DEBUG-FRDM-KL25Z\_Pemicro\_v118.SDA" to the BOOTLOADER drive.

- Ensure that there is enough time for the firmware to be saved in the BOOTLOADER.

- 4. Disconnect the USB cable from the SDA port.

KITFS27-24VEVM evaluation board

## 6.1.2 Firmware installation/update steps

Firmware installation/update steps are:

- 1. WITHOUT pressing the RST button, connect the USB cable to the SDA port on the Freedom Board.

- The FRDM-KL25Z device appears on the left pane of the File Explorer as pictured in Figure 30.

- 2. Locate the **<device>** specific file with the required **<revision>** from the package, such as "nxp-gui-fw-frdm-kl25z-usb\_hid-<device>\_<revision>.bin".

- 3. Drag and drop this file into the FRDM-KL25Z device.

- Ensure that there is enough time for the firmware to be saved.

- The Freedom board firmware is successfully loaded.

- 4. Disconnect the USB-cable

### KITFS27-24VEVM evaluation board

# 6.2 Installing the NXP GUI software package

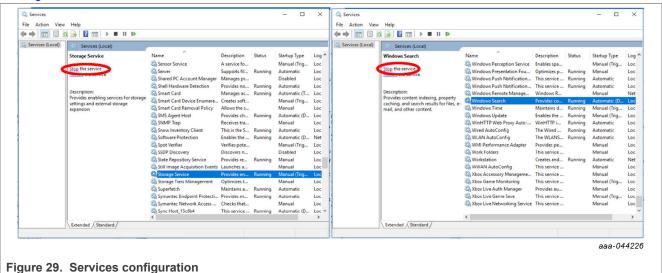

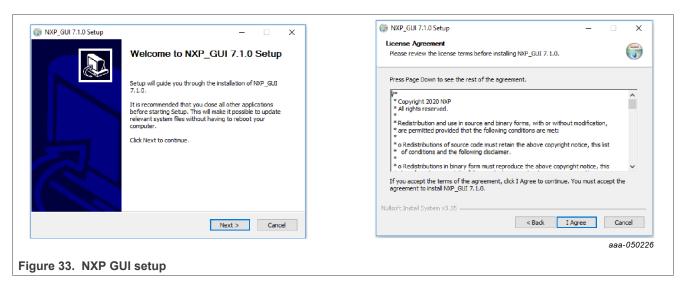

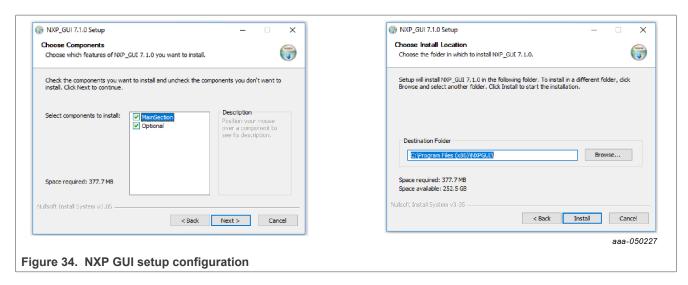

To install the FS2700-B0 NXP GUI, download or obtain the NXP GUI package, unzip an open 1-NXP GUI Setup folder:

Then double-click on the NXP\_GUI\_version-Setup.exe and follow the instructions.

To install the application on a Windows PC, proceed with the following pop-up windows:

#### KITFS27-24VEVM evaluation board

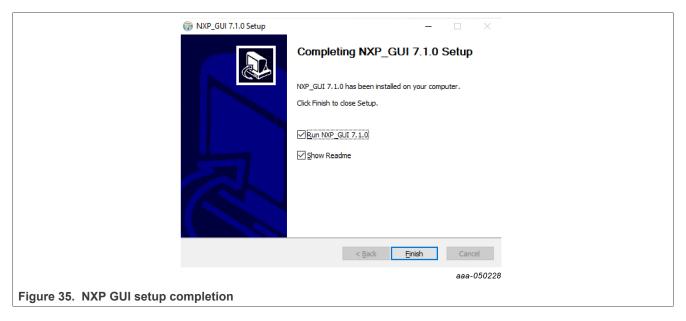

Select the following options before completing the installation of the setup:

- Run NXP GUI

- Show Readme

Select Finish to complete the installation.

When the installation is finished, find the application by searching for *NXPGUI* in the Windows search bar. Click to launch.

KITFS27-24VEVM evaluation board

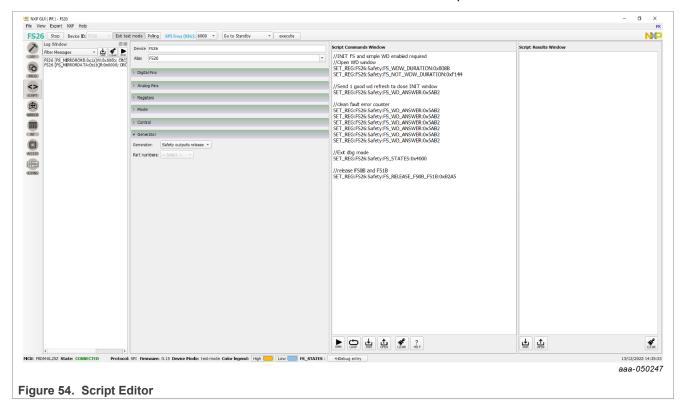

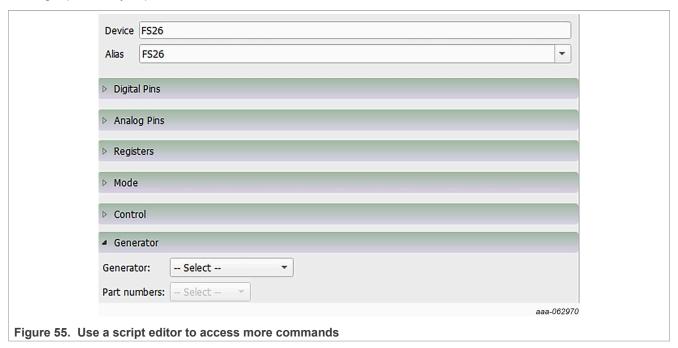

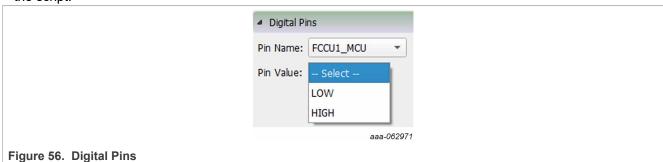

# 7 Using the FS2700-B0 NXP GUI for Automotive PMIC Families

To follow the steps in this section, ensure that the board is connected using the appropriate hardware configuration.

Always use the latest version of the NXP GUI for Automotive PMIC Families.

## 7.1 Starting the FS2700-B0 NXP GUI for Automotive PMIC Families

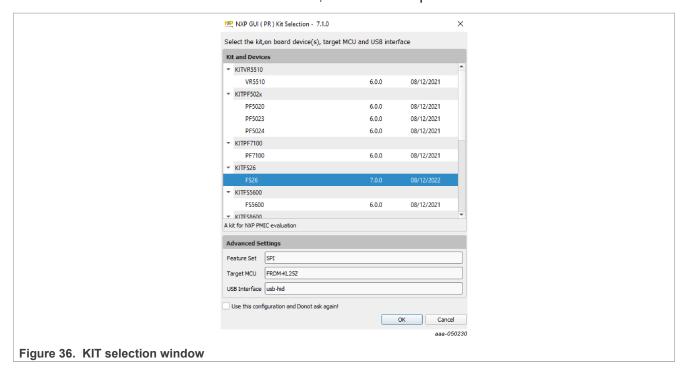

When the kit is ready and the NXP GUI for Automotive PMIC Families is installed, click to launch the kit from the Windows search bar. When the pop-up window appears, choose **FS2700-B0** and click **OK**.

To avoid the kit selection window on every launch, check the "Use this configuration and do not ask again" box.

To show the kit selection window on the next launch, check the first option on the "File" menu.

#### KITFS27-24VEVM evaluation board

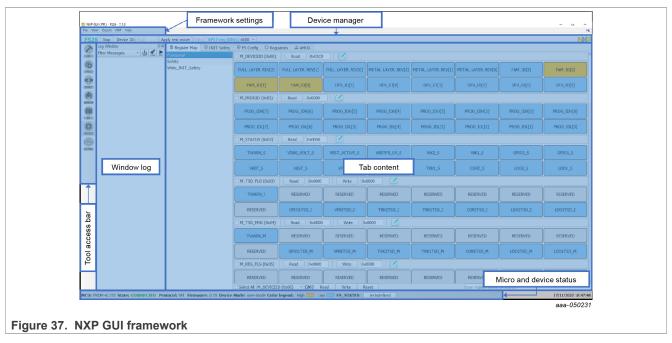

The GUI is loaded, and its interface such as in Figure 37 is shown.

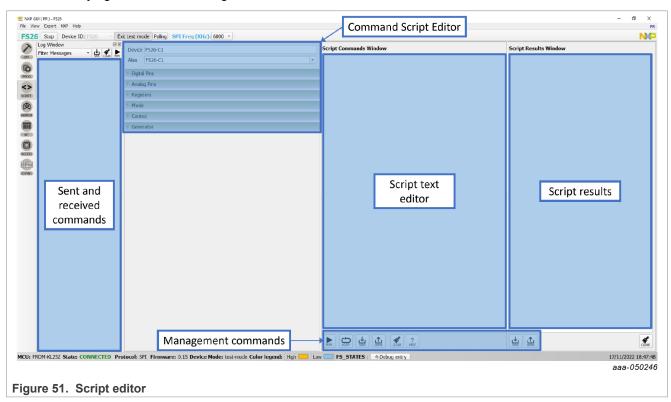

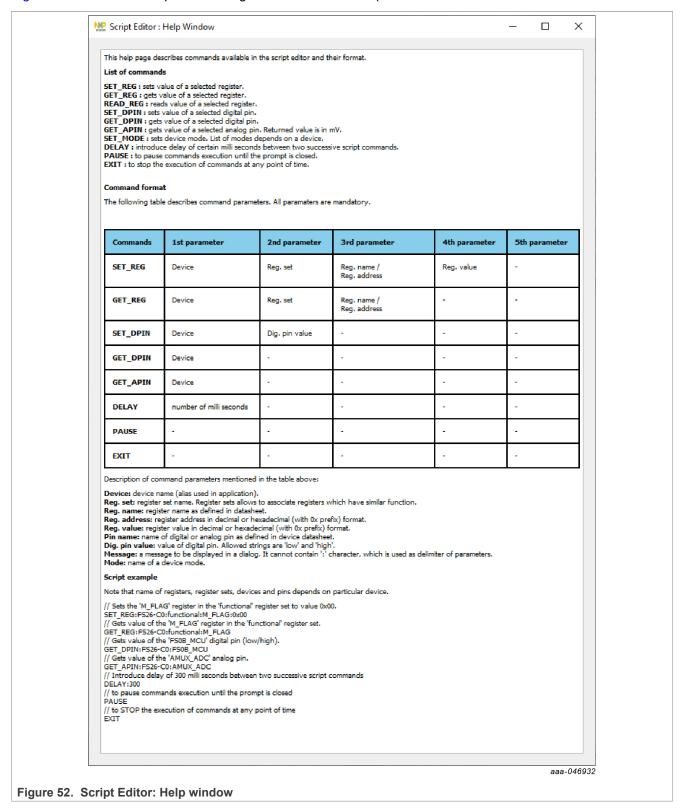

The NXP GUI for Automotive PMIC Families interface is now in use. It can be divided in several parts:

- Settings: Import or export files; configure framework

- Device Manager: Start communication with the device; enter or exit test mode; SPI communication settings

- Tool Access Bar: Quick access to the evaluation tools and features

- Window Log: Microcontroller and device communication events

- Tab Content: Content of each tool or tab there can be more tabs, boxes, or windows

- **Micro and Device Status:** Displays whether USB or device is connected or disconnected; displays Firmware and GUI version; displays the current state of the FS state machine click **Display** button to refresh

**Note:** The tool access bar shows the GUI tools in the sequence that they must be used. The first step is to verify device POWER dissipation and then configure the OTP. When the power is verified and OTP is done, the device can be programmed or emulated with a SCRIPT. MIRROR registers can be read/modified to a configuration validation. To verify states and configure safety reactions, the Access tab allows manipulation of the registers.

KITFS27-24VEVM evaluation board

## 7.2 Framework settings

The NXP GUI for Automotive PMIC Families main menu has five elements: File, View, Export, NXP, and Help.

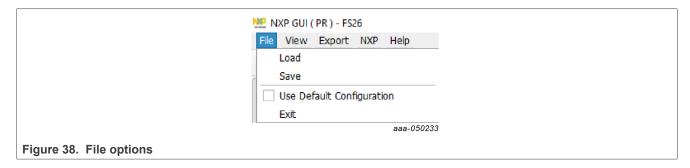

#### 7.2.1 File

Load or save a configuration or exit the application. Load and save are only enabled when the OTP tool tab is active

- Load: Loads an existing configuration file previously exported from the OTP tool, to continue to modify it on the OTP tool. This file has a .cfg extension. It is identified as: <device>\_ProgIDASILlevel\_CONFIG.cfg. Example: <device>\_A0D\_CONFIG.cfg.

- Save: Saves the current configuration of the OTP tool as a .cfg file.

- Use default configuration: Check to show Kit selection window.

- Exit: Exits NXP GUI application.

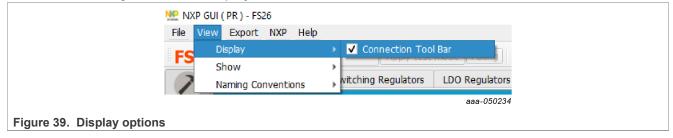

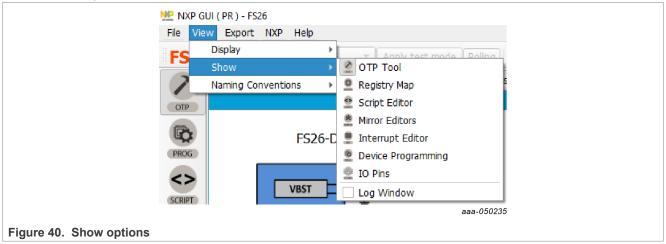

## 7.2.2 View

This main menu has options related to the GUI display.

Display: It consists of the Connection Tool Bar (enabled by default) option.

To show or hide, go to View → Display and then select Connection Tool Bar.

#### KITFS27-24VEVM evaluation board

• Show: This option can be used to access various sections of the GUI.

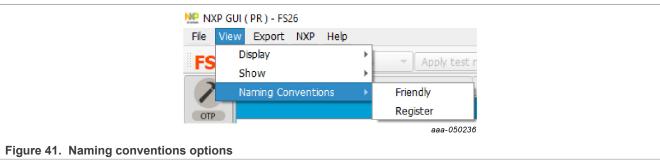

• **Naming Conventions**: Select Friendly or Register name display for the OTP tool. This option is enabled only when the OTP tool is active.

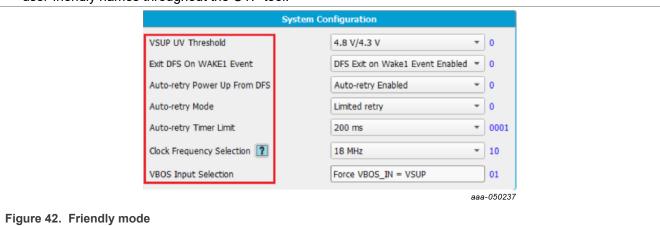

Friendly: Go to View → Naming Conventions → Friendly. This mode helps to view the register names as user-friendly names throughout the OTP tool.

Register: Go to View → Naming Conventions → Register. This mode helps to view the register names as

the registers' technical names throughout the OTP Tool.

Example: VSUP UV threshold → VSUP UVTH OTP

KITFS27-24VEVM evaluation board

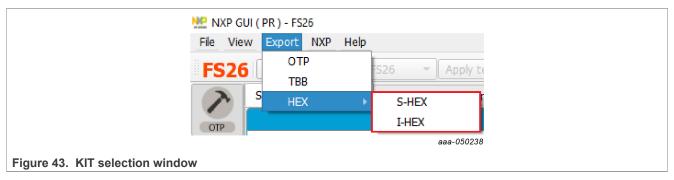

## **7.2.3 Export**

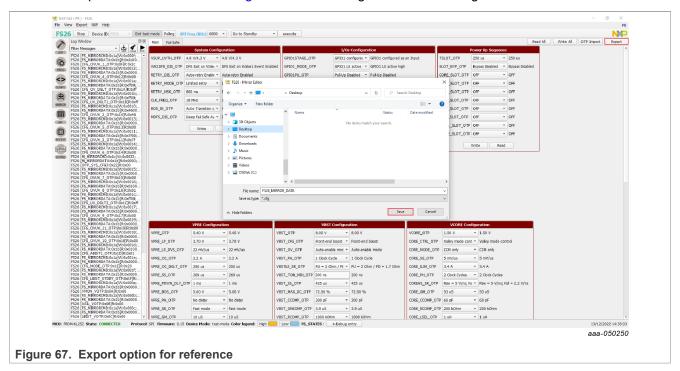

This option allows the user to export the current OTP from the OTP tool into different script formats.

- OTP: Exports OTP configuration into an OTP script file.

- TBB: Exports OTP configuration into a TBB script file for programming and emulation.

- I-HEX: Exports to Intel Hex script file.

- S-HEX: Exports to Simple Hex script file.

This option is enabled only in the OTP Tool, and remains disabled in other sections of the GUI.

#### 7.3 OTP tab

The OTP tool allows the configuration of OTP registers and generates scripts for OTP emulation or OTP programming. These scripts program parameters that the main state machine and the fail-safe state machine control.

The OTP tool includes four tabs:

- · System Configuration

- · Switching and LDO Regulators

- Voltage Monitoring

- System Safety Configuration

- OTP ID

These five tabs are used to define the entire FS27 OTP configuration.

When the OTP configuration is defined, TBB/OTP scripts can be generated using the *Export* menu. Generate a TBB file for emulation and an OTP file for OTP programming.

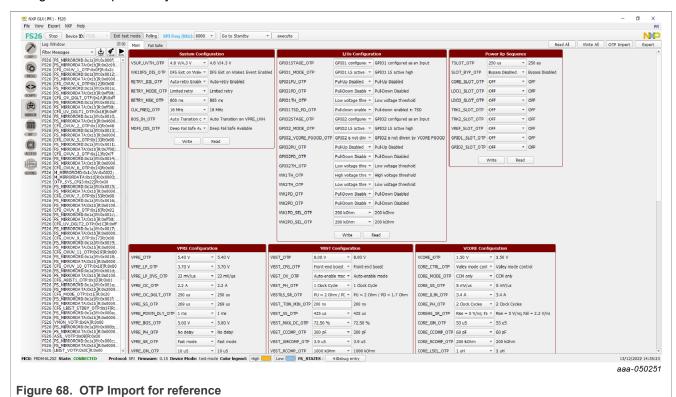

It is possible to save a configuration to use or to modify it later. To export the OTP configuration, click **Save Config.** To import a configuration initially saved from the OTP tool or the Mirrors tab, click the **Import** button.

KITFS27-24VEVM evaluation board

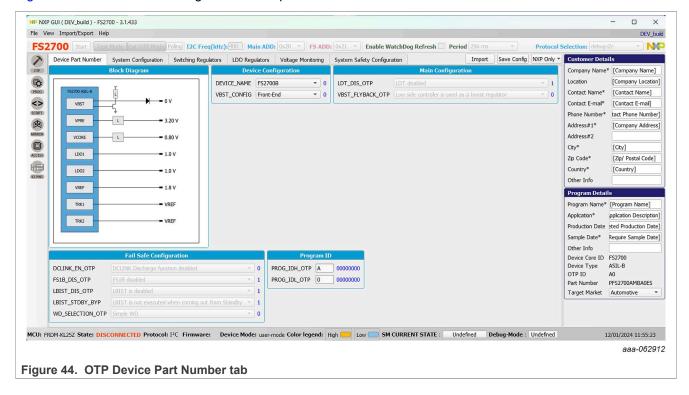

#### 7.3.1 Device Part Number tab

The system configuration tab has several sections:

- Block Diagram: This graphic shows the output voltage set for each supply rail (VBST, VPRE, VCORE, ...).

- Device Configuration: Used to set device versioning (DEVICE NAME) and VBST regulator configuration.

- Main Configuration: Shows the main configuration based on device versioning.

- Fail-safe Configuration: Shows the fail-safe configuration based on device versioning.

- Program ID: Shows the device ID chosen.

Figure 44 shows an OTP configuration example.

KITFS27-24VEVM evaluation board

## 7.3.2 System Configuration tab

The system configuration tab has several sections:

- **System Configuration**: Used to configure the VSUP undervoltage threshold, VBOS transitions, clock frequency spread spectrum, and others.

- Communication: Used to device address and communication protocol type.

- GPIO1 Configuration: Used to configure the GPIO1.

- GPIO2 Configuration: Used to configure the GPIO2.

- WAKE Configuration: Used to configure WAKE1 and WAKE2.

- Regulator Power Sequencing: Used to define the power sequencing of the device.

- Power Sequencing Configuration: Used to define the power sequencing enhancement, such as slot transition conditions.

- **Sequence Diagram**: This diagram reflects the power-up sequence depending on the OTP configuration the power-up sequence timing may not be 100 % accurate.

Figure 45 shows an OTP configuration example.

Figure 45. OTP System Configuration Tab

KITFS27-24VEVM evaluation board

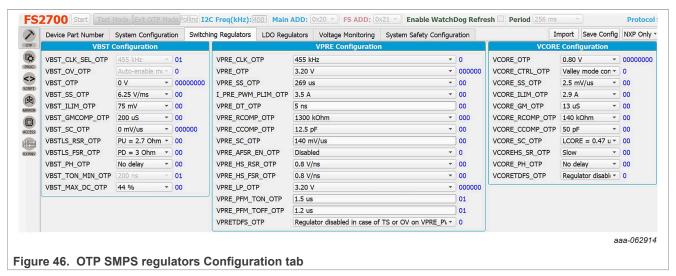

### 7.3.3 Switching Regulators tab

The Switching Regulators tab shown in Figure 46 has three sections:

- VBST Configuration: VBST minimum ON time is already set. Other parameters can be chosen.

- VPRE Configuration: Minimum ON and OFF time in PFM mode and the slope compensation are set and cannot be modified. Also, VPRE transition voltage when going to Standby mode (VPRE\_BOS\_OTP) is linked to VPRE output voltage in Standby mode (VPRE\_LP\_OTP). Other parameters can be chosen.

- VCORE Configuration: VCORE control mode is already set. Other parameters can be chosen.

Regulators VPRE and VCORE can be configured individually to trigger a transition to deep fail-safe (<regulator>TDFS OTP bit field) when an OV is detected.

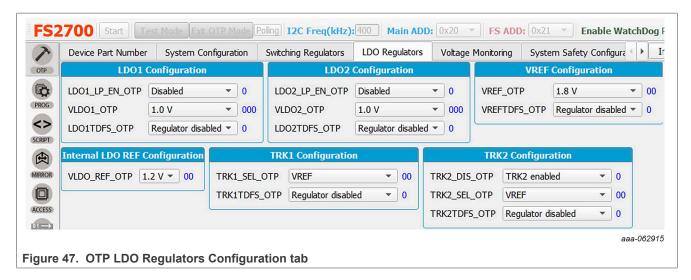

#### 7.3.4 LDO Regulators tab

The LDO Regulators tab shown in Figure 47 has five sections:

- LDO1/LDO2 Configuration: Linear dropout regulators configuration.

- VREF Configuration: High-precision voltage linear dropout regulator configuration.

- Internal LDO REF Configuration: High-precision voltage linear dropout internal regulator configuration.

- TRK1/TRK2 Configuration: Voltage tracking regulators configuration. Can track LDO2, VREF, or the internal LDO REF, in any combination.

#### KITFS27-24VEVM evaluation board

Each regulator can be configured individually to trigger a transition to deep fail-safe (<regulator>TDFS\_OTP bit) when an OV is detected.

KITFS27-24VEVM evaluation board

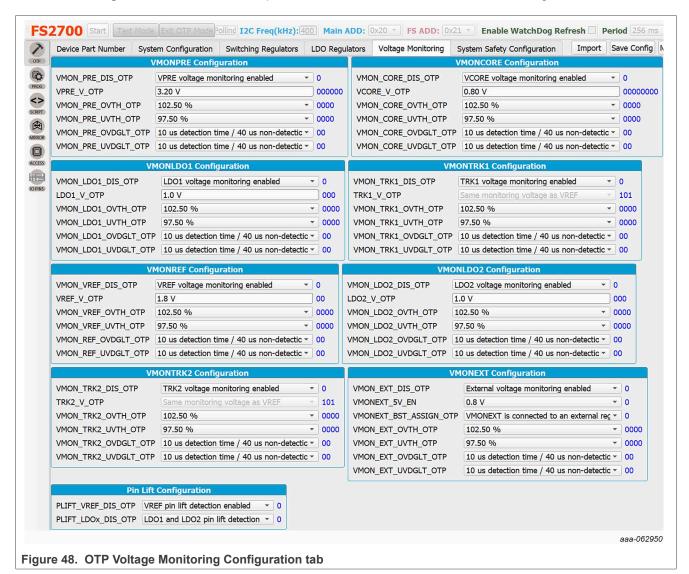

### 7.3.5 Voltage Monitoring tab

The Voltage Monitoring tab shown in Figure 48 has the following sections:

- VMONPRE, VMONCORE, VMONTRK1, VMONTRK2, VMONEXT Configuration: Defines OV/UV thresholds and deglitch timings for VPRE, VCORE, TRK1 and TRK2 regulators. The monitoring voltages are bound to the respective regulator voltage set in the Switching/LDO Regulators tab (except for VMONEXT). VMONEXT monitoring target can be set to 5.0 V when VBST is in the back-end at 5.0 V.

- VMONLDO1, VMONLDO2, VMONREF Configuration: Defines OV/UV thresholds, normal or degraded UV (except for VREF), and deglitch timings for LDO1, LDO2, and VREF regulators.

- Pin Lift Configuration: Used to disable pin lift detection on VREF, LDO1, and LDO2 regulators.

KITFS27-24VEVM evaluation board

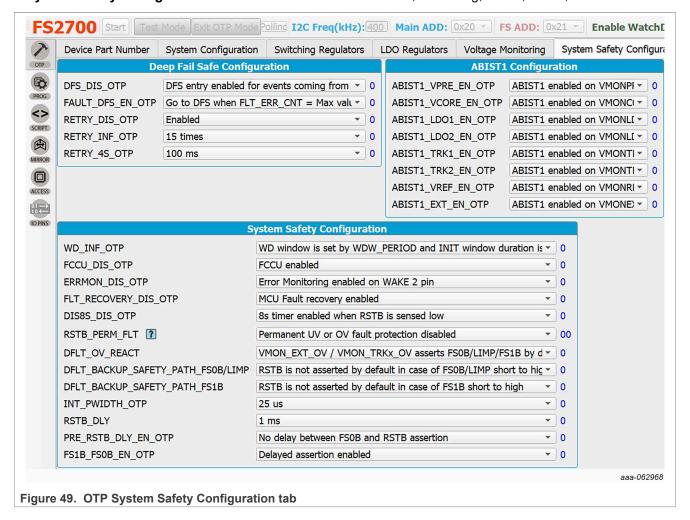

## 7.3.6 System Safety Configuration tab

The System Safety Configuration tab shown in Figure 49 has two sections:

- **Deep fail-safe Configuration**: Used to disable transition to deep fail-safe (development only), to go to deep fail-safe when fault error counter in incremented, auto retry strategy.

- ABIST1 Configuration: Used to enable ABIST1 execution for each available monitoring.

- System Safety Configuration: Used to set the behavior of FS1B, Watchdog, LBIST, RSTB, and others.

KITFS27-24VEVM evaluation board

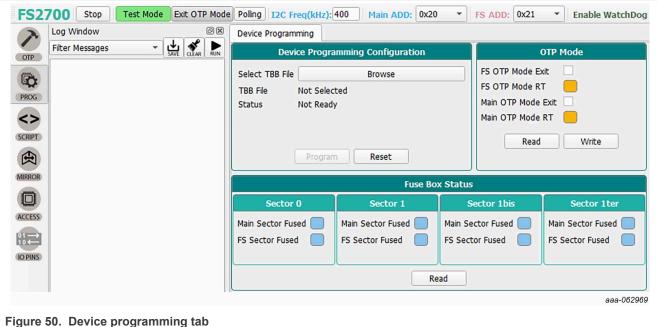

## 7.4 Device programming

The Device Programming tab shown in Figure 50 allows the user to burn the OTP using a script initially generated by the OTP tool. To enable this window, the device must be in test mode.

To program an OTP configuration, the V<sub>OTP</sub> voltage must be applied to the DEBUG pin. To do so, the user must turn on SW5 to apply 8.0 V to the device DEBUG pin.

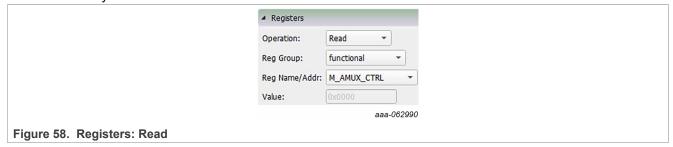

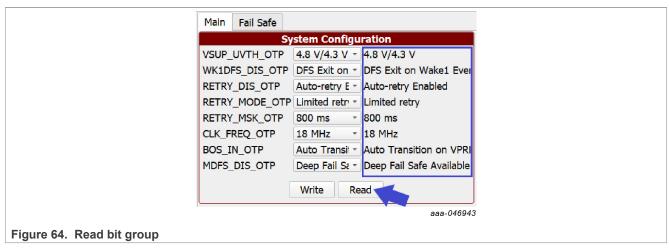

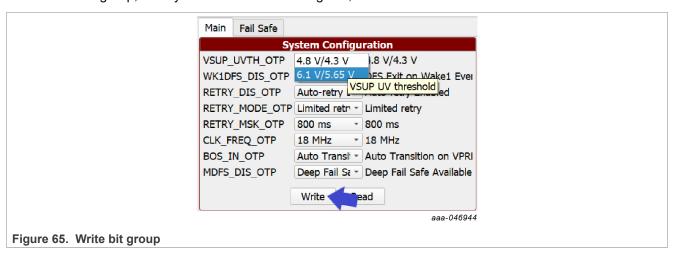

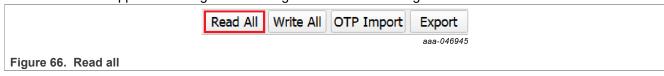

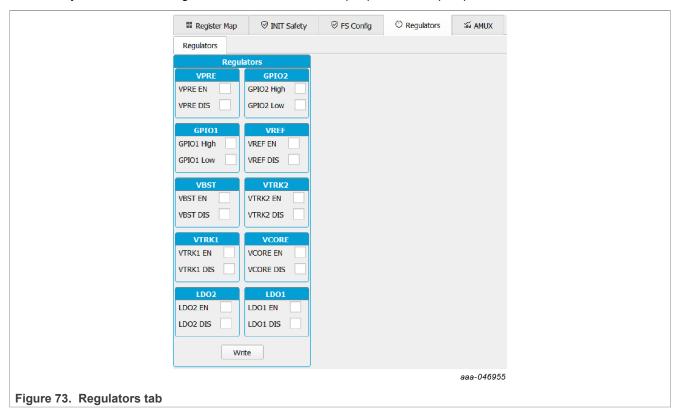

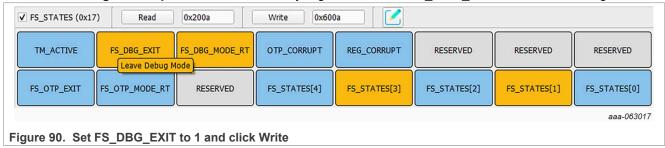

Click Browse to select an OTP script file, then click the Program button to run the script. If the DEBUG pin voltage is not set to V<sub>OTP</sub>, a pop up appears to ask the user to turn on SW5.