## UG10246

# NXP 48V Motor Control Development Platform User Guide Rev. 2.0 — 10 November 2025

User guide

#### **Document information**

| Information | Content                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | Motor control, 48V, PMSM                                                                                                     |

| Abstract    | This user guide introduces NXP 48 V Motor Control Development Platform for high power automotive motor control applications. |

**NXP 48V Motor Control Development Platform User Guide**

## 1 Introduction

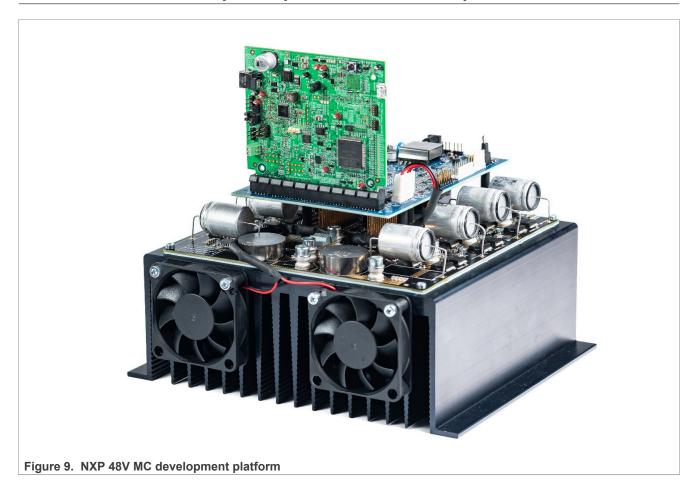

This user guide introduces NXP 48 V Motor Control Development Platform for high power automotive motor control applications. This development platform is built up of three standalone boards called Power Stage board, Adapter board and Controller board. These boards are mechanically and electrically connected to each other and cannot operate independently. Power Stage board primarily controls energy flow from power supply source to the motor load. Adapter board processes and adjusts analog, digital and power supply signals, which are routed in between Power Stage board and Controller board. Controller board contains microcontroller, system basis chip, and communication layers, which ensure proper control of power elements, supply of processing circuitry and communication with external systems. This platform is formed to drive two 3-phase BLDC/PMSM or one 6-phase motors in power range up to 5.6 kW. Moreover, it offers several advanced features for complex, high-end motor control application development in 48 V automotive or non-automotive segments.

## 1.1 MC development platform features

NXP 48 V MC development platform provides following functionalities:

#### System parameters:

- Two independent 48 V 3-phase half-bridge arrangements with standalone DC-link circuits

- Standalone DC-link pre-charging for each DC-link circuit in two steps

- Extended low voltage operation starting from 24 V

- Phase current capability up to 80 A<sub>(RMS)</sub> and 120 A<sub>(MAX)</sub> for each 3-phase half-bridge

- Power supply converters for internal digital and analog subsystems:

- 48 V/15 V Non-Isolated DC/DC Buck-Boost converter

- 12 V/12 V Isolated DC/DC Flyback converter

## · Analog quantities measurement:

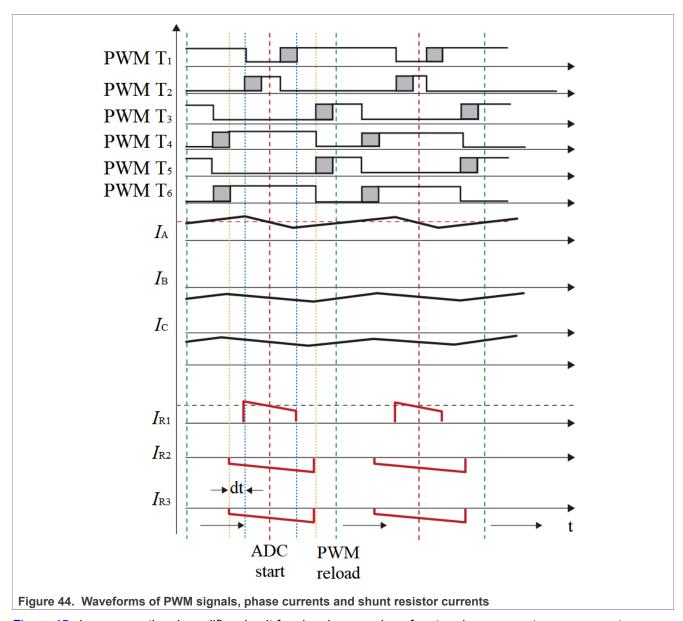

- Phase current sensing using triple-shunt configuration

- Parallel connection of two shunts in each leg of inverter

- Various hardware (HW) configurations allow to change maximum current sensing range

- Measurement of following voltages:

- BEMF voltage sensing by voltage divider

- Phase voltage reconstruction realized by external comparators and dedicated microcontroller (MCU) peripherals with software (SW) routine

- DC-link voltage measurement

- Forward voltage measurement

- Battery voltage measurement

- Temperature measurement on different positions of Power Stage board

- Measurement of temperature in each leg of inverter

- Temperature measurement of pre-charge MOSFETs

- Multiplexing of temperature signals

## • Motor speed and position sensors support:

- Resolver sensor signal generation and signal processing support

- Encoder/HALL signal processing support

#### · Fault detection and safe mechanisms:

- Fault protection mechanisms

- Over-voltage protection using single comparator

- Over-current protection using window comparators

- Over-temperature protection

- Pre-charge desaturation protection

UG10246

## **NXP 48V Motor Control Development Platform User Guide**

- Monitor of Buck power supply malfunction

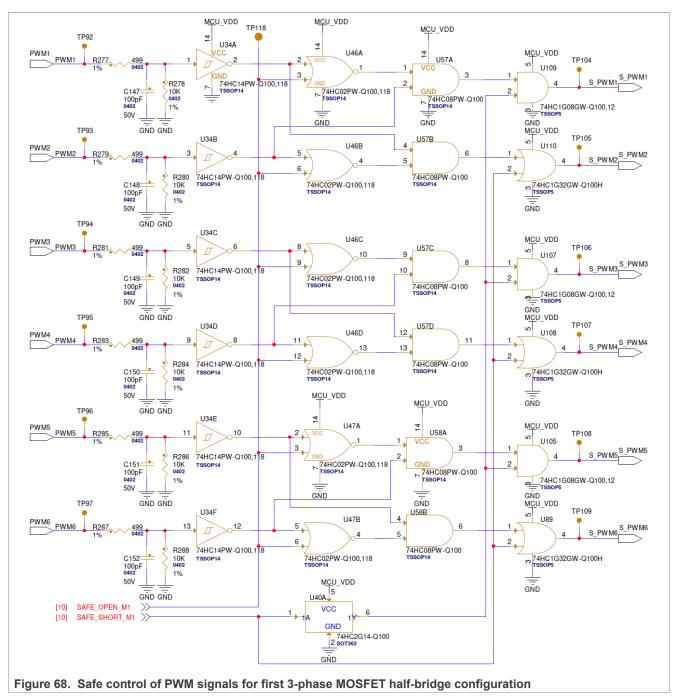

- Independent safe mechanisms for PWM signals:

- Safe open mechanism turns-off all power MOSFETs in 3-phase half-bridge

- Safe short mechanism turns-on only low side power MOSFETs in 3-phase half-bridge

- Power supply redundancy:

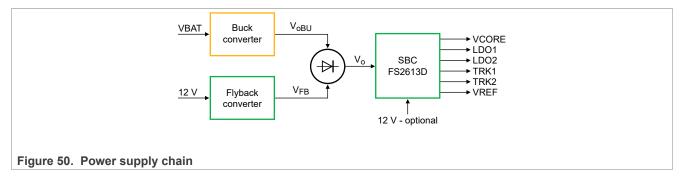

- Main Non-Isolated Buck-Boost converter is backed up Isolated Flyback converter in case of Buck-Boost malfunction

- Galvanically isolated control and wake-up signals

#### · General system information:

- S32K344 Arm<sup>®</sup> Cortex<sup>®</sup>-M7-based microcontroller in lockstep core configuration linked with FS2613 SBC (System Basis Chips)

- Short protection realized by fuse

- Robust high current screw terminals

- Massive aluminum heatsink, supported by active cooling

- MCU independent/dependent control of dual fans (not included)

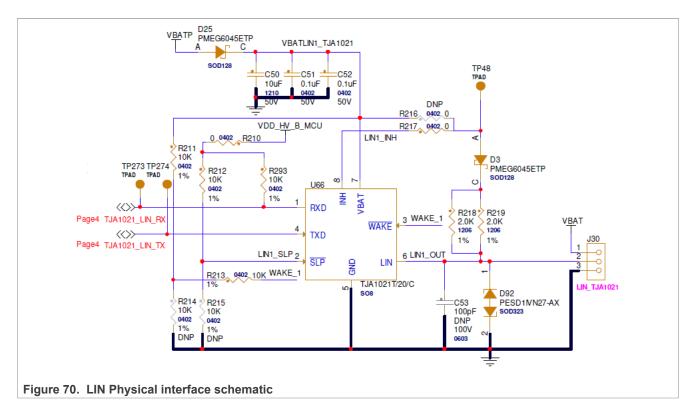

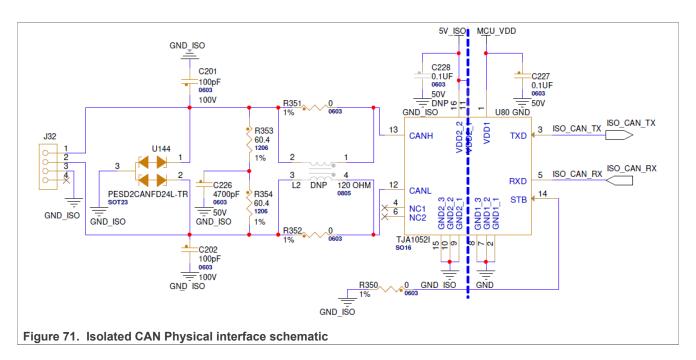

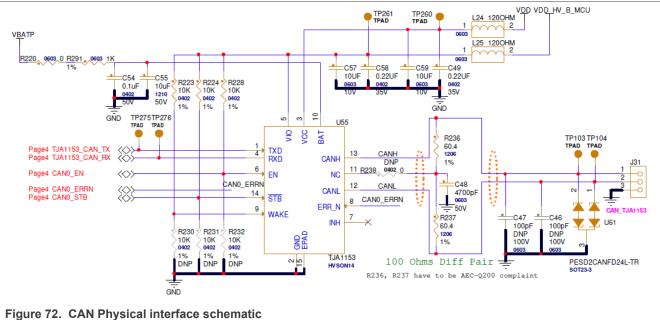

- Automotive connectivity interfaces LIN, CAN, and Ethernet

- Galvanically isolated and non-isolated CAN transceivers

- Application buttons and switches

- Headers for MCU pin accessibility

- On-board debugger and JTAG debug interfaces

- LED indicators and debugging headers

## 1.2 Operation conditions of NXP 48 V MC development platform

\*The platform was not evaluated in whole operation range, values in the table above are based on design specification.

Table 1. Electrical specification of NXP 48 V MC development platform

| Parameter                                 | Min                      |                          | Typical            | Max   |

|-------------------------------------------|--------------------------|--------------------------|--------------------|-------|

|                                           | Designed Pov             | ver Stage electrical spo | ecifications       |       |

| Supply voltage                            | 20 V                     |                          | 48 V               | 60 V  |

| Phase current                             | -                        |                          | 80 A               | 120 A |

| Ambient temperature                       | 0°C                      |                          | 20°C               | 40°C  |

| Board temperature (with passive heatsink) | -                        |                          | -                  | 150°C |

|                                           | Electrical conditions of | of Power Stage applied   | for EMC evaluation |       |

| Supply voltage                            | -                        |                          | -                  | 48 V  |

| Phase current                             | -                        |                          | 2 A                | 5 A   |

| Ambient temperature                       | -                        |                          | 25°C               | -     |

| Board temperature (with passive heatsink) | -                        |                          | -                  | -     |

|                                           | Adap                     | oter board specification | ns                 |       |

| Flyback                                   | Input supply voltage     | 8 V                      | 12 V               | 16 V  |

|                                           | Output current           | -                        | 500 mA             | 1 A   |

| Input digital ports                       | Input supply voltage     | -                        | 5 V                | 5.5 V |

## NXP 48V Motor Control Development Platform User Guide

Table 1. Electrical specification of NXP 48 V MC development platform...continued

| Parameter                   | Min                   |                         | Typical | Max    |

|-----------------------------|-----------------------|-------------------------|---------|--------|

| Fan control                 | Output supply voltage | -                       | 12 V    | 15 V   |

|                             | Output current        | -                       | 100 mA  | 500 mA |

| Encoder                     | Output supply voltage | -                       | 5 V     | 5.1 V  |

|                             | Output current        | -                       | -       | 10 mA  |

|                             | Contr                 | oller board specificati | on      |        |

| Input supply voltage of SBC | 3.2 V                 |                         | 12 V    | 15 V   |

**Note:** NXP does not guarantee compliance with EMC standards within or out of the conditions specified in the section "Designed Power Stage electrical specifications" of Table 1.

## 1.3 NXP 48 V MC development platform architecture

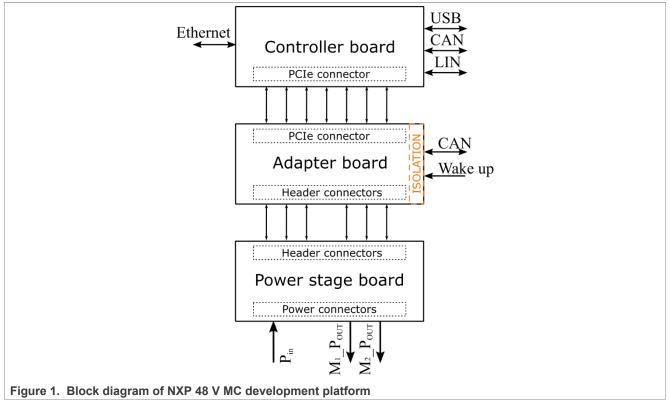

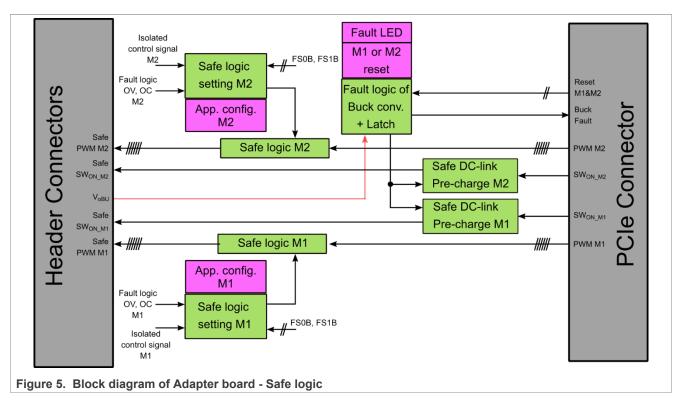

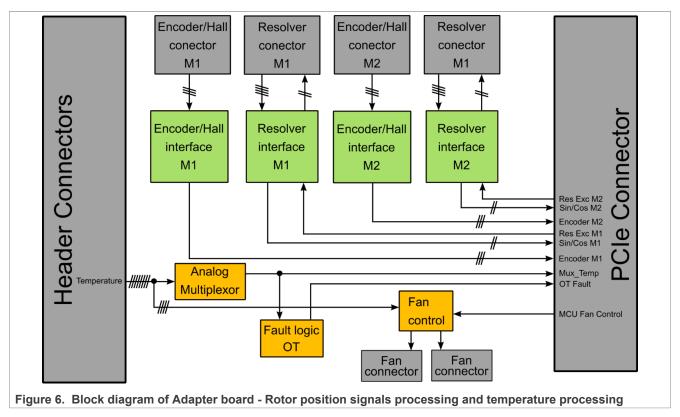

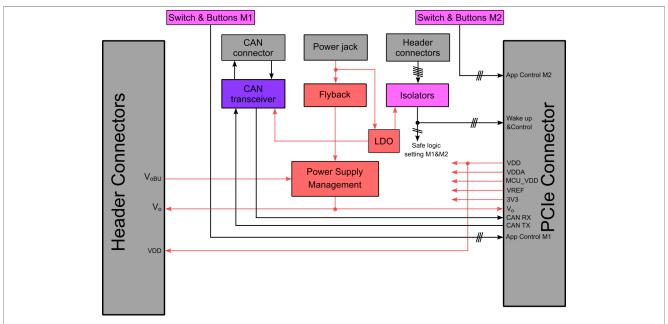

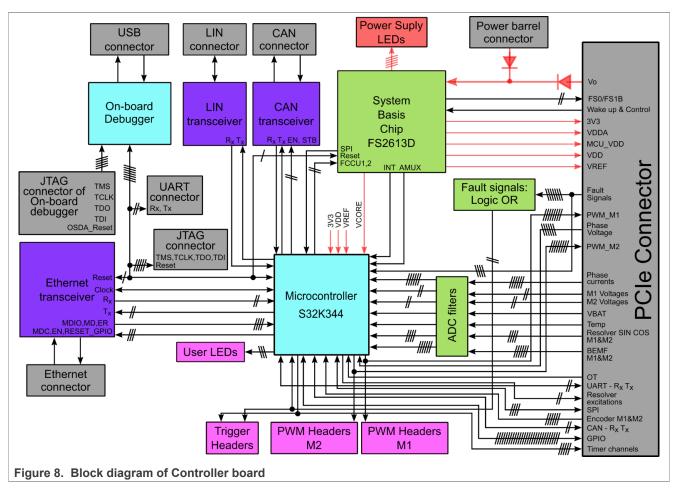

The simplified block diagram of NXP 48 V MC development platform is depicted in <u>Figure 1</u>. This hardware platform consists of three different boards, which contains different subsystems reasonably distributed on each board. The boards are mechanically and electrically connected to each other by means of different type of connectors i.e., header connectors or PCle connector. For the sake of clear clarity, the architecture of complete platform is decomposed on board architectures. <u>Figure 2</u> shows block diagram of Power Stage board, <u>Figure 3</u>, <u>Figure 4</u>, <u>Figure 5</u>, <u>Figure 6</u> and <u>Figure 7</u> show block diagrams of Adapter board and <u>Figure 8</u> shows block diagram of Controller board.

Block diagram of complete NXP 48 V MC development platform demonstrates connection of individual boards to each other and way of system interaction with environment through different interfaces. Power Stage board is in charge to transform DC voltage and current provided by supply source on the input terminals to 3-phase AC voltage and current on the output terminals for the motor load. Two 3-phase half-bridges with output terminals are capable of independent controlling of two 3-phase BLDC/PMSM motors or single 6-phase motor. The electrical and mechanical connection of Power Stage board and Adapter board is arranged by two header connectors, where each of the two supports signal transfer just for particular 3-phase half-bridge.

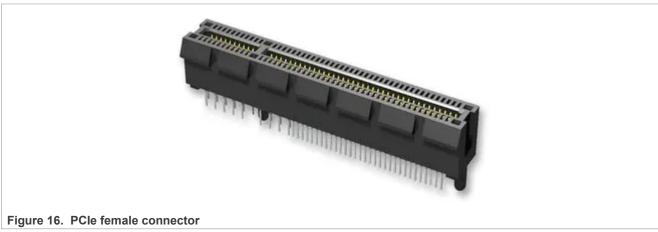

The main purpose of Adapter board is to adjust and process analog, digital and power supply signals, which are transmitted between Power Stage board and Controller board. There are several subsystems, which support proper operation of platform. Platform communication with superior system is carried out through galvanically isolated CAN (Controller Area Network) transceiver. In addition, superior system is capable to control and wake the system up through wake-up control signals. The connection of Controller board and Adapter board is arranged by means of PCI-Express connector. It contains a huge number of pins for analog, digital and power supply signals, therefore can easily fulfill requirements for control of two 3-phase motors or one 6-phase motor. Moreover, it provides sufficient mechanical robustness of Controller and Adapter boards connection.

NXP 48V Motor Control Development Platform User Guide

NXP 48 V MC development platform introduces benefit of modularity to be able to scale output power with less or more powerful Power stage boards or boost computational performance with more powerful microcontrollers being a part of the Controller board.

The following sections provide detailed explanation of Power stage board, Adapter board and Controller board architectures.

## 1.3.1 Power stage board architecture

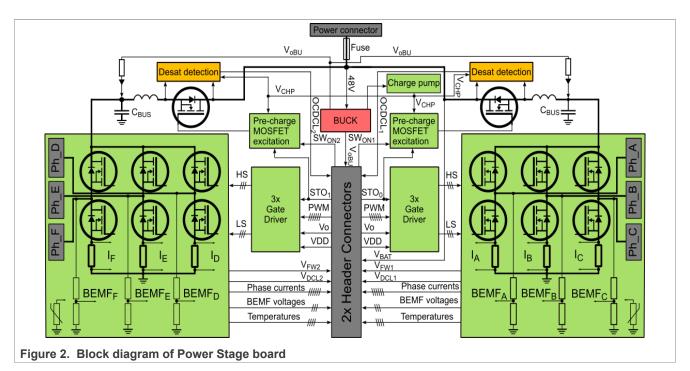

Various block colour differentiate a block functionality:

- Green Motor control related hardware + 3-phase half-bridge

- · Gray Interfaces and terminals

- · Orange Other functions of the system

- Red Board power supply functionality

#### NXP 48V Motor Control Development Platform User Guide

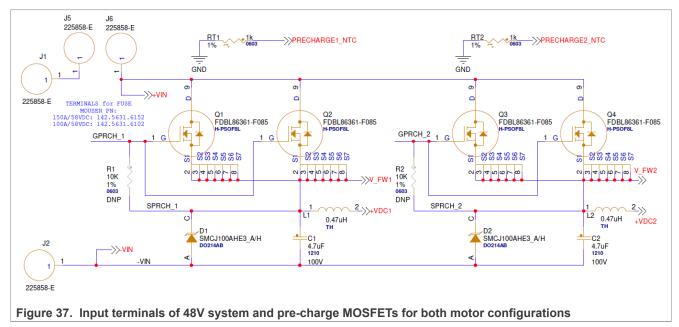

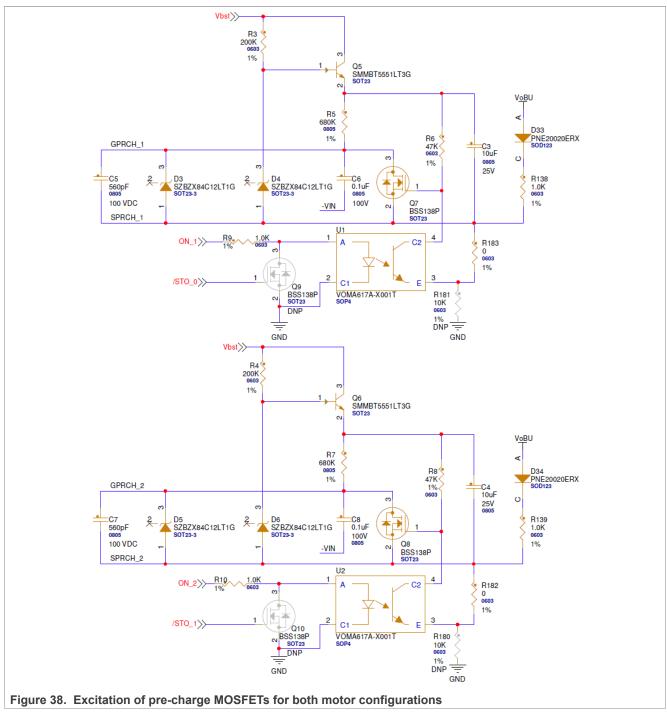

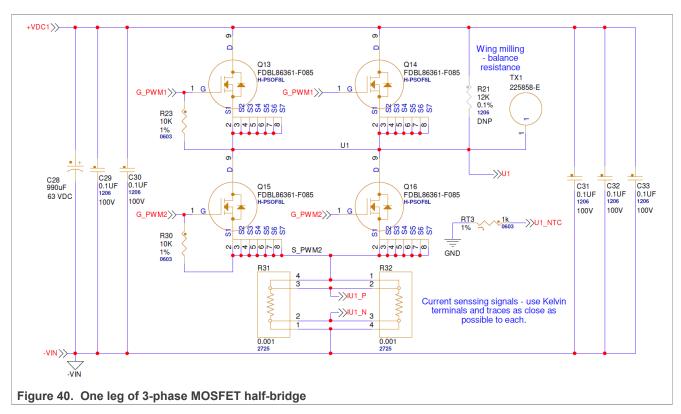

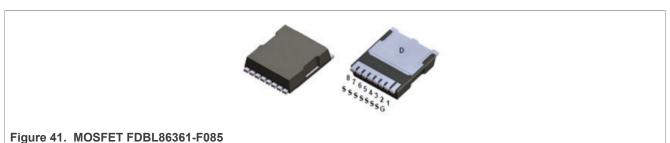

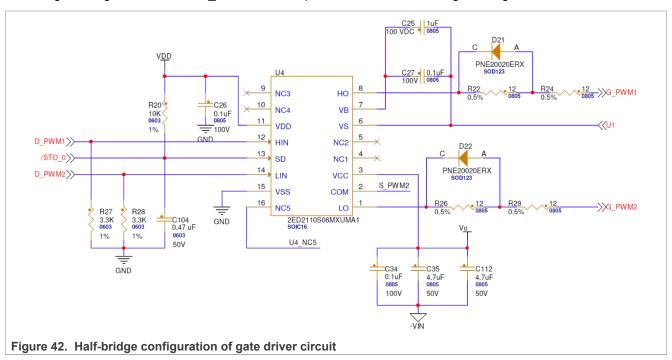

Power Stage board is constructed to be fully functional and be reliably operated in wide range of input voltage from 24 V up to 60 V. Figure 2 shows block diagram of Power Stage board. The board primarily contains two 3-phase MOSFET half-bridges. The phase outputs of both 3-phase half-bridges are connected to the robust power terminals. Each 3-phase MOSFET half-bridge is powered from standalone DC-link circuit, which is pre-charged by own pre-charge circuit built up on power MOSFETs. The power MOSFETs of 3-phase half-bridges and power MOSFETs of pre-charge circuits are duplicated due to high power. Parallel connection of components is highlighted by bold outlines i.e., power MOSFETs or shunt resistors. Simple analog logic supporting high side MOSFET switching is used for pre-charge MOSFETs. Three single phase gate drivers are used to excite one 3-phase MOSFET half-bridge. Those gate drivers provides enough energy for all power MOSFETs. They are activate by default, however can be disabled by shutdown signals STO<sub>0</sub> for first 3-phase MOSFET half-bridge or STO<sub>1</sub> for second 3-phase MOSFET half-bridge. Those control signals can be generated by microcontroller or supervisor system over galvanic isolated layer. Single 3-phase MOSFET half-bridge with three standalone gate drivers utilizes one control signal shared for those three gate drivers and particular precharge circuit.

The sensors of phase currents and BEMF voltages are also implemented in Power Stage board. Two parallelly connected shunt resistors are placed in each leg of inverter below low side MOSFETs. Differential signals of phase current are directly connected to the particular header connector and transmitted to Adapter board. The BEMF voltages, DC-link, forward and battery voltages are scaled by voltage dividers, which adjust analog signals to fit the ADC input range of 0-5 V. Such scaled analog signals are subsequently connected to particular header connector. Additionally to phase current and BEMF voltage measurement, the Power Stage board support temperature measurement by NTC sensors. The NTC sensors are placed close to each phase of inverter and close to pre-charge MOSFETs, because fully operated power MOSFETs are sources of the greatest heat. All analog and digital signals of Power stage board are subsequently transferred through two header connectors to the Adapter board.

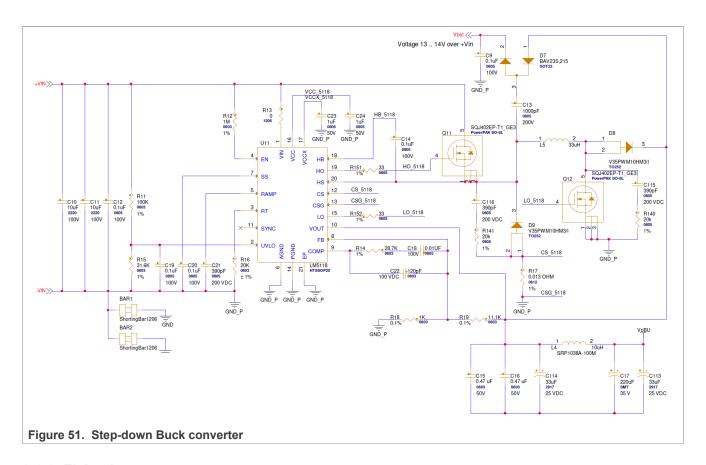

Input 48 V voltage is used to be converted by step-down Buck converter. The converter configuration enables to operate in wide range of input voltage, from 20 V up to 60 V, while output voltage is always constantly set to 15 V. This output voltage is connected to header connectors and transmitted to Adapter board to power supply redundancy circuit.

The pre-charge circuit contains power MOSFETs, which allow to connect DC-link circuit with input terminals and transfer energy from input to the output through 3-phase MOSFET half-bridge and excitation circuit, which

#### **NXP 48V Motor Control Development Platform User Guide**

controls turn-on/off process of power MOSFETs. The process of DC-link capacitors pre-charging is an essential function in high voltage and especially high-power systems due to limitation of inrush current. The DC-link circuit is pre-charged in two steps. In the first step, limited DC current is injected through diode and resistor from Buck converter to the DC-link capacitors. DC-link capacitors are going to be pre-charged on 15 V. In the second step, pre-charge MOSFET excitation circuit turns on pre-charge power MOSFETs, which allows to connect input terminals with DC-link capacitors. Those capacitors are subsequently charged on the level of voltage of input power supply source. Turn-on action of pre-charge MOSFETs is conditional by followings requirements.

- 1. Digital control signals STO<sub>0</sub> or for first 3-phase MOSFET half-bridge or STO<sub>1</sub> for second 3-phase MOSFET half-bridge have to be inactive, which means logic zero has to appear on these ports. However this condition is bypassed in current HW configuration, so logic state of STO0 of for first 3-phase MOSFET half-bridge or STO1 for second 3-phase MOSFET half-bridge doesn't influence of pre-charge functionality.

- 2. Digital control signals  $SW_{ON1}$  or for first 3-phase MOSFET half-bridge or  $SW_{ON2}$  for second 3-phase MOSFET half-bridge have to be activated at the same time.

- 3. High side position of pre-charge MOSFETs requires boosting of excitation voltage over the DC-link voltage. This role is covered by charge pump circuit, which utilizes switching voltage of Buck converter.

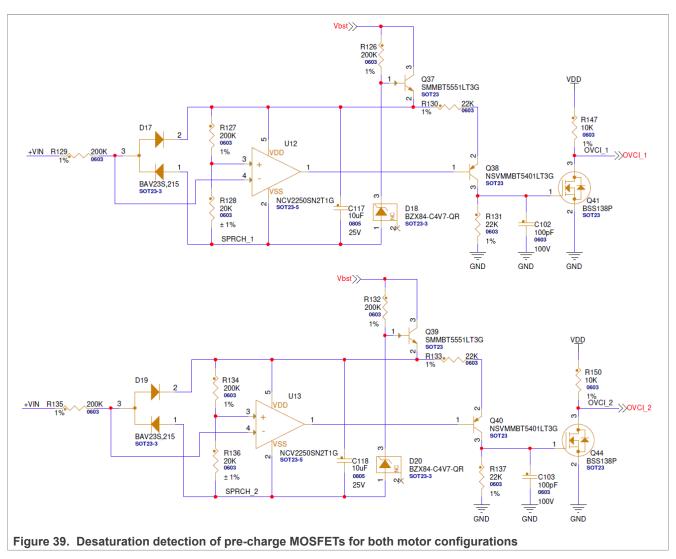

Monitoring of desaturation fault of pre-charge MOSFETs is an additional feature and also utilizes boosted voltage from charge pump circuit. Reverse polarity protection of input source is handled by fuse, which is irreversible damaged if such event happened. Heat dissipation and cooling of system is handled by aluminum heatsink and active cooling system.

## 1.3.2 Adapter board architecture

Various block colour differentiate a block functionality:

- Green Motor control related hardware + 3-phase half-bridge

- Pink Application control

- · Gray Interfaces and terminals

- Orange Other functions of the system

- Red Board power supply functionality

- Violet Communication interface

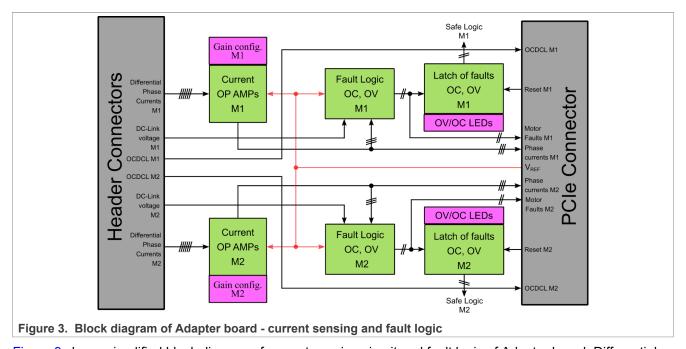

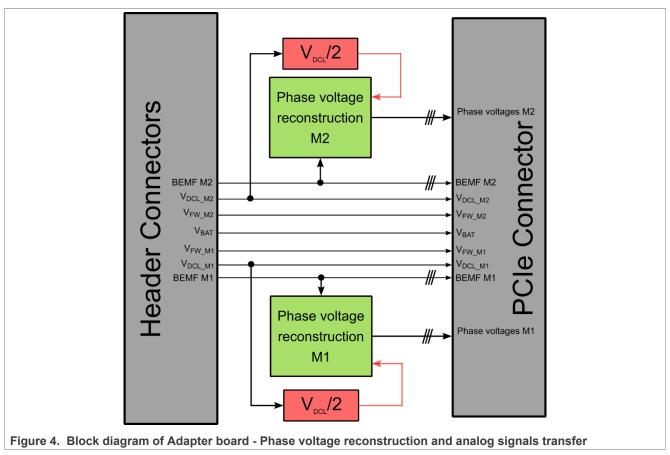

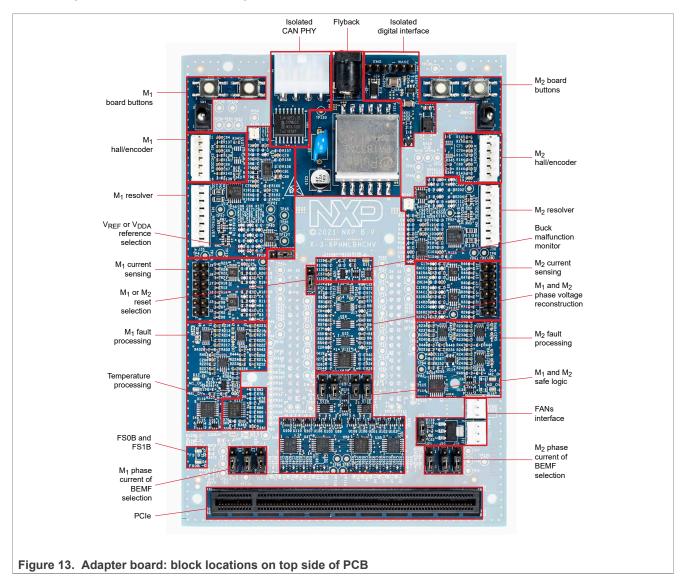

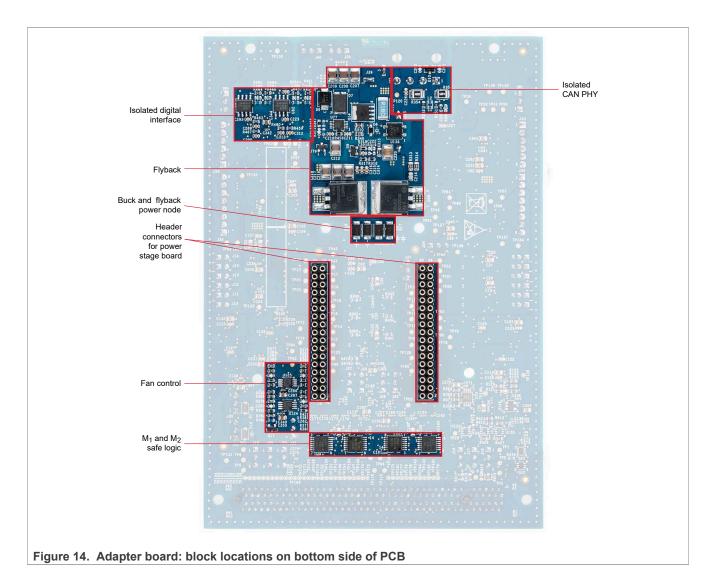

Figure 3, Figure 4, Figure 5, Figure 6 and Figure 7 show individual block diagrams of Adapter board. The Adapter board is responsible for signal processing of all signals, which are transferred in between Power Stage board and Controller board. In addition, the board provides communication interface with superior system through galvanically isolated layer. Mechanical and electrical connection with Power Stage board is arranged by header connectors, while mechanical and electrical connection with Controller board is arranged by PCIe connector. Overall architecture of Adapter board is divided on several block diagrams.

#### NXP 48V Motor Control Development Platform User Guide

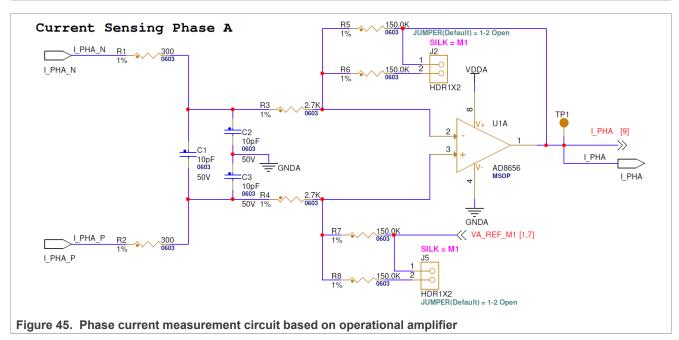

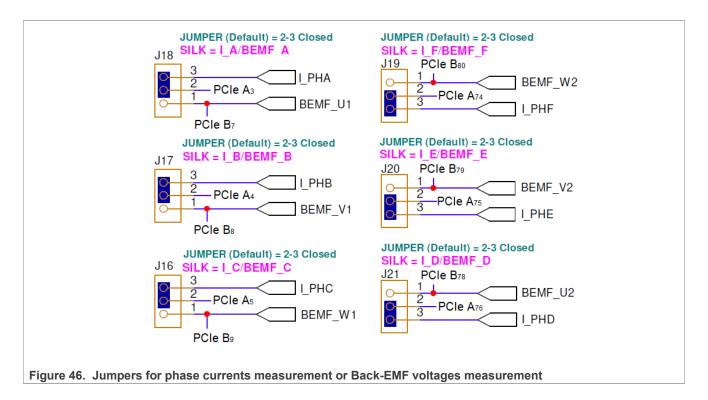

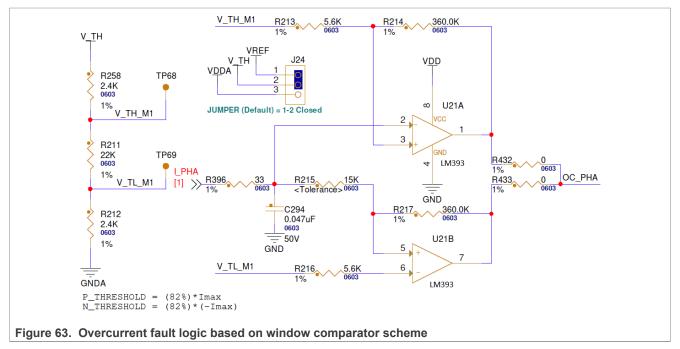

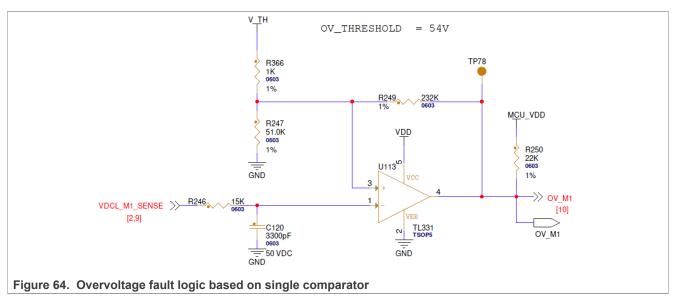

Figure 3 shows simplified block diagram of current sensing circuit and fault logic of Adapter board. Differential signals phase currents are routed to conditional circuitry with operational amplifiers. Conditional circuitry amplifies those differential signals and adds voltage offset in order to fit ADC input range of 0-5 V. The range of current measurement can be modified by gain configuration headers, which are a part of conditional circuitry with operational amplifiers. Amplified signals of current are directly routed to the PCIe connector and are also used for fault monitoring purpose. Fault logic is monitoring phase currents and DC-link voltage in order to detect over-current state and over-voltage state. There is only one, common fault signal of overcurrent for all 3-phase currents. The output signals of fault logic are routed to the PCIe connector and are also routed to the latch logic. The signal of desaturation fault of pre-charge MOSFETs is routed from header connector directly to PCIe connector without additional signal processing. This logic is latching the fault state of over-current or overvoltage or both and in addition, it indicates latched fault status by LEDs. Reset of the latched faults is carried out by reset signal, which is provided by microcontroller and routed over PCIe connector. Outputs of latch logic are subsequently routed to the safe logic. The conditional circuitry with operational amplifier and fault logic require voltage reference due to bidirectional flow of phase current. This voltage reference is provided by Controller board and transmitted over PCIe connector. Each 3-phase MOSFET half bridge utilizes standalone conditional circuitry with operational amplifiers and fault logic.

## NXP 48V Motor Control Development Platform User Guide

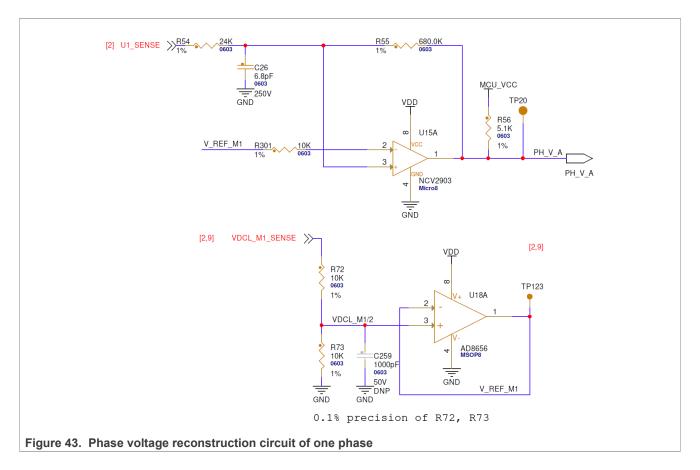

Figure 4 shows block diagram of Adapter board - phase voltage reconstruction and analog signals transfer. Analog signals of forward voltage, DC-link voltage, BEMF voltages for both 3-phase MOSFET half bridges and battery voltage are directly routed from header connectors to PCle connector. However, DC-link voltages of both 3-phase MOSFET half-bridges as well as BEMF signals are used for phase voltages reconstruction purpose. This hardware circuit supports signal processing, but final reconstruction of phase voltage is carried out by means of appropriate timer module of microcontroller and software routine. The outputs of phase voltage reconstruction module are routed to PCle connector. Each 3-phase MOSFET half-bridge uses standalone phase voltage reconstruction module.

#### **NXP 48V Motor Control Development Platform User Guide**

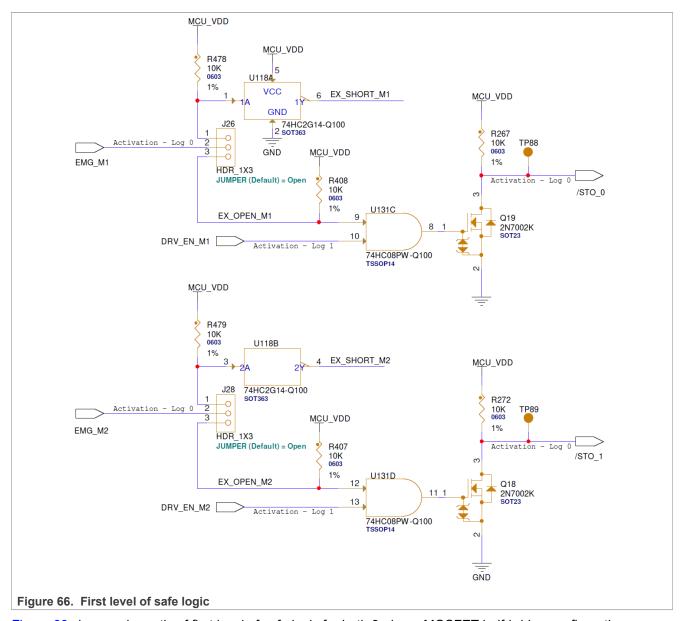

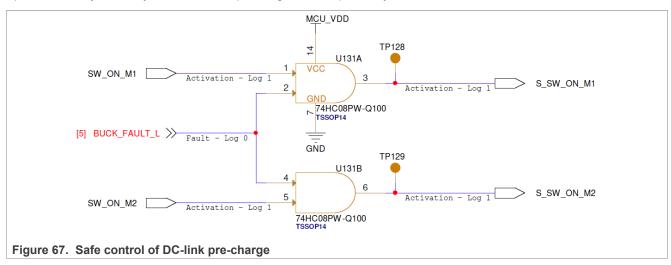

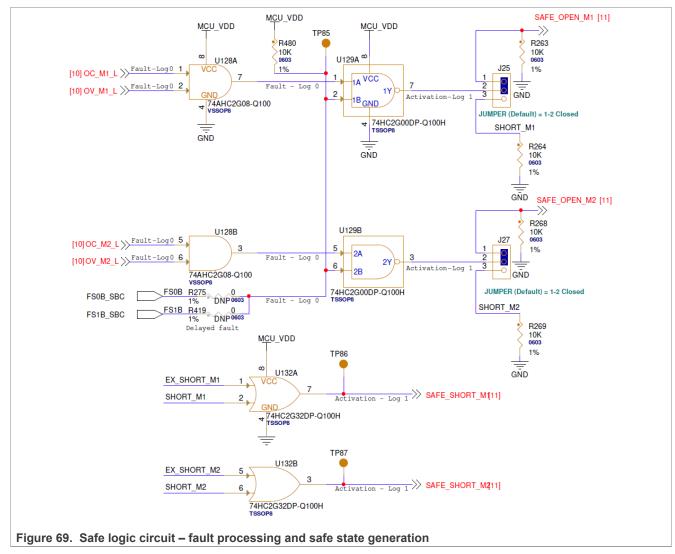

<u>Figure 5</u> shows block diagram of Adapter board safe logic circuitry. This circuitry is composed of several parts, which process generated PWM signals, pre-charging control signals, latched fault signals and external control signals. In addition, monitoring of proper operation of Buck converter is a part of this safe logic. Latched fault signals of over-current and over-voltage together with external control signal and fault-safe signals FS0B or FS1B are processed in Safe logic setting block. This block enables to configure safe state of system in accordance with application requirements by means of App. Config block. The NXP 48 V MC development platform supports two safe states:

- Safe open state All MOSFETs are turned off

- Safe short state Low side MOSFETs are turned on and high side MOSFETs are turned off

The safe state can be activated on behalf of fault logic behavior, interaction of superior system or interaction of system basis chip (SBC).

The block of Safe logic processes PWM signals generated by microcontroller depending on operation of system. There are three typical operation states:

- Normal operation: Behavior of PWM outputs of safe logic copies behavior of the inputs. Generated PWM signals are transmitted through safe logic without change of behavior, only symmetrical propagation delay is inserted.

- 2. Fault operation: Safe open state The PWM outputs of safe logic are deactivated, input PWM signals are not propagated through safe logic.

- 3. Fault operation: Safe short state The outputs of safe logic are modified and do not follow input behavior. PWM channels of safe logic for low side MOSFETs are activated and PWM channels of safe logic for high side MOSFETs are deactivated.

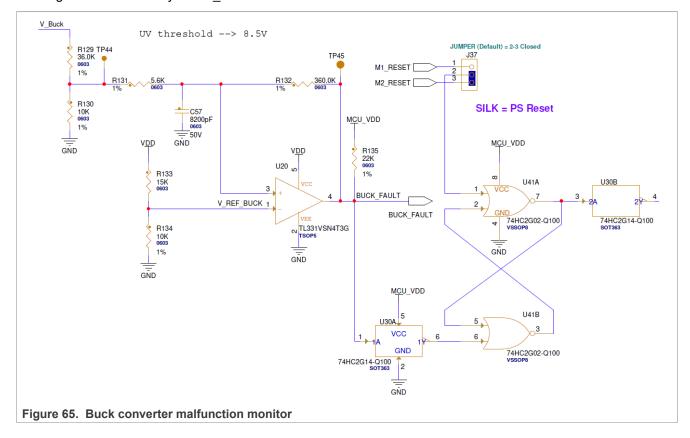

The fault logic of Buck converter monitors output voltage of Buck converter and detect fault in case of under-voltage state. This fault is subsequently latched and signalized by Fault LED. Latched fault of Buck undervoltage disable digital control signal of pre-charge MOSFETs. Activation of pre-charge MOSFETs is conditioned to proper functionality of Buck converter.

## NXP 48V Motor Control Development Platform User Guide

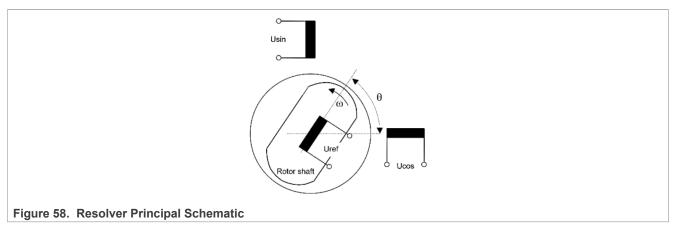

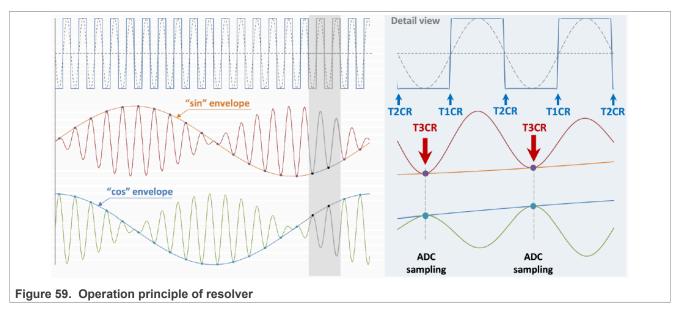

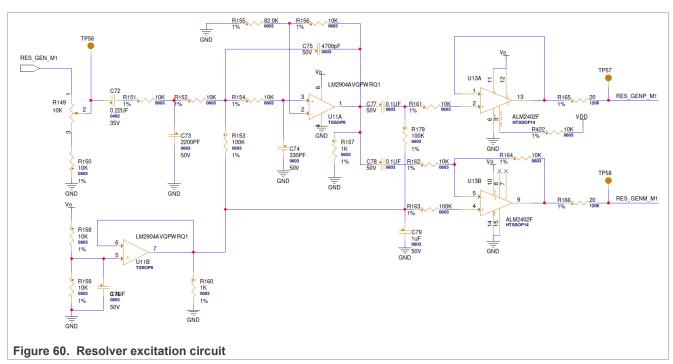

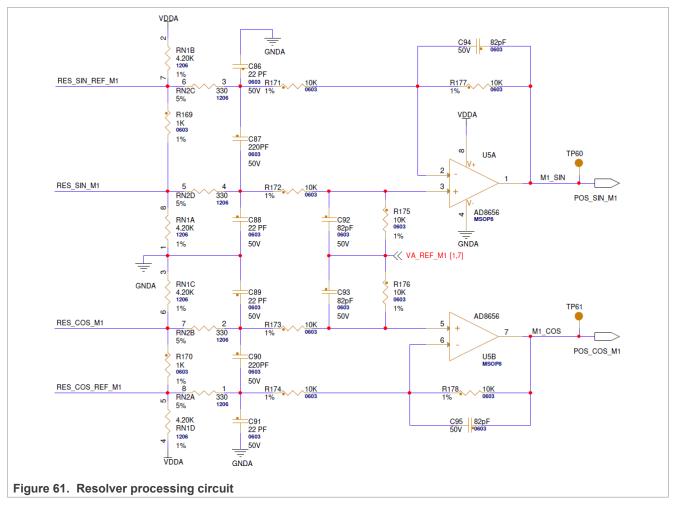

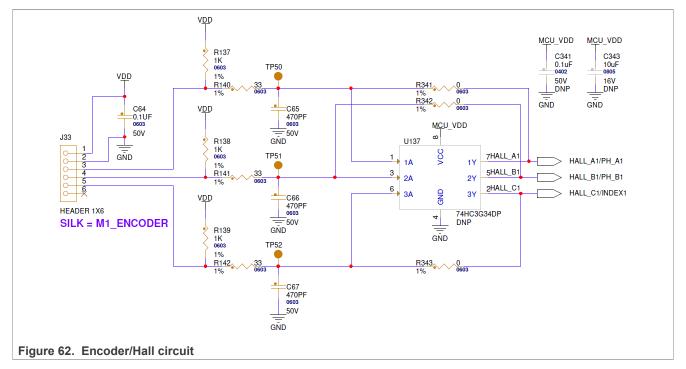

<u>Figure 6</u> shows block diagram of Adapter board - Rotor position signals processing and temperature processing. Adapter board supports resolver and encoder/hall signal processing for sensor-based motor control applications. Resolver signal processing circuit deals with resolver excitation, and sine-cosine signal processing. Those two functions are part of one block in figure above. Resolver sensor is connected to the system over resolver connector and microcontroller signals connection is managed over PCIe connector.

Signal processing of encoder/hall is carried out over different module. Encoder sensor or three Hall sensor can be connected over Encoder/Hall connector. An output signals of Encoder/Hall interface module are routed to the PCIe connector, where can be processed by appropriate peripheral of microcontroller. Both rotor position signal processing interfaces are duplicated in Adapter board, which allows to execute independent control of two 3-phase PMSM or BLDC motors with resolver or encoder/hall sensors.

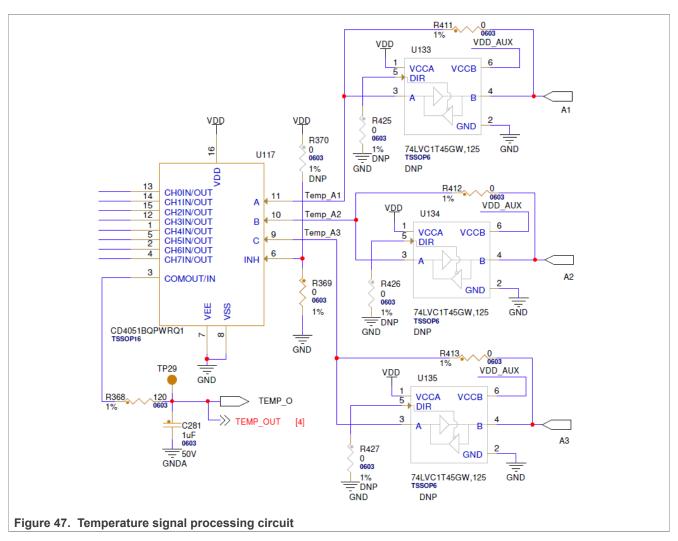

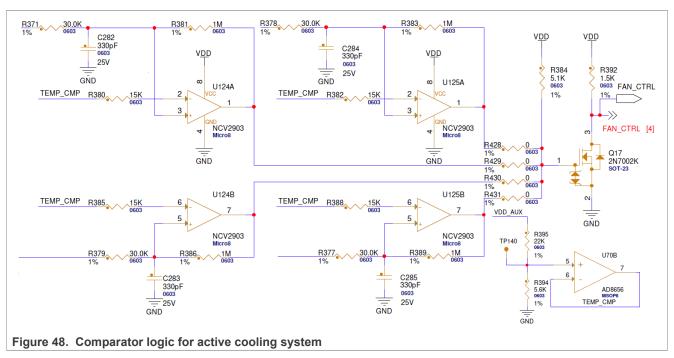

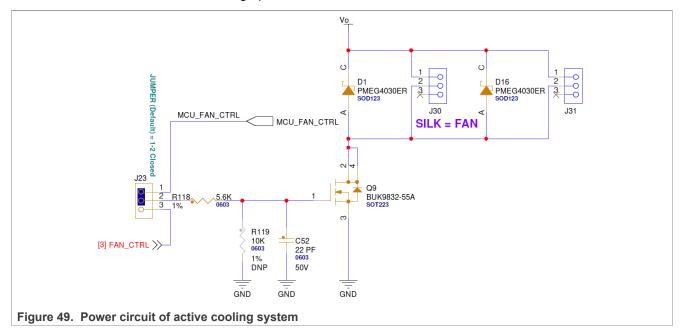

Eight analog signals of temperature are routed from header connectors to Analog multiplexer. Single output of multiplexer is routed to PCIe connector, but it is also used for over-temperature fault logic. An output of this fault logic is subsequently routed to the PCIe connector. Selection of input analog channels is managed by three GPIO pins of microcontroller routed from PCIe connector. Four specific analog signals of temperature and digital control signal from microcontroller are used for control of active cooling realized by fan control block. This block mainly processes signals of temperature and controls two fans either by four analog signals of temperature or by digital signal provided by microcontroller. Those two fans can be connected over fan connectors.

#### NXP 48V Motor Control Development Platform User Guide

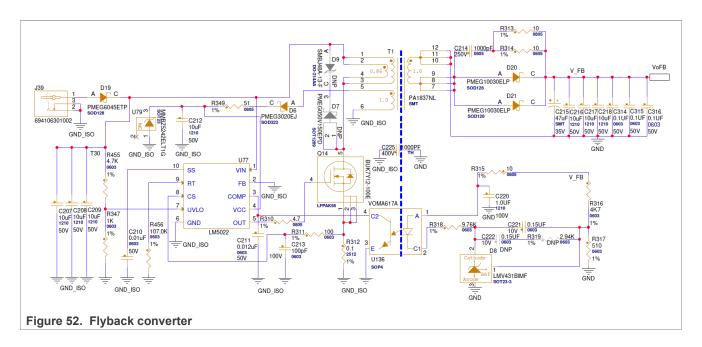

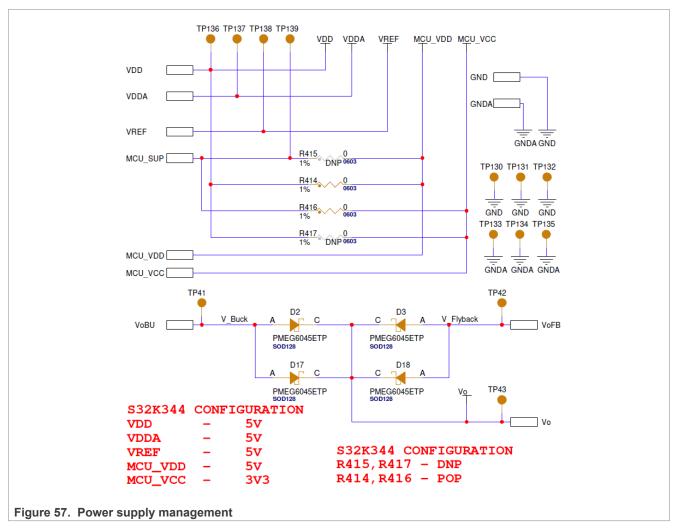

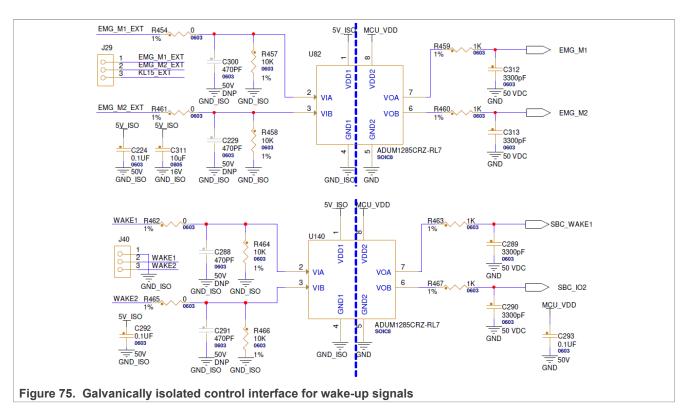

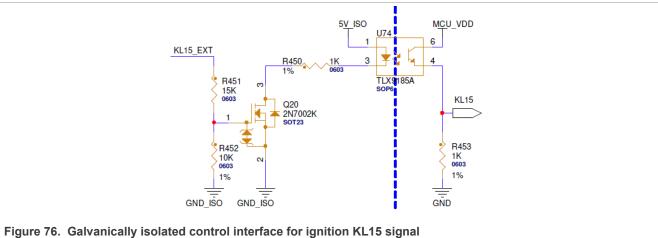

Figure 7. Block diagram of Adapter board - Isolated layer, Power supply management and Application control buttons

Figure 7 shows block diagram of Adapter board Isolated layer, Power supply management and Application control buttons. The Adapter board contains galvanically isolated circuitry with CAN transceiver, Flyback converter and Isolators for digital control and wake-up functionalities. This galvanically isolated layer allows to supply, control and communicate with NXP 48 V MC development platform from superior system. Digital signals of superior system can be connected over Header connector to the Isolator and can control or wake the system up. The control signal of superior system can only invoke pre-defined safe state i.e., if the system is not responding. The galvanically isolated CAN transceiver is responsible for communication of the superior system with NXP 48 V MC development platform. The Flyback converter represents redundant power supply source to the Buck converter. This isolated converter is in charge of overtaking the supply task in case of malfunction of Buck converter and it is powered from standalone 12 V battery. The output of Flyback converter is connected to Power Supply Management block. Additional LDO regulator provides power supply for circuitry of galvanically isolated layer. The Power Supply Management block connects the output voltage of Buck converter and output voltage of Flyback converter and provide output voltage Vo, which is routed to the header connector and PCIe connector. During normal operation of Buck converter, the output voltage Vo is equal to the Buck output voltage. If Buck converter operation is interrupted or faulty and do not provide sufficient voltage at output, the output voltage V<sub>0</sub> is equal to the Flyback output voltage. Main purpose of this Power Supply Management block is to keep the system alive in case that main power supply source failed. The power supply signals VDD, VDDA, MCU\_VDD, VREF and 3V3 are provided by Controller board and used for supplying of all circuitries of Adapter board. The VDD power supply signal is also transmitted to the Power stage board over header connector.

The Adapter board also contains buttons and switches which are dedicated for application control. Those application control signals are routed to the PCIe connector.

NXP 48V Motor Control Development Platform User Guide

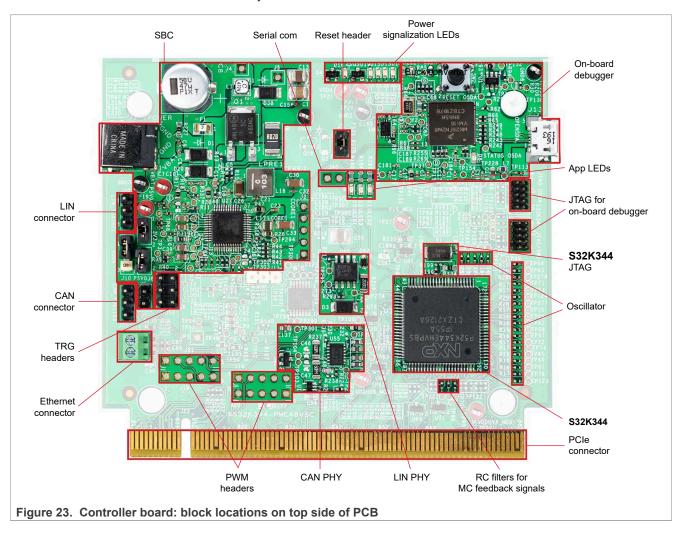

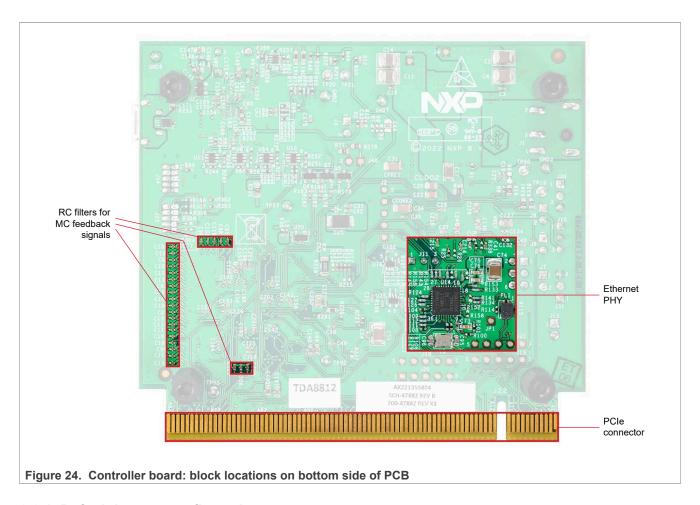

#### 1.3.3 Controller board architecture

Various block colour differentiate a block functionality:

- Green Motor control related hardware + 3-phase half-bridge

- Pink Application control

- Gray Interfaces and terminals

- Red Board power supply functionality

- Violet Communication interface

- Turquoise Microcontroller and application software download, and debug interface

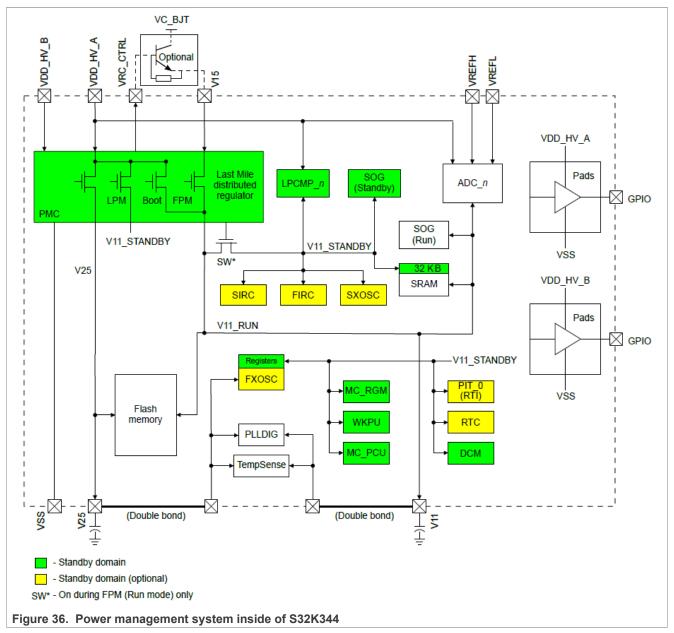

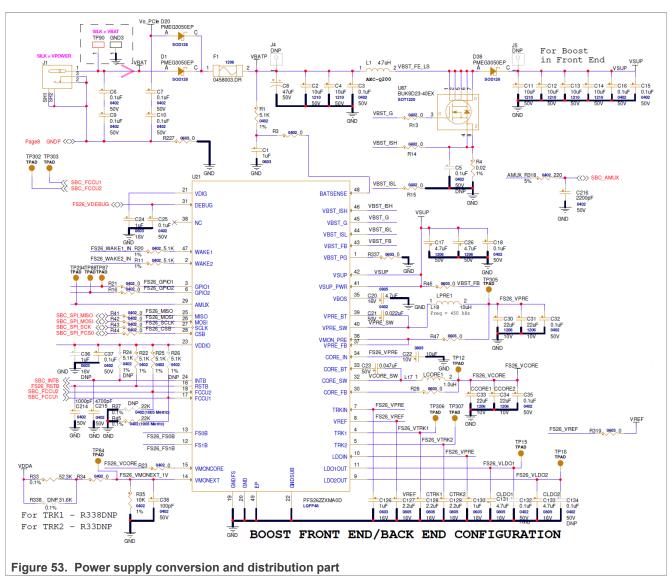

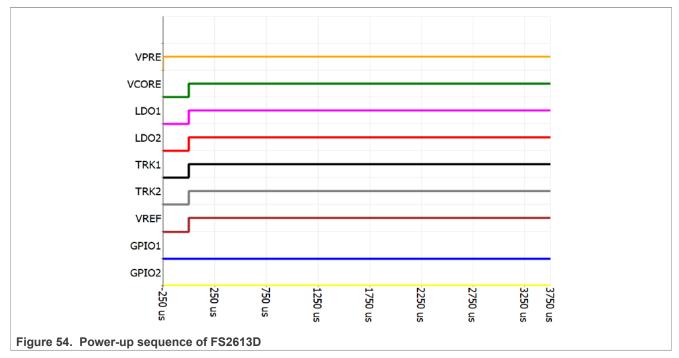

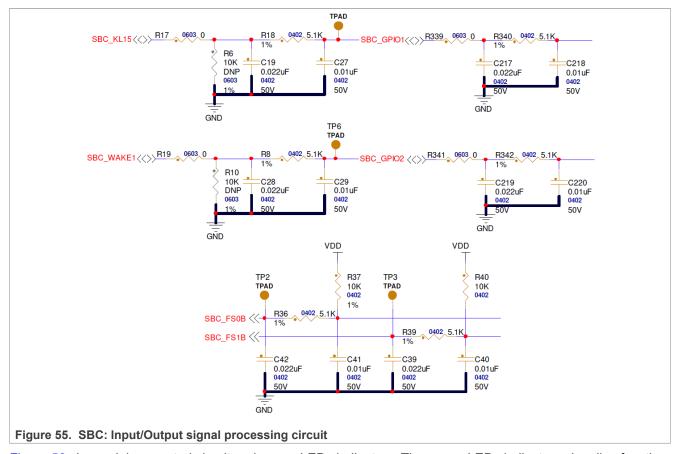

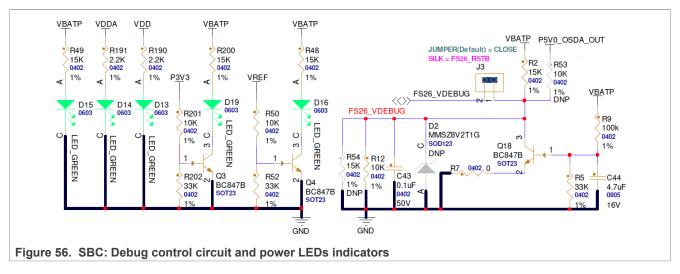

<u>Figure 8</u> shows simplified block diagram of Controller board. This board is in charge of controlling energy transformation process and establishes communication with environment. The main role of the board components is played by microcontroller S32K344, which is tightly linked with SBC FS2613D.

The SBC part provides power supply outputs for analog, digital, communication circuitry and microcontroller itself. Functionality of power supply outputs of SBC is signalized by Power supply LEDs. The System basis chip is powered by  $V_o$  input voltage from PCle connector. This input voltage is provided by Power supply management block situated in Adapter board. The SBC can be optionally powered through barrel connector, however the Controller board cannot be connected to the NXP 48 V MC development platform. The System basis chip offers also functional and safety features which supervise microcontroller operation or interact with external systems and allow to do pre-development of safety application. Fail-safe outputs (FS0/FS1B) of system basis chip are routed to the safe logic through PCle connector. The wake-up and control signals routed from galvanically isolated layer through PCle connector are connected to the input ports of SBC. The

## NXP 48V Motor Control Development Platform User Guide

FCCU0/1 signals are routed from SBC to the microcontroller and are responsible for HW failure monitoring of microcontroller. Communication of SBC with microcontroller is managed over SPI interface.

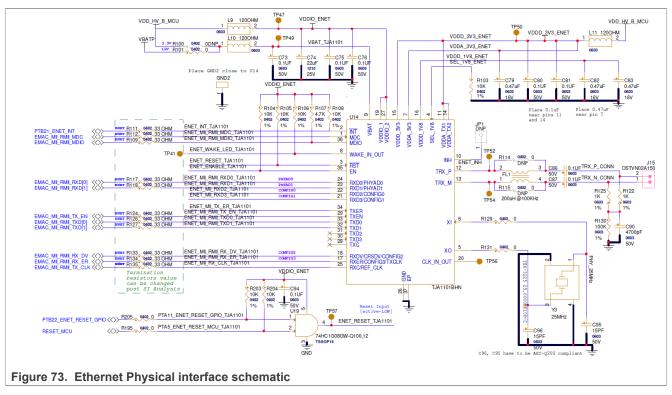

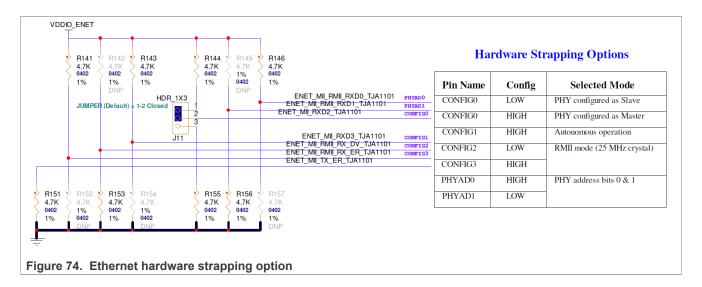

Automotive non-isolated communication interfaces CAN, LIN and Ethernet are a part of board circuit enablement. Those interfaces are connected to the microcontroller and output terminals are placed solely on Controller board. Software upload and its debugging can be carried out through JTAG interface or On-board debugger. This On-board debugger is capable to create virtual serial port for communication with FreeMASTER, which is useful tool for debugging and visualization. Trigger and PWM header connectors, user LEDs support application debugging. ADC filters are used for analog signals filtering. The motor fault signals of over-current, over-voltage Buck monitoring malfunction and desaturation fault of pre-charge MOSFETs are processed by logic OR function in order to create common and standalone fault signals for first motor configurations and second motor configuration.

## 2 NXP 48V MC Development platform PCB description

NXP 48V Motor Control Development Platform User Guide

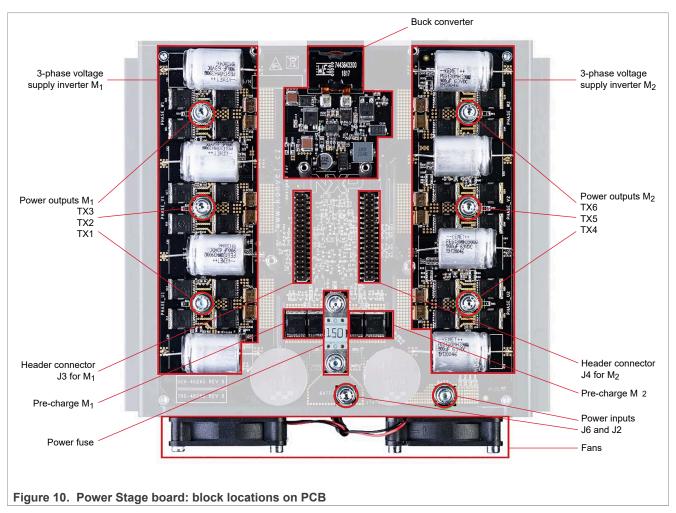

## 2.1 Power Stage board PCB description

The Power Stage board does not contain any jumper configuration for flexible change of circuit configuration or any test point due to direct and close connection of adapter board. The following sections summarize the onboard headers, connectors and their pinouts and signal meanings.

#### 2.1.1 Power supply, power outputs and fuse holder

The Power Stage board input and output terminals are populated by power bolts, which reduce power losses during energy transfer. These power bolts have threaded metric hole M3 for wiring ring-eye terminals. Beside of input and output terminals, those power bolts are also used for fuse connection, which is placed between positive input terminal and both pre-charge circuits. Use appropriate wires and high conductivity terminals to connect your power source and motor load. In the following table, there is summary of power bolt connectors placed on Power Stage board.

## NXP 48V Motor Control Development Platform User Guide

TE Connectivity part no. 225858-E

Table 2. Power input, output, and fuse terminals

| Terminals | Signal name | Description          |

|-----------|-------------|----------------------|

| J1        | P48V        | Power supply (+) pin |

| J2        | -VIN        | Power supply (-) pin |

| J5        | P48V        | Fuse terminal A      |

| J6        | +VIN        | Fuse terminal B      |

| TX1       | U1          | Power Output Phase A |

| TX2       | V1          | Power Output Phase B |

| TX3       | W1          | Power Output Phase C |

| TX4       | U2          | Power Output Phase D |

| TX5       | V2          | Power Output Phase E |

| TX6       | W2          | Power Output Phase F |

#### 2.1.2 Header connector

The Power Stage board is populated by two header connectors in order to transfer signals between Adapter board and Power Stage board. In addition, header connectors provide robust connection of those two boards. The connectors pinout description is summarized in the following table.

Figure 12. Header connector for first and second MOSFET half-bridg

Matting connector: part no. SSW-117-01-S-D Fischer Electronic SL16 SMD 247

Table 3. Pinout description of header J3 for first 3-phase MOSFET half-bridge

| Terminals | Signal name    | Description                                                            |

|-----------|----------------|------------------------------------------------------------------------|

| 1         | D_PWM1         | Safe PWM signal phase A top                                            |

| 2         | D_PWM2         | Safe PWM signal phase A bottom                                         |

| 3         | D_PWM3         | Safe PWM signal phase B top                                            |

| 4         | D_PWM4         | Safe PWM signal phase B bottom                                         |

| 5         | D_PWM5         | Safe PWM signal phase C top                                            |

| 6         | D_PWM6         | Safe PWM signal phase C bottom                                         |

| 7         | OVCI_1         | Desaturation fault of pre-charge MOSFETs for first DC-link             |

| 8         | /STO_0         | Shutdown for first 3-phase MOSFET half-bridge                          |

| 9         | VDD            | Digital power supply                                                   |

| 10        | ON_1           | Enable of pre-charge for first 3-phase MOSFET half-bridge              |

| 11        | U1_SENSE       | BEMF_A                                                                 |

| 12        | U1_NTC         | Temperature of Phase A                                                 |

| 13        | V1_SENSE       | BEMF_B                                                                 |

| 14        | V1_NTC         | Temperature of Phase B                                                 |

| 15        | W1_SENSE       | BEMF_C                                                                 |

| 16        | W1_NTC         | Temperature of Phase C                                                 |

| 17        | VBAT_SENSE     | Battery voltage                                                        |

| 18        | PRECHARGE1_NTC | Temperature of pre-charge MOSFETs for first 3-phase MOSFET half-bridge |

| 19        | VFW1_SENSE     | Forward voltage of first 3-phase MOSFET half-bridge                    |

| 20        | VDCL1_SENSE    | DC-link voltage of first 3-phase MOSFET half-bridge                    |

| 21        | IU1_P          | Phase A current (+) positive                                           |

| 22        | IU1_N          | Phase A current (-) negative                                           |

| 23        | IV1_P          | Phase B current (+) positive                                           |

| 24        | IV1_N          | Phase B current (-) negative                                           |

| 25        | IW1_P          | Phase C current (+) positive                                           |

| 26        | IW1_N          | Phase C current (-) negative                                           |

| 27        | GNDA           | Analog ground                                                          |

| 28        | GNDA           | Analog ground                                                          |

| 29        | GND            | Digital ground                                                         |

| 30        | GND            | Digital ground                                                         |

| 31        | VoBU           | Buck converter output voltage                                          |

| 32        | Vo             | Output voltage of Buck or Flyback converter                            |

| 33        | VoBU           | Buck converter output voltage                                          |

| 34        | Vo             | Output voltage of Buck or Flyback converter                            |

Table 4. . Pinout description of header J4 for second 3-phase MOSFET half-bridge

| Terminals | Signal name    | Description                                                      |

|-----------|----------------|------------------------------------------------------------------|

| 1         | D_PWM6         | Safe PWM signal phase D top                                      |

| 2         | D_PWM7         | Safe PWM signal phase D bottom                                   |

| 3         | D_PWM8         | Safe PWM signal phase E top                                      |

| 4         | D_PWM9         | Safe PWM signal phase E bottom                                   |

| 5         | D_PWM10        | Safe PWM signal phase F top                                      |

| 6         | D_PWM11        | Safe PWM signal phase F bottom                                   |

| 7         | OVCI_2         | Desaturation fault of pre-charge MOSFETs for second DC-link      |

| 8         | /STO_1         | Shutdown for second 3-phase MOSFET half-bridge                   |

| 9         | VDD            | Digital power supply                                             |

| 10        | ON_2           | Enable of pre-charge for second 3-phase MOSFET half-bridge       |

| 11        | U2_SENSE       | BEMF_D                                                           |

| 12        | U2_NTC         | Temperature of Phase D                                           |

| 13        | V2_SENSE       | BEMF_E                                                           |

| 14        | V2_NTC         | Temperature of Phase E                                           |

| 15        | W2_SENSE       | BEMF_F                                                           |

| 16        | W2_NTC         | Temperature of Phase F                                           |

| 17        | VBAT_SENSE     | Battery voltage                                                  |

| 18        | PRECHARGE2_NTC | Temperature of pre-charge MOSFETs for second 3-phase half-bridge |

| 19        | VFW2_SENSE     | Forward voltage of second 3-phase MOSFET half-bridge             |

| 20        | VDCL2_SENSE    | DC-link voltage of second 3-phase MOSFET half-bridge             |

| 21        | IU2_P          | Phase D current (+) positive                                     |

| 22        | IU2_N          | Phase D current (-) negative                                     |

| 23        | IV2_P          | Phase E current (+) positive                                     |

| 24        | IV2_N          | Phase E current (-) negative                                     |

| 25        | IW2_P          | Phase F current (+) positive                                     |

| 26        | IW2_N          | Phase F current (-) negative                                     |

| 27        | GNDA           | Analog ground                                                    |

| 28        | GNDA           | Analog ground                                                    |

| 29        | GND            | Digital ground                                                   |

| 30        | GND            | Digital ground                                                   |

| 31        | VoBU           | Buck converter output voltage                                    |

| 32        | Vo             | Output voltage of Buck or Flyback converter                      |

| 33        | VoBU           | Buck converter output voltage                                    |

| 34        | Vo             | Output voltage of Buck or Flyback converter                      |

## NXP 48V Motor Control Development Platform User Guide

## 2.2 Adapter board PCB description

## NXP 48V Motor Control Development Platform User Guide

## 2.2.1 Default jumper configuration

The Adapter board contains several jumpers and allows to change configuration of several circuits based on user requirements. Description and particular configuration of Adapter board jumpers are summarized in the following table.

Table 5. Adapter board jumper configuration

| Jumper        | Function                                                                    | Setting | Description                                            |

|---------------|-----------------------------------------------------------------------------|---------|--------------------------------------------------------|

| J16, J17, J18 | Phase current or BEMF voltage signals for first 3-phase MOSFET half-bridge  | 1-2     | BEMF voltage measurement (Block commutation technique) |

|               |                                                                             | 2-3     | Phase current measurement (FOC technique) (default)    |

| J19, J20, J21 | Phase current or BEMF voltage signals for second 3-phase MOSFET half-bridge | 1-2     | BEMF voltage measurement (Block commutation technique) |

|               |                                                                             | 2-3     | Phase current measurement (FOC technique) (default)    |

## NXP 48V Motor Control Development Platform User Guide

Table 5. Adapter board jumper configuration...continued

| J2, J5, J6, J7,<br>J8, J9       | Current measurement gain configuration of first 3-phase MOSFET half-bridge  | Open  | Operational amplifiers gain is set to 50 (default)              |

|---------------------------------|-----------------------------------------------------------------------------|-------|-----------------------------------------------------------------|

|                                 |                                                                             | Close | Operational amplifiers gain is set to 25                        |

| J10, J11, J12,<br>J13, J14, J15 | Current measurement gain configuration of second 3-phase MOSFET half-bridge | Open  | Operational amplifiers gain is set to 50 (default)              |

|                                 |                                                                             | Close | Operational amplifiers gain is set to 25                        |

| J23                             | Fan control                                                                 | 1-2   | Autonomous mode of fan control                                  |

|                                 |                                                                             | 2-3   | Microcontroller mode of fan control (default)                   |

| J37                             | Selection Reset 1 or Reset 2 for power                                      | 1-2   | Reset M1 resets latched fault of Buck monitor                   |

|                                 | supply fault monitor                                                        | 2-3   | Reset M2 resets latched fault of Buck monitor(default)          |

| J24                             | Fault logic reference voltage                                               | 1-2   | VREF is selected as reference voltage for fault logic (default) |

|                                 |                                                                             | 2-3   | VDDA is selected as reference voltage for fault logic           |

| J25                             | First 3-phase half-bridge safe state activation (by fault logic)            | 1-2   | Safe open activated by operational faults (default)             |

|                                 |                                                                             | 2-3   | Safe short activated by operational faults                      |

| J26                             | First 3-phase half-bridge safe state activation (by superior system)        | 1-2   | Safe short activated by superior system                         |

|                                 |                                                                             | 2-3   | Safe open activated by superior system (default)                |

| J27                             | Second 3-phase half-bridge safe state activation (by fault logic)           | 1-2   | Safe open activated by operational faults (default)             |

|                                 |                                                                             | 2-3   | Safe short activated by operational faults                      |

| J28                             | Second 3-phase half-bridge safe state                                       | 1-2   | Safe short activated by superior system                         |

|                                 | activation (by superior system)                                             | 2-3   | Safe open activated by superior system (default)                |

#### 2.2.2 Socket connector

The Adapter board is populated by two socket connectors in order to transfer signals of both 3-phase MOSFET half-bridges separately. Signals are transferred in between Power Stage board and Adapter board. The connector pinout description is summarized in the following table.

Figure 15. Socket connector for first and second 3-phase MOSFET half-bridge

Matting connector: Fischer Electronic SL16 SMD 247 Samtec part no. SSW-117-01-S-D

UG10246

Table 6. Pinout description of socket connector J3 for first 3-phase MOSFET half-bridge

| Terminals | Signal name      | Description                                                            |

|-----------|------------------|------------------------------------------------------------------------|

| 1         | D_PWM1           | Safe PWM signal phase A top                                            |

| 2         | D_PWM2           | Safe PWM signal phase A bottom                                         |

| 3         | D_PWM3           | Safe PWM signal phase B top                                            |

| 4         | D_PWM4           | Safe PWM signal phase B bottom                                         |

| 5         | D_PWM5           | Safe PWM signal phase C top                                            |

| 6         | D_PWM6           | Safe PWM signal phase C bottom                                         |

| 7         | OC_DCL_M1        | Desaturation fault of pre-charge MOSFETs for first DC-link             |

| 8         | /STO_0           | Shutdown for first 3-phase MOSFET half-bridge                          |

| 9         | MCU_VDD          | Digital power supply                                                   |

| 10        | S_ON_M1          | Enable of pre-charge for first 3-phase MOSFET half-bridge              |

| 11        | U1_SENSE         | BEMF_A                                                                 |

| 12        | U1_NTC           | Temperature of Phase A                                                 |

| 13        | V1_SENSE         | BEMF_B                                                                 |

| 14        | V1_NTC           | Temperature of Phase B                                                 |

| 15        | W1_SENSE         | BEMF_C                                                                 |

| 16        | W1_NTC           | Temperature of Phase C                                                 |

| 17        | VBAT_SENSE       | Battery voltage                                                        |

| 18        | PRECHARGE_M1_NTC | Temperature of pre-charge MOSFETs for first 3-phase MOSFET half-bridge |

| 19        | VFW_M1_SENSE     | Forward voltage of first 3-phase MOSFET half-bridge                    |

| 20        | VDCL_M1_SENSE    | DC-link voltage of first 3-phase MOSFET half-bridge                    |

| 21        | IU1_P            | Phase A current (+) positive                                           |

| 22        | IU1_N            | Phase A current (-) negative                                           |

| 23        | IV1_P            | Phase B current (+) positive                                           |

| 24        | IV1_N            | Phase B current (-) negative                                           |

| 25        | IW1_P            | Phase C current (+) positive                                           |

| 26        | IW1_N            | Phase C current (-) negative                                           |

| 27        | GNDA             | Analog ground                                                          |

| 28        | GNDA             | Analog ground                                                          |

| 29        | GND              | Digital ground                                                         |

| 30        | GND              | Digital ground                                                         |

| 31        | VoBU             | Buck converter output voltage                                          |

| 32        | Vo               | Output voltage of Buck or Flyback converter                            |

| 33        | VoBU             | Buck converter output voltage                                          |

| 34        | Vo               | Output voltage of Buck or Flyback converter                            |

Table 7. Pinout description of socket J4 for second 3-phase MOSFET half-bridge

| Terminals | Signal name      | Description                                                      |

|-----------|------------------|------------------------------------------------------------------|

| 1         | D_PWM6           | Safe PWM signal phase D top                                      |

| 2         | D_PWM7           | Safe PWM signal phase D bottom                                   |

| 3         | D_PWM8           | Safe PWM signal phase E top                                      |

| 4         | D_PWM9           | Safe PWM signal phase E bottom                                   |

| 5         | D_PWM10          | Safe PWM signal phase F top                                      |

| 6         | D_PWM11          | Safe PWM signal phase F bottom                                   |

| 7         | OC_DCL_M2        | Desaturation fault of pre-charge MOSFETs for second DC-link      |

| 8         | /STO_1           | Shutdown for second 3-phase MOSFET half-bridge                   |

| 9         | MCU_VDD          | Digital power supply                                             |

| 10        | S_ON_M2          | Enable of pre-charge for second 3-phase MOSFET half-bridge       |

| 11        | U2_SENSE         | BEMF_D                                                           |

| 12        | U2_NTC           | Temperature of Phase D                                           |

| 13        | V2_SENSE         | BEMF_E                                                           |

| 14        | V2_NTC           | Temperature of Phase E                                           |

| 15        | W2_SENSE         | BEMF_F                                                           |

| 16        | W2_NTC           | Temperature of Phase F                                           |

| 17        | VBAT_SENSE       | Battery voltage                                                  |

| 18        | PRECHARGE_M2_NTC | Temperature of pre-charge MOSFETs for second 3-phase half-bridge |

| 19        | VFW_M2_SENSE     | Forward voltage of second 3-phase MOSFET half-bridge             |

| 20        | VDCL_M2_SENSE    | DC-link voltage of second 3-phase MOSFET half-bridge             |

| 21        | IU2_P            | Phase D current (+) positive                                     |

| 22        | IU2_N            | Phase D current (-) negative                                     |

| 23        | IV2_P            | Phase E current (+) positive                                     |

| 24        | IV2_N            | Phase E current (-) negative                                     |

| 25        | IW2_P            | Phase F current (+) positive                                     |

| 26        | IW2_N            | Phase F current (-) negative                                     |

| 27        | GNDA             | Analog ground                                                    |

| 28        | GNDA             | Analog ground                                                    |

| 29        | GND              | Digital ground                                                   |

| 30        | GND              | Digital ground                                                   |

| 31        | VoBU             | Buck converter output voltage                                    |

| 32        | Vo               | Output voltage of Buck or Flyback converter                      |

| 33        | VoBU             | Buck converter output voltage                                    |

| 34        | Vo               | Output voltage of Buck or Flyback converter                      |

## NXP 48V Motor Control Development Platform User Guide

## 2.2.3 PCIe connector - socket

The purpose of this connector is to connect Adapter board and Controller board to each other and ensure sufficient mechanical robustness. High number of ports allows to transfer numerous analogs, digital or power supply signals. The pinout description of this connector is compressed and summarized in the following table.

Amphenol ICC part no. 10082378-11113TLF

Table 8. Pinout description of PCle J1 female connector

| Terminals                                                     | Signal name                             | Description                                                           |

|---------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------|

| B1                                                            | VREF                                    | Reference voltage                                                     |

| B2, B11, B82,<br>A2, A11, A82                                 | GNDA                                    | Analog ground                                                         |

| B3, B74, B81, A6,<br>A7, A10, A77-79                          | Analog input                            | Spare analog inputs                                                   |

| B4                                                            | V_DCL_M1                                | DC-link voltage of first 3-phase MOSFET half-bridge                   |

| B5                                                            | V_FW_M1                                 | Forward voltage of first 3-phase MOSFET half-bridge                   |

| B6                                                            | V_BAT                                   | Battery voltage                                                       |

| B7-9                                                          | BEMF_U1/V1/W1                           | BEMF voltages of first motor                                          |

| B10                                                           | TEMP                                    | Temperature of power stage                                            |

| B12                                                           | MCU_SUP                                 | Voltage for specific MCU ports                                        |

| B13, B32, B51, A13, A51                                       | GND                                     | Digital ground                                                        |

| B14-16                                                        | HALL_A1/B1/C1 –<br>PH_A1, PH_B2, INDEX1 | Hall/Encoder signals of first motor                                   |

| B17-18, B34, B38-39,<br>B41, B45, B50, B55,<br>B64-69, B72-73 | Not connected                           | N/A                                                                   |

| B19, A8, A9                                                   | EXC_M1, SIN_M1, COS_M1                  | Resolver excitation and sin/cos signals for first motor configuration |

| B20, A31, A32                                                 | SW_RUN/UP/DOWN_M1                       | Application control signals for first motor configuration             |

| B21-24                                                        | MISO/MOSI/SCK/SS                        | SPI signals (not applicated in 48V platform)                          |

Table 8. Pinout description of PCle J1 female connector...continued

| olo ol i illout docolipi | ion of Fole 31 female confidencialco   | nunaca                                                             |

|--------------------------|----------------------------------------|--------------------------------------------------------------------|

| Terminals                | Signal name                            | Description                                                        |

| B25, A69                 | SBC_FS0B/FS1B                          | Fault safe signals of SBC                                          |

| B26-27                   | SCI_TX/SCI_RX                          | Serial communication (not applicated in 48V platform)              |

| B28                      | SW_ON_M1                               | Enable of DC-link pre-charge for first 3-phase MOSFET half-bridge  |

| B29                      | DRV_ON_M1                              | Enable of gate-drivers for first 3-<br>phase MOSFET half-bridge    |

| B30, A29                 | BUCK_FAULT_L, BUCK_FAULT               | Fault of Buck converter: latched and non-latched                   |

| B31                      | Vo                                     | Output voltage of Buck or Flyback converter                        |

| B33, A33                 | CAN_RX, CAN_TX                         | CAN receive and transmit signals for isolated CAN PHY              |

| B35-37                   | HALL_A2/B2/C2 –<br>PH_A1 PH_B2, INDEX2 | Hall/Encoder signals of second motor                               |

| B40, A80, A81            | EXC_M2, SIN_M2, COS_M2                 | Resolver excitation and sin/cos signals for second moto            |

| B42-44                   | A1-3                                   | Temperature multiplexor control signals                            |

| B46                      | MCU_RUN                                | Control of fan by microcontroller                                  |

| B47-49                   | SW_RUN/UP/DOWN_M2                      | Application control signals for second motor configuration         |

| B52                      | M2_RESET                               | Reset of latched faults for second motor configuration             |

| B53                      | DRV_ON_M2                              | Enable of gate-drivers for second<br>3-phase MOSFET half-bridge    |

| B54                      | SW_ON_M2                               | Enable of DC-link pre-charge for second 3-phase MOSFET half-bridge |

| B56-58, A59-61           | TRG4/5/6/3/2/1                         | MCU trigger signals (not used in 48V system)                       |

| B59-61                   | SBC_WAKE1, SBC_IO2/3                   | SBC input ports (IO3 – not used in 48V system)                     |

| B62-63, B70-71           | I/O_28/29, GPIO2/4                     | Input/Output ports (not used in 48V system)                        |

| B75                      | V_DCL_M2                               | DC-link voltage of second 3-phase MOSFET half-bridge               |

| B76                      | V_FW_M2                                | Forward voltage of second 3-phase MOSFET half-bridg                |

| B78-80                   | BEMF_U2/V2/W2                          | BEMF voltages for second motor                                     |

| A1                       | VDDA                                   | Supply voltage for analog circuitry                                |

| A3-5                     | I_PHA/B/C – BEMF_U1/V1/W1              | Phase currents or BEMF voltages of first motor configuration       |

| A12                      | VDD                                    | Supply voltage for digital circuitry                               |

| A14-A21                  | PWM1-6, PWM13-14                       | PWM signals for first 3-phase MOSFET half-bridge                   |

| A22-24                   | PHA, PHB, PHC                          | Phase voltage digital signals of first motor                       |

| A26-28                   | OC/OV/OC_DCL_M1                        | Latched faults of first motor configuration                        |

| A30                      | M1_RESET                               | Reset of latched faults for first motor configuration              |

| A35-42                   | PWM7-12, PWM18-19                      | PWM signals for second 3-phase MOSFET half-bridge                  |

| A43-45                   | PHD, PHE, PHF                          | Phase voltage digital signals of second motor                      |

| A47-49                   | OC/OV/OC_DCL_M2                        | Latched faults for second motor configuration                      |

| A50                      | ОТ                                     | Over-temperature fault                                             |

## NXP 48V Motor Control Development Platform User Guide

Table 8. Pinout description of PCle J1 female connector...continued

| Terminals | Signal name               | Description                                                   |

|-----------|---------------------------|---------------------------------------------------------------|

| A52-57    | TM13-18                   | Spare timer inputs (not used in 48V system)                   |

| A68       | KL15                      | Ignition switch                                               |

| A70       | FAN_CTRL                  | Monitoring of autonomous control of fan                       |

| A71-73    | APP_LED2/3/1              | Application LED signals (not used in 48V system)              |

| A74-76    | I_PHD/E/F – BEMF_U2/V2/W2 | Phase currents or BEMF voltages of second motor configuration |

#### 2.2.4 Fan connector

Adapter board has an interface, which is intended to power two external fans. External fans actively support cooling of Power Stage board. There are two connectors for two external fans, which are connected to the same signals. The pinout description is summarized in the following table.

Mating connector: part No. MX-22-01-3037 Molex part no. 22-23-2031

Table 9. Pinout description of fan connectors J30 and J31

| Terminals | Signal name  | Description   |

|-----------|--------------|---------------|

| 1         | Positive (+) | Positive pole |

| 2         | Negative (-) | Negative pole |

| 3         | NC           | N/A           |

#### 2.2.5 Rotor position sensors interface

There are two types of interfaces for rotor position sensors. Hall/Encoder rotor position interface utilizes connector with 6 pins, which pinout description is summarized in <u>Table 10</u>. Resolver position interface utilizes connector with 8 pins, which pinout description is summarized in <u>Table 11</u>. The Adapter board contains two sets of resolver and Hall/Encoder rotor position sensor interfaces to support dual motor control operation.

## NXP 48V Motor Control Development Platform User Guide

Figure 18. Hall/Encoder sensor connector

Mating connector: part No.22-01-2061 Molex part no. 22-27-2061

Table 10. Pinout description of Hall/Encoder connectors

| Terminals     | Signal name                       | Description                            |  |  |

|---------------|-----------------------------------|----------------------------------------|--|--|

|               | J33 connector                     |                                        |  |  |

| 1             | VDD                               | Positive (+) pin                       |  |  |

| 2             | GND                               | Negative (-) pin                       |  |  |

| 3             | HALL_A/PH_A                       | Input signal Hall A/Encoder Channel A  |  |  |

| 4             | HALL_B/PH_B                       | Input signal Hall B/ Encoder Channel B |  |  |

| 5             | HALL_C/INDEX1                     | Input signal Hall C/ Encoder Index 1   |  |  |

| 6             | Not connected                     | N/A                                    |  |  |

| J34 connector |                                   |                                        |  |  |

| Terminals     | Terminals Signal name Description |                                        |  |  |

| 1             | VDD                               | Positive (+) pin                       |  |  |

| 2             | GND                               | Negative (-) pin                       |  |  |

| 3             | HALL_D/PH_D                       | Input signal Hall D/Encoder Channel D  |  |  |

| 4             | HALL_E/PH_E                       | Input signal Hall E/ Encoder Channel E |  |  |

| 5             | HALL_F/INDEX2                     | Input signal Hall F/ Encoder Index 2   |  |  |

| 6             | Not connected                     | N/A                                    |  |  |

Mating connector: part No.22-01-2087 Molex part no. 22-23-2031

## NXP 48V Motor Control Development Platform User Guide

Table 11. Pinout description of Resolver connectors

| Terminals | Signal name    | Description                                  |  |  |  |

|-----------|----------------|----------------------------------------------|--|--|--|

|           | J35 connector  |                                              |  |  |  |

| 1         | RES_GENP_M1    | Square signal, 10kHz output                  |  |  |  |

| 2         | RES_GENM_M1    | for first motor configuration                |  |  |  |

| 3         | RES_SIN_M1     | Resolver sine signal input for first motor   |  |  |  |

| 4         | RES_SIN_REF_M1 |                                              |  |  |  |

| 5         | RES_COS_M1     | Resolver cosine signal input for first motor |  |  |  |

| 6         | RES_COS_REF_M1 |                                              |  |  |  |

| 7         | GND            | Ground                                       |  |  |  |

| 8         | VDDA           | Analog power supply                          |  |  |  |

|           | J36 connector  |                                              |  |  |  |

| 1         | RES_GENP_M2    | Square signal 10kHz output                   |  |  |  |

| 2         | RES_GENM_M2    | for second motor configuration               |  |  |  |

| 3         | RES_SIN_M2     | Resolver sine signal input for second motor  |  |  |  |

| 4         | RES_SIN_REF_M2 |                                              |  |  |  |

| 5         | RES_COS_M2     | Resolver cosine signal                       |  |  |  |

| 6         | RES_COS_REF_M2 | input for second motor                       |  |  |  |

| 7         | GND            | Ground                                       |  |  |  |

| 8         | VDDA           | Analog power supply                          |  |  |  |

## 2.2.6 Isolated layer interface

Adapter board isolated layer contains flyback converter as a redundant power supply source. This converter is supplied from external 12 V voltage source by Center Positive Barrel type connector with outer diameter 5.5mm, inner diameter 2.1mm. Supervisor system is connected to system by means of two 3-pin header connectors (Figure 21), which allow to transfer control and wake-up signals. CAN communication interface uses Molex type of connector (Figure 22). The pinout descriptions of all mentioned connectors are summarized in tables below:

Figure 20. Power supply barrel connector for flyback converter

Mating connector: KLDX-PA-0202-A-LT Wurth Electronic part no. 694106301002

## NXP 48V Motor Control Development Platform User Guide

Table 12. Pinout description of power supply jack J39 for flyback converter

| Terminals | Signal name | Description             |

|-----------|-------------|-------------------------|

| 1         | T30         | Positive input pin      |

| 2         | GND         | Digital isolated ground |

| 3         | GND         | Digital isolated ground |

Figure 21. Header connector for external digital signals and Ignition signal

Samtec part no. TSW-103-14-G-S

Table 13. Pinout description of header connectors for external control signals

| Terminals | Signal name                   | Description                                     |  |  |

|-----------|-------------------------------|-------------------------------------------------|--|--|

|           | J29 connector                 |                                                 |  |  |

| 1         | EMG_M1_EXT                    | Energency signal for first motor configuration  |  |  |

| 2         | EMG_M2_EXT                    | Energency signal for second motor configuration |  |  |

| 3         | KL15_EXT                      | Ignition signal                                 |  |  |

|           | J40 connector                 |                                                 |  |  |

| Terminals | inals Signal name Description |                                                 |  |  |

| 1         | GND                           | Digital isolated ground                         |  |  |

| 2         | WAKE1                         | First wake up signal                            |  |  |

| 3         | WAKE2                         | Second wake up signal                           |  |  |

Figure 22. CAN connector of isolated CAN communication interface

## NXP 48V Motor Control Development Platform User Guide

Mating connector: part No. 39-01-4040 Molex part no. 39-30-3047

Table 14. Pinout description of CAN connector J32

| Terminals | Signal name   | Description             |

|-----------|---------------|-------------------------|

| 1         | CAN_H         | CAN_HI signal           |

| 2         | CAN_L         | CAN_LI signal           |

| 3         | GND           | Isolated digital ground |

| 4         | Not connected | N/A                     |

## 2.2.7 Test points of Adapter board

The below summarizes test points of Adapter board.

Table 15. Adapter board test points

| Test point          | Signal name                      | Description                                                                              |

|---------------------|----------------------------------|------------------------------------------------------------------------------------------|

| TP1, TP2, TP3       | I_PHA, I_PHB, I_PHC              | Phase currents for first motor configuration                                             |

| TP4, TP8            | VA_REF_M1, VA_REF_M2             | Reference for bidirectional current measurement for first and second motor configuration |

| TP5, TP6, TP7       | I_PHD, I_PHE, I_PHF              | Phase currents for second motor configuration                                            |

| TP9, TP10, TP11     | U1_SENSE, V1_<br>SENSE, W1_SENSE | BEMF voltages of first motor                                                             |

| TP12,<br>TP13, TP14 | U2_SENSE, V2_<br>SENSE, W2_SENSE | BEMF voltages of second motor                                                            |

| TP18                | VDCL_M1_SENSE                    | DC-link voltage of first 3-phase MOSFET half-bridge                                      |

| TP19                | VDCL_M2_SENSE                    | DC-link voltage of second 3-phase MOSFET half-bridge                                     |

| TP20,<br>TP21, TP22 | PH_V_A, PH_V_B, PH_V_C           | Phase voltage digital signals of first motor                                             |

| TP23,<br>TP24, TP25 | PH_V_D, PH_V_E, PH_V_F           | Phase voltage digital signals of second motor                                            |

| TP123, TP124        | V_REF_M1, V_REF_M2               | Voltage references for phase voltage reconstruction of first and second motor            |

| TP29                | TEMP_OUT                         | Temperature of power stage                                                               |

| TP31,<br>TP32, TP33 | U1_TEMP, V1_TEMP, W1_TEMP        | Temperature of first 3-phase MOSFET half-bridge                                          |

| TP34                | PCH1_TEMP                        | Temperature of DC-link pre-charge MOSFETs for first 3-phase MOSFET half-bridge           |

| TP35,<br>TP36, TP37 | U2_TEMP, V2_TEMP, W2_TEMP        | Temperature of second 3-phase MOSFET half-bridge                                         |

| TP38                | PCH2_TEMP                        | Temperature of DC-link pre-charge MOSFETs for second 3-phase MOSFET half-bridge          |

| TP140               | VDD_AUX_REF                      | Voltage reference for temperature measurement                                            |

| 17 140              | VDD_NOX_INEI                     | g                                                                                        |

| TP40                | V_TH_REF_OT                      | Voltage reference for over-temperature monitoring                                        |

Table 15. Adapter board test points...continued

| Test point          | board test pointscontinued Signal name | Description                                                                                   |

|---------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|

| TP41                | V Buck                                 | Buck output voltage                                                                           |

| TP42                | V_Buck<br>V Flyback                    | Flyback output voltage                                                                        |

| TP43                | V_FIYDACK<br>Vo                        | Output voltage of Buck or Flyback converter                                                   |

| TP43                | 1                                      | , , , , , , , , , , , , , , , , , , ,                                                         |

|                     | V_Buck Scaled                          | Scaled voltage of Buck converter                                                              |

| TP45                | BUCK_FAULT                             | Fault of Buck converter: non-latched                                                          |

| TP47                | BUCK_FAULT_L                           | Fault of Buck converter: latched                                                              |

| TP130-132           | GND                                    | Digital ground                                                                                |

| TP133-135           | GNDA                                   | Analog ground                                                                                 |

| TP136               | VDD                                    | Supply voltage for digital circuitry                                                          |

| TP137               | VDDA                                   | Supply voltage for analog circuitry                                                           |

| TP138               | VREF                                   | Reference voltage                                                                             |

| TP139               | MCU_SUP                                | Voltage for specific MCU ports                                                                |

| TP50,<br>TP51, TP52 | HALL_A1, HALL_B1, HALL_C1              | Hall/Encoder signals of first motor                                                           |

| TP53,<br>TP54, TP55 | HALL_A2, HALL_B2, HALL_C2              | Hall/Encoder signals of second motor                                                          |

| TP56                | RES_GEN_M1 Scaled                      | Scaled resolver excitation signal generated by microcontroller for first motor configuration  |

| TP57, TP58          | RES_GENP_M1, RES_GENM_M1               | Resolver excitation signals for first motor configuration                                     |

| TP60, TP61          | M1_SIN, M1_COS                         | Resolver sin/cos signals for first motor configuration                                        |

| TP62                | RES_GEN_M2 Scaled                      | Scaled resolver excitation signal generated by microcontroller for second motor configuration |

| TP63, TP64          | RES_GENP_M2, RES_GENM_M2               | Resolver excitation signals for second motor configuration                                    |

| TP66, TP67          | M2_SIN, M2_COS                         | Resolver sin/cos signals for second motor configuration                                       |

| TP68, TP69          | V_TH_M1, V_TL_M1                       | Upper and lower threshold of phase over-<br>current detection of first motor configuration    |