# MCUXSPTUG\_25.09

## **Secure Provisioning Tool User Guide 25.09**

Rev. 18 — 10 October 2025

User guide

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | MCUXpresso Secure Provisioning Tool                                                                                                                                                                                                                                                                                       |

| Abstract    | MCUXpresso Secure Provisioning Tool (SEC) is a GUI tool made to simplify the generation and provisioning of bootable executables on NXP processors. It is built upon the proven security enablement toolset provided by NXP and takes advantage of the breadth of programming interfaces provided by the BootROM library. |

## 1 Introduction

A Chinese translation of the user guide in the PDF format can be downloaded from the <u>Secure Provisioning Tool</u> <u>home page</u>.

The MCUXpresso Secure Provisioning Tool (SEC) is a graphical user interface (GUI) application designed to streamline the creation and provisioning of bootable executables for NXP processors. Built on NXP's robust security enablement toolset, SEC leverages the extensive programming capabilities of the BootROM to simplify secure image preparation and deployment.

Whether you are new to secure provisioning or an experienced developer, SEC offers a user-friendly interface that enhances productivity. New users benefit from guided workflows for preparing, flashing, and securing images, while experienced users recognize familiar utilities—such as sdphost, blhost, and nxpimage—now integrated into a cohesive and intuitive environment.

For advanced use cases, SEC also supports customization through editable scripts, enabling experienced users to tailor provisioning flows to meet specific security and deployment requirements.

Figure 1. MCUXpresso Secure Provisioning Tool

## 2 Features

Here are the key features of the **Secure Provisioning Tool** (SEC):

#### 2.1 Security Enablement

- Image signing and encryptions: supports generation of signed and encrypted images using customer-provided keys and certificates.

- Secure boot configuration: automates creation of secure boot headers (for example, HAB, TrustZone-M, BEE).

- Key management: integrates with NXP's key provisioning workflows, including SRK, DEK, and OTP key programming.

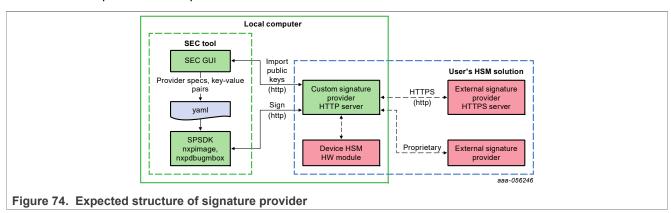

- Optional signature provider: allows customizing integration of the HSM module for signing the image.

- · Trust provisioning: device HSM and EdgeLock 2GO

## 2.2 Device communication and flashing

BootROM interface support: communicates with BootROM via UART, USB, SPI, or I2C.

MCUXSPTUG\_25.09

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

- Flash programming: supports writing to internal flash and external memory (for example, QSPI, FlexSPI NOR/ NAND, eMMC).

- · Device detection and connection management: auto-detects connected devices and manages communication

## 2.3 User experience

- · Guided workflows: workspace wizard with predefined profiles to create a new configuration easily.

- · Visual feedback: real-time status updates, logs, and error reporting.

- · Cross-Platform support: available for Windows, Linux, and macOS.

#### 2.4 Useful extensions

- Debug authentication support

- · SB editor allowing creation of Secure Binary files

- · The Merge Tool allowing merging several images into one

- MCUboot signer allowing signing the custom application via the MCUboot third-party Tool

- · Manufacturing Tool for FAB operations, allowing provisioning several devices in parallel

- · Additional command-line utilities for low-level interaction with the device

## 2.5 Device and platform support

- Broad processor family coverage: Compatible with a wide range of NXP processors (for example, i.MX, LPC, MCX).

- Support for latest silicon features: Regularly updated to support new security features and silicon revisions.

#### 3 Terms and definitions

#### **Table Terms and definitions**

| Term                                                                                                                                                                          | Definition                                                                                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| AAD                                                                                                                                                                           | Additional Authenticated Data; typically used with AES-GCM                                |  |  |

| AES                                                                                                                                                                           | Advanced Encryption Standard                                                              |  |  |

| AES-128                                                                                                                                                                       | Rijndael cipher with block and key sizes of 128 bits                                      |  |  |

| АНАВ                                                                                                                                                                          | Advanced High Assurance Boot                                                              |  |  |

| ATF                                                                                                                                                                           | ARM Trusted Firmware                                                                      |  |  |

| BCA                                                                                                                                                                           | Bootloader Configuration Area                                                             |  |  |

| BEE                                                                                                                                                                           | Bus Encryption Engine                                                                     |  |  |

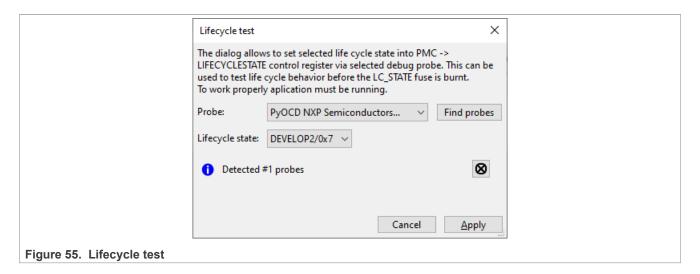

| Block cipher                                                                                                                                                                  | Encryption algorithm that works on blocks of N={64, 128,} bits                            |  |  |

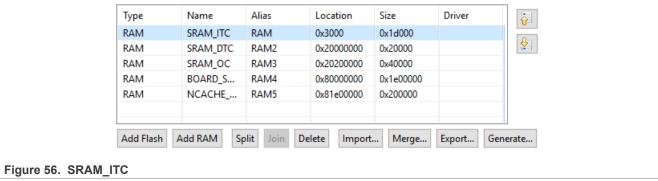

| CA                                                                                                                                                                            | Certificate Authority, the holder of a private key used to certify public keys            |  |  |

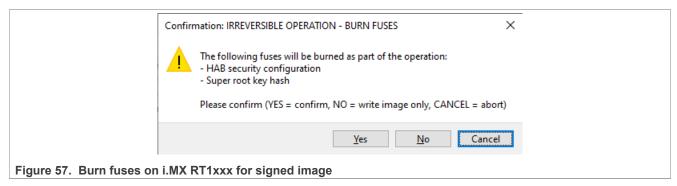

| Cryptographic Acceleration and Assurance Module, a accelerator for encryption, stream cipher, and hashin algorithms, with a random number generator and run integrity checker |                                                                                           |  |  |

| CBC                                                                                                                                                                           | Cipher Block Chaining, a cipher mode that uses the feedback between the ciphertext blocks |  |  |

| Term         | Definition                                                                                                                                                                                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBC-MAC      | A message authentication code computed with a block cipher                                                                                                                                                     |

| CFPA         | Customer In-field Programmable Area                                                                                                                                                                            |

| Cipher block | The minimum amount of data on which a block cipher operates                                                                                                                                                    |

| Ciphertext   | Encrypted data                                                                                                                                                                                                 |

| CMAC         | Cipher-based Message Authentication Code                                                                                                                                                                       |

| СМРА         | Customer Manufacturing/Factory Programmable Area                                                                                                                                                               |

| CMS          | Cryptographic Message Syntax, a general format for data that may have cryptography applied to it, such as digital signatures and digital envelopes. HAB uses the CMS as a container holding PKCS#1 signatures. |

| CSEc         | Cryptographic Services Engine / EdgeLock Accelerator, feature set for various encryption, decryption, and authentication algorithms built to meet the SHE specification.                                       |

| CSF          | Command Sequence File, a binary data structure interpreted by the HAB to guide authentication operations                                                                                                       |

| DA           | Debug Authentication                                                                                                                                                                                           |

| DAP          | Debug Authentication Protocol                                                                                                                                                                                  |

| DCD          | Device Configuration Data, a binary table used by the ROM code to configure the device at an early boot stage                                                                                                  |

| DCP          | Data coprocessor, an accelerator for AES encryption and SHA hashing algorithms                                                                                                                                 |

| DEK          | Data encryption key, a one-time session key used to encrypt the bulk of the boot image                                                                                                                         |

| DUK          | Device Unique Key                                                                                                                                                                                              |

| DUKB         | DUK certificate block                                                                                                                                                                                          |

| ECB          | Electronic Code Book, a cipher mode with no feedback between the ciphertext blocks                                                                                                                             |

| EKIB         | Encrypted Key Info Block                                                                                                                                                                                       |

| ECU          | Electronic Control Unit                                                                                                                                                                                        |

| ELE          | EdgeLock Secure Enclave                                                                                                                                                                                        |

| EPRDB        | Encrypted Protection Region Descriptor Block                                                                                                                                                                   |

| FAC          | Flash Access Controlled                                                                                                                                                                                        |

| FCB          | Flash Configuration Block or Flash Control Block                                                                                                                                                               |

| FCF          | Flash Configuration Field; can also be referenced as FCB                                                                                                                                                       |

| GCM          | Galois/Counter Mode; it is a mode of operation for symmetric key cryptographic block ciphers, most commonly used with AES                                                                                      |

| GUI          | Graphical User Interface                                                                                                                                                                                       |

| НАВ          | High Assurance Boot, a software library executed in internal ROM on the Freescale processor at boot time that, among other things, authenticates software in external memory by                                |

| Term           | Definition                                                                                                                                                              |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | verifying digital signatures in accordance with a CSF. This document is strictly limited to processors running HABv4                                                    |

| Hash           | Digest computation algorithm                                                                                                                                            |

| HSM            | Hardware System Module                                                                                                                                                  |

| IEE            | Inline Encryption Engine                                                                                                                                                |

| IFR            | Information Flash Region                                                                                                                                                |

| IMG            | Image Signing Key, interchangeable term with ISK                                                                                                                        |

| ISK            | Image Signing Key, interchangeable term with IMG                                                                                                                        |

| ISP            | In-system programming, a mode in which the processor can be programmed directly into the product                                                                        |

| IVT            | Image Vector Table                                                                                                                                                      |

| KEK            | Key Encryption Key, used to encrypt a session key or DEK                                                                                                                |

| KeyBlob        | KeyBlob is a data structure that wraps the key and the counter and the range of image decryption using AESCTR (AES in Counter mode) algorithm                           |

| KIB            | Key Info Block with KEY and IV for AES128-CBC, recall key and IV used in PRDB wrap and unwrap is defined as key info block                                              |

| MAC            | Message Authentication Code. Provides integrity and authentication checks                                                                                               |

| Message digest | A unique value computed from the data using a hash algorithm; provides only an integrity check (unless encrypted)                                                       |

| NBU            | Narrowband Unit                                                                                                                                                         |

| NDA            | Non-disclosure Agreement                                                                                                                                                |

| OEI            | Optional Executable Image                                                                                                                                               |

| OEM            | Original Equipment Manufacturer                                                                                                                                         |

| os             | Operating System                                                                                                                                                        |

| OTFAD          | On-The-Fly AES Decryption                                                                                                                                               |

| ОТР            | One-Time Programmable. OTP hardware includes masked ROM, and electrically programmable fuses (eFuses).                                                                  |

| ОТРМК          | One-Time Programmable Master Key                                                                                                                                        |

| PFR            | Protected Flash Region                                                                                                                                                  |

| PKCS#1         | Standard specifying the use of the RSA algorithm. For more information, see <a href="PKCS#1">PKCS#1</a> Wikipedia article and RSA PKCS#1 security archive.              |

| PKI            | Public Key Infrastructure, a hierarchy of public key certificates in which each certificate (except the root certificate) can be verified using the public key above it |

| Plaintext      | Unencrypted data                                                                                                                                                        |

| PRDB           | Protection Region Descriptor Block recalls the counter and the range of image decryption using the AES-CTR algorithm                                                    |

| Term        | Definition                                                                                                                                                                                                                                                                                     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRINCE      | lightweight block cipher designed for low-latency hardware implementations, especially in environments like embedded systems and IoT devices                                                                                                                                                   |

| PUC         | Product Unit Certificates                                                                                                                                                                                                                                                                      |

| PUF         | Physical Unclonable Function                                                                                                                                                                                                                                                                   |

| pyOCD       | Python-based tool and API for debugging, programming, and exploring Arm Cortex microcontrollers; for details, see <a href="mailto:pyOCD official website">pyOCD official website</a>                                                                                                           |

| Rijndael    | Block cipher chosen by the US Government to replace DES; pronounced <i>rain-dahl</i>                                                                                                                                                                                                           |

| ROMCFG      | ROM Bootloader configurations                                                                                                                                                                                                                                                                  |

| RoT         | Root of Trust                                                                                                                                                                                                                                                                                  |

| RSA         | A public key cryptography algorithm developed by Rivest,<br>Shamir, and Adleman; Hardware accelerator (including hash<br>acceleration) is found on some processors                                                                                                                             |

| RSA-PSS     | RSA probabilistic signature scheme                                                                                                                                                                                                                                                             |

| SDP         | Serial Download Protocol, also called UART/USB Serial Download mode. IT allows code provisioning through UART or USB during production and development phases                                                                                                                                  |

| SEC Tool    | Secure Provisioning Tool                                                                                                                                                                                                                                                                       |

| Session key | The encryption key is generated at the time of encryption. Only ever used once                                                                                                                                                                                                                 |

| SHA-1       | Hash algorithm that produces a 160-bit message digest                                                                                                                                                                                                                                          |

| SHE         | Secure Hardware Extension                                                                                                                                                                                                                                                                      |

| SI          | Secure installer                                                                                                                                                                                                                                                                               |

| SNVS        | Secure Non-Volatile Storage                                                                                                                                                                                                                                                                    |

| SPL         | Secondary Program Loader                                                                                                                                                                                                                                                                       |

| SPSDK       | Secure Provisioning SDK, an open source Python library, and command-line tools for secure provisioning of NXP processors                                                                                                                                                                       |

| SRK         | Super Root Key, an RSA key pair that forms the start of the boot-time authentication chain. The hash of the SRK public key is embedded in the processor using OTP hardware. The SRK private key is held by the CA. Unless explicitly noted, SRK in this document refers to the public key only |

| TEE         | Trusted Execution Environment                                                                                                                                                                                                                                                                  |

| UID         | Unique Identifier, a unique value (such as a serial number) assigned to each processor during fabrication                                                                                                                                                                                      |

| υυυ         | Universal Update Utility used to download images to different MPU devices                                                                                                                                                                                                                      |

| V2X         | Vehicle-to-everything is a standalone cryptographic accelerator (EdgeLock Accelerator) on i.MX 95                                                                                                                                                                                              |

| WPC         | Wireless Power Consortium                                                                                                                                                                                                                                                                      |

| Term | Definition                                                                                                                                                     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Execute-In-Place refers to a software image that is executed directly from its non-volatile storage location rather than first being copied to volatile memory |

| XMCD | External Memory Configuration Data                                                                                                                             |

## 4 Installation

This chapter describes the procedure required to install SEC on Windows, macOS, and Linux operating systems. For the supported operating systems, refer to Minimum system requirements.

## 4.1 Minimum system requirements

The tool runs on Microsoft(R) Windows(R), Ubuntu, and macOS operating systems. The detailed system requirements are specified in <u>Secure Provisioning Tool Release Notes</u>. The document also describes what debug probe drivers should be installed. These drivers might also be needed for communication with the processor in ISP mode where the probe provides USB to UART/SPI/I2C converter.

#### 4.2 Windows

To install SEC as a desktop application on a local host, perform the following steps:

- 1. Visit the Secure Provisioning Tool home page to download the SEC installer for Windows.

- 2. Double-click the MCUXpresso Secure Provisioning version. exe installer to begin installation.

- 3. On the first page of the wizard, click Next.

4. On the End-User License Agreement page of the wizard, select I accept the terms of the License Agreement and click Next.

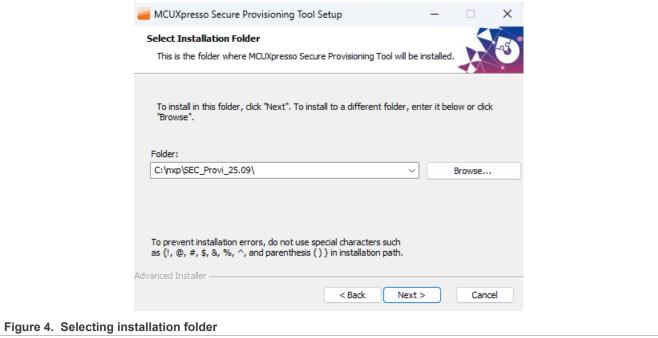

5. On the **Select Installation Folder** page of the wizard, select **Browse** and navigate to a destination folder you want to install the SEC to and click **Next**.

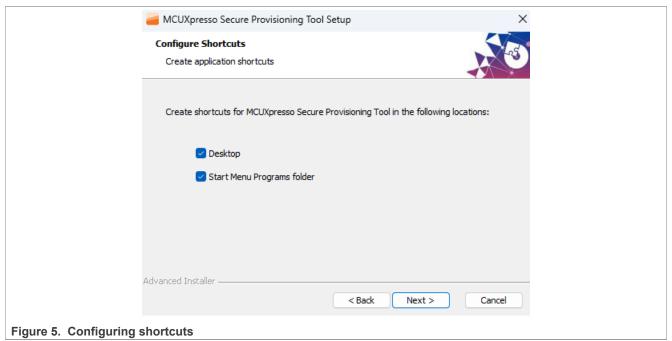

6. On the **Configure Shortcuts** page of the wizard, select the shortcuts you want to be created for SEC and click **Next**.

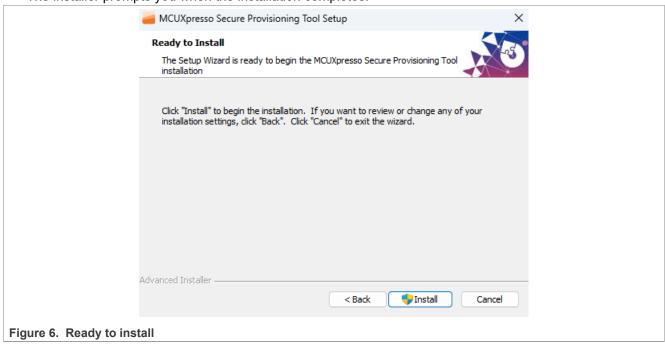

7. On the **Ready to Install** page of the wizard, select **Install**.

The setup begins the installation.

**Note:** If you want to review or change any of your installation settings, click **Back**. Click **Cancel** to exit the wizard.

The installer prompts you when the installation completes.

8. Click Finish to close and exit the setup wizard.

9. To start using SEC, run the tool from the desktop shortcut on the desktop or from the **Start** menu. You can also navigate to the <code>rep.exe</code> or launch the shortcut in the <code>rep.exe</code> or launch the <p

## 4.2.1 Windows CLI

It is possible to install the SEC Tool using the command line. In this case, use **Run the installer** with the following parameters: start /wait

MCUXpresso\_Secure\_Provisioning\_YY.MM.exe /exenoui /qn

## 4.3 MacOS

To install SEC as a desktop application on a local host, perform the following steps:

- 1. Visit the NXP website to download the SEC installer for macOS. Based on your computer, select either an installer for an Intel or Apple M processor.

- 2. Double-click the MCUXpresso\_Secure\_Provisioning\_YY.MM.pkg to start the Install MCUXpresso Secure Provisioning Tool wizard.

**Note:** When you try to open the macOS installer, you may receive an error. To avoid it, manually select the option **Mac App Store and identified developers** in the **Security & Privacy** menu.

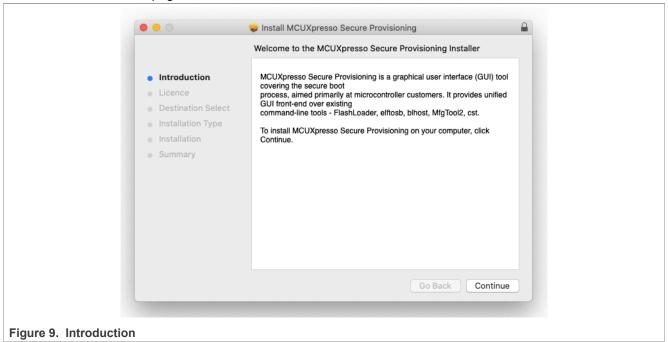

1. On the Introduction page, click Continue.

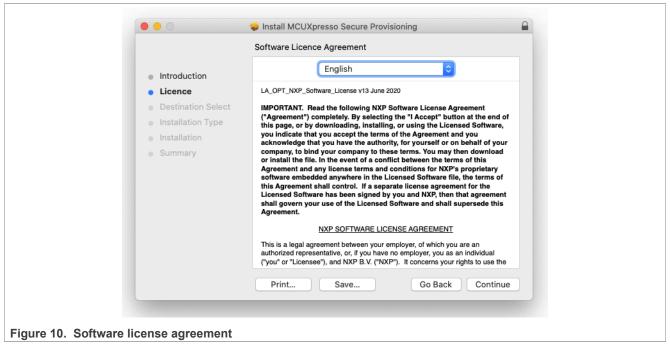

2. On the Software License Agreement page, click Continue.

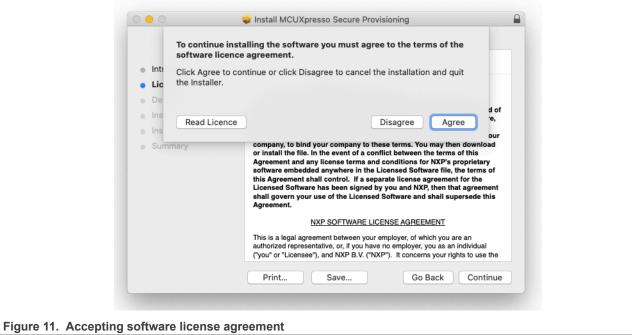

3. Confirm that you have read and agreed to the terms of the Software License Agreement by clicking Agree.

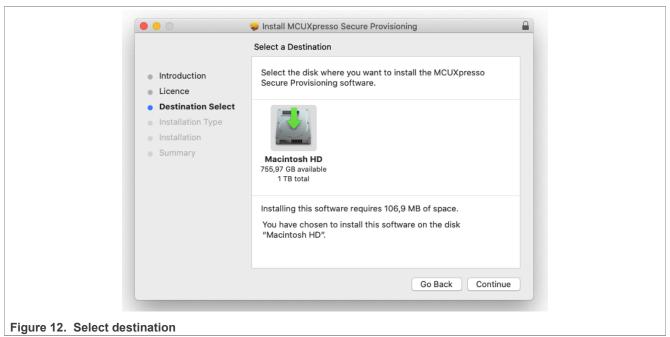

4. On the **Destination Select** page, click the green arrow to select the installation folder, and once done, click **Continue**.

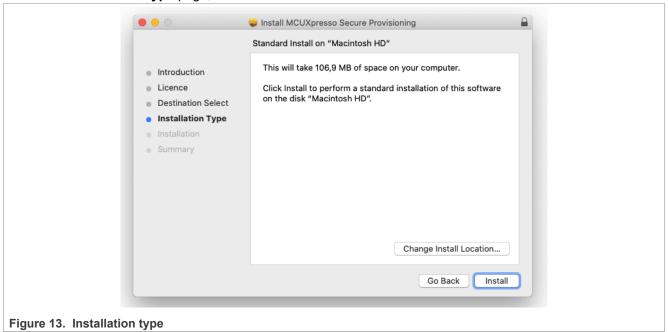

5. On the Installation Type page, click Install.

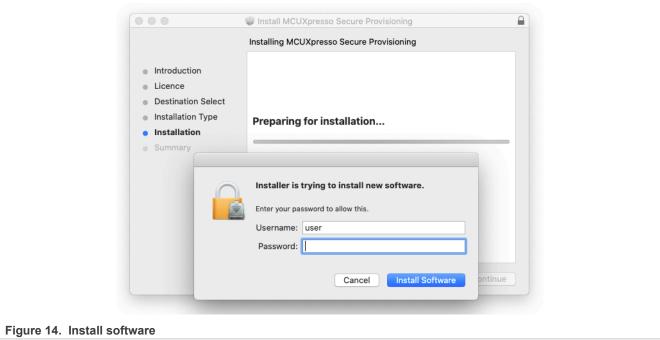

6. Type in your login credentials to continue with the installation and click **Install Software**.

#### 7. Click Continue.

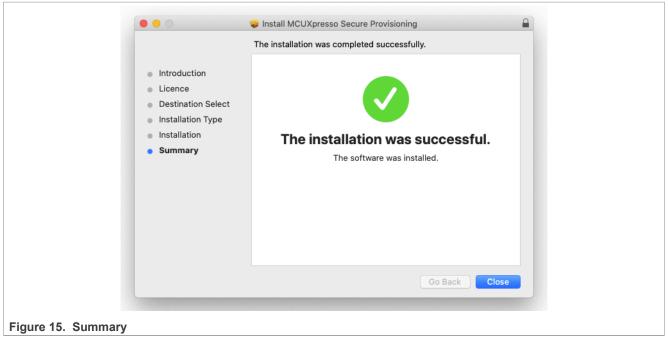

Unless errors are reported, the Summary page confirms that the installation was completed successfully.

8. On the **Summary** page, click **Close**.

## 4.3.1 Enabling USB connection on macOS

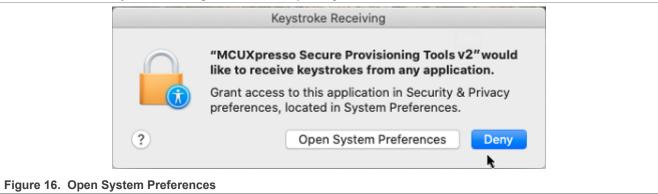

During the first connection to the target by USB, macOS X Catalina blocks the access to USB HID devices as a security measure and the operation will fail with error. In macOS 13 (Ventura), this works differently and these steps are not needed.

Perform the following steps to enable USB connection:

1. In the OS security alert message box, select Open System Preferences.

- 2. Unlock **Privacy** preferences to enable changes.

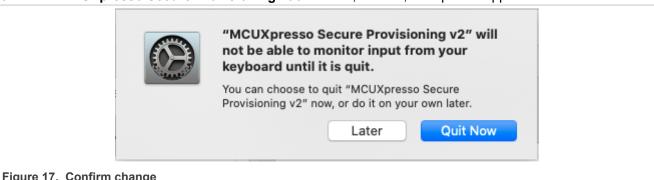

- Select MCUXpresso Secure Provisioning Tool YY.MM, confirm, and quit the application.

Figure 17. Confirm change

- 4. Lock **Privacy** preferences.

- 5. If the application was not closed, close it manually.

- 6. Start the application and proceed with the operation.

#### 4.4 Linux

Installation of SEC on Ubuntu can be done in the Terminal.

- 1. Visit the NXP website to download the SEC installer for Linux.

- 2. Open the terminal and change the directory where the installer is downloaded, install using dpkg with sudo.

```

$ cd ~/Downloads

$ sudo dpkg -i mcuxpresso-secure-provisioning-<version> <architecture> <os-

version>.deb

```

If the command executed with sudo is successful, the setup installs the SEC Tool in the dedicated folder / opt/nxp/.

**Note:** SEC depends on other packages that have to be installed in advance:

```

$ sudo apt install libhidapi-dev libsdl2-2.0-0

```

## 4.5 Uninstalling

#### 4.5.1 Windows

The Secure Provisioning Tool can be uninstalled in the following ways:

• by using Settings | Apps & features

• by navigating into the %APPDATA%\NXP Semiconductors and then finding the appropriate MSI installer in the Secure Provisioning Tool YY.MM\install\ folder and choosing the Remove option in the wizard.

#### 4.5.2 MacOS

Secure Provisioning Tool can be uninstalled by using Finder, navigating to Applications, and moving SEC Provi ##.## into the Trash.

#### 4.5.3 Linux

The Secure Provisioning Tool can be uninstalled by using the Debian package manager.

In the Terminal you can get the list of secure provisioning tools with the package names:

| +++-====                                |       |       |            |  |  |  |

|-----------------------------------------|-------|-------|------------|--|--|--|

| ======================================= |       |       |            |  |  |  |

| ii mcuxpresso-secure-provisioning-25.09 | 25.09 | amd64 | MCUXpresso |  |  |  |

| Secure Provisioning Tool                |       |       |            |  |  |  |

| ii mcuxpresso-secure-provisioning-v3.1  | 3.1   | amd64 | MCUXpresso |  |  |  |

| Secure Provisioning                     |       |       |            |  |  |  |

| ii mcuxpresso-secure-provisioning-v4    | 4.0   | amd64 | MCUXpresso |  |  |  |

| Secure Provisioning                     |       |       |            |  |  |  |

Now, the desired version can be uninstalled:

```

$ sudo dpkg --remove mcuxpresso-secure-provisioning-25.09

```

## 4.5.4 Remove configuration files

The user preferences are stored in the folder <user home>\.nxp\secure\_provisioning\_<version> \ and are not removed by uninstalling the product. These folders can be removed manually. For more details about preferences, see <a href="Preferences">Preferences</a>.

#### 4.5.5 Remove restricted data

The restricted data are installed in the folder <user home>\.nxp\secure\_provisioning\_restricted\_data\ and are not removed by uninstalling the product. These folders can be removed manually.

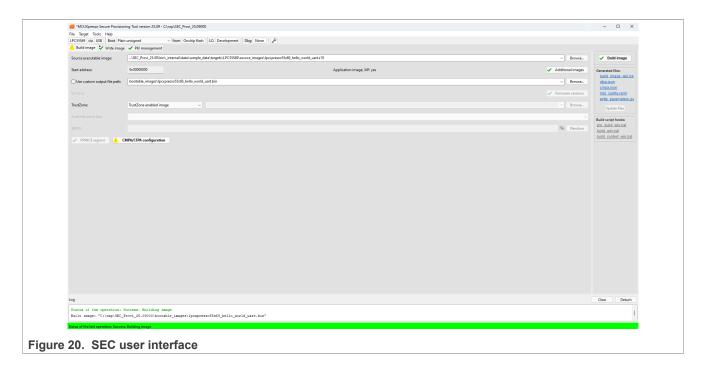

#### 5 User interface

SEC offers a simple and user-friendly interface. It consists of the **menu bar**, **toolbar**, and main views accessible through tabs:

- Build image allows building a bootable image.

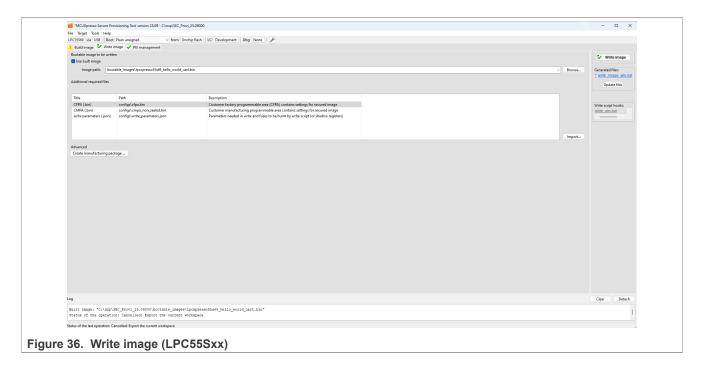

- Write image allows writing a bootable image into the processor and optionally securing it.

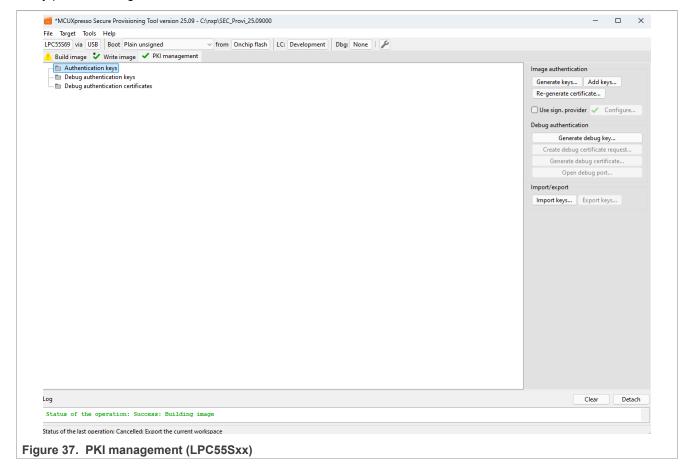

- PKI management allows generating authentication keys or configuring the Signature Provider.

- The bottom part of the interface is occupied by the Log window and status line.

Configuration controls that are not supported for the selected processor might not be displayed. If a control is supported for the processor but is not meaningful in the current setting, it is disabled (gray). The tool highlights controls with configuration problems in red (errors) or yellow/orange (warnings). The problem is described in the tooltip. The tool displays information messages in blue.

## 5.1 Menu and settings

This chapter gives detailed information about menu options and settings of the tool.

### 5.1.1 Title of the main window

The main window title shows:

- Asterisk (\*), if the configuration is not saved on the disk (it is "dirty")

- Name of the tool

- · Path to the current workspace

#### 5.1.2 Menu bar

The **menu bar** (main menu) contains several drop-down menus offering various application, configuration, and file-related functions.

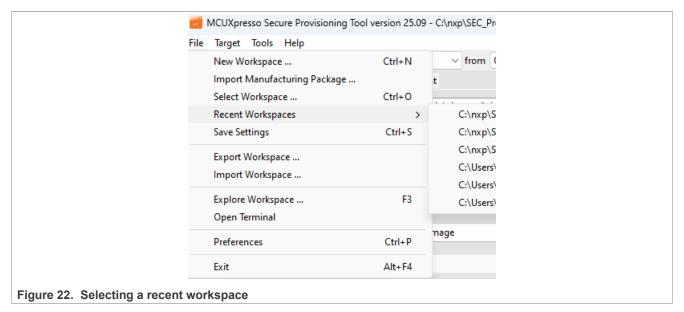

File: General workspace and configuration-related operations

- **New Workspace** ...: Creates a workspace. You are prompted to specify its location and choose from the supported processors. In the case the location already contains a workspace, the workspace is opened and not created. For more information, see <a href="Workspaces">Workspaces</a>.

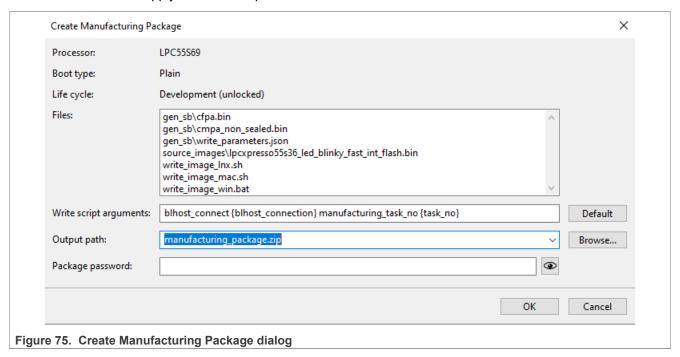

- Import Manufacturing Package ... : Imports a manufacturing package (\*.zip) with all data necessary for manufacturing and creates a "manufacturing workspace" (see <a href="Workspace">Workspace</a>. for details about manufacturing workspace).

- **Select Workspace** ... : Switches to another workspace. You are prompted to specify which workspace to open. For more information, see <u>Workspaces</u>.

- **Recent Workspaces**: Displays a list of recently used workspaces. For more information, see <u>Workspaces</u>. The number of displayed workspaces can be customized in <u>Preferences</u>.

- Save Settings : Saves the current workspace settings.

- Export Workspace ... : Exports the current workspace as package (\*.zip) with options to filter out unnecessary files such as generated scripts. For more information, see <a href="Sharing and copying workspaces">Sharing and copying workspaces</a>.

- Import Workspace ... : Imports workspace package (\*.zip) into a specified folder.

- Explore Workspace : Opens the file explorer in the current workspace.

- **Open Terminal**: Opens the terminal in the current workspace directory with a path configured for SPSDK applications.

- Preferences: Opens the Preferences dialog. For more information, see Preferences.

- Exit: Exits SEC.

**Target**: This menu duplicates the operations available from the toolbar, see <u>Toolbar</u> for a detailed description.

Tools: List of additional tools

- Manufacturing Tool: Opens the Manufacturing Tool. For more information, see Manufacturing Tool.

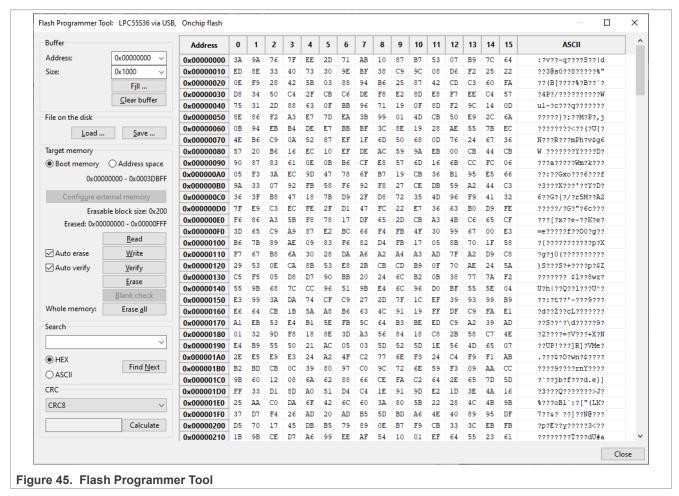

- **Flash Programmer**: Opens the tool for flash programming and modifications. For more information, see Flash Programmer.

- SB editor: Allows creating a custom Secure Binary file for secure updates. For details, see SB editor.

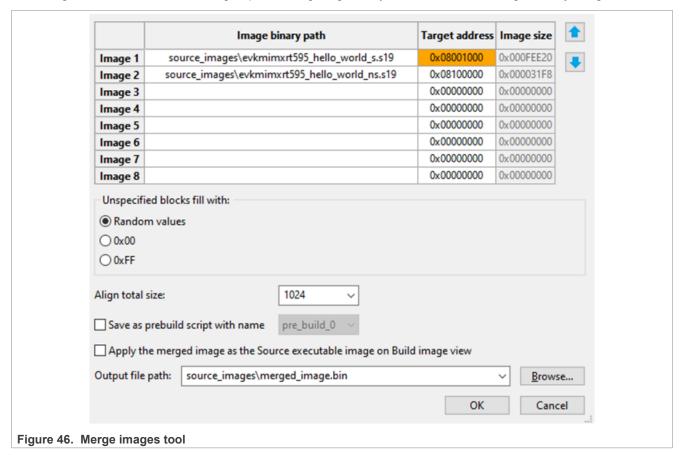

- Merge Tool : Allows merging up to 8 images into one single binary image. For more information, see Merge Tool.

- MCUboot Sign Image...: Allows signing the application image with the key for the MCUboot secondary bootloader.

- MCUboot Export Key...: Exports the public key from the given private key as a C source file for the MCUboot secondary bootloader.

Help: User help and additional general information

Commands opening the local documentation:

- · User Guide: Opens the User Guide PDF.

- Release Notes: Opens the Release Notes markdown file.

- · Quick Start Guide: Opens the Quick Start Guide PDF.

Commands opening the online documentation:

- **Online Documentation**: Opens the online SEC Tool documentation (quick start guide, user guide, and release notes).

- Community: Opens an NXP webpage with the blog, where you can find discussions about issues related to this tool

- **SPSDK Documentation**: Displays a web page with documentation for the NXP Secure Provisioning SDK command-line tools.

Additional commands:

- Check for Updates: Checks whether there is a new version of the tool available.

- About: Displays information about the current version.

#### 5.1.3 Preferences

User preferences are stored in the folder <code><user home>\.nxp\secure\_provisioning\_<version>\</code> and are shared for all workspaces. The preferences are backward-compatible, so for example SEC Tool v9 can load preferences from SEC Tool v8 if preferences for v9 do not exist yet. If no preferences are available, the SEC Tool starts with default values.

User preferences contain information about recently used files and workspaces, window sizes, locations, positions of the splitters, and options configurable in the Preferences dialog:

**Timeout for communication re-established after reset** (flashloader to be initialized) [sec]: Represents a delay (in seconds) after which the ROM bootloader or flashloader will be ready after reset of the processor. The

real value may be affected by the configuration of your host. The selected value may affect the generated write script.

**Maximal number of recent workspaces displayed in the File menu**: Customize the maximal number of recent workspaces displayed in **File > Recent Workspaces**. Supported range 1 - 25. Default value: 9

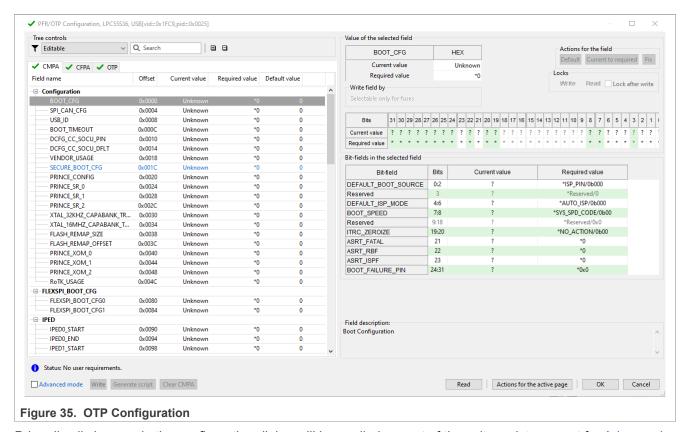

**Read current values after the OTP/PFR configuration is opened**: Choose how the reading of device values on opening the **OTP Configuration** is handled.

The following options are available:

- · Never : Do not read the values automatically

- · Ask : Confirm the reading manually

- . Always: Automatically read device values

**Preferred language for the tool**: Select the language in which the tool will be displayed. Supported languages are English and Chinese.

The following options are available:

- **Default**: The language is selected based on the language selected in the operating system. If the system language is different from the supported languages, English is used.

- EN: Set the tool to English

- · ZH: Set the tool to Chinese

Save tool settings: Specifies when the tool settings must be saved to the disk.

It is possible to select one of the following options:

- Automatically: It is the default value. The settings are saved if needed

- On request only: The tool always asks whether to save the settings or not

**Sound on error during configuration**: If a new error is displayed in the configuration dialog, the tool notifies the user with a sound signal. The sound signal is OS-specific.

**Password/key visibility at startup**: Specifies whether the passwords and keys are shown or hidden at the SEC Tool startup. In the UI, the visibility can be controlled by the button, so this option configures just the initial value.

**Check for the new version of the tool**: Specifies how frequently the tool checks the availability of the new version during the start-up.

It is possible to select one of the following options:

- Never : Never check; the feature is disabled

- Daily: The check is executed once per day

- Weekly: The check is executed once per week

- Monthly: The check is executed once per month

**Help NXP improve the tool by sending diagnostic data**: If enabled, this feature allows the collection of diagnostic data to generate statistical insights into how the tool is used. This helps us enhance functionality and prioritize improvements. If disabled, no data is collected or transmitted.

#### **Statistical Data Collection Notice**

To support continuous improvement of our software, we collect diagnostic usage data that include:

· Frequency of tool and user interface feature usage

- Operating system details (type, version)

- · Device configuration

- Target device, boot type, boot device type, TrustZone status (enabled/disabled), connection type (USB, UART, and so on)

- Trust provisioning method (Device HSM, EL2GO), Debug Authentication (enabled/disabled), Signature Provider (enabled/disabled), Debug Probe type

Although the types of data collected are clearly listed above, we explicitly confirm that the following are not collected:

- · Personally identifiable information (PII), such as names, email addresses, or contact details

- User-generated content, including project files, source code, or any data stored on the user's device

- · Location data or behavioral tracking is outside the scope of the tool usage

- Sensitive project information (for example, fuses, cryptographic keys, file paths or file names)

All collected data is non-personal, not shared with third parties, and is used solely to improve user experience and guide feature development.

**Restricted data ...**: The data can be downloaded from the <u>Secure Provisioning Tool home page</u>, however, access to this package is contingent upon the execution of a Non-Disclosure Agreement (NDA). Among other, the data contains trust provisioning firmware. The data are installed from a ZIP archive. SEC first verifies whether the selected data are compatible with the current tool and if yes, the data are copied into the subfolder in the user home directory. To start using the data, restart SEC.

**Use restricted data from directory**: Allows controlling whether the restricted data are used. The checkbox is enabled only if restricted data are installed.

#### 5.1.4 Workspaces

All files generated by the tool are stored in a dedicated folder structure called a workspace.

A workspace is a practical concept for operating with multiple boards, devices, or executables signed with different sets of keys. It is recommended to create a workspace for every project.

A workspace is always created for a specific device family (series of processors). Once created, it can only be used to modify the configuration of devices belonging to that family.

There are two types of workspaces:

- Development workspace is used during regular tool operation.

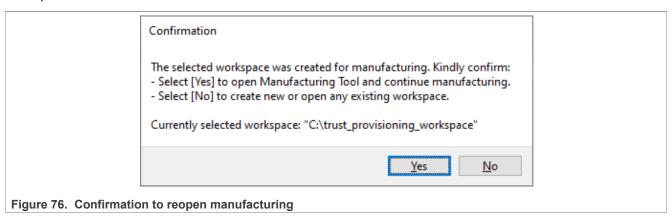

- Manufacturing workspace is used during manufacturing. See section Manufacturing workflow for details.

To create a workspace, select File > New Workspace..., File > Import Manufacturing Package... or File > Import Workspace... from the menu bar. See New workspace creation for details.

To switch to a different workspace, select **File > Select Workspace** ... from the **menu bar** and choose the path from the **Open Workspace** dialog. Another way to open the existing workspace is to double-click the appropriate settings.sptjson file in file explorer. It opens the tool with the given workspace.

To switch to a recently used workspace, select **File > Recent Workspaces** from the **menu bar** and choose from the list.

Every created workspace contains multiple subfolders. Some of them are specific to device families. For the new workspace, most of the subfolders are empty; the files are generated or added by the user later.

- backups/: Backup of old keys/crts after importing or generating new ones

- bootable\_images/: Intermediate and final bootable images (nxpimage output). The no padding binary starts at the address IVT, while the regular binary includes everything from the beginning of the boot device.

- configs/: Generated configuration files, for example, OTFAD/IEE config file (YAML), BEE user keys config file (YAML), and the corresponding generated (BIN) files.

- crts/, keys/: Generated certificates and their corresponding keys.

- dcd files/: DCD files included in the build image step.

- debug\_auth/: Debug authentication files generated by the tool, configuration file for certificate generation (YAML), certificate request (ZIP), certificate (DC and ZIP), and authentication script.

- e12go/: Files for EdgeLock 2GO trust provisioning

- gen\_bee\_encrypt/: BEE user key files created during the build image step for XIP encrypted boot types. The keys are used to burn SW GP2/GP4 fuses during the image write step.

- gen\_hab\_certs/: Output super root key table and hash (nxpcrypto output). The table is programmed along with the bootable image. The hash is programmed in platform fuses.

- gen\_hab\_encrypt/: DEK key files generated by the nxpimage utility. The DEK key file is used during write the image to generate the key blob for the encrypted HAB boot type.

- gen scripts/: Temporary scripts for tool operation.

- hooks/: Hook scripts allow customizing build, write, or the manufacturing process. Hooks with prefix "pre" are executed before the script is executed. Hooks with "context" in the name are executed at the beginning of the script after the environment variables are defined. They can be used for environment variables redefinition. General hook files are called multiple times during the script execution. For details, see <a href="Build image">Build image</a>, Write image, Manufacturing Tool.

- logs/: Log files; log.txt contains content/history of the Log view. The folder also contains logs from SPSDK command-line applications and from the manufacturing.

- root folder: Contains the following:

- Last configuration of the tool in file settings.sptjson.

- Build and write scripts.

- Build and write JSON files containing all parameters used to generate the build and write scripts.

- source\_images/: Primarily intended as a folder to store input images provided by users. Also used by the tool to store input images, if input format conversion is needed.

- trust\_provisioning/: Trust provisioning files (supported only if the processor supports trust provisioning)

- trustzone\_files/: TrustZone-M configuration files (YAML, JSON, or BIN) used by nxpimage during bootable image generation step (nxpimage input).

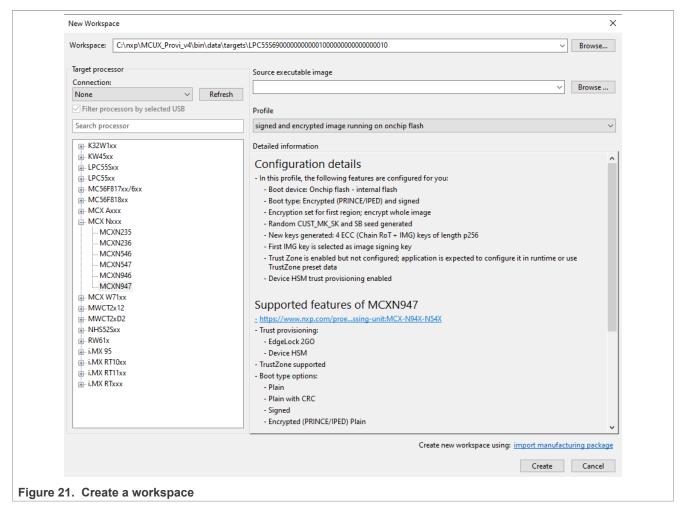

### 5.1.4.1 New workspace creation

To create a workspace, select **main menu > File > New Workspace**. The following options can be selected in the **New Workspace** dialog:

- Workspace path: The folder where the workspace is created; use an empty or non-existing folder.

- **Connection**: Connection that should be used in the new workspace for communication with the processor. If no connection is selected, a new workspace is created with the default connection for the processor.

- Refresh button: Update the list of detected connections.

- Filter processors by selected USB: When checked and the USB connection is selected, the device tree is filtered by the device family identified by USB VID/PID

- **Search processor**: Filter processors from the processors tree. A substring of the processor, series, or board name can be used.

- **Processor tree**: Displays processors matching the filter above. The processors are organized in folders by high-level processor category and series.

- **Source executable image**: Chooses the input executable application image file. For more information about the input image format, see Source image formats.

- MCUboot bootloader image: Chooses the input MCUboot bootloader image. For more information about MCUboot, see MCUboot workflow.

- **Profile**: Pre-defined settings that will be applied to the new workspace. It is recommended to start development with the default profile and verify the plain image works. For secure profiles, the Quick Fix will be applied to the configuration so there are no errors by default. To create a custom profile, see <u>Profile</u> creation.

- **Detailed information**: The configuration details section displays the information about pre-configuration of the workspace based on the profile selection. The "Supported features" section lists the processor features that are supported by the tool.

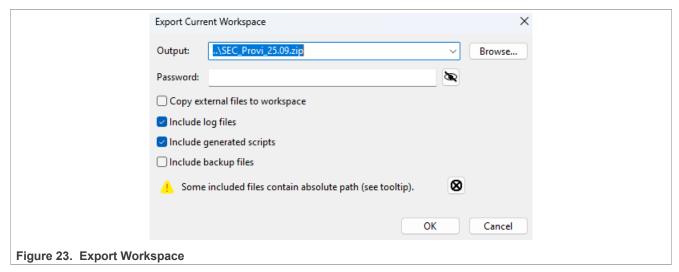

## 5.1.4.2 Sharing and copying workspaces

It is recommended to store all used files in the workspace. The <code>settings.sptjson</code> file contains all paths relative to the workspace root folder, so if you open settings on another computer, you can still regenerate all scripts. The workspace can be a part of another project. Paths to the parent folder are stored as relative, but paths to other folders are absolute. It is recommended to use the **Export Workspace** dialog for sharing workspace.

In case the script must be executed on another computer without regeneration, it uses environment variables to specify the SEC installation directory and workspace. These environment variables can be specified externally, or if not specified, the default value is used. Workspace is detected automatically and an environment variable must be specified only if the script is copied outside the workspace.

The workspace can be exported using the **Export Workspace** dialog, select **File > Export Workspace** ... from the **Menu bar**. The dialog box displays options for exporting the current workspace into a ZIP file with optional AES encryption.

The Export Workspace dialog allows selecting the following options:

- Output: Path to the output ZIP file to be created. Any existing file will be overwritten.

- Password : Optional password for a ZIP file encryption. Leave empty for no encryption.

- Copy external files to workspace: Select this option to copy all external files (files located outside the workspace directory) into the exported workspace. A list of all external files is shown in the tooltip. All files will be saved in the source\_images folder. Filename conflicts are automatically resolved to ensure that no file is overwritten. The current workspace and settings are not affected. The operation affects the ZIP archive only. The option is not available if any file does not exist.

- Include log files: Select this option to include all log files in the exported workspace.

- **Include generated scripts**: Select this option to include all generated scripts. The scripts contain an environment variable to specify the workspace the SEC installation directory, which is an absolute path. Regeneration of the scripts may still be needed.

- Include backup files: Includes files from the "backup" sub-folder.

A warning message is shown when there are some absolute paths detected in the included files. A list of these files is presented as a tooltip.

#### 5.1.4.3 Import workspace from the ZIP

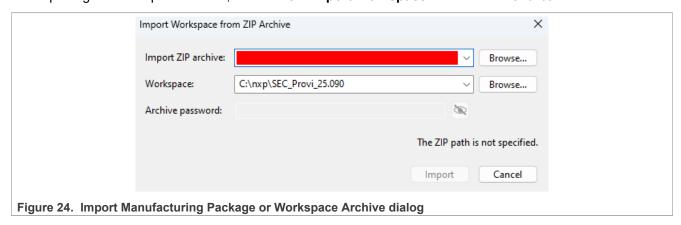

For importing the manufacturing package, select **File > Import Manufacturing Package** ... from the **menu bar**. For importing the workspace archive, select **File > Import Workspace** ... from the **menu bar**.

• Import ZIP archive : The path to the ZIP workspace archive.

- **Workspace**: The folder where the imported workspace is created; it is recommended to use an empty or non-existing folder.

- Archive password: A ZIP password for encrypted archives. This field is enabled only when encryption is

detected.

The dialog allows importing both workspace from the ZIP archive and manufacturing package. In both cases, the workspace is imported into a new directory (or empty directory). For the workspace import, the tool supports imports from older versions, but for the manufacturing package, the tool and the manufacturing package version must be the same. If the ZIP file is encrypted, write the correct password. For more information about the manufacturing process, see <u>Manufacturing operations</u>.

#### 5.1.4.4 Profile creation

A profile for New Workspace wizard can be created from any workspace using settings.sptjson. The profile is a subset of the workspace setting that is relevant for the profile. Profiles must be placed in the <install\_folder>/bin/\_internal/sample\_data/targets/configuration\_profiles folder to be offered as an option for the profile selection in the New Workspace dialog. To create a valid profile, manually specify these JSON fields:

- is\_profile : a flag identifying a profile setting, it must be set to true

- profile\_name : the name of the profile; this name is displayed in the tool and must be processor-unique

- **profile\_description\_introduction**: the profile description in the natural language. It is displayed before the formatted profile description. This field is optional.

- **profile\_description**: should contain information what is set by the profile. It must be specified as a list of information.

Fields that should be removed from the profile settings:

- write\_image\_settings, keys\_management\_settings, and connection have no meaning for the new workspace.

- From build\_image\_settings, remove all fields that contain secrets that should not be distributed (such as dek\_key, keyblob\_key\_id\_int, sbkek, sb\_seed) or fields that are irrelevant for the new workspace (source\_image\_path, dcd\_path, ele\_firmware\_path, xmcd\_path, tz\_path, script\_updated, updated)

The description of all fields can be found in the JSON schema **settings\_schema\_##\_##.json** distributed within the tool installation files.

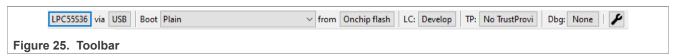

#### 5.1.5 Toolbar

The **toolbar** offers a quick selection of basic settings. The same commands are also available in **main menu > Target**.

- **Processor**: Shows the chosen processor. Click the button to switch the processor. You can switch to a processor from the same device family for which the current settings are compatible. To select a processor from a different family, create a new workspace.

- **Connection (via)**: Choose the connection to the target. This release supports UART, USB-HID, SPI, and I2C connectivity. Click the button to customize connection details. For more information, see <u>Connection</u>.

- **Boot mode**: Choose the type of boot. The list depends on the device capabilities of the currently selected processor.

- **Boot memory (from)**: Click the button to open the boot memory configuration. For more information, see Boot memory configuration.

- **Life cycle**: Allows the selection of the processor life cycle. Click the button to select from processor-specific life cycles; the selection dialog displays a short description for each option.

- **Trust provisioning type**: Allows the selection of the trust provisioning type and enabling it for the trust provisioning operation. For details, refer to <u>Trust provisioning</u>.

- **Debug probe**: Allows the selection of the debug probe connected to the computer; see <u>Debug Probe Selection dialog</u>.

- Quick fix: Resolve problems that are displayed on the build tab. Not all problems can be fixed by the "quick fix" solver as not all problems have a single deterministic solution. Before the solver does any changes, the user is prompt to save settings. Once the quick fix is complete, a list of actions that were applied to fix the problems is displayed; the actions are also displayed in the log. It is recommended to review all changes carefully to ensure that the solution meets the expectations.

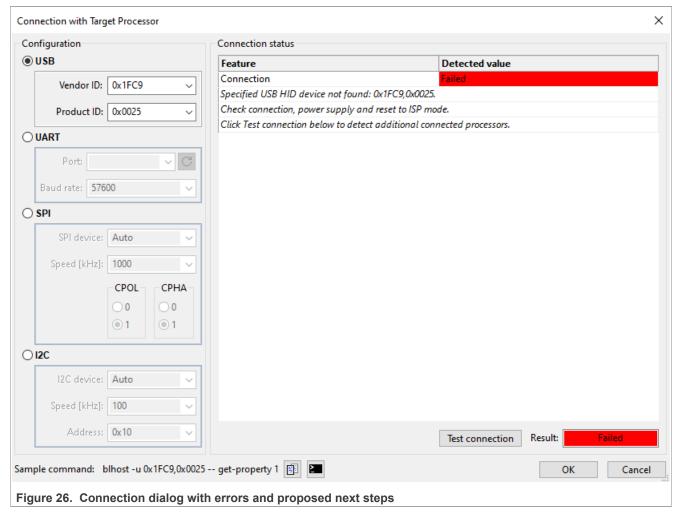

#### 5.1.6 Connection

The Connection dialog allows you to select the connection with the target processor and test it.

The dialog is accessible from Target > Connection from the menu bar or the toolbar.

It contains the following options (if supported for the processor):

• USB: Specify USB connectivity to the specified Vendor ID/Product ID pair.

- **UART**: Specify UART connectivity through the specified port and baud rate. The baud rate is automatically detected by the bootloader when processing the initial ping. This means that the target processor must be reset after a new baud rate has been selected.

- **SPI/I2C**: It is possible to connect with the processor using an SPI or I2C connection using the LIBUSB interface available on:

- MCU-Link Pro

- <u>LPC-Link2</u>. LPC-Link2 is present on several EVK boards, however, to connect via SPI you must use jumper wires to connect with the processor.

Before starting the Secure Provisioning Tool, it is necessary to download and install USB drivers from the product pages listed above. It is possible to configure the following connection parameters:

- **SPI/I2C device**: The device is specified using a USB Path. The default value in the connection dialog is "Auto", which means if there is just one device connected to the computer, it is selected automatically. The details about the USB Path format can be found in the SPSDK documentation.

- Speed [kHz]: Communication clock frequency in kHz.

- CPOL, CPHA: Signal polarity and phase; see SPI specification for details.

- · Address : Address of the I2C device.

**Crystal frequency [kHz]**: Frequency of the external crystal. It is used to configure communication speed with the processor. Currently it is used only for <code>lpcprog</code>.

Use the **Test connection** function to verify that the device can be properly accessed with the given configuration. To ensure successful detection of the processor with **Test connection**, make sure of the following:

- The board is correctly powered up

- The board is properly configured to ISP (In-System Programming) mode

- · The board is connected to the computer

The connection dialog detects the following parameters:

- Connection: Status of the selection of a communication device (USB or serial port) or a USB path for the SPI/I2C connection

- Mode: Communication mode bootloader or flashloader application.

- **Processor**: *Match* if the connected processor matches the selected one, *No match* otherwise. This feature allows finding a mistake when the SEC Tool is communicating with a wrong board. This function is not 100% reliable as there is not enough information to identify each processor.

- Life cycle: Life cycle that was detected in the connected processor.

- **Silicon version**: Displayed only if the connected processor is of an older version. When the old revision is detected, the connection test results in a Failed state. All known issues related to this version are mentioned in the tooltip.

The following connection results are possible:

- Not tested yet: Use the Test connection button to run tests.

- OK: Connection successfully established.

- **FAILED**: Connection tests failed. For details, see **Connection status**. For more information about the failure, it is possible to use SEC in verbose mode and find details in the console view.

At the bottom of the connection dialog, there is the "Sample blhost/sdphost/lpcprog/nxpuuu command" that allows running the corresponding SPSDK command-line tools with specified arguments. The first button copies the command with arguments into the clipboard. The second button opens a terminal where the command can be executed.

## 5.1.7 Boot memory configuration

The Boot Memory Configuration dialog allows selecting and configuring a boot device. The dialog contains the following configuration parts:

- Boot memory type: This part allows selection of the boot memory type, and optionally, instance.

- Predefined template: This part allows selection of the boot memory configuration template. The list is

specific for each memory type and contains memories where some are available on NXP evaluation boards.

After opening the boot memory configuration dialog, the option contains the previously selected memory

(if values were not changed), or is empty, the first item in the drop-down menu is a memory used on the

evaluation board (if applicable). Memory configuration templates that are marked as verified were tested on

hardware.

- **User configuration**: This part allows loading or saving the configuration to the selected file. It might be useful for reuse of the configuration for another project or sharing the configuration with colleagues.

- **Protected area**: This part allows specifying the memory area that must not be changed by the SEC Tool. If the tool tries to erase or modify the selected memory area, a confirmation dialog is displayed. It might be useful for protection of the custom data in a boot memory. Specify comments/reasons, because it will be displayed as part of the confirmation message.

- Boot memory configuration parameters : Configuration of the memory, these parameters are specific for each memory type.

- Comment: The description of the boot memory that contains information if the predefined template was applied

- **Test the configuration**: This button is used to test the current memory configuration with the connected processor/board. The test consists of two steps: read test (whether the memory can be read) and bootloader test that verifies the memory configuration using the blhost list-memory command.

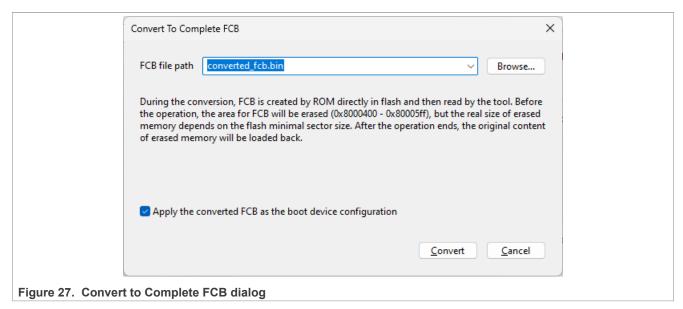

- Convert to Complete FCB: This option is available for SPI NOR only. The button allows converting a simplified SPI NOR configuration into a full "Flash Control Block" (see <u>SPI NOR</u>)

### 5.1.7.1 SPI NOR

SPI NOR flash can be configured in two ways:

- by using the flashloader/ROM based simplified configuration (two 32-bit words)

- by using the complete Flash Control Block (FCB binary, 512 bytes)

For a simplified configuration, the user can modify the values suggested in the dialog box. To create your own FCB from SEC Tool, use the **Convert to complete FCB** button in the bottom-right corner. It opens the **Convert To Complete FCB** dialog box that allows to convert existing simplified configuration into complete configuration using the connected processor. A simplified device configuration is written to an SPI NOR flash device and read back while the original data are preserved. When the conversion process is complete, it creates a .bin file in the desired location, given by the path to the FCB file.

The **Convert To Complete FCB** dialog offers a checkbox to use the created FCB binary file as a SPI NOR/**user FCB file**. If unchecked, only the conversion is done.

FCB can also be created in MCUXpresso IDE by adding the FCB component into Peripheral Drivers in Peripherals tools, where the full configuration can be specified.

When the complete FCB is specified in the boot device configuration, the user can specify two separate FCB files. The FCB for runtime is used for flash configuration during the processor boot. The FCB for write is used for flash configuration for programming the application.

## 5.1.7.2 On-chip RAM

The SEC Tool allows creating images executed in internal RAM, which might be useful for chip (re-)configuration or executing a diagnostic test. For this boot memory, the write script writes the application into the processor and intermediately launches it. If the chip is secured, the application is written and launched via the SB file.

Note: The SB file could also be used for recovery flash.

#### 5.1.7.3 Serial downloader

The serial boot provides a means to download a boot image to the chip and execute the image. In this boot mode, a host PC/device can communicate to the ROM bootloader, using the serial downloader protocol. The SEC Tool allows execution of the image in internal or external RAM. It might be useful to distribute the application to flashless devices.

The write script contains both provisioning of secure assets to the processor and loading and execution of the application in RAM. During manufacturing, the application is not loaded.

#### 5.1.8 Trust provisioning

The **Trust provisioning** dialog allows selecting a processor-specific trust provisioning type and enabling it for the trust provisioning operation.

The SEC Tool supports the following trust provisioning types:

- **Device HSM** the secrets are encrypted using a key stored in a processor. It is the same for all processors in the series.

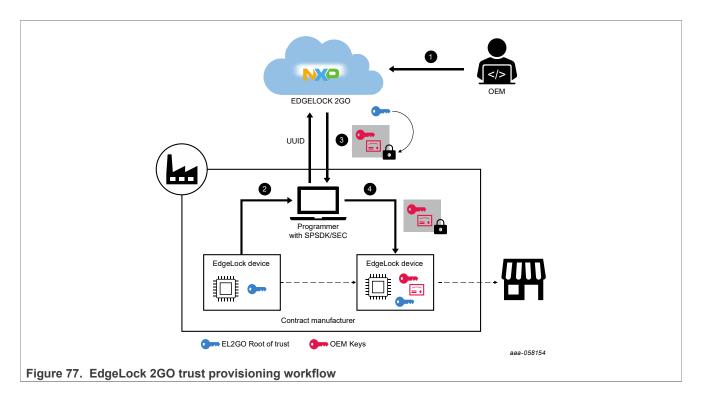

- EdgeLock 2GO the secrets are stored in the NXP cloud, on the EdgeLock 2GO server.

### 5.1.8.1 Device HSM provisioning

There are two types of device HSM provisioning:

- The device HSM is directly supported in ROM. In this case, there is no need for extra firmware.

- There is extra firmware needed for the following use cases:

- i.MX RT5xx/6xx where the device HSM is optional. For details on how to enable it, see <u>Device HSM</u> <u>provisioning</u>. This firmware is distributed in a restricted data package (see <u>main menu > File > Preferences</u> to install it).

- RW61x processors where the device HSM is mandatory for secure boot types are partially supported in ROM. This firmware is distributed in tool data.

To successfully build an image with Device HSM enabled, the processor must be connected and selected in the Connection dialog. It is not required only when there is already an image built with Device HSM and the settings are the same.

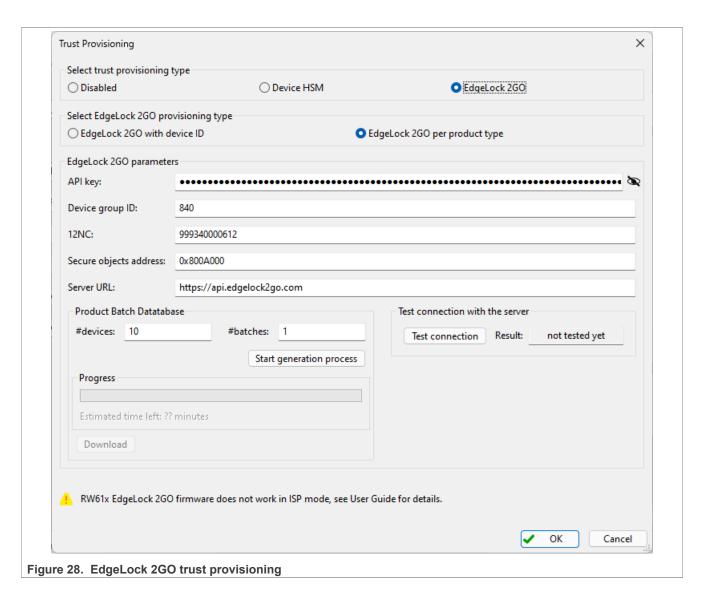

## 5.1.8.2 EdgeLock 2GO trust provisioning

The EdgeLock 2GO parameters allow configuration of the access to the assets on the EdgeLock 2GO server.

There are two EdgeLock 2GO flows supported:

- EdgeLock 2GO with device ID: the secure objects are retrieved from the EdgeLock 2GO cloud server during the provisioning process

- EdgeLock 2GO per product type: the secure objects are retrieved from a server in a batch database and provisioning can be executed without connection to the cloud server (offline)

Other configuration controls:

- API key user-specific HEX key granting access to the server. For details, see <u>API key to access EdgeLock</u> <u>2GO server</u>.

- **Device group ID** the identification number of the device group on the EdgeLock 2GO server that contains all the secure assets. On the EdgeLock 2GO server, it can be found under **Devices > MCU & MPU**.

- 12NC hardware product unique identification. On the EdgeLock 2GO server, this can be found within the information about the device group.

- Secure objects address address in the flash memory where the secure objects are stored during provisioning.

- Server URL URL of the EdgeLock 2GO REST API server. Use an empty string to apply the default value.

- The **Test** button allows verifying a connection to the server.

- Product Batch Database panel allows to generate and download a database of secure objects from the EdgeLock 2GO server and use it for offline per product provisioning flow. For details, see <u>Create database</u> with secure objects for <u>EdgeLock 2GO per product type</u>.

- #devices number of processors to be included in the batch database

- #batches number of batch databases to be generated

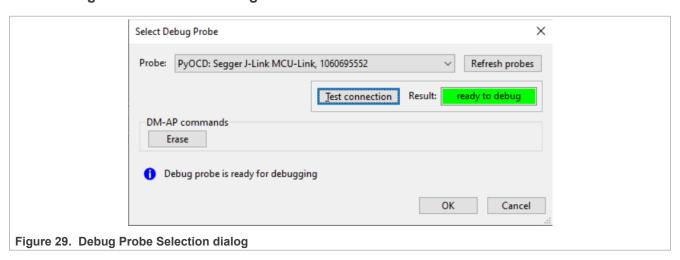

## 5.1.9 Debug Probe Selection dialog

The Debug Probe Selection dialog allows to:

- Select a probe for shadow registers (only for processors where the shadow registers for fuses are initialized via a debug probe)

- Use a test connection with the given probe

- Erase the processor flash (if supported in the processor via the debug probe API)

When the dialog is opened, the probes connected to the computer are detected. It is possible to rescan the probes anytime later again using the **Refresh probes** button.

Once the probe is selected, the selection is stored in the workspace settings including the hardware ID (serial number). If a different board is connected, update the selection. During opening the dialog, if the selected probe is not found, the tool updates the hardware ID automatically.

The **Test connection** button provides information on whether the debug can be started for the selected debug probe. The possible results are:

- ready to debug if the debug probe and the processor are ready for debugging

- **no debug** if the connection with the debug probe was established, but the processor cannot be debugged; in this case ensure that the debugger is properly connected and the processor is running (not ISP mode)

- FAILED if the connection with the debug probe failed

The **Erase** button allows erasing the internal flash (mass erase). See the reference manual for processor-specific details.

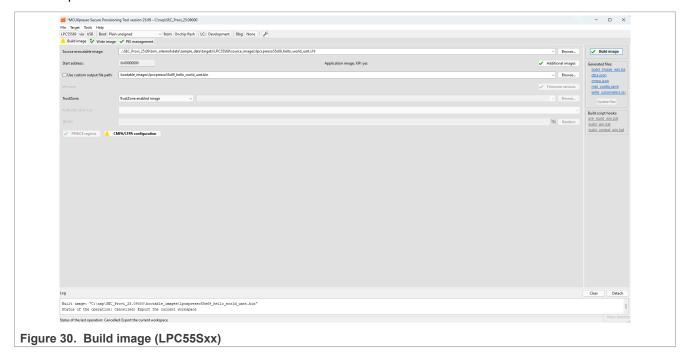

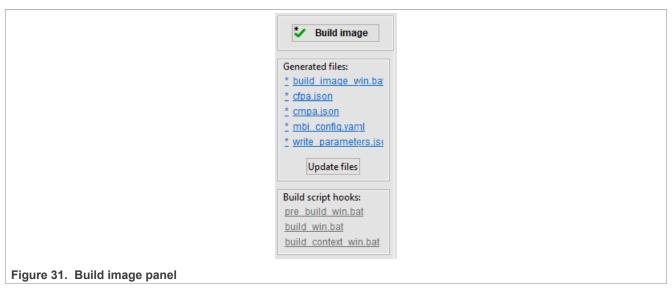

## 5.2 Build image

In the **Build image** view, you can transform an application image into a bootable format compatible with the selected processor.

#### 5.2.1 Controls on the build image view:

**Source executable image**: Chooses the input executable file. For more information about the input image format, see <a href="Source image formats">Source image formats</a>.

**Start address**: The base address of the image. It is editable only to a binary image. For ELF and S-Record and HEX files, it is detected automatically.

**Application/Bootable image and XIP**: The label provides the following information about the selected source image:

- 1. whether it is an application or a bootable image.

- 2. whether the selected source image is built as "eXecuted In Place", and will be executed from the boot memory, where it is stored. If not, the image must be copied to RAM before the execution. The information is derived from the starting address of the image and compared with the memory address of the selected processor, so the result might not be correct if the selected image does not match the selected processor.

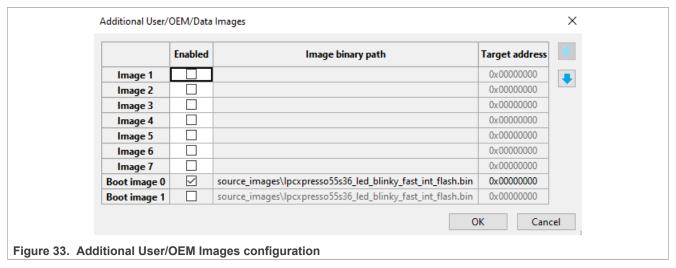

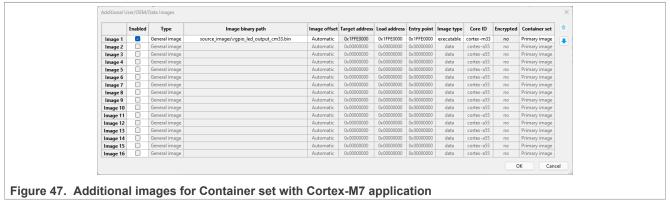

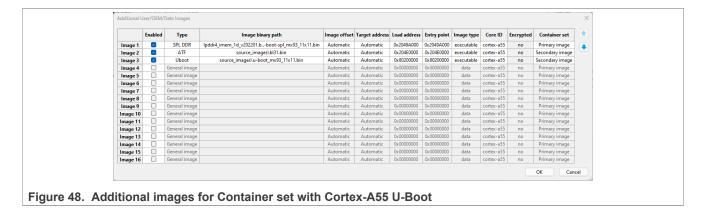

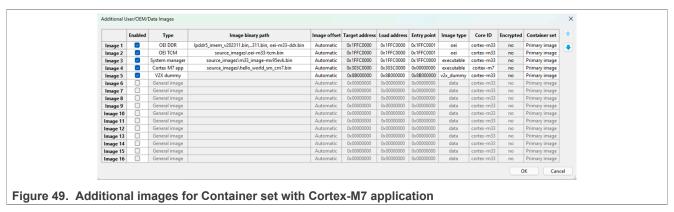

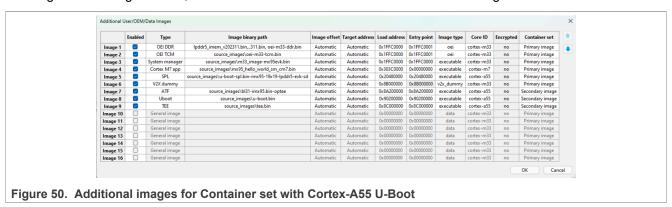

Additional images: Opens the configuration dialog for the Additional User/OEM Image, see Additional images.

**Use custom output file path**: Name of the generated bootable image file and its location. If not specified, the tool names the image based on the input. The file extension is specific for a processor and a boot type, it is either BIN for bootable images or SB for secure-binary capsules.

**Image version**: Version of the bootable image. It is used for dual image boot. The image with the higher image version is booted first.

**Dual image boot**: Opens the configuration window for dual image ping-pong boot. Image can be written to the base (image0) and/or to the remapped (image1) space of the flash, each of the them has its own image version. The ROM then uses the image version to select the latest image to boot. If the latest image boot fails, the old image is used to boot again.

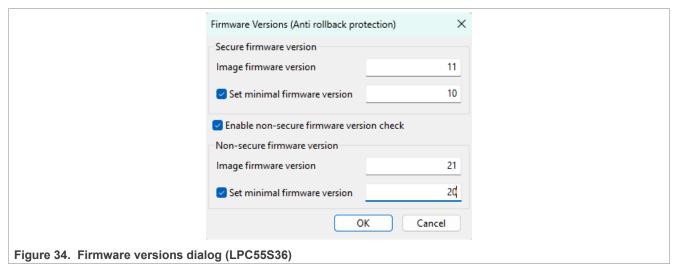

**Firmware versions**: Opens the configuration dialog of Firmware versions (Secure and Non-secure). The firmware version allows setting the anti-rollback protection. For details, see <u>Firmware versions</u>.

**XMCD**: Allows enabling the External Memory Configuration Data feature. XMCD is needed for comprehensive or feature-rich applications requiring large capacity of RAM (on-chip RAM is not enough). Either a YAML or BIN configuration file can be provided or XMCD simplified configuration can be prepared in <u>XMCD configuration</u> dialog. (for details, see the description of the **-xmcd-cfg** CLI parameter).

**DCD (Binary)**: Selection of what Device Configuration Data must be included in the bootable image. The option **From source image** can be used only if the source image contains DCD. The DCD enables early configuration of the platform including SDRAM. MCUXpresso Config Tools can generate a DCD in a compatible format. If the target processor does not support DCD files, the checkbox is disabled. For more information, see <a href="Creating/Customizing DCD files">Creating/Customizing DCD files</a>.

**TrustZone**: Allows you to enable TrustZone features. The following selection is possible:

- TrustZone disabled image Disables TrustZone. This option might not be supported for some processors.

- TrustZone enabled image Enables TrustZone with the default configuration preset in the processor.

- TrustZone enabled image with preset data Enables TrustZone with custom TrustZone-M data. JSON and BIN file formats are supported. JSON data can be generated in and exported from the TEE Tool of MCUXpresso Config Tools. BIN file is created by the nxpimage utility. For more information, see <a href="TrustZone configuration file">TrustZone configuration file</a>.

**Authentication key**: Signs the image with the specified key. The key can also be used for the authentication of the SB file. This option is only applicable to authenticated and encrypted boot modes and offers a selection of keys generated in the **PKI management** view.

Key id: The keyblob encryption key identifier is used in the encrypted (AHAB) boot type

**AHAB/HAB encryption algorithm**: Selection of AHAB/HAB encryption algorithm used in the encrypted (HAB), authenticated, or encrypted (AHAB) boot types.

**Key source**: A key source for signing the image.

**User key**: For the OTP key, the source master key is used to derive other keys. For the PUF KeyStore, the user key is used to sign the image. Only available for Plain signed boot types.

**SBKEK**, **SB3KDK**, **or CUST\_MK\_SK**: A key is used as a key-encryption key to handle an SB file. Only available for secured boot types. For RT5xx/6xx, it is only enabled when the key source is KeyStore. For LPC55Sxx devices, the key store is initialized only once in the device life cycle and after that, any change in SBKEK will cause failure to load the SB file into the processor. For more information, see <u>PFR and PUF KeyStore</u>. OEM seeks a hex key used to randomize the creation of the SB file with the CUST MK SK key.

Configuration dialogs: The following configuration dialogs are available on the Build image view:

- XIP encryption (BEE user keys): Opens the configuration dialog of XIP encryption user keys. Option enabled only for XIP encrypted (BEE user keys) authenticated and XIP encrypted (BEE user keys) unsigned boot types.

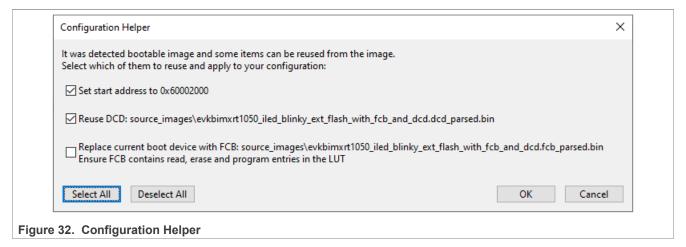

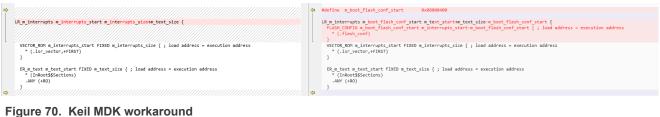

- XIP encryption (BEE OTPMK): Opens the configuration window of BEE with the OTP Master Key. The option is enabled only for XIP encrypted (BEE OTPMK) authenticated boot type.