# Freescale Semiconductor, Inc.

## 7.2.4.3 Last Cell Processing Tim

This read-only register contains the cell to This value may be used to find the most is updated in a cyclical fashion.

|   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | :  |

|---|----|----|----|----|----|----|----|----|

|   |    |    |    |    |    |    |    | L( |

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9  |    |

| Ī |    |    |    |    |    |    |    | L  |

Figure 7-6. Last Cell Proces

### 7.2.4.4 ATMC CFB Revision Regis

This read-only register contains the ATM

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | ;   |

|----|----|----|----|----|----|----|-----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  |     |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  |     |

| 0  | 0  | 0  | 0  |    |    | ΑN | 1R\ |

Figure 7-7. ATMC CFB

- ATMC CFB Major Revision (AM: Revision Number.

- ATMC CFB Sub-Revision (ASR\ Revision Number.

The following values of AMRV and ASR'

Table 7-2. Values of

| AMRV   | ASRV   |

|--------|--------|

| 000000 | 000000 |

| 000001 | 000000 |

| 000001 | 000001 |

# Addendum MC92501 ATM Cell Prod

This technical update provides additional changes su (MC92501GCA, Revision A) and clarifies some previous pages that are attached to this addendum (pages 4-2 replacement pages that may be removed and placed in the control of the co

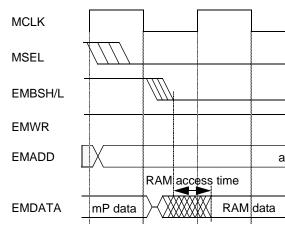

- Page 4-29, Figure 4-29: The MSEL signal has

to indicate a one-wait state access, and a note

indicating the wait state requirement.

- Page 7-11, Table 7-2: Revision A was added

- Page 9-12, Table 9-4: The following changes

- I<sub>IN</sub> Input leakage values:

- with pullup resistor—minimum change

- with pulldown resistor—maximum ch

- I<sub>OH</sub>/I<sub>OL</sub> minimum values for EACEN, EI

EMBSLx were changed from 24 mA to 2

- Input Capacitance was changed from 8 p

- Page G-1: Old reference 15 was deleted.

This document contains information on a new product under development be discontinue this product without notice.

© Motorola, Inc., 1999. All rights reserved.

## Freescale Semiconductor, Inc.

**Figure 4-42** shows a maintenance read/c Memory extends for three MCLK phases MCLK cycles, which is the minimum len Interface. Thus, the clear does not extend

Figure 4-42. External Memo

NOTE: When performing a read/c one wait state is required for duration of an MCLK phas

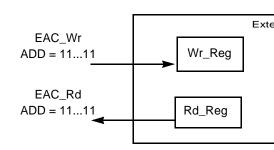

# 4.4.4 External Address Cor

Normal (non-maintenance) accesses to the have the same timing as normal External asserted instead of the EM bank select significant with all 1s when accessing the EAC Devidenate the same timing as External Memory signal is asserted instead of the EM bank driven on EMADD, so 24 bits (16 MB) of space are available to the microprocessor of the EAC circuitry. Note that the MC92 read register. The microprocessor is free to control and/or program the address control.

Figure 4-43. Example Implemen

Mfax is a trademark of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any regarding the suitability of its products for any particular purpose, nor does Mr or circuit, and specifically disclaims any and all liability, including without limit vary in different applications. All operating parameters, including "Typicals experts. Motorola does not convey any license under its patent rights nor the for use as components in systems intended for surgical implant into the bo application in which the failure of the Motorola product could create a situati Motorola products for any such unintended or unauthorized application, Buye affiliates, and distributors harmless against all claims, costs, damages, and any claim of personal injury or death associated with such unintended or regarding the design or manufacture of the part.

Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc.

#### **Motorola Literature Distribution Centers:**

**USA/EUROPE:** Motorola Literature Distribution; P.O. Box 5405; Denver, Col World Wide Web Address: http://ldc.nmd.com/

JAPAN: Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi-G ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd Silicon Harbour Centre 2

Mfax™: RMFAX0@email.sps.mot.com; TOUCHTONE 1-602-244-6609; US World Wide Web Address: http://sps.motorola.com/mfax

INTERNET: http://motorola.com/sps

Technical Information: Motorola Inc. SPS Customer Support Center 1-800

Document Comments: FAX (512) 895-2638, Attn: RISC Applications Engin

World Wide Web Addresses: http://www.motorola.com/PowerPC

http://www.motorola.com/netcomm

http://www.motorola.com/Coldfire

- 1. ANSI Recommendation I.361, "B-l

- 2. ITU-T Recommendation I.610, "Band Functions", November, 1995

- 3. ATM Forum, "ATM User-Networl September, 1994

- 4. ATM Forum, "BISDN Inter Carrie September, 1994

- 5. ATM Forum, "BISDN Inter Carrie Letter Ballot, November, 1995

- 6. ATM Forum, "Traffic Managemen

- 7. ANSI T1S1.5/93-004R2, "Broadba" Principles and Functions", Januar

- 8. Bellcore TA-NWT-01110, "Broadba requirements", Issue 1, August, 19

- 9. Bellcore GR-1113-CORE, "Asynchi Adaptation Layer (AAL) Protocols

- 10. Bellcore GR-1248-CORE, "Generic Elements", Issue 1, August, 1994

- 11. Motorola, "MC68360 Quad Integra Manual", 1993

- 12. "UTOPIA, An ATM-PHY Interface 1994.

- 13. "UTOPIA Level 2 Specification, Ve

- 14. Bellcore TA-TSV-001408, "Generic Service", Issue 1, August, 1993

- 15. P. Bardell, W. McAnney, and J. Sav Techniques, John Wiley & Sons, 198

#### 9.3.3 **DC Electrical Characterist**

Table 9-4. DC Electrica

| Cymbol           | Doromotor                                                                                              |                          |

|------------------|--------------------------------------------------------------------------------------------------------|--------------------------|

| Symbol           | Parameter                                                                                              |                          |

| $V_{IH}$         | TTL Inputs (5V Tolerant)                                                                               |                          |

| $V_{IL}$         | TTL Inputs (5V Tolerant)                                                                               |                          |

| I <sub>IN</sub>  | Input Leakage Current,<br>No Pull Resistor                                                             | V <sub>IN</sub>          |

|                  | With Pullup Resistor *                                                                                 |                          |

|                  | With Pulldown Resistor *                                                                               |                          |

| I <sub>OH</sub>  | Output High Current, LVTTL Output Type Outputs: EACEN, EMWR, EMADDx, EMBSHx, EMBSLx                    | V <sub>O</sub> H         |

|                  | Output High Current,<br>LVTTL Output Type<br>Outputs:<br>All other outputs                             |                          |

| I <sub>OL</sub>  | Output Low Current, LVTTL Output Type Outputs: EACEN, EMWR, EMADDX, EMBSHx, EMBSLx Output Low Current, | Vo                       |

|                  | LVTTL Output Type Outputs: All other outputs                                                           |                          |

| I <sub>OZ</sub>  | Output Leakage Current,<br>Tri-State Output                                                            | Outpo<br>V <sub>OU</sub> |

| I <sub>DDQ</sub> | Max Quiescent Supply<br>Current                                                                        | V <sub>IN</sub>          |

| I <sub>DD</sub>  | Max Dynamic Supply<br>Current                                                                          | ACI<br>MO                |

| C <sub>I</sub>   | Input Capacitance (TTL)                                                                                |                          |

Notes: 1. Under Typical Loca, 25 Mhz ACLK/MCLK

- **2.**  $T_A = -40^{\circ}\text{C}$  to 85°C,  $V_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}$  Guarant

- 3. Inputs may be modified to include pullup re-

- 4. See Section 9.2 Signal Description for pin i