## MC13783

Power Management and Audio Circuit User's Guide

Document Number: MC13783UG

Rev. 3.8

06/2010

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006–2010. All rights reserved.

## **Contents**

## **About This Book**

|                                                                                | Audience Organization Revision History Suggested Reading Definitions, Acronyms, and Abbreviations References.                                                                                                                                                                                                | ix x                                                                                   |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                                                | oter 1<br>duction                                                                                                                                                                                                                                                                                            |                                                                                        |

| 1.1<br>1.2                                                                     | Features                                                                                                                                                                                                                                                                                                     |                                                                                        |

|                                                                                | oter 2<br>eral Description                                                                                                                                                                                                                                                                                   |                                                                                        |

|                                                                                | Detailed Block Diagram  Main Functions Audio Switchers and Regulators Battery Management Logic Miscellaneous Functions.  Typical Application  Maximum Ratings and Operating Input Voltage Absolute Maximum Ratings Power Dissipation Current Consumption Operational Input Voltage Range I/O Characteristics | . 2-2<br>. 2-3<br>. 2-3<br>. 2-3<br>. 2-4<br>. 2-4<br>. 2-6<br>. 2-6<br>. 2-7<br>. 2-8 |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.4 | SPI Interface Register Set  Dual SPI Resource Sharing General Description Supply Arbitration Audio Resource Sharing ADC Resource Sharing and Arbitration Peripheral Resource Sharing. Semaphore Bits Interrupt Handling                                                                                      | . 3-2<br>. 3-2<br>. 3-3<br>. 3-4<br>. 3-5<br>. 3-5                                     |

MC13783 User's Guide, Rev. 3.8

| 3.4.1 | Control                           | 3-7 |

|-------|-----------------------------------|-----|

| 3.4.2 | Bit Summary                       |     |

| 3.5   | Interface Requirements            |     |

| 3.5.1 | SPI Interface Description         |     |

| 3.5.2 | SPI Requirements                  |     |

| 3.6   | Test Modes                        |     |

| 3.6.1 | Identification                    |     |

| 3.6.2 | Test Mode Registers               |     |

|       | pter 4                            |     |

| Cloc  | k Generation and Real Time Clock  |     |

| 4.1   | Clock Generation                  | 4-1 |

| 4.1.1 | Clocking Scheme                   |     |

| 4.1.2 | Oscillator Specifications         |     |

| 4.1.3 | Oscillator Application Guidelines |     |

| 4.2   | Real Time Clock                   |     |

| 4.2.1 | Time and Day Counters             | 4-3 |

| 4.2.2 | Time of Day Alarm                 |     |

| 4.2.3 | Timer Reset                       |     |

| 4.3   | RTC Control Register Summary      | 4-5 |

| Char  | ntou E                            |     |

|       | pter 5<br>er Control System       |     |

| 5.1   | Interface                         | 5-1 |

| 5.2   | Operating Modes.                  |     |

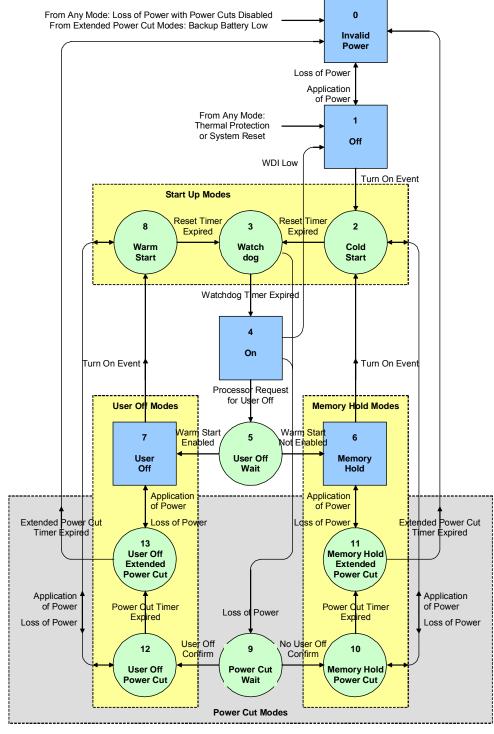

| 5.2.1 | Power Control State Machine       |     |

| 5.2.2 | Battery Powered Modes             |     |

| 5.2.3 | Power Cut Modes                   |     |

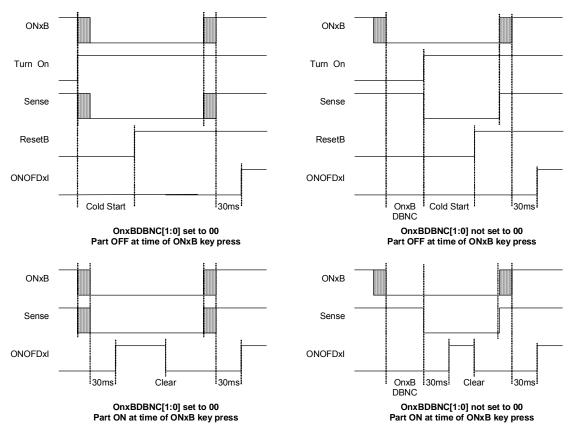

| 5.2.4 | Turn On Events.                   |     |

| 5.2.5 | Turn Off Events                   |     |

| 5.2.6 | Power Monitoring                  |     |

| 5.2.7 | Timers                            |     |

| 5.3   | Power Up                          |     |

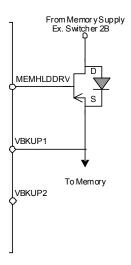

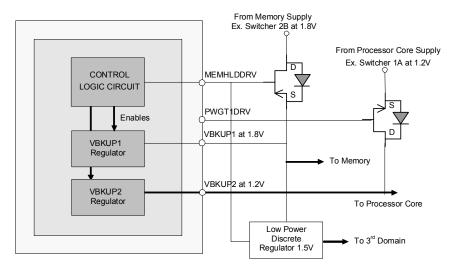

| 5.4   | Memory Hold                       |     |

| 5.4.1 | Memory Hold Operation.            |     |

| 5.4.2 | Backup Regulators                 |     |

| 5.4.3 | Chip Select                       |     |

| 5.4.4 | Embedded Memory.                  |     |

| 5.5   | Power Saving Modes                |     |

| 5.5.1 | Regulators and Boost Switcher     |     |

| 5.5.2 | Buck Switchers                    |     |

| 5.5.3 | Power Ready                       |     |

| 5.6   | Power Control Register Summary    |     |

iv Freescale Semiconductor

## Chapter 6 Supplies

| 6.1           | Supply Flow                        | . 6-1 |

|---------------|------------------------------------|-------|

| 6.2           | Switch Mode Supplies               | . 6-1 |

| 6.2.1         | Common Circuitry                   | . 6-2 |

| 6.2.2         | Buck Switchers Control             | . 6-3 |

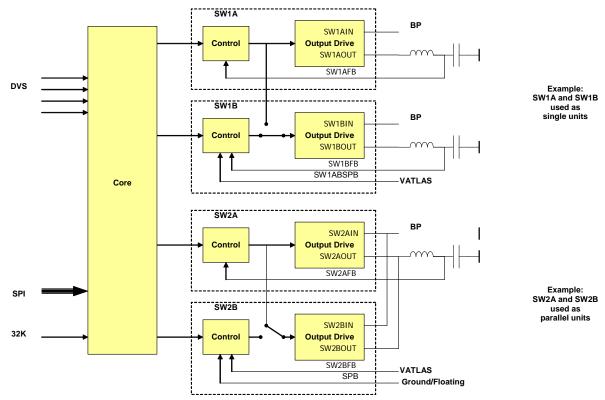

| 6.2.3         | Buck Switchers                     | . 6-3 |

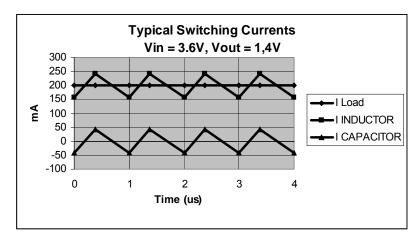

| 6.2.4         | Buck Switchers Equations           | . 6-4 |

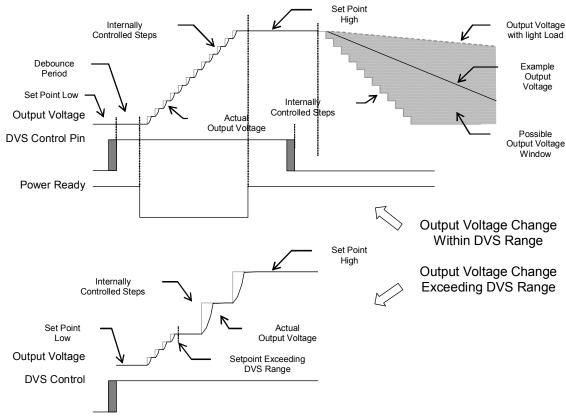

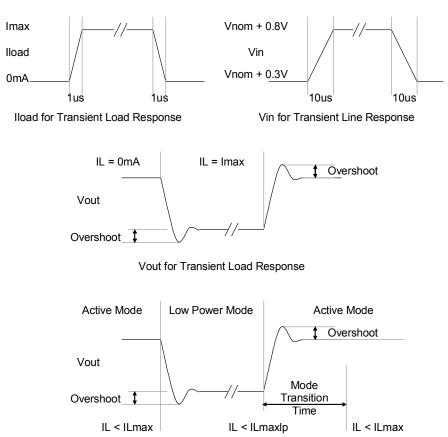

| 6.2.5         | Dynamic Voltage Scaling            | . 6-6 |

| 6.2.6         | Boost Switcher                     | . 6-8 |

| 6.3           | Linear Regulators                  | 6-11  |

| 6.3.1         | Regulators General Characteristics | 6-12  |

| 6.3.2         | Transceiver                        | 6-13  |

| 6.3.3         | Digital                            |       |

| 6.3.4         | Interface                          |       |

| 6.3.5         | Camera                             | 6-24  |

| 6.3.6         | SIM                                |       |

| 6.3.7         | MMC                                | 6-29  |

| 6.3.8         | Vibrator Motor Driver              | 6-31  |

| 6.4           | Supply Control                     | 6-33  |

| 6.4.1         | Power Gating                       |       |

| 6.4.2         | General Purpose Outputs            | 6-35  |

| 6.4.3         | External Enables                   |       |

| 6.4.4         | SPI Register Summary               | 6-36  |

| <b>O</b> la a | -17                                |       |

| Cnap<br>Audi  | pter 7                             |       |

| Auui          |                                    |       |

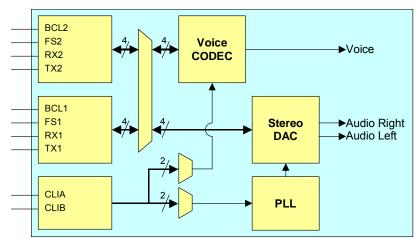

| 7.1           | Dual Digital Audio Bus             | . 7-1 |

| 7.1.1         | Interface                          |       |

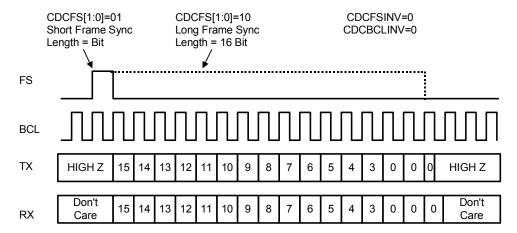

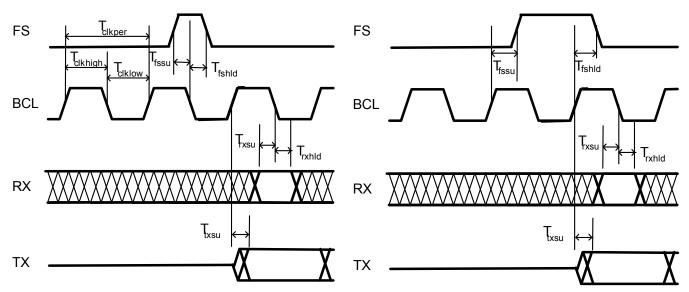

| 7.1.2         | Voice CODEC Protocol               | . 7-2 |

| 7.1.3         | Stereo DAC Protocol                |       |

| 7.1.4         | Audio Port Mixing and Assignment   | . 7-8 |

| 7.2           | Voice CODEC                        |       |

| 7.2.1         | Common Characteristics             | 7-10  |

| 7.2.2         | A/D Converters                     | 7-10  |

| 7.2.3         | D/A Converter.                     | 7-12  |

| 7.2.4         | Clock Modes                        | 7-13  |

| 7.2.5         | Control Bits                       | 7-14  |

| 7.3           | Stereo DAC                         | 7-15  |

| 7.3.1         | Common Characteristics             | 7-15  |

| 7.3.2         | D/A Converter                      | 7-15  |

| 7.3.3         | Clock Modes                        | 7-17  |

| 7.3.4         | Control Bits                       | 7-20  |

| 7.4           | Audio Input Section                | 7-21  |

|               |                                    |       |

MC13783 User's Guide, Rev. 3.8

| 7.4.1       | Microphone Bias                               | . 7-21 |

|-------------|-----------------------------------------------|--------|

| 7.4.2       | Microphone Amplifiers                         | . 7-22 |

| 7.5         | Audio Output Section                          | . 7-25 |

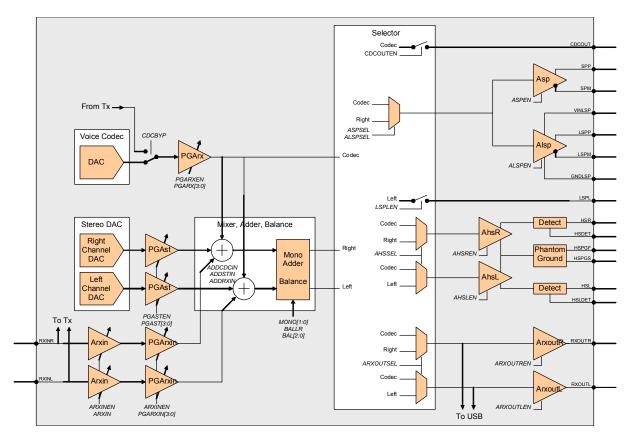

| 7.5.1       | Audio Signal Routing                          | . 7-25 |

| 7.5.2       | Programmable Gain Amplifiers                  | . 7-27 |

| 7.5.3       | Balance, Mixer, Mono Adder and Selector Block | . 7-28 |

| 7.5.4       | Ear Piece Speaker Amplifier Asp               | . 7-31 |

| 7.5.5       | Loudspeaker Amplifier Alsp                    |        |

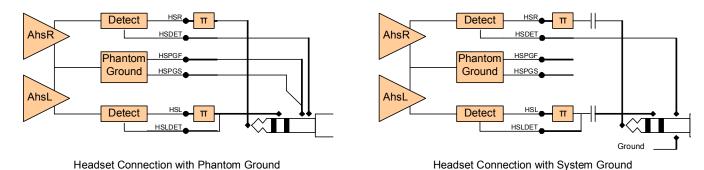

| 7.5.6       | Headset Amplifiers Ahsr/Ahsl                  |        |

| 7.5.7       | Line Output Amplifier Arxout                  |        |

| 7.6         | Audio Control                                 |        |

| 7.6.1       | Supply                                        | . 7-36 |

| 7.6.2       | Bias and Anti Pop                             | . 7-38 |

| 7.6.3       | Arbitration Logic                             |        |

| 7.6.4       | Audio Register Summary                        |        |

|             |                                               |        |

| Chap        |                                               |        |

| Batte       | ry Interface and Control                      |        |

| 8.1         | Introduction                                  | Ω_1    |

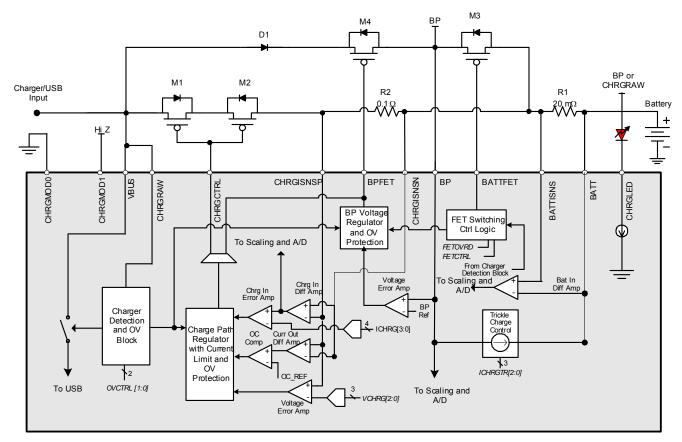

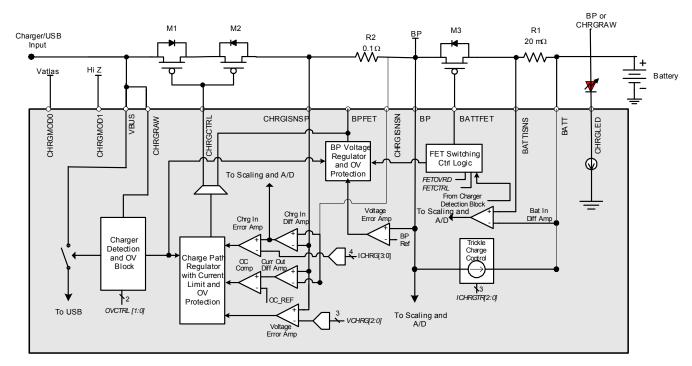

| 8.1.1       | Dual Path Charging.                           |        |

| 8.1.2       | Serial Path Configuration                     |        |

| 8.1.3       |                                               |        |

| 8.1.4       | Single Path Configuration                     |        |

| 8.1.5       |                                               |        |

| 8.1.6       | Separate Input Serial Path Configuration      |        |

| 8.2         | Building Blocks and Functions                 |        |

| 8.2.1       |                                               |        |

| 8.2.2       | Unregulated Charging                          |        |

| 8.2.3       | BP Voltage Regulator                          |        |

| 8.2.4       | Reverse Supply Mode                           |        |

| 8.2.5       | Internal Trickle Charge Current Source        |        |

| 8.2.6       | Battery Comparators                           |        |

| 8.3         | Charger Operation.                            |        |

| 8.3.1       | CEA-936-A.                                    |        |

| 8.3.2       | Charger Control Logic                         |        |

| 8.3.3       | Charger Detection                             |        |

| 8.3.4       | Standalone Trickle Charging                   |        |

| 8.4         | Coincell.                                     |        |

| 8.5         | Battery Interface Register Summary            |        |

|             |                                               |        |

| Chap        |                                               |        |

| ADC         | Subsystem                                     |        |

| 9.1         | Converter Core                                | Q_1    |

| 9.1         | Input Selector                                |        |

| ). <u>u</u> | mput selector                                 | , _    |

MC13783 User's Guide, Rev. 3.8

vi Freescale Semiconductor

| 9.3    | Control                               | . 9-3 |

|--------|---------------------------------------|-------|

| 9.3.1  | Starting Conversions                  | . 9-3 |

| 9.3.2  | Reading Conversions                   | . 9-5 |

| 9.4    | Pulse Generator                       | . 9-6 |

| 9.5    | Dedicated Channels Reading            | . 9-7 |

| 9.5.1  | Battery Current and Voltage           | . 9-7 |

| 9.5.2  | Charge Current and Voltage            | . 9-9 |

| 9.5.3  | Backup Voltage                        | 9-10  |

| 9.5.4  | Battery Thermistor and Battery Detect | 9-10  |

| 9.5.5  | Die Temperature and UID               | 9-11  |

| 9.5.6  | Readout Comparison                    | 9-12  |

| 9.6    | Touch Screen Interface                | 9-14  |

| 9.7    | ADC Arbitration                       | 9-17  |

| 9.8    | ADC Control Register Summary          | 9-21  |

| Chan   | ter 10                                |       |

|        | ectivity                              |       |

| 10.1   | USB Interface                         | 10-1  |

| 10.1.1 | Supplies                              |       |

| 10.1.2 | Detect                                |       |

| 10.1.3 | Transceiver                           |       |

| 10.1.4 | Full Speed/ Low Speed Configuration   |       |

| 10.1.5 | USB Suspend                           |       |

| 10.1.6 | USB On-The-Go.                        |       |

| 10.1.7 | Transceiver Electrical Specification  |       |

| 10.2   | RS-232 Interface                      |       |

| 10.3   | CEA-936-A Accessory Support           |       |

| 10.4   | Booting Support                       |       |

| 10.5   | SPI Register Summary                  |       |

|        |                                       |       |

|        | ter 11<br>ing System                  |       |

|        |                                       |       |

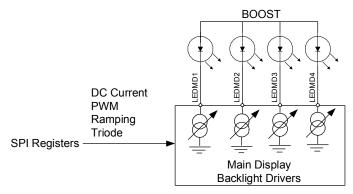

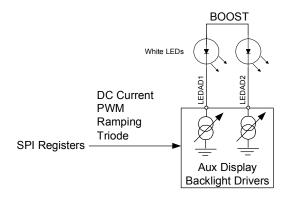

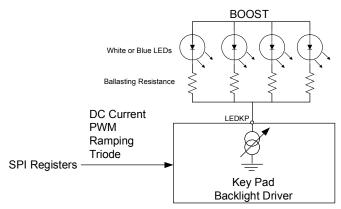

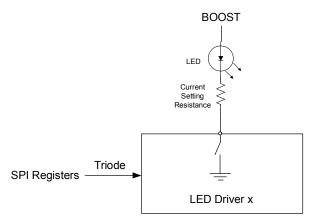

| 11.1   | Backlight Drivers                     |       |

| 11.1.1 | Current Level Control                 |       |

| 11.1.2 | Triode Mode                           |       |

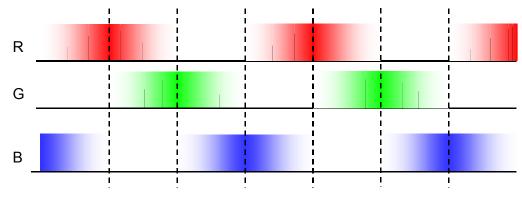

| 11.1.3 | PWM Control                           |       |

| 11.1.4 | Period Control                        |       |

| 11.1.5 | Pulse Control and Brightness Ramping  |       |

| 11.1.6 | SPI Control for Ramp Modes            |       |

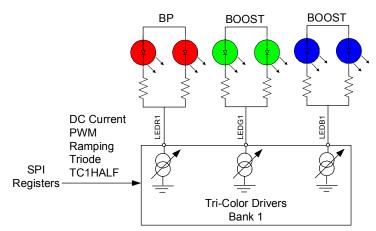

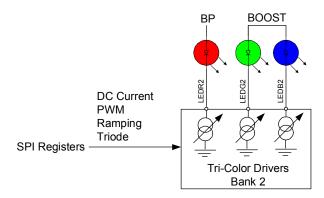

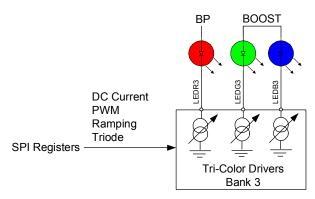

| 11.2   | Tri-Color LED Drivers                 |       |

| 11.2.1 | Current Level Control                 |       |

| 11.2.2 | Triode Mode                           |       |

| 11.2.3 | PWM Control                           |       |

| 11.2.4 | Period Control                        | 11-12 |

Freescale Semiconductor vii

| 11.2.5 | Pulse Control and Brightness Ramping |

|--------|--------------------------------------|

| 11.2.6 | Fun Light Patterns and Control       |

| 11.2.7 | SPI Control for Fun Light Patterns   |

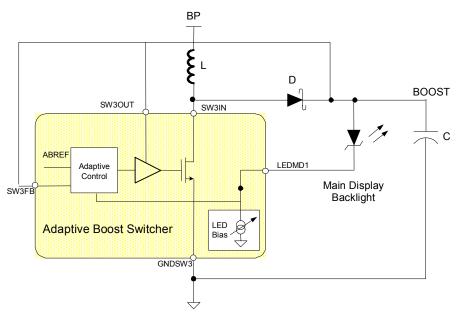

| 11.3   | Adaptive Boost                       |

| 11.4   | SPI Register Summary                 |

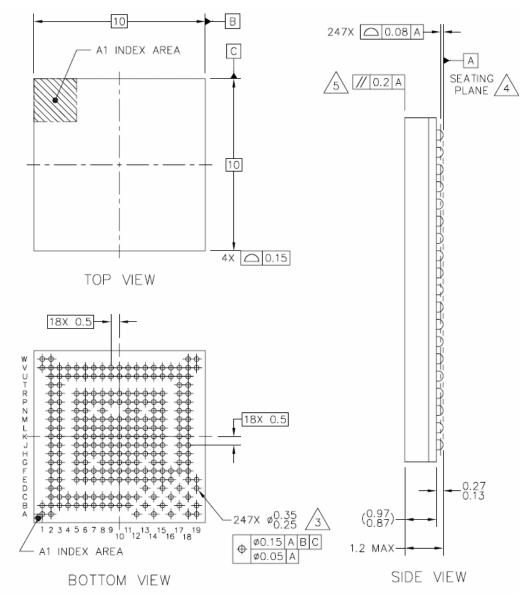

|        | ter 12<br>ut and Package             |

| 12.1   | Package Drawing and Marking          |

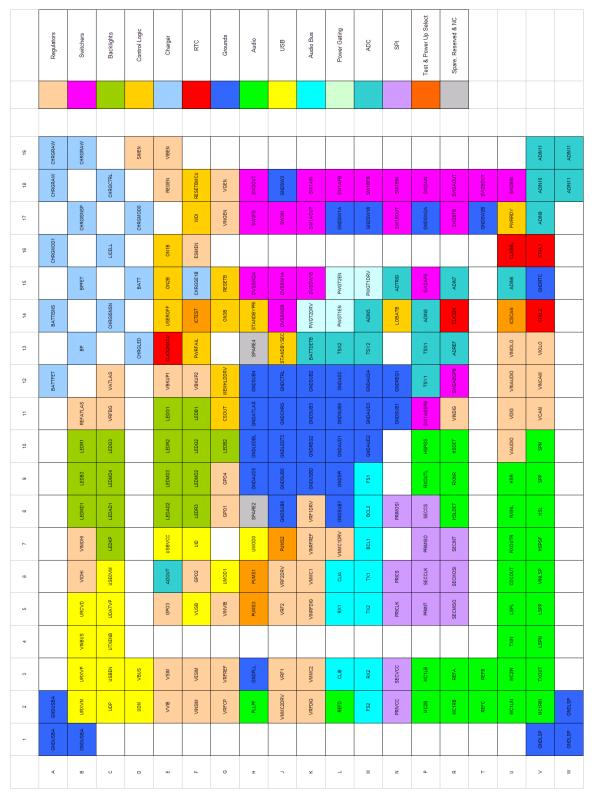

| 12.2   | Pinout Description                   |

| 12.3   | Thermal Characteristics              |

| 12.3.1 | Rating Data                          |

| 12.3.2 |                                      |

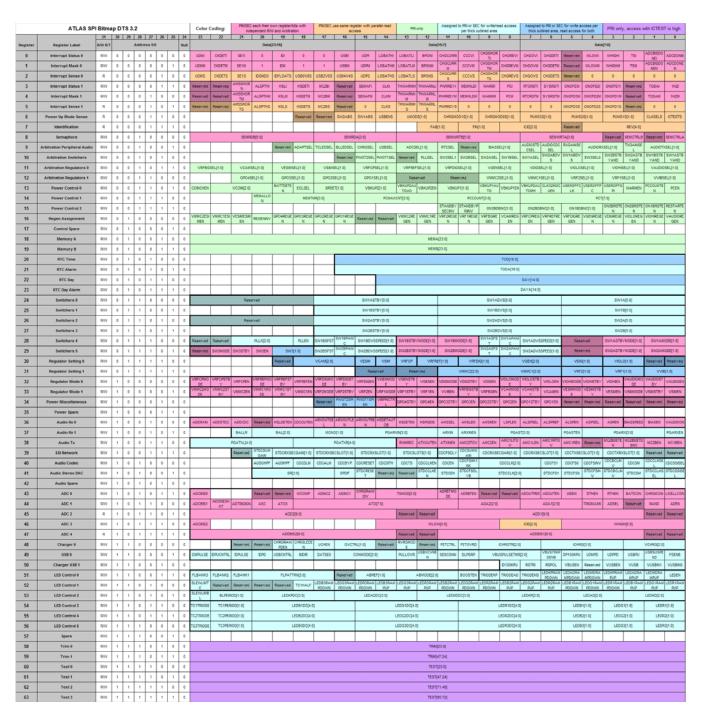

|        | ter 13<br>Bitmap                     |

| 13.1   | Bitmap Diagram                       |

| 13.2   | MC13783 Device Register Summary      |

viii Freescale Semiconductor

#### **About This Book**

This document presents information on the MC13783 power management and audio circuit device. The MC13783 is a highly integrated power management, audio and user interface component dedicated to handset and portable applications covering GSM, GPRS, EDGE and UMTS standards. This device implements high-performance audio functions suited to high-end applications, such as smartphones and UMTS handsets.

#### **Audience**

This document is intended for the:

- Hardware validation team

- Engineer software design team

- Phone product engineering team

- PMP product engineering team

## Organization

This document contains the following chapters:

| Chapter 1  | Introduction                         |

|------------|--------------------------------------|

| Chapter 2  | General Description                  |

| Chapter 3  | Programmability                      |

| Chapter 4  | Clock Generation and Real Time Clock |

| Chapter 5  | Power Control System                 |

| Chapter 6  | Supplies                             |

| Chapter 7  | Audio                                |

| Chapter 8  | Battery Interface and Control        |

| Chapter 9  | ADC Subsystem                        |

| Chapter 10 | Connectivity                         |

| Chapter 11 | Lighting System                      |

| Chapter 12 | Pinout and Package                   |

| Chapter 13 | SPI Bitmap                           |

## **Revision History**

The following table summarizes changes to the technical content of this document since the previous release (Rev. 3.7).

#### **Revision History**

| Location            | Revision                                                                                                    |

|---------------------|-------------------------------------------------------------------------------------------------------------|

| Throughout document | Grammar, style, and formatting changes throughout for clarity and readablity, no technical content changes. |

Freescale Semiconductor ix

## Suggested Reading

External Component Recommendations for the MC13783 Reference Design Application Note (order number AN3295)

MC13783 Buck and Boost Inductor Sizing Application Note, Document Number (order number AN3294)

Interfacing the MC13783 Power Management IC with i.MX31 Applications Processors Application Note (order number AN3276)

MC13783 Recommended Audio Output SPI Sequences Application Note (order number AN3261)

*Voltage Drop Compensation on the MC13783 Switchers Line Application Note* (order number AN3249)

Battery Management for the MC13783 Application Note (order number AN3155)

#### Definitions, Acronyms, and Abbreviations

PMIC Power Management Integrated Circuit

ADC Analog to Digital Converters

DAC Digital to Analog Converter

SSI Serial Standard Interface

SPI Serial Peripheral Interface

RTC Real Time Clock

GPO General Purpose Outputs

PWM Pulse Width Modulation

PFM Pulse Frequency Modulation

PLL Phase Locked Loop

PSRR Power Supply Rejection Ratio ESR Equivalent Serial Resistance

#### References

The following sources were referenced to produce this book:

MC13783 Detailed Technical Specification (DTS), Rev. 3.5, 10/2006, Freescale Semiconductor

## Chapter 1 Introduction

The MC13783 is a highly integrated power management, audio and user interface component dedicated to handset and portable applications covering GSM, GPRS, EDGE and UMTS standards. This device implements high-performance audio functions suited to high-end applications, such as smartphones and UMTS handsets.

#### 1.1 Features

The following features indicate the wide functionality of the MC13783:

- Battery charger interface for wall charging and USB charging

- 10-bit ADC for battery monitoring and other readout functions

- Buck switchers for direct supply of the processor cores

- Boost switcher for backlights and USB on the go supply

- Regulators with internal and external pass devices

- Transmit amplifiers for two handset microphones and a headset microphone

- Receive amplifiers for ear piece, loudspeaker, headset and line out

- 13-bit voice CODEC with dual ADC channel and both narrow and wide band sampling

- 13-bit stereo recording from an analog input source such as FM radio

- 16-bit stereo DAC supporting multiple sample rates

- Dual SSI audio bus with network mode for connection to multiple devices

- Power control logic with processor interface and event detection

- Real time clock and crystal oscillator circuitry

- Dual SPI control bus with arbitration mechanism

- Multiple backlight drivers and LED control including funlight support

- USB/RS232 transceiver with USB Carkit support

- Touchscreen interface

This document provides a detailed overview of each of these functions of the MC13783.

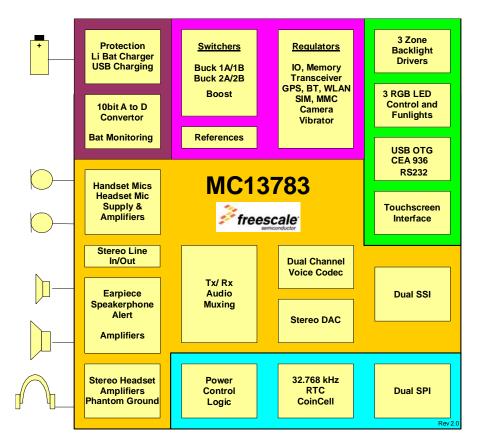

## 1.2 Block Diagram

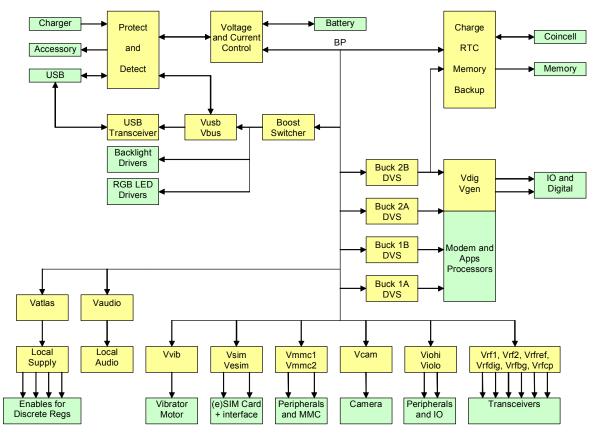

A high level block diagram of the MC13783 is presented Figure 1-1 on page 1-2.

#### Introduction

Figure 1-1. MC13783 High Level Block Diagram

# **Chapter 2 General Description**

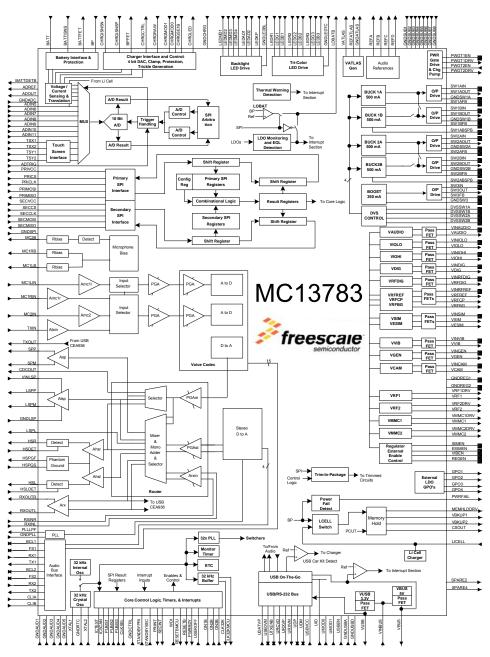

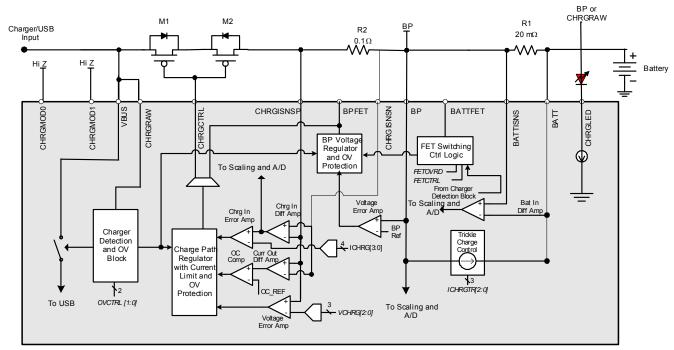

## 2.1 Detailed Block Diagram

Figure 2-1. MC13783 Detailed Block Diagram

MC13783 User's Guide, Rev. 3.8

Freescale Semiconductor 2-1

**General Description**

#### 2.2 Main Functions

This section provides an overview of the primary functions of the MC13783 which are illustrated in the detailed block diagram in Figure 2-1.

#### 2.2.1 Audio

The audio of the MC13783 is composed of microphone and speaker amplifiers, a voice CODEC, and a stereo DAC.

Three microphone amplifiers are available for amplification of two handset microphones and of the headset microphone. The feedback networks are fully integrated for a current input arrangement. A line input buffer amplifier is provided for connecting external sources. All microphones have their own stabilized supply with an integrated microphone sensitivity setting. The microphone supplies can be disabled. The headset microphone supply has a fully integrated microphone detection.

Several speaker amplifiers are provided. A bridged ear piece amplifier is available to drive an ear piece. Also a battery supplied bridged amplifier with thermal protection is included to drive a low ohmic speaker for speakerphone and alert functionality. The performance of this amplifier allows it to be used as well for ear piece drive to support applications with a single transducer combining ear piece, speakerphone and alert functionality, thus avoiding the use of multiple transducers.

A left audio out is provided which in combination with a discrete power amplifier and the integrated speaker amplifier allows for a stereo speaker application. Two single ended amplifiers are included for the stereo headset drive including headset detection. The stereo headset return path is connected to a phantom ground which avoids the use of large DC decoupling capacitors. The additional stereo receive signal outputs can be used for connection to external accessories like a car kit. Via a stereo line in, external sources such as an FM radio or standalone midi ringer can be applied to the receive path.

A voice CODEC with a dual path ADC is implemented following GSM audio requirements. Both narrow band and wide band voice is supported. The dual path ADC allows for conversion of two microphone signal sources at the same time for noise cancellation or stereo applications as well as for stereo recording from sources like FM radio. A 16bit stereo DAC is available which supports multi clock modes. An on board PLL ensures proper clock generation. The voice CODEC and the stereo DAC can be operated at the same time via two interchangeable busses supporting master and slave mode, network mode, as well as the different protocols like I2S.

Volume control is included in both transmit and receive paths. The latter also includes a balance control for stereo. The mono adder in the receive path allows for listening to a stereo source on a mono transducer. The receive paths for stereo and mono are separated to allow the two sources to be played back simultaneously on different outputs. The different sources can be analog mixed and two sources on the SSI configured in network mode can be mixed as well.

#### 2.2.2 Switchers and Regulators

The MC13783 provides most of the telephone reference and supply voltages.

Four down converters and an up converter are included. The down, or buck, converters provide the supply to the processors and to other low voltage circuits such as I/O and memory. The four down converters can be combined into two higher power converters. Dynamic voltage scaling is provided on each of the down converters. This allows under close processor control to adapt the output voltage of the converters to minimize processor current drain. The up, or boost, converter supplies the white backlight LEDs and the regulators for the USB transceiver. The boost converter output has a backlight headroom tracking option to reduce overall power consumption.

The regulators are directly supplied from the battery or from the switchers and include supplies for I/O and peripherals, audio, camera, multi media cards, SIM cards, memory and the transceivers. Enables for external discrete regulators are included as well as a vibrator motor regulator. A dedicated preamplifier audio output is available for multifunction vibrating transducers.

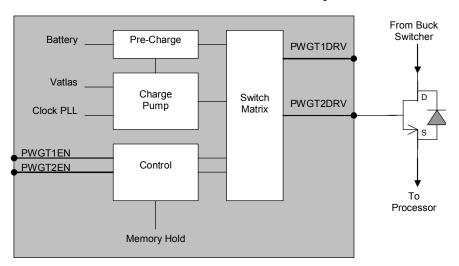

Drivers for power gating with external NMOS transistors are provided including a fully integrated charge pump. This will allow to power down parts of the processor to reduce leakage current.

#### 2.2.3 Battery Management

The MC13783 supports different charging and supply schemes including single path and serial path charging. In single path charging the phone is always supplied from the battery and therefore always has to be present and valid. In a serial path charging scheme the phone can operate directly from the charger while the battery is removed or deeply discharged.

The charger interface provides linear operation via an integrated DAC and unregulated operation like used for pulsed charging. It incorporates a standalone trickle charge mode in case of a dead battery with LED indicator driver. Over voltage, short circuit and under voltage detectors are included as well as charger detection and removal. The charger includes the necessary circuitry to allow for USB charging and for reverse supply to an external accessory. The battery management is completed by a battery presence detector and an A to D converter that serves for measuring the charge current, battery and other supply voltages as well as for measuring the battery thermistor and die temperature.

## 2.2.4 Logic

The MC13783 is fully programmable via SPI bus. Additional communication is provided by direct logic interfacing. Default startup of the device is selectable by hard wiring the Power Up Mode Select pins.

Both the call processor and the applications processor have full access to the MC13783 resources via two independent SPI busses. The primary SPI bus is able to allow the secondary SPI bus to control all or some of the registers. On top of this an arbitration mechanism is built in for the audio, the power and ADC functions. This together will avoid programming conflicts in case of a dual processor type of application.

The power cycling of the phone is driven by the MC13783. It has the interfaces for the power buttons and dedicated signaling interfacing with the processor. It also ensures the supply of the memory and other circuits from the coin cell in case of brief power failures. A charger for the coin cell is included as well. Several pre-selectable power modes are provided such as SDRAM self refresh mode and user off mode.

MC13783 User's Guide, Rev. 3.8

Freescale Semiconductor

2-3

#### **General Description**

The MC13783 provides the timekeeping based on an integrated low-power oscillator running with a standard watch crystal. This oscillator is used for internal clocking, the control logic, and as a reference for the switcher PLL. The timekeeping includes time of day, calendar and alarm. The clock is put out to the processors for reference and deep sleep mode clocking.

#### 2.2.5 Miscellaneous Functions

The drivers and comparators for a USB On the Go and a CEA-936-A compatible USB carkit including audio routing, as well as RS232 interfaces are provided. Special precautions are taken to allow for specific booting and accessory detection modes.

Current sources are provided to drive tricolored funlights and signaling LEDs. The funlights have pre-programmed lighting patterns. The wide programmability of the tricolored LED drivers allows for applications such as audio modulation. Three backlight drivers with auto dimming are included as well for keypad and dual display backlighting.

A dedicated interface in combination with the A to D converter allow for precise resistive touch screen reading. Pen touch wake up is included.

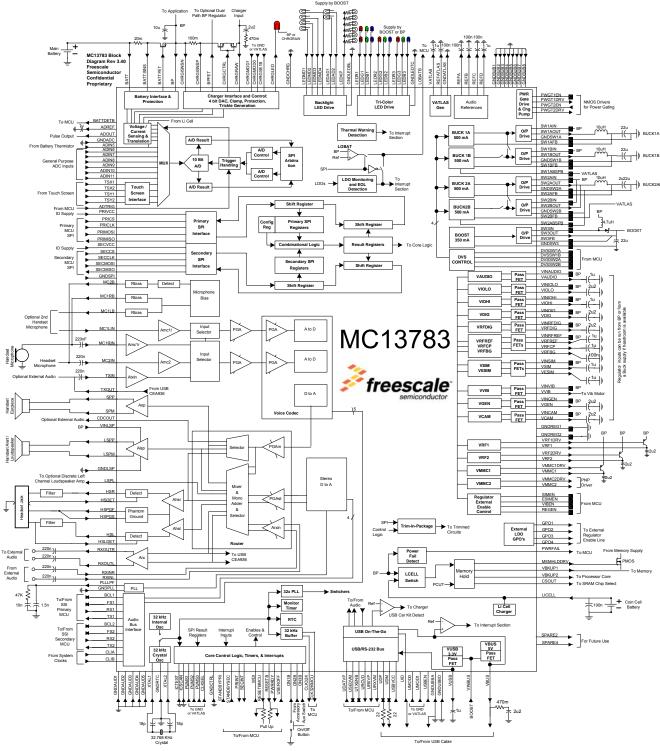

## 2.3 Typical Application

Figure 2-2 gives a typical application diagram of the MC13783 together with its functional components. For details on component references and additional components such as filters please refer to the individual chapters.

Figure 2-2. Typical Application Diagram

Freescale Semiconductor 2-5

**General Description**

## 2.4 Maximum Ratings and Operating Input Voltage

#### 2.4.1 Absolute Maximum Ratings

Table 2-1 gives the maximum allowed voltages, current and temperature ratings which can be applied to the IC. Exceeding these ratings can damage the circuit.

**Units** Min Typ Max **Parameter** Charger Input Voltage -0.3 +20 V USB Input Voltage if Common to Charger -0.3+20 USB Input Voltage if Separate from Charger -0.3 +5.50 V ٧ Battery Voltage -0.3 +4.65 V Coincell Voltage -0.3 +4.65 -30 °C Ambient Operating Temperature Range +85 Operating Junction Temperature Range -30 +125 °C Storage Temperature Range °С -65 +150ESD Protection Human Body Model 2.0 kV

**Table 2-1. Absolute Maximum Ratings**

The detailed maximum voltage rating per pin can be found in the pin list which is included in chapter 12.

## 2.4.2 Power Dissipation

During operation, the temperature of the die must not exceed the maximum junction temperature. Depending on the operating ambient temperature and the total dissipation on the circuit this limit can be exceeded.

To optimize the thermal management scheme and avoid overheating, the MC13783 provides a thermal management system. The thermal protection uses the temperature dependency of the voltage of a forward biased junction. This junction voltage can be read out via the ADC for precise temperature readouts, Chapter 9, "ADC Subsystem".

Internally this voltage is monitored by means of a comparator and an interrupt THWARNLI and THWARNHI will be generated when respectively crossing, in either direction, the lower and higher thermal warning thresholds. The temperature range can be determined by reading the THWARNLS and THWARNHS bits.

A thermal protection is integrated which will power off the MC13783 in case of over dissipation. This thermal protection will act above the maximum junction temperature to avoid any unwanted power downs. The protection is debounced by one period of the 32 kHz clock in order to suppress any (thermal) noise. Consider this protection as a fail-safe mechanism and therefore the phone design must not be dimensioned such that this protection is tripped under normal conditions. The temperature thresholds and the sense bit assignment are listed in Table 2-2 and Table 2-3.

| Table 2-2  | Thermal    | Protection | <b>Thresholds</b> |

|------------|------------|------------|-------------------|

| Iable 2-2. | HIIGHIIIAI | FIULECTION | IIII CONUUS       |

| Parameter                               |     | Тур | Max | Units |

|-----------------------------------------|-----|-----|-----|-------|

| Thermal Warning Lower Threshold (Twl)   |     | 100 | 105 | °C    |

| Thermal Warning Higher Threshold (Twh)  |     | 120 | 125 | °C    |

| Thermal Warning Hysteresis <sup>1</sup> |     |     | 4   | °C    |

| Thermal Protection Threshold            | 130 | 140 | 150 | °C    |

<sup>1</sup> Equivalent to approximately 50 mW min., 100 mW max.

**Table 2-3. Thermal Warning Sense Bits**

| Temperature   | THWARNHS | THWARNLS |

|---------------|----------|----------|

| T < Twl       | 0        | 0        |

| Twl < T < Twh | 0        | 1        |

| Twh < T       | 1        | 1        |

Because the speakerphone amplifier is the only single block on the MC13783 which can consume significant power on itself, this block has an additional thermal protection, see Chapter 7, "Audio". The thermal characteristics of the package are listed in detail in Chapter 12, "Pinout and Package".

## 2.4.3 Current Consumption

The current consumption of the individual blocks is described in detail throughout this specification. For convenience, Table 2-4 is included with the main characteristics.

#### **NOTE**

The external loads are not taken into account.

**Table 2-4. Summary of Current Consumption**

| Mode      | Description                                                                                                                                                       | Тур                  | Max                  | Unit |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| RTC       | All blocks disabled, no main battery attached, coincell is attached to LICELL: MC13783 core and RTC module                                                        | 4                    | 6                    | uA   |

| OFF       | All blocks disabled except for MC13783 core and RTC module supplied from BATT                                                                                     | 30                   | 45                   | uA   |

| Power Cut | All blocks disabled, no main battery attached, coincell is attached and valid: MC13783 core and RTC module Trimmed references low-power 2 backup regulators Total | 5<br>20<br>10<br>35  | 6<br>30<br>16<br>52  | uA   |

| User OFF  | All blocks disabled except for: MC13783 core and RTC module Trimmed references low-power 2 backup regulators Total                                                | 30<br>20<br>10<br>60 | 45<br>30<br>16<br>91 | uA   |

Freescale Semiconductor 2-7

#### **General Description**

Table 2-4. Summary of Current Consumption (continued)

| Mode               | Description                                                                                                                                                                                                                                           | Тур                                           | Max                                           | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|------|

| ON Standby         | Low-power mode: MC13783 core and RTC module Trimmed references Power gating, comparators and I/O 2 switchers in low-power mode 5 regulators in low-power mode including 1 with external pass device Total                                             | 30<br>40<br>10<br>30<br>25<br>135             | 45<br>50<br>15<br>60<br>50<br>220             | uA   |

| ON Mode            | Typical 'power only' use case:  MC13783 core and RTC module Trimmed references Power gating, comparators and I/O Switcher core and 2 buck switchers In pulse skipping mode 10 Regulators internal pass device 2 Regulators external pass device Total | 30<br>40<br>10<br>280<br>200<br>60<br>620     | 45<br>50<br>15<br>500<br>300<br>90<br>1000    | uA   |

| ON Audio Call      | ON Mode with: Voice CODEC Audio Bias Microphone Bias, Amplifier, PGA Receive Channel Mono Ear piece Amplifier Total                                                                                                                                   | 0.6<br>3.0<br>0.2<br>0.6<br>0.6<br>2.3<br>7.3 | 1.0<br>4.0<br>0.3<br>0.9<br>0.9<br>2.8<br>9.9 | mA   |

| ON Stereo Playback | ON Mode with: Stereo DAC Audio Bias Receive Channel Stereo Headset Amplifier Total                                                                                                                                                                    | 0.6<br>6.0<br>0.2<br>1.2<br>1.5<br>9.5        | 1.0<br>7.0<br>0.3<br>1.8<br>2.0<br>12.1       | mA   |

## 2.4.4 Operational Input Voltage Range

Table 5 provides the recommended operational input voltage range of the MC13783.

**Table 5. Operational Input Voltage Range**

| Parameter                                              | Minimum | Maximum | Units |

|--------------------------------------------------------|---------|---------|-------|

| Operational input voltage range (connected to BP node) | +2.6    | +4.65   | V     |

## 2.5 I/O Characteristics

The characteristics of the logic inputs and outputs are described in detail throughout this specification. For convenience, Table 2-6 is included with the main characteristics.

Table 2-6. Summary of I/O Characteristics

| Pin Name                                                | Internal<br>Termination <sup>1</sup> | Parameter                 | Load<br>Condition   | Min               | Max <sup>2</sup>             | Unit |

|---------------------------------------------------------|--------------------------------------|---------------------------|---------------------|-------------------|------------------------------|------|

| ON1B, ON2B, ON3B                                        | Pull up <sup>3</sup>                 | Input Low<br>Input High   | 47 kOhm<br>1 MOhm   | 0<br>0.7 * VATLAS | 0.3 * VATLAS<br>VATLAS       | V    |

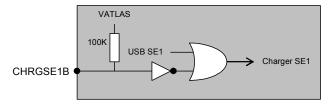

| CHRGSE1B                                                | Pull up <sup>4</sup>                 | Input Low<br>Input High   | _                   | 0<br>0.7 * VATLAS | 0.3 * VATLAS<br>VATLAS       | V    |

| STANDBYPRI,<br>STANDBYSEC, WDI <sup>5</sup> ,<br>ADTRIG | Weak Pull Down                       | Input Low<br>Input High   | _                   | 0<br>0.7 * VIOLO  | 0.3 * VIOLO<br>3.1           | V    |

| USEROFF                                                 | Weak Pull Down                       | Input Low<br>Input High   | _                   | 0<br>0.7 * VBKUP1 | 0.3 * VBKUP1<br>3.1          | V    |

| LOBATB, CLK32K,<br>PWRRDY, BATTDETB                     | CMOS                                 | Output Low<br>Output High | -100 uA<br>100 uA   | 0<br>VIOLO - 0.2  | 0.2<br>VIOLO                 | V    |

| CLK32KMCU <sup>6</sup> , PWRFAIL                        | CMOS                                 | Output Low<br>Output High | -100 uA<br>100 uA   | 0<br>VBKUP1 - 0.2 | 0.2<br>VBKUP1                | V    |

| ADOUT                                                   | CMOS                                 | Output Low<br>Output High | -1 mA<br>1 mA       | 0<br>VIOHI - 0.2  | 0.2<br>VIOHI                 | V    |

| RESETB, RESETBMCU <sup>7</sup>                          | Open Drain                           | Output Low<br>Output High | -2 mA<br>Open Drain | 0                 | 0.4<br>3.1                   | V    |

| DVSSW1A, DVSSW1B,<br>DVSSW2A, DVSSW2B                   | Weak Pull Down                       | Input Low<br>Input High   | _                   | 0<br>0.7 * VIOLO  | 0.3 * VIOLO<br>3.1           | V    |

| PWGT1EN, PWGT2EN                                        | Weak Pull Down                       | Input Low<br>Input High   | _                   | 0<br>0.7 * VIOLO  | 0.3 * VIOLO<br>3.1           | V    |

| SIMEN, ESIMEN, VIBEN, REGEN                             | Weak Pull Down                       | Input Low<br>Input High   | _                   | 0<br>0.7 * VIOLO  | 0.3 * VIOLO<br>3.1           | V    |

| GPO1, GPO2, GPO3,<br>GPO4                               | CMOS                                 | Output Low<br>Output High | -100 uA<br>100 uA   | 0<br>VIOHI - 0.2  | 0.2<br>VIOHI                 | V    |

| PRICS, PRICLK,<br>PRIMOSI                               | _                                    | Input Low<br>Input High   | _                   | 0<br>0.7 * PRIVCC | 0.3 * PRIVCC<br>PRIVCC + 0.5 | V    |

| PRIMISO, PRIINT                                         | CMOS                                 | Output Low<br>Output High | -100 uA<br>100 uA   | 0<br>PRIVCC - 0.2 | 0.2<br>PRIVCC                | V    |

| SECCS, SECCLK,<br>SECMOSI                               | _                                    | Input Low<br>Input High   | _                   | 0<br>0.7 * SECVCC | 0.3 * SECVCC<br>SECVCC + 0.5 | V    |

| SECMISO, SECINT                                         | CMOS                                 | Output Low<br>Output High | -100 uA<br>100 uA   | 0<br>SECVCC - 0.2 | 0.2<br>SECVCC                | V    |

| BCL1, FS1, RX1                                          | _                                    | Input Low<br>Input High   | _                   | 0<br>0.7 * PRIVCC | 0.3 * PRIVCC<br>PRIVCC + 0.5 | V    |

| BCL1, FS1, TX1                                          | CMOS                                 | Output Low<br>Output High | -100 uA<br>100 uA   | 0<br>PRIVCC - 0.2 | 0.2<br>PRIVCC                | V    |

Freescale Semiconductor 2-9

#### **General Description**

Table 2-6. Summary of I/O Characteristics (continued)

| Pin Name                                          | Internal<br>Termination <sup>1</sup> | Parameter                            | Load<br>Condition | Min                                | Max <sup>2</sup>                     | Unit |

|---------------------------------------------------|--------------------------------------|--------------------------------------|-------------------|------------------------------------|--------------------------------------|------|

| BCL2, FS2, RX2                                    | _                                    | Input Low<br>Input High              | _                 | 0<br>0.7 * SECVCC                  | 0.3 * SECVCC<br>SECVCC + 0.5         | V    |

| BCL2, FS2, TX2                                    | CMOS                                 | Output Low<br>Output High            | -100 uA<br>100 uA | 0<br>SECVCC - 0.2                  | 0.2<br>SECVCC                        | ٧    |

| CLIA, CLIB                                        | AC Coupled                           | Peak to peak input                   | _                 | 0.3                                | VAUDIO + 0.3                         | V    |

| UDATVP, USE0VM,<br>UTXENB                         | Weak Pull Down                       | Input Low<br>Input High              | _                 | 0<br>0.7 * USBVCC                  | 0.3 * USBVCC<br>3.1                  | V    |

| URXVP, URXVM, URCVD,<br>UDATVP, USE0VM,<br>UTXENB | CMOS                                 | Output Low<br>Output High            | -400 uA<br>400 uA | 0<br>USBVCC - 0.4                  | 0.4<br>USBVCC                        | V    |

| USBEN                                             | Weak Pull Down                       | Input Low<br>Input High              | _                 | 0<br>1.3                           | 0.5<br>3.1                           | V    |

| PUMS1, PUMS2, PUMS3,<br>UMOD0                     | 8                                    | Input Low<br>Input Mid<br>Input High | ±100 uA           | 0<br>0.45 * VATLAS<br>0.7 * VATLAS | 0.3 * VATLAS<br>0.55 * VATLAS<br>3.1 | V    |

| SW1ABSPB, SW2ABSPB                                | 9<br>Weak Pull Down                  | Input Low<br>Input High              | _                 | 0<br>0.7 * VATLAS                  | 0.3 * VATLAS<br>3.1                  | V    |

| CHRGMOD0,<br>CHRGMOD1                             | 9                                    | Input Low<br>Input Mid<br>Input High | ±100 uA           | 0<br>0.45 * VATLAS<br>0.7 * VATLAS | 0.3 * VATLAS<br>0.55 * VATLAS<br>3.1 | V    |

| UMOD1                                             | 8                                    | Input Low<br>Input High              | _                 | 0<br>0.7 * VATLAS                  | 0.3 * VATLAS<br>3.1                  | V    |

| ICTEST, ICSCAN,<br>CLKSEL                         | 9                                    | Input Low<br>Input High              | _                 | 0<br>0.7 * VATLAS                  | 0.3 * VATLAS<br>3.1                  | V    |

| VATLAS                                            | _                                    | _                                    | _                 | 2.50                               | 2.86                                 | V    |

| VAUDIO                                            | _                                    | _                                    | _                 | 2.69                               | 2.86                                 | V    |

| VIOLO                                             | _                                    | _                                    | _                 | 1.15                               | 1.86                                 | V    |

| VIOHI                                             | _                                    | _                                    | _                 | 2.69                               | 2.86                                 | ٧    |

| VBKUP1                                            | _                                    | _                                    | _                 | 0.95                               | 1.85                                 | ٧    |

| PRIVCC, SECVCC                                    | _                                    | _                                    | _                 | 1.74                               | 3.10                                 | ٧    |

| USBVCC                                            |                                      |                                      |                   | 1.74                               | 3.10                                 | V    |

<sup>&</sup>lt;sup>1</sup> A weak pull down represents a nominal internal pull down of 100nA unless otherwise noted.

2-10 Freescale Semiconductor

<sup>&</sup>lt;sup>2</sup> The maximum must never exceed the maximum rating of the pin as given in Chapter 12, "Pinout and Package".

<sup>&</sup>lt;sup>3</sup> Input has internal pull up to VATLAS equivalent to 200 kOhm.

<sup>&</sup>lt;sup>4</sup> Input has internal pull up to VATLAS equivalent to 100 kOhm.

<sup>&</sup>lt;sup>5</sup> VIOLO needs to remain enabled for proper detection of WDI High to avoid involuntary shutdown.

<sup>&</sup>lt;sup>6</sup> During non power cut operation the VBKUP1 regulator can be inactive while an external supply is applied to the VBKUP1 pin.

<sup>&</sup>lt;sup>7</sup> RESETB and RESETBMCU are open drain outputs, an external pull up is required.

$<sup>^{8}\,\,</sup>$  Input state is latched in first phase of cold start.

<sup>&</sup>lt;sup>9</sup> Input state is not latched.

# Chapter 3 Programmability

#### 3.1 SPI Interface

The MC13783 IC contains two SPI interface ports which allow parallel access by both the call processor and the applications processor to the MC13783 register set. Via these registers the MC13783 resources can be controlled. The registers also provide status information about how the MC13783 IC is operating as well as information on external signals. The SPI interface is comprised of the signals listed in Table 3-1.

**Table 3-1. SPI Interface Pin Description**

| SPI Interface Pin | Description                                                                   |

|-------------------|-------------------------------------------------------------------------------|

| SPI Bus           |                                                                               |

| PRICLK            | Primary processor clock input line, data shifting occurs at the rising edge   |

| PRIMOSI           | Primary processor serial data input line                                      |

| PRIMISO           | Primary processor serial data output line                                     |

| PRICS             | Primary processor clock enable line, active high                              |

| SECCLK            | Secondary processor clock input line, data shifting occurs at the rising edge |

| SECMOSI           | Secondary processor serial data input line                                    |

| SECMISO           | Secondary processor serial data output line                                   |

| SECCS             | Secondary processor clock enable line, active high                            |

| Interrupt         |                                                                               |

| PRIINT            | Primary processor interrupt                                                   |

| SECINT            | Secondary processor interrupt                                                 |

| Supply            |                                                                               |

| PRIVCC            | Primary processor SPI bus supply                                              |

| SECVCC            | Secondary processor SPI bus supply                                            |

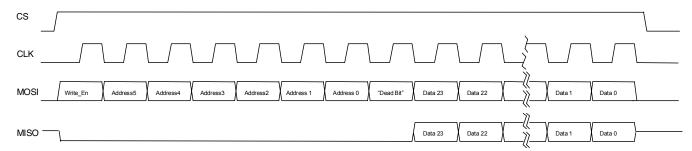

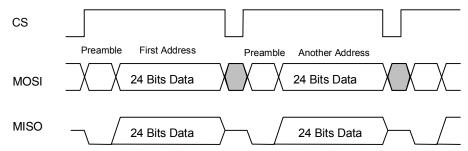

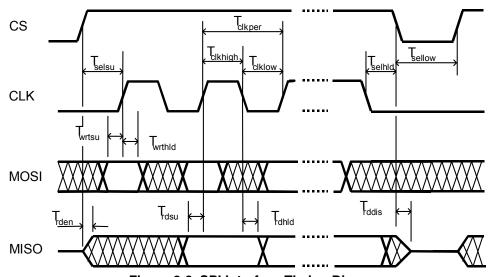

Both SPI ports are configured to utilize 32-bit serial data words, using 1 read/write bit, 6 address bits, 1 null bit, and 24 data bits. The SPI ports' 64 registers correspond to the 6 address bits.

Programmability

14

15

## 3.2 Register Set

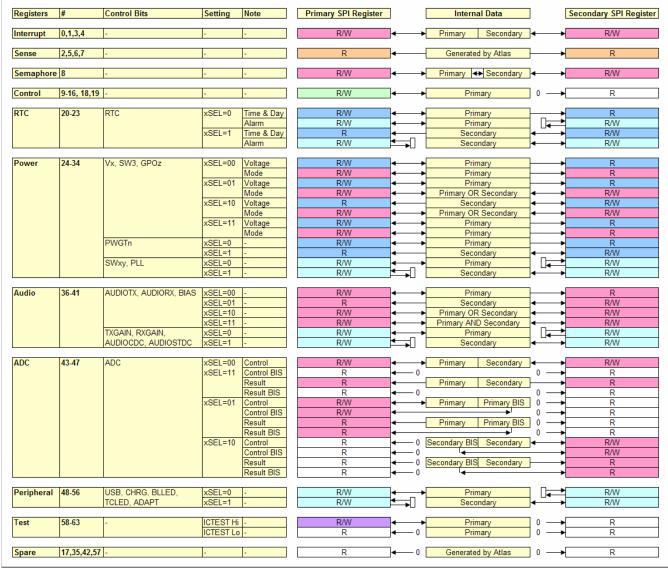

The register set is given in Table 3-2. A more detailed overview of the SPI bits, the arbitration and the register assignment is given in Chapter 13, "SPI Bitmap".

Register Register Register Register 16 32 0 Interrupt Status 0 Regen Assignment Regulator Mode 0 48 Charger USB 0 1 Interrupt Mask 0 17 Control Spare 33 Regulator Mode 1 49 2 Interrupt Sense 0 18 Memory A 34 Power Miscellaneous 50 Charger USB 1 3 Interrupt Status 1 19 Memory B 35 **Power Spare** 51 LED Control 0 4 20 36 LED Control 1 Interrupt Mask 1 **RTC Time** Audio Rx 0 52 5 Interrupt Sense 1 21 RTC Alarm 37 Audio Rx 1 53 LED Control 2 6 Power Up Mode Sense 22 38 Audio Tx 54 LED Control 3 RTC Day 7 Identification 23 RTC Day Alarm 39 SSI Network 55 LED Control 4 8 Semaphore 24 Switchers 0 40 Audio CODEC 56 LED Control 5 57 Arbitration Peripheral Audio 25 Switchers 1 41 Audio Stereo DAC Spare 10 26 42 **Arbitration Switchers** Switchers 2 Audio Spare 58 Trim 0 11 Arbitration Regulators 0 27 43 59 Switchers 3 ADC 0 Trim 1 12 Arbitration Regulators 1 28 Switchers 4 44 ADC 1 60 Test 0 13 Power Control 0 29 Switchers 5 45 ADC 2 61 Test 1

Table 3-2. Register Set

## 3.3 Dual SPI Resource Sharing

30

31

Regulator Setting 0

Regulator Setting 1

## 3.3.1 General Description

Power Control 1

Power Control 2

In single processor configurations the MC13783 SPI resources do not have to be shared and access control is not required. In that case the processor has to communicate via the PRISPI bus where it has direct access to the register base. In dual processor configurations, all the MC13783 SPI resources can be shared between the primary and secondary SPI interfaces. The MC13783 provides a method for controlling the sharing of its resources so that both processors access the resources they need.

46

47

ADC 3

ADC 4

62

63

Test 2

Test 3

At startup, all resources, (bits or bit vectors within a SPI register) are readable and writable via the primary SPI interface while in general the secondary SPI bus has a read access only. Via the primary SPI interface, most resources can be assigned to be controlled from the secondary SPI interface.

#### 3.3.2 Supply Arbitration

The switchers and regulators can be controlled by both SPI busses. The assignment and shared control of switchers and regulators is done via the SEL bits as indicated in Table 3-3. See Chapter 5, "Power Control System" and Chapter 6, "Supplies" for more details on the arbitration.

**Table 3-3. Supply Arbitration Control**

| Bit          | State | Description                                                                            | Standby Mode Control                                                                                                                |

|--------------|-------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| SWxySEL      | 0     | Primary SPI has sole control                                                           | STANDBYPRI if SWxSTBYAND=0. Logic AND of STANDBYPRI and STANDBYSEC if SWxySTBYAND=1.                                                |

|              | 1     | Secondary SPI has sole control                                                         | STANDBYSEC if SWxSTBYAND=0. Logic AND of STANDBYPRI and STANDBYSEC if SWxySTBYAND=1.                                                |

| VxSEL[1:0]   | 00    | Primary SPI has sole control                                                           | STANDBYPRI                                                                                                                          |

| SW3SEL[1:0]  | 01    | Only primary SPI can set the voltage level, both SPIs can control the operating mode   | STANDBYPRI for primary SPI. STANDBYSEC for secondary SPI. The highest power mode out of the two requested by both SPIs is selected. |

|              | 10    | Only secondary SPI can set the voltage level, both SPIs can control the operating mode | STANDBYPRI for primary SPI. STANDBYSEC for secondary SPI. The highest power mode out of the two requested by both SPIs is selected. |

|              | 11    | Primary SPI has sole control                                                           | Logic AND of STANDBYPRI and STANDBYSEC.                                                                                             |

| GPOzSEL[1:0] | 00    | Primary SPI has sole control                                                           | STANDBYPRI                                                                                                                          |

|              | 01    | Both SPIs can control the operating mode                                               | STANDBYPRI for primary SPI. STANDBYSEC for secondary SPI. The highest power mode out of the two requested by both SPIs is selected. |

|              | 10    | _                                                                                      | _                                                                                                                                   |

|              | 11    | Primary SPI has sole control                                                           | Logic AND of STANDBYPRI and STANDBYSEC.                                                                                             |

| PWGTnSEL     | 0     | Primary SPI has sole control                                                           | _                                                                                                                                   |

| PLLSEL       | 1     | Secondary SPI has sole control                                                         | -                                                                                                                                   |

**Note:** xy Stands for all switchers (1A, 1B, 2A, and 2B), x for all regulators (IOHI, DIG, etc.), z for all GPO outputs (1, 2, 3, and 4), and n for all PWGT drivers (1 and 2).

The VxSEL, SW3SEL, GPOzSEL and PWGTnSEL assigned registers and bits are always readable by both SPI busses independent on which bus has control. Both busses will read back the actual state of the regulator, switcher, etc. see Chapter 5, "Power Control System". This is not valid for the registers and bits determined by SWxySEL and PLLSEL. Here the SPI bus which does not have control can still write, but this will have no effect on the operation of the IC, while it will read back its own written data.

**Programmability**

#### 3.3.3 Audio Resource Sharing

The sharing of audio resources between the primary and secondary SPI interfaces allow both processors to, for example, enable or disable audio amplifiers or control audio gains if programmed and read back the actual state of the amplifiers. This is true for the bits assigned by AUDIOTXSEL, AUDIORXSEL and BIASSEL. The other bits are only controllable and readable by the SPI which has control. The SPI bus which does not have control can still write, but this will have no effect on the operation of the IC. The non controlling SPI will read its own written data.

**Table 3-4. Audio Arbitration Control**

| Bits            | Description                                                                                                                                       | Bits Concerned                          |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| AUDIOTXSEL[1:0] | Transmit audio amplifiers assignment<br>00 = Primary SPI only<br>01 = Secondary SPI only<br>10 = OR-ing of both SPIs<br>11 = AND-ing of both SPIs | Reg 38, bits 0-13                       |

| TXGAINSEL       | Transmit gain assignment 0 = Primary SPI only 1 = Secondary SPI only                                                                              | Reg 38, bits 14-23                      |

| AUDIORXSEL[1:0] | Receive audio amplifiers assignment<br>00 = Primary SPI only<br>01 = Secondary SPI only<br>10 = OR-ing of both SPIs<br>11 = AND-ing of both SPIs  | Reg 36, bits 3-23                       |

| RXGAINSEL       | Receive gain assignment<br>0 = Primary SPI only<br>1 = Secondary SPI only                                                                         | Reg 37, bits 0-21                       |

| AUDIOCDCSEL     | CODEC assignment<br>0 = Primary SPI only<br>1 = Secondary SPI only                                                                                | Reg 40, bits 0-20<br>Reg 39, bits 0-11  |

| AUDIOSTDCSEL    | Stereo DAC assignment<br>0 = Primary SPI only<br>1 = Secondary SPI only                                                                           | Reg 41, bits 0-20<br>Reg 39, bits 12-21 |

| BIASSEL[1:0]    | Audio bias assignment 00 = Primary SPI only 01 = Secondary SPI only 10 = OR-ing of both SPIs 11 = AND-ing of both SPIs                            | Reg 36, bits 0-2                        |

See Chapter 7, "Audio" for more details.

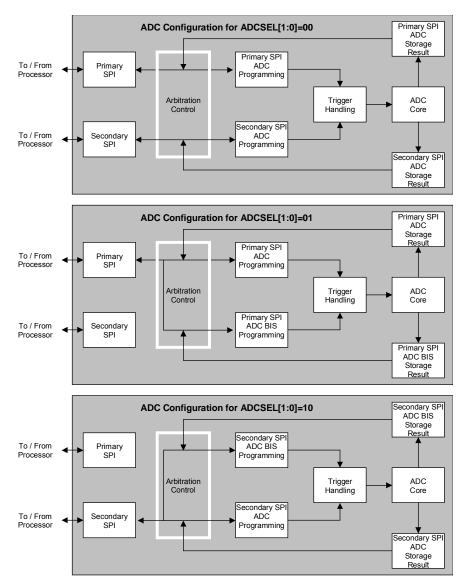

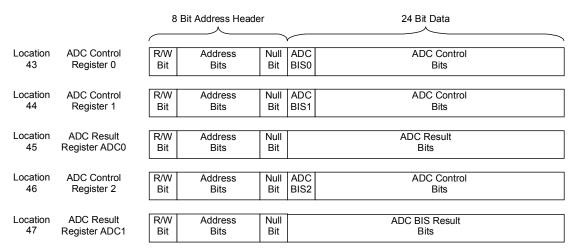

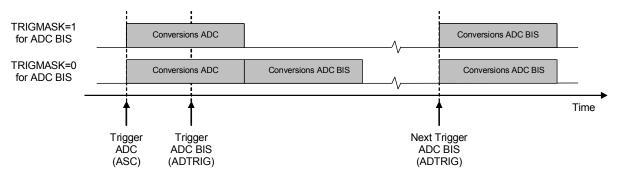

## 3.3.4 ADC Resource Sharing and Arbitration

The ADC convertor and its control is based on a single ADC convertor core with the possibility to store two requests and their results. There are 3 main operating modes for the arbitration control which are set via the ADCSEL[1:0] bits, see Table 3-5. These bits are located in the "Arbitration Peripheral Audio" register which is only accessible via the primary SPI. These bits are set at startup and are not to be re-configured dynamically during phone operation.

MC13783 User's Guide, Rev. 3.8

3-4 Freescale Semiconductor

| Table 3-5. ADC Arbitration Control | <b>Table</b> | 3-5. | <b>ADC</b> | <b>Arbitration</b> | Control |

|------------------------------------|--------------|------|------------|--------------------|---------|

|------------------------------------|--------------|------|------------|--------------------|---------|

| ADCSEL1 | ADCSEL0 | Arbitration Control                                                                                             |

|---------|---------|-----------------------------------------------------------------------------------------------------------------|

| 0       | 0       | Primary SPI can queue a single ADC conversion request. Secondary SPI can queue a single ADC conversion request. |

| 0       | 1       | Primary SPI can queue two ADC conversion requests.<br>Secondary SPI has no ADC access.                          |

| 1       | 0       | Primary SPI has no ADC access.<br>Secondary SPI can queue two ADC conversion requests.                          |

| 1       | 1       | Will give same operating mode as for ADCSEL[1:0]=00.                                                            |

See Chapter 9, "ADC Subsystem" for more details.

#### 3.3.5 Peripheral Resource Sharing

The Charger, USB transceiver, RTC and LED drivers are by default controlled by the primary SPI but can be assigned by the primary SPI to the secondary SPI via the CHRGSEL, USBSEL, RTCSEL and the BLLEDSEL, TCLEDSEL and ADAPTSEL bits. Only the RTC registers TIME and DAY will always provide read access to both SPI busses, all other listed registers provide write and read for only one of the two SPI busses. The SPI bus which does not have control can still write, but this will have no effect on the operation of the IC. The non controlling SPI will read its own written data.

Bit Description **Bits Concerned RTCSEL** Reg 20, 21, 22, 23 USBSEL Reg 49 0 = Primary SPI has write access only, Reg 50, bits 0-8 both SPIs have read access **CHRGSEL** Reg 48 1 = Secondary SPI has write access only, BLLEDSEL Reg 51, bits 0-9 both SPIs have read access Reg 53 **TCLEDSEL** Reg 51, bits 17-23 Reg 52, 54, 55, 56 Reg 51, bits 10-16 ADAPTSEL

**Table 3-6. Peripheral Arbitration Control**

## 3.3.6 Semaphore Bits

The MC13783 provides a semaphore register through which the processors can communicate with each other via their respective SPI busses without using the inter processor communication bus. An interrupt mechanism is added to this to allow for selective interrupts based on the contents of the semaphore register.

The semaphore registers for the primary and secondary SPI are set up according to Table 3-7.

#### **Programmability**

**Table 3-7. Semaphore Bits**

| Primary SPI   | Secondary SPI | Description                                |

|---------------|---------------|--------------------------------------------|

| SEM1CTRLA     | SEM2CTRLA     | Control bit for semaphore word A           |

| SEM1CTRLB     | SEM2CTRLB     | Control bit for semaphore word B           |

| SEM1WRTA[3:0] | SEM2WRTA[3:0] | Writable semaphore word A                  |

| SEM1WRTB[5:0] | SEM2WRTB[5:0] | Writable semaphore word B                  |

| SEM2RDA[3:0]  | SEM1RDA[3:0]  | Readable semaphore word A of the other SPI |

| SEM2RDB[5:0]  | SEM1RDB[5:0]  | Readable semaphore word B of the other SPI |

Via each SPI a processor can write to the SEMxWRTy semaphore words while it can read on its own SPI bus via the SEMxRDy words the contents of the semaphore words as written by the other SPI to its SEMxWRTy words. An interrupt bit SEMAFI is set and the processor is interrupted based on the comparison of the data in the semaphore words. The comparison mechanism is set via the SEMxCTRLy bits. If the SEMAFM bit is set, the interrupt is not generated. There is no semaphore sense bit.

There are two modes of comparison possible via the SEMxCTRLy bit setting. If set to 0 then the contents of words are compared and an interrupt is generated when both words become identical or if they were identical but become different. If set to 1 then a mask is applied for a bit to bit comparison and an interrupt is generated when one of the bits change state. The comparison modes for the A and B words can be set the same or differently.

Word comparison example: Suppose the processor at the secondary SPI writes to SEM2WRTA[3:0] its internal state during startup. Starting from 0000 it goes up to 1011. When reaching an intermediate state 0111 the primary processor has to take a specific action so that the secondary processor can continue its startup procedure. To do so, the processor at the primary SPI sets SEM1CTRLA=0 and programs the comparison word to SEM1WRTA[3:0]=0111. At the moment the secondary SPI writes SEM2WRTA[3:0]=0111 an interrupt is generated. The primary SPI can read SEM2RDA[3:0] to verify this is true and take the specific action.

Bit comparison example: Suppose the processor at the secondary SPI needs to know if one out of five shared resources is being used by the other processor and cannot go through the inter processor communication bus for that. To do so, the processor at the secondary SPI sets SEM2CTRLB=1 and programs the comparison word to SEM2WRTB[5:0]=011111, with SEM2WRTB0 stands for the resource one, SEM2WRTB1 for resource two, etc. At the moment the processor at the primary SPI starts using resource 3, resource 4 was already in use, it writes SEM1WRTB[5:0]=001100, and an interrupt is generated to the other processor. If it frees up resource three it can program SEM1WRTB[5:0]=001000 which again will generate an interrupt.

When starting from default but with the SEMAFM bit cleared, any change to the semaphore register by one SPI will result in an interrupt to the other SPI because by default the word comparison is active.

## 3.4 Interrupt Handling

#### **3.4.1** Control

The MC13783 has interrupt generation capability to inform the system on important events occurring. Interrupts are handled independently for both SPI busses. An interrupt is signaled to the processors connected to the primary SPI and the secondary SPI by driving the PRIINT respectively the SECINT line high.

Each interrupt is latched so that even if the interrupt source becomes inactive, the interrupt will remain active until cleared. Each interrupt can be cleared by a SPI bus by writing a 1 to the appropriate bit in the Interrupt Status register, this will also cause the interrupt line to go low for that SPI bus. If a new interrupt occurs while the processor clears an existing interrupt bit, the interrupt line will remain high. Clearing an interrupt bit on one SPI bus will not clear the interrupt bit on the other SPI bus.

Each interrupt can be masked by setting the corresponding mask bit to a 1. As a result, when the interrupt bit goes high, the interrupt line will not go high. However, even when the interrupt is masked, the interrupt source can still be read from the Interrupt Status register. This gives the processor the option of polling for status from the MC13783. The MC13783 powers up with all interrupts masked, so the processor must initially poll the MC13783 to determine if any interrupts are active. Alternatively, the processor can later unmask the interrupt bits of interest. If the related interrupt bit was already high, the interrupt line will go high after the unmasking. All mask bits labeled as reserved in the SPI bitmap do default to a 1 and must not be programmed to 0. Each SPI bus has its own independent set of mask bits.

The MC13783 sense registers contain status and input sense bits. These bits provide information to the processor about specific MC13783 I/O, power on inputs and power up sources. They only represent the current status of the sources, and thus are not latched, and are not clearable. The values in this register are read only. The contents of the primary SPI and secondary SPI status registers are strictly identical.

## 3.4.2 Bit Summary

Table 3-8 summarizes all interrupt, mask and sense bits. Although the polarity of the sense bits is given, for the accurate behavior of the sense bits the related chapter has to be consulted. For the applied debounce timing per interrupt, see the related chapters.

| Interrupt   | Mask        | Sense   | Used for / Sense Bit Polarity                               | Trigger | Chapter |

|-------------|-------------|---------|-------------------------------------------------------------|---------|---------|

| ADCDONEI    | ADCDONEM    | _       | ADC has finished requested conversions                      | L2H     | 9       |

| ADCBISDONEI | ADCBISDONEM | _       | ADCBIS has finished requested conversions                   | L2H     | 9       |

| TSI         | TSM         | _       | Touchscreen wake up                                         | Dual    | 9       |

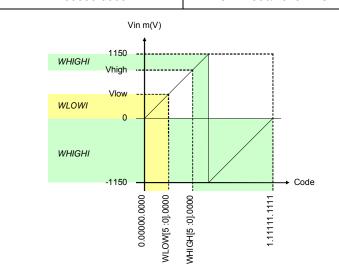

| WHIGHI      | WHIGHM      | _       | ADC reading above high limit                                | L2H     | 9       |

| WLOWI       | WLOWM       | _       | ADC reading below low limit                                 | L2H     | 9       |

| CHGDETI     | CHGDETM     | CHGDETS | Charger attach and removal<br>Sense is 1 if above threshold | Dual    | 8       |

Table 3-8. Interrupt, Mask and Sense Bits

MC13783 User's Guide, Rev. 3.8

Freescale Semiconductor

3-7

#### Programmability

#### Table 3-8. Interrupt, Mask and Sense Bits (continued)

| Interrupt | Mask      | Sense     | Used for / Sense Bit Polarity                                          | Trigger | Chapter |

|-----------|-----------|-----------|------------------------------------------------------------------------|---------|---------|

| CHGOVI    | CHGOVM    | CHGOVS    | Charger over voltage detection<br>Sense is 1 if above threshold        | Dual    | 8       |

| CHGREVI   | CHGREVM   | CHGREVS   | Charger path reverse current<br>Sense is 1 if current flows into phone | L2H     | 8       |

| CHGSHORTI | CHGSHORTM | CHGSHORTS | Charger path short circuit Sense is 1 if above threshold               | L2H     | 8       |

| CCCVI     | CCCVM     | cccvs     | Charger regulator operating mode<br>Sense is 1 if voltage regulation   | Dual    | 8       |

| CHGCURRI  | CHGCURRM  | CHGCURRS  | Charge current below threshold<br>Sense is 1 if above threshold        | H2L     | 8       |

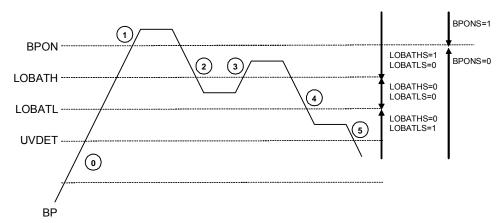

| BPONI     | BPONM     | BPONS     | BP turn on threshold detection<br>Sense is 1 if above threshold        | L2H     | 5       |

| _         | _         | _         | End of life / low battery detect                                       | _       | 5       |

| LOBATLI   | LOBATLM   | LOBATLS   | Sense is 1 if end of life detected                                     | L2H     | _       |

| _         | _         | _         | Sense is 1 if below low battery threshold                              | _       | _       |

| LOBATHI   | LOBATHM   | LOBATHS   | Low battery warning<br>Sense is 1 if above threshold                   | Dual    | 5       |

| USBI      | USBM      | USB4V4S   | USB 4V4 detect<br>Sense is 1 if above threshold                        | Dual    | 10      |

| _         | _         | USB2V0S   | USB 2V0 detect<br>Sense is 1 if above threshold                        | Dual    | 10      |

| _         | _         | USB0V8S   | USB 0V8 detect<br>Sense is 1 if above threshold                        | Dual    | 10      |

| UDPI      | UDPM      | UDPS      | UDP detect<br>Sense is 1 if pin is high                                | L2H     | 10      |

| UDMI      | UDMM      | UDMS      | UDM detect<br>Sense is 1 if pin is high                                | L2H     | 10      |

| IDI       | IDM       | IDFLOATS  | USB ID Line detect<br>Sense bits are coded, see related chapter        | Dual    | 10      |

| _         | _         | IDGNDS    | _                                                                      | _       | _       |

| SE1I      | SE1M      | SE1S      | Single ended 1 detect<br>Sense is 1 if detected                        | Dual    | 10      |

| CKDETI    | CKDETM    | CKDETS    | Carkit detect<br>Sense is 1 if detected                                | L2H     | 10      |

| MC2BI     | MC2BM     | MC2BS     | Microphone bias 2 detect<br>Sense is 1 if detected                     | Dual    | 7       |

| HSDETI    | HSDETM    | HSDETS    | Headset attach<br>Sense is 1 if attached                               | Dual    | 7       |

| HSLI      | HSLM      | HSLS      | Stereo headset detect<br>Sense is 1 if detected                        | L2H     | 7       |

3-8 Freescale Semiconductor

Table 3-8. Interrupt, Mask and Sense Bits (continued)

| Interrupt | Mask      | Sense     | Used for / Sense Bit Polarity                                     | Trigger | Chapter |

|-----------|-----------|-----------|-------------------------------------------------------------------|---------|---------|

| ALSPTHI   | ALSPTHM   | ALSPTHS   | Thermal shutdown Alsp<br>Sense is 1 if above threshold            | L2H     | 7       |

| AHSSHORTI | AHSSHORTM | AHSSHORTS | Short circuit on Ahs outputs<br>Sense is 1 if detected            | L2H     | 7       |

| 1HZI      | 1HZM      | _         | 1 Hz timetick                                                     | L2H     | 4       |

| TODAI     | TODAM     | _         | Time of day alarm                                                 | L2H     | 4       |

| ONOFD1I   | ONOFD1M   | ONOFD1S   | ON1B event<br>Sense is 1 if pin is high                           | Dual    | 5       |

| ONOFD2I   | ONOFD2M   | ONOFD2S   | ON2B event<br>Sense is 1 if pin is high                           | Dual    | 5       |

| ONOFD3I   | ONOFD3M   | ONOFD3S   | ON3B event<br>Sense is 1 if pin is high                           | Dual    | 5       |

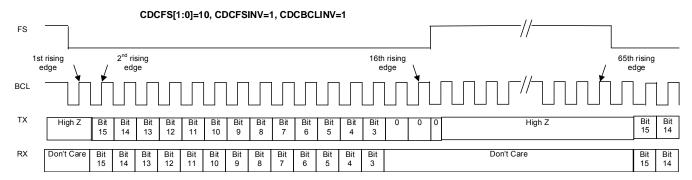

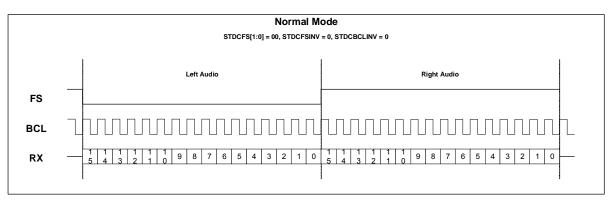

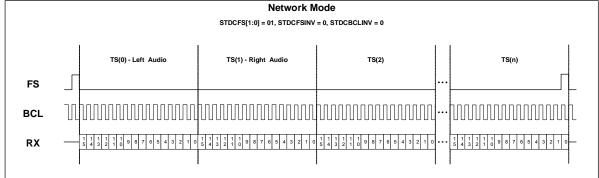

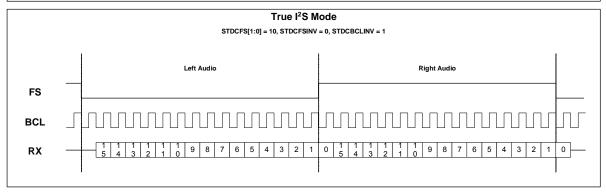

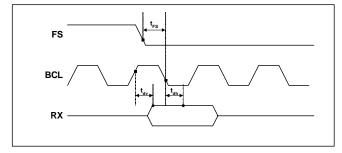

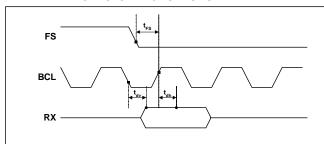

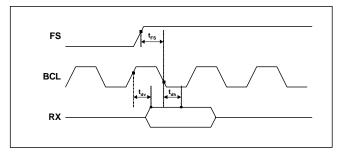

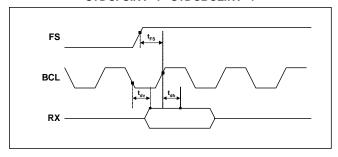

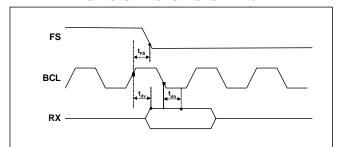

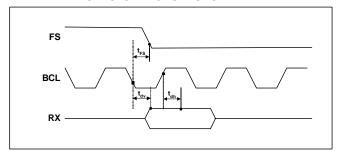

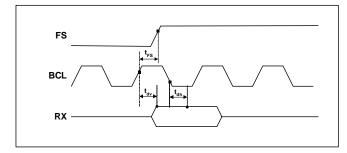

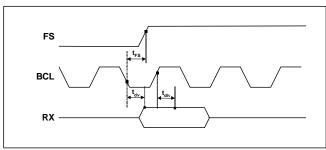

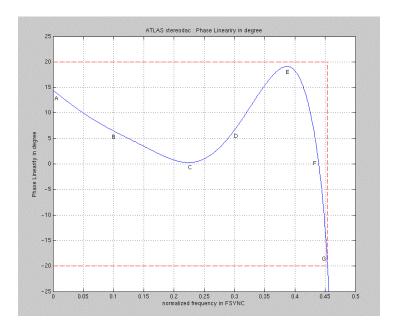

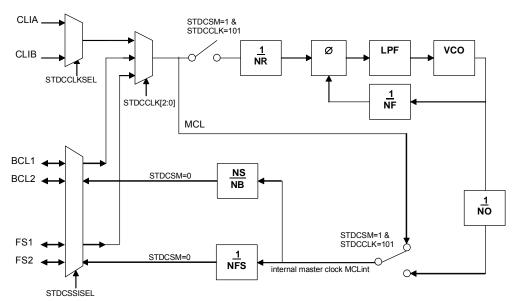

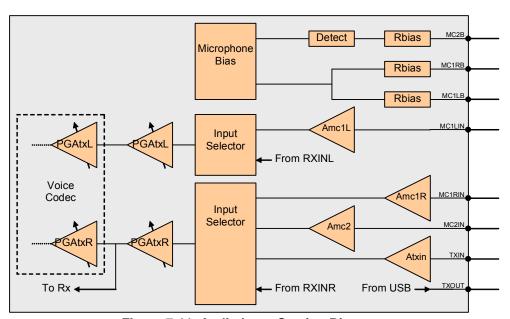

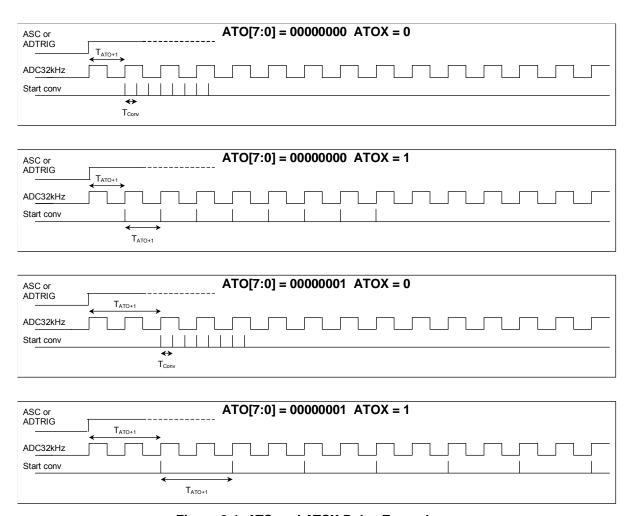

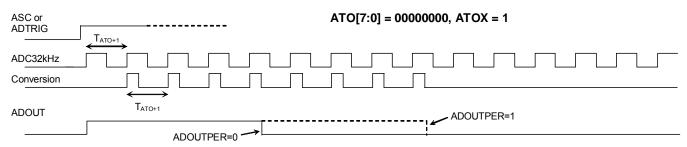

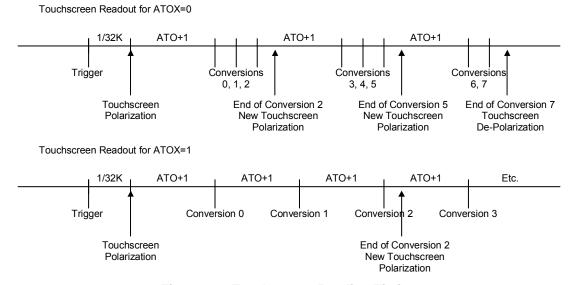

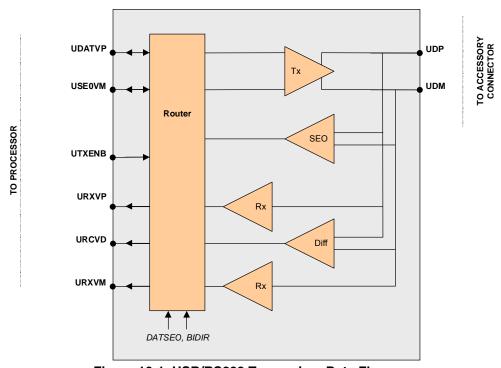

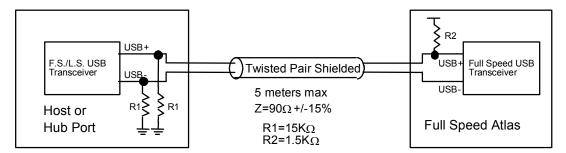

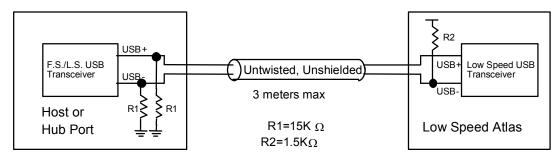

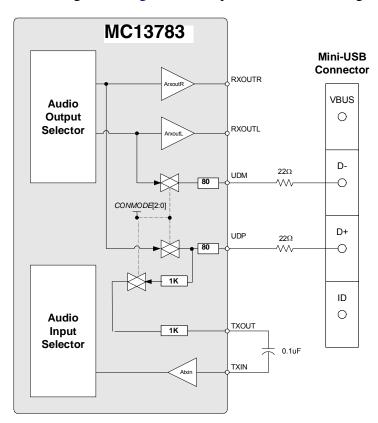

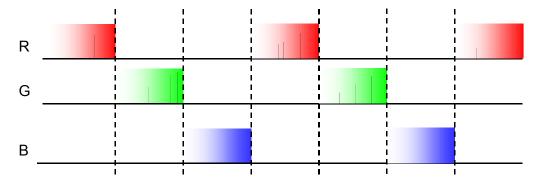

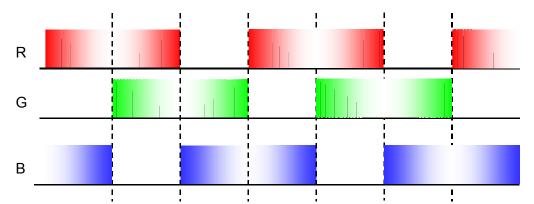

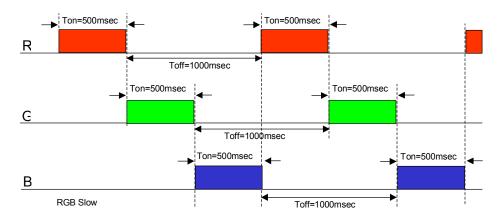

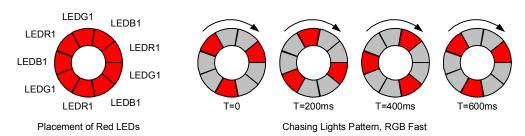

| SYSRSTI   | SYSRSTM   | _         | System reset                                                      | L2H     | 5       |