# Sandpoint Reference Platform Errata

| <b>Board Revision Level</b> | X2 |

|-----------------------------|----|

| Errata Revision Level       | G  |

$\odot$  Copyright 1999 by Motorola Incorporated. All rights reserved.

## **Revision History**

| Version | <u>Date</u> | Changes                                                          |

|---------|-------------|------------------------------------------------------------------|

| А       | 1999 Feb 17 | Initial errata.                                                  |

| В       | 1999 Feb 24 | Updated power errata; slots                                      |

|         | 1999 Apr 20 | Test clock errata noted; no change to revision.                  |

| С       | 1999 May 20 | Add IDSEL rework.                                                |

| D       | 1999 Jun 18 | PPMC issues; cleanup.                                            |

| E       | 1999 Aug 10 | Added 64-bit slot issues.                                        |

| F       | 1999 Oct 28 | IOCS16* and IDE issue.                                           |

| G       | 1999 Nov 04 | Errata #7 revised not optional, it is mandatory for COP support. |

### Table 1: Summary of Sandpoint Errata

| # | Туре           | Problem                                                                                                                                                         | Impact                                                                                                                                                                                  | Work-Around                                                                                                                                                                                                                                                                                                              | Affects | Rev |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 1 | CAD            | The placement of all the slots is incor-<br>rect. The expected order, from the PMC<br>outward is: 1, 2, 3, 4.<br>The actual order is: 2, 1, 4, 3.               | Slots misidentified. This is signifi-<br>cant for operating modes 3&4,<br>which treat slot 4 specially; and for<br>some OSes which expect an ether-<br>net card in slot 2 specifically. | Re-label slots and modify documentation.<br>For X3: reposition slots.                                                                                                                                                                                                                                                    | X2      | A   |

| 2 | Design         | The Winbond PCIRST* signal conflicts<br>with the PCIRST* signal from the reset<br>controller.                                                                   | Possible chip damage or loss of s/w reset capability.                                                                                                                                   | <ul><li>Lift pin 22 of U8. This prevents the Winbond from asserting software reset.</li><li>For X3: route Winbond PCIRST through PAL merge logic.</li></ul>                                                                                                                                                              | X2      | A   |

| 3 | CAD/<br>Design | The VSB filter capacitor is placed too far<br>from the header and SuperI/O part.                                                                                | Cannot turn power on with switches.                                                                                                                                                     | <ul> <li>On the bottom of the board, under J23<br/>(ATX power connector) attach a capaci-<br/>tor between pins 7 (GND) and pin 9<br/>(VSTBDY).</li> <li>Capacitor value may be 1.0uF Non-pol to<br/>33uF tantalum (value is not critical).</li> <li>For X3: Move capacitor closer to power<br/>supply header.</li> </ul> | X2      | В   |

| 4 | Design         | The test clock jumper select does not<br>work.<br>The test clock jumper grounds<br>TCLK_SEL, which has an internal pull-<br>down, so the jumper changes nothing | Cannot supply test clocks.                                                                                                                                                              | <ol> <li>Connect a jumper from J33 pin 1 to J34<br/>pin 1 when using an external clock, if no<br/>jumper is used in J34. Alternately con-<br/>nect to J29 pin 26 (chassis header) or<br/>any available 3.3V power point.</li> <li>For X3: Connect TCLK_SEL to +3.3V or<br/>change to pulldown.</li> </ol>                | X2      | В   |

### Table 1: Summary of Sandpoint Errata

| # | Туре                                        | Problem                                                                                                                                                                                                                                                                                                                                                   | Impact                                                  | Work-Around                                                                                                                                                                                                                                                                                 | Affects | Rev |

|---|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 5 | Spec<br>issue                               | If the MPC8240 or MPC107, as a PCI master/host, issues a configuration cycle which results in its own IDSEL being asserted, will hang or behave erratically.                                                                                                                                                                                              | System failure.                                         | <ul> <li>SW:<br/>On Sandpoint systems, do not issue configuration cycles to device 12.</li> <li>HW: <ol> <li>Remove R71</li> <li>Connect wire from R71 pad (nearest J12) to J12 pin 21.</li> </ol> </li> <li>For X3: If SYSCON asserted, disconnect AD12 from IDSEL on PMC slot.</li> </ul> | X2      | С   |

| 6 | PPMC<br>Spec<br>changes                     | PPMC VITA spec changes propose that<br>PCI arbitration be removed.                                                                                                                                                                                                                                                                                        | Incompatible in mode 0/1.                               | Do not install VITA-compatible PPMC<br>boards on Sandpoint or vice-versa.<br>For X3: Allow PCI arbitration separately<br>from interrupt/SYSCON selection.<br>Another switch?                                                                                                                | X2      | D   |

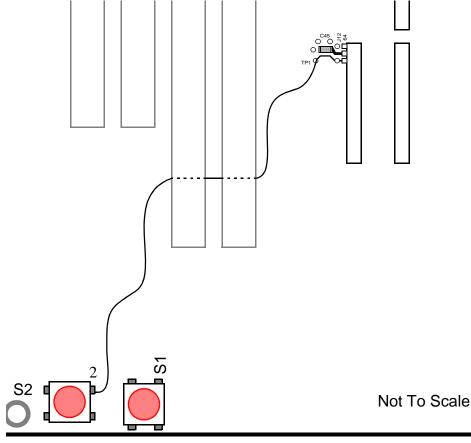

| 7 | PPMC<br>Spec<br>changes<br>/ COP<br>failure | PPMC VITA spec changes propose that<br>system that PPMCs may reset the target<br>system by asserting J2-60 low.<br>COP debuggers expect to be able to reset<br>the target system. In addition, the Win-<br>bond may lock up if a PCI transaction is<br>interrupted by resetting only the PCI<br>master (MPC8240 or MPC107) and not<br>the Winbond target. | COP debuggers may not be able to control target system. | <ul> <li>1.Connect a wire from TP1 (near PMC connector J12 pin 60) to Reset switch S2 (near chassis header) pin 2 (pin 2 is directly opposite pin 1, on a square pad).</li> <li>For X3: Merge J2-60 with on-board reset logic in the PAL.</li> </ul>                                        | X2      | G   |

| 8 | Cleanup                                     | Hard to configure, switches all over the place.                                                                                                                                                                                                                                                                                                           | None                                                    | <ul> <li>None.</li> <li>For X3:</li> <li>1. Replace scattered slide switches with SMT DIP switches.</li> <li>2. Use PAL to invert INT selectively.</li> </ul>                                                                                                                               | X2      | D   |

### Table 1: Summary of Sandpoint Errata

| #  | Туре   | Problem                                                                                                                                                                                | Impact                                                                                                                                                                               | Work-Around                                                                                                                                                                                                                                              | Affects | Rev |

|----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 9  | Design | The 64-bit PCI slots are wired and keyed<br>for 3.3V operation, but the Sandpoint is<br>a 5V environment. The slots should have<br>been univerally keyed and VIO con-<br>nected to 5V. | Cards used in 64-bit PCI slots must<br>operate at 3.3V and tolerate 5V sig-<br>nalling (from the Winbond and<br>PMC).<br>Cards which cannot tolerate 5V sig-<br>nals may be damaged. | <ul> <li>Use only universal cards in the 64-bit<br/>slots. Universal PCI cards have two<br/>notches cut into the gold-plated connec-<br/>tor area.</li> <li>For X3:</li> <li>1. Connect VIO to 5V.</li> <li>2. Change slot type to universal.</li> </ul> | X2      | E   |

| 10 | Design | IOCS16* is connected to the IDE disk drives. This can cause system failures under heavy interrupt loads.                                                                               | IDE disk activity during interrupt activity may cause hangs.                                                                                                                         | <ol> <li>Cut IOCS16* to IDE disks and connect<br/>to ground. See detailed drawing.</li> <li>For X3: permanent connection.</li> </ol>                                                                                                                     | X2      | F   |

### Errata 7: Target System Reset

#### **Overview:**

COP in-circuit emulators may not be able to reliably gain control of the target system if the reset command issued to the PPMC card does not also reset the motherboard (Sandpoint). The cause is apparently due to interrupting a PCI transaction the Winbond before completion. If the Winbond is not reset, the system will lock up until a global reset is issued.

The latest VITA specification has added a pin to the PPMC connector for just such a purpose. The rework adds this function.

(Note: Some older PPMC cards may also require some rework).

Work-arounds:

The work-around is to connect the new SYSRST\* function to the reset switch pin.

1. Connect a wire to pin 2 of S2 to pad TP1 (connects to J12 pin 60).

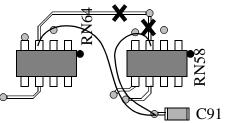

#### Errata 10: IDE IOCS16\* FIX

#### **Overview:**

The ISA signal IOCS16\* is connected to the IOCS16\* pin of the IDE disk drive cables. This can cause problems with interactions between the Winbond PIC and the IDE disk controller during periods of heavy interrupt activity, depending upon the nature and timing of interrupts.

The failure is intermittent but repeatable on certain OSs, the exact nature of the problem is under investigation.

#### Work-arounds:

The work-around is to permanently wire IOCS16\* to ground, putting the device in 16-bit transfer mode.

- 1. Cut trace between RN58 pin 3 and via.

- 2. Connect RN58 pin 3 to C91 left side or to via.

- 3. Cut trace between RN64 pin 3 and via.

- 4 Connect RN64 pin 3 to C91 left side or to via..

| J27<br>SECONDARY IDE |  |

|----------------------|--|

| PRMARY IDE           |  |