# QorlQ LS1046A BSP v0.4

# **Contents**

| Chapter 1 SDK Overview                                                               | 17 |

|--------------------------------------------------------------------------------------|----|

| 1.1 What's New in LS1046A BSP v0.4                                                   |    |

| 1.2 Components                                                                       |    |

| 1.3 Known Issues                                                                     |    |

| Chapter 2 Getting Started                                                            | 23 |

| 2.1 SDK File System Images                                                           |    |

| 2.1.1 fsl-image-minimal                                                              |    |

| 2.1.2 fsl-image-mfgtool                                                              |    |

| 2.1.3 fsl-image-full                                                                 |    |

| 2.1.4 fsl-image-core                                                                 |    |

| 2.1.5 fsl-image-virt                                                                 |    |

| 2.2 Essential Build Instructions                                                     | 25 |

| 2.2.1 Install the SDK                                                                | 25 |

| 2.2.2 Set Up Host Environment                                                        | 25 |

| 2.2.3 Setup Poky                                                                     |    |

| 2.2.4 Builds                                                                         |    |

| 2.3 Additional Instructions for Developers                                           |    |

| 2.3.1 Customize U-Boot                                                               |    |

| 2.3.2 Customize the Linux Kernel                                                     |    |

| 2.3.3 Build Native Packages                                                          | 29 |

| Chapter 3 Deploy U-Boot, Linux Kernel, and Root Filesys Reference Design Board (RDB) | 30 |

| 3.1 Introduction                                                                     | 30 |

| 3.2 Basic Host Set-up                                                                |    |

| 3.3 Supported Boards                                                                 |    |

| 3.3.1 LS1046ARDB                                                                     |    |

| 3.3.1.1 Overview                                                                     |    |

| 3.3.1.2 Switch Settings                                                              |    |

| 3.3.1.3 U-Boot Environment Variables                                                 |    |

| 3.3.1.3.1 U-Boot Environment Variable "hwconfig"                                     |    |

| 3.3.1.3.2 Configuring U-Boot Network Parameters                                      |    |

| 3.3.1.4 Frame Manager Microcode (FMan Ucode)                                         |    |

| 3.3.1.5 RCW (Reset Configuration Word) and Ethernet Interfaces                       |    |

| 3.3.1.6 System Memory Map                                                            |    |

| 3.3.1.7 Flash Bank Usage                                                             |    |

| 3.3.1.9 Deployment                                                                   |    |

| 3.3.1.9.1 FIT Image Deployment from TFTP                                             |    |

| 3.3.1.9.2 FIT Image Deployment from Flash                                            |    |

| 3.3.1.9.3 NFS Deployment                                                             |    |

| 3.3.1.9.4 SD Deployment                                                              |    |

| 3.3.1.9.5 QSPI Deployment                                                            |    |

| 3.3.1.10 Check 'Link Up' for Serial Ethernet Interfaces                              |    |

| 3.3.1.11 Basic Networking Ping Test                                                  |    |

| Chapter 4 System Recovery                                                                     | 56  |

|-----------------------------------------------------------------------------------------------|-----|

| 4.1 Environment Setup                                                                         |     |

| 4.1.1 Environment Setup (Common)                                                              | 56  |

| 4.2 Image Recovery                                                                            |     |

| 4.2.1 Recover system with already working U-Boot                                              | 56  |

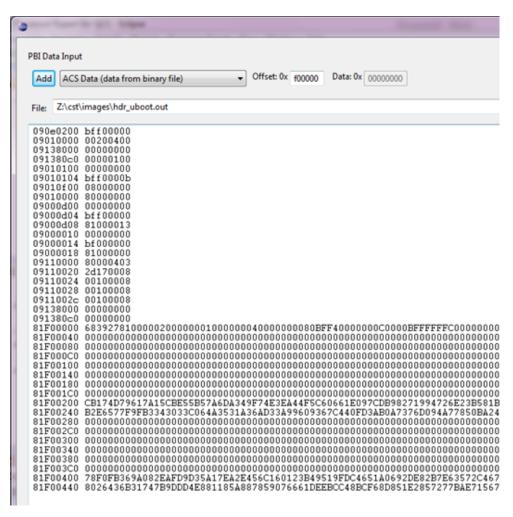

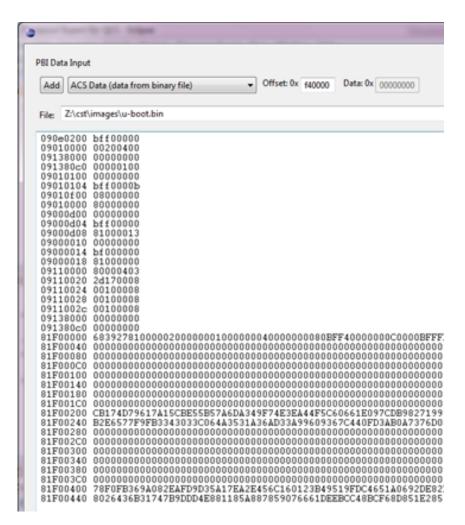

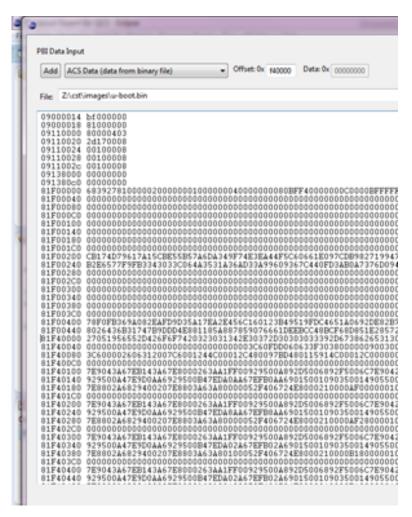

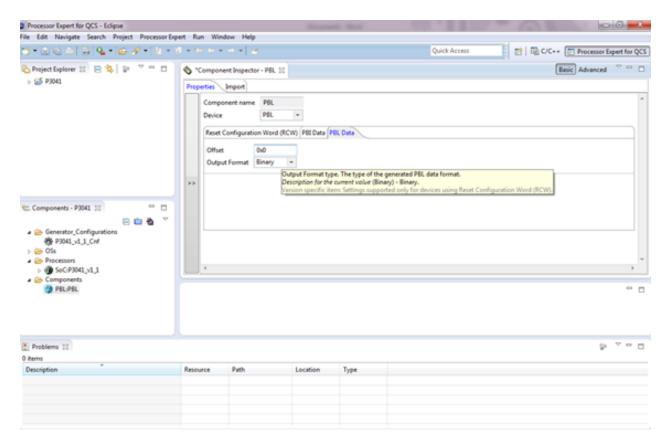

| 4.2.2 Recover system using CodeWarrior Flash Programmer                                       |     |

|                                                                                               |     |

| Chapter 5 Linux Kernel Drivers                                                                | 60  |

| 5.1 DMA Controller                                                                            | 60  |

| 5.1.1 Enhanced Direct Memory Access Driver (ARM)                                              | 60  |

| 5.1.1.1 eDMA User Manual                                                                      | 60  |

| 5.2 DPAA 1.x Devices                                                                          |     |

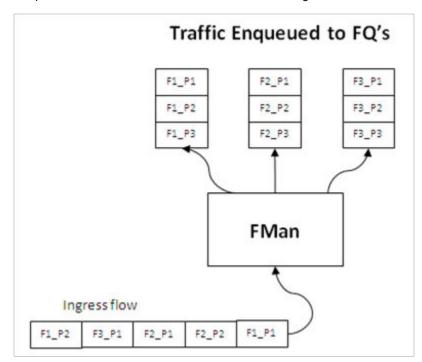

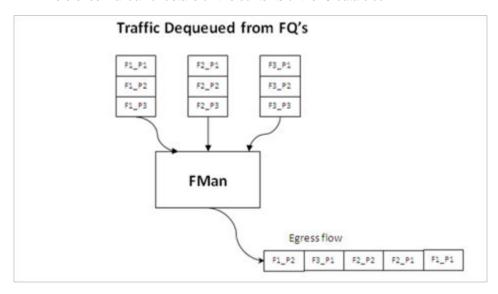

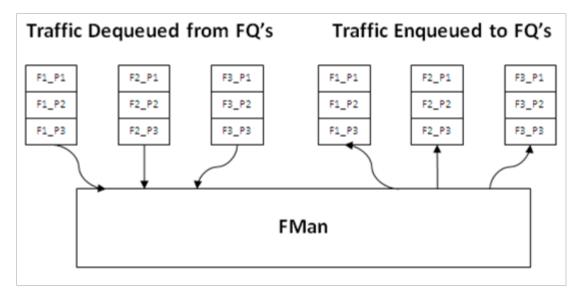

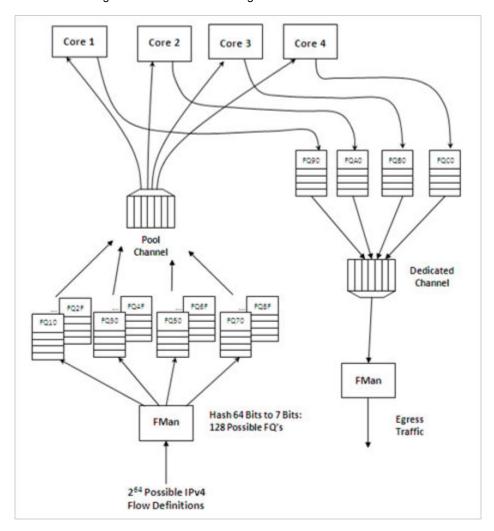

| 5.2.1 DPAA Primer for Software Architecture                                                   | 62  |

| 5.2.1.1 DPAA Primer                                                                           |     |

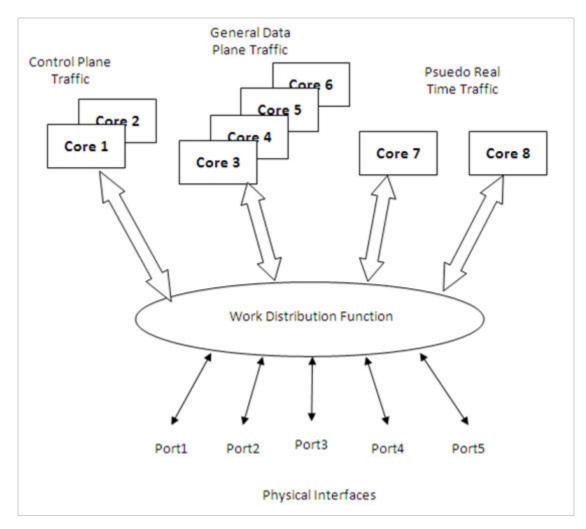

| 5.2.1.1.1 General Architectural Considerations                                                | 63  |

| 5.2.1.1.2 Multicore Design                                                                    |     |

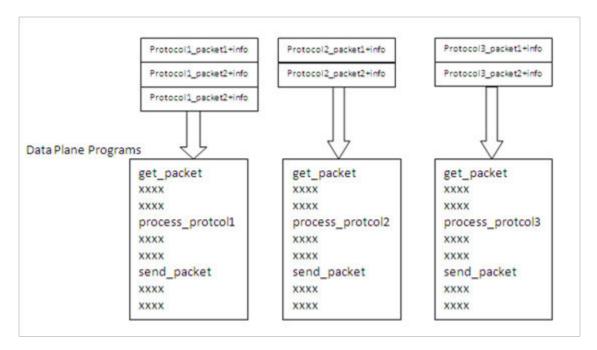

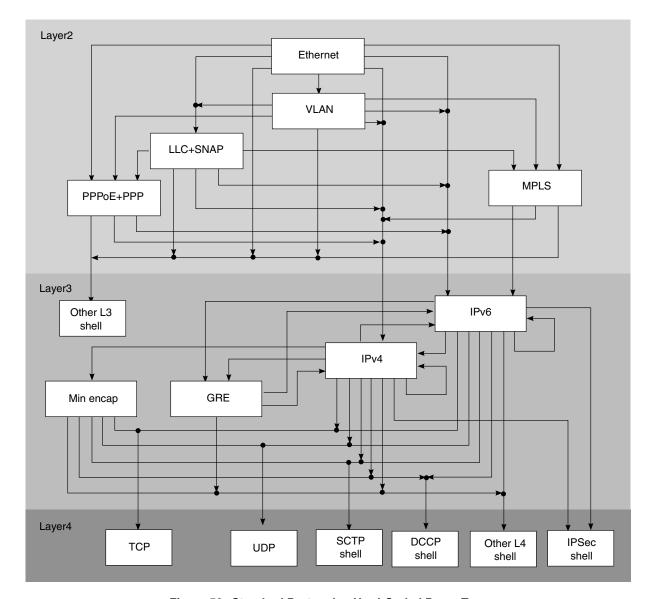

| 5.2.1.1.3 Parse/classification Software Offload                                               | 63  |

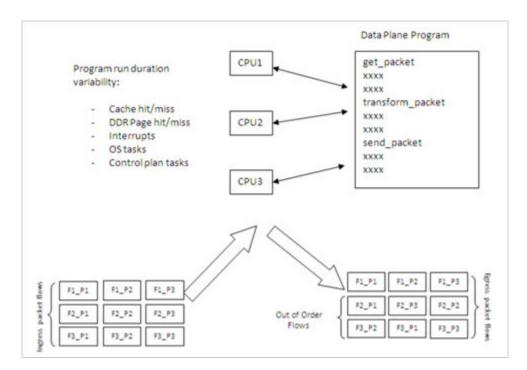

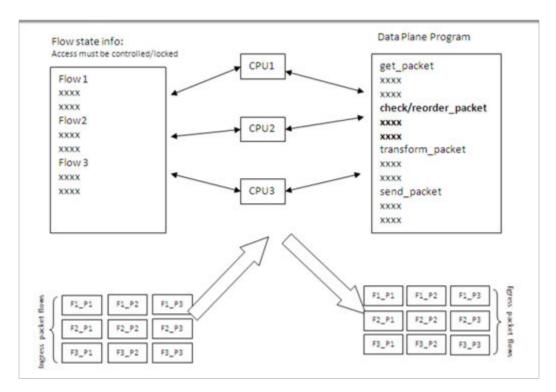

| 5.2.1.1.4 Flow Order Considerations                                                           | 64  |

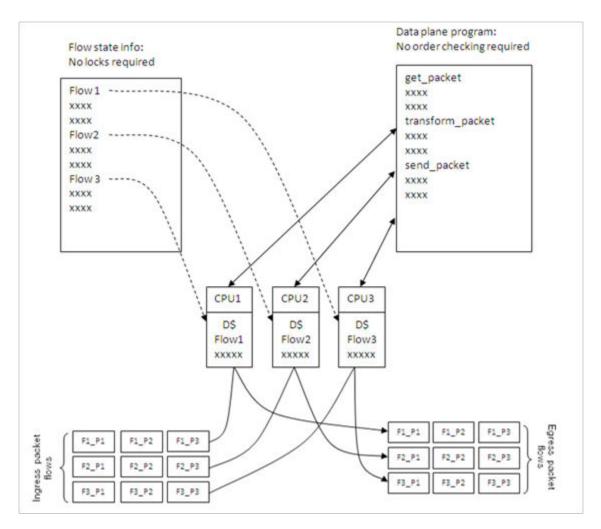

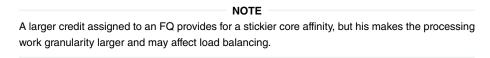

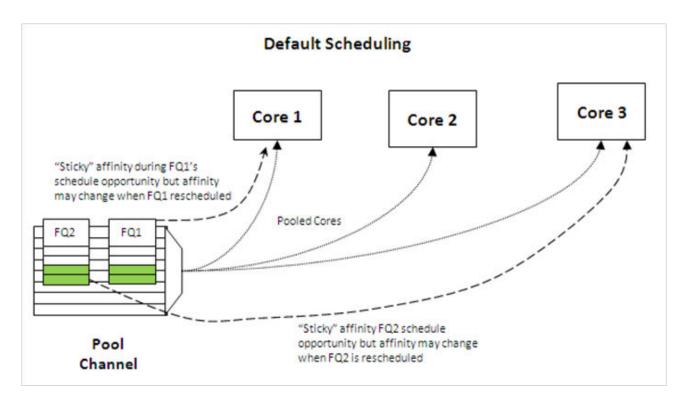

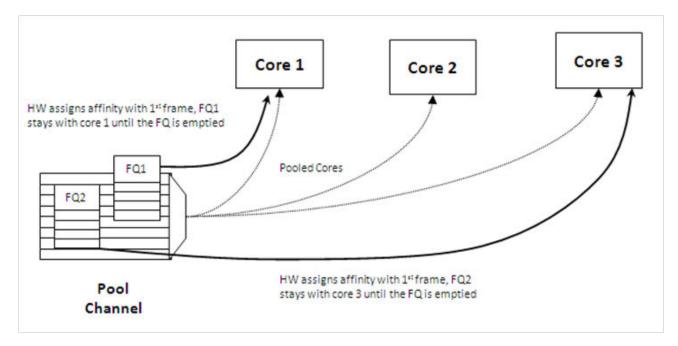

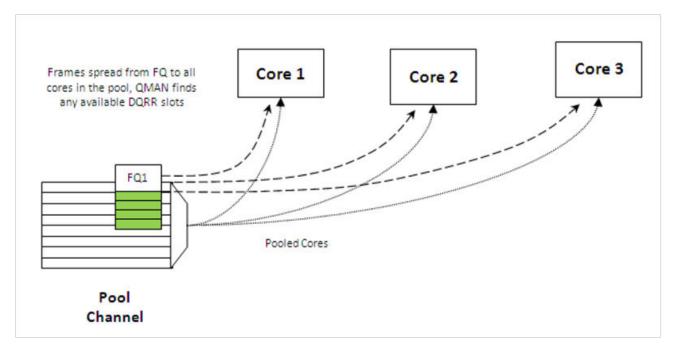

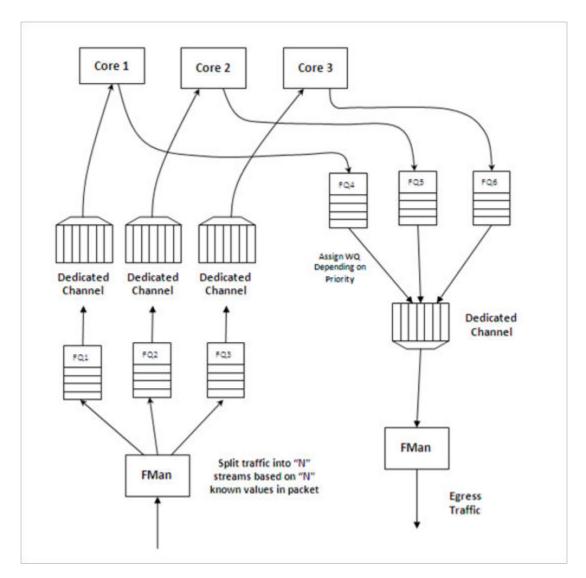

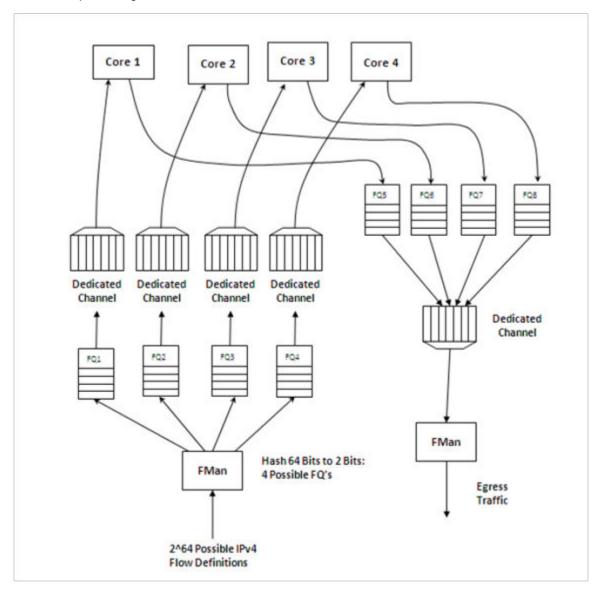

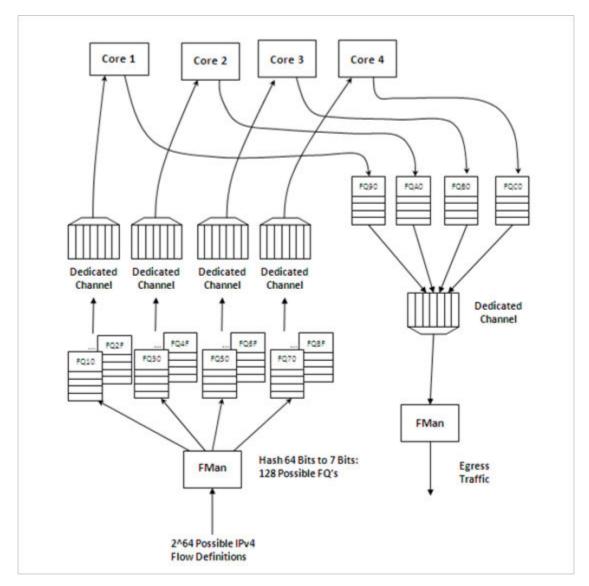

| 5.2.1.1.5 Managing Flow-to-Core Affinity                                                      | 66  |

| 5.2.1.2 DPAA Goals                                                                            | 67  |

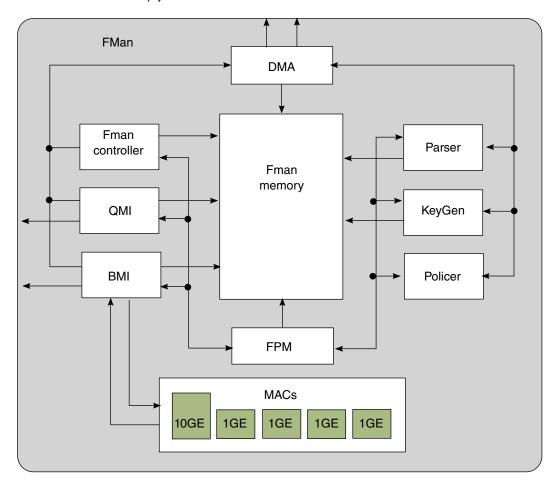

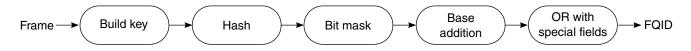

| 5.2.1.3 FMan Overview                                                                         | 68  |

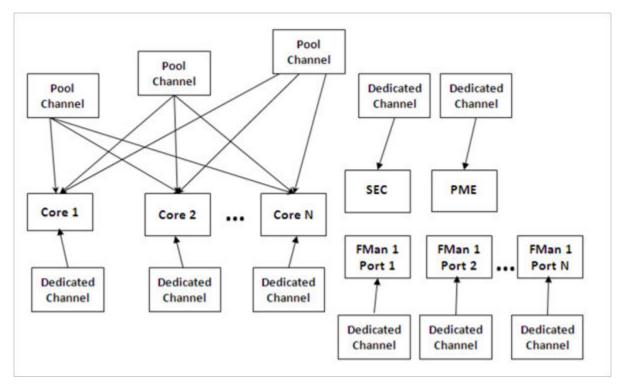

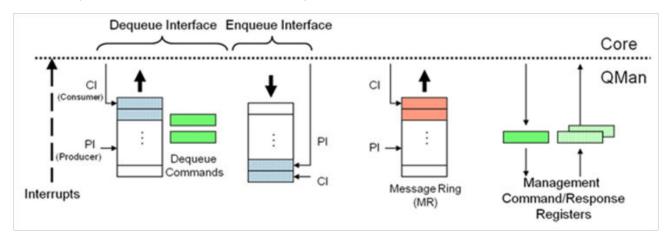

| 5.2.1.4 QMan Overview                                                                         | 70  |

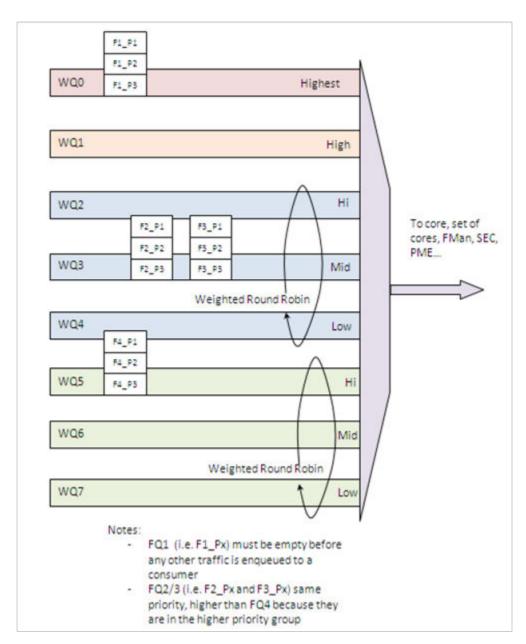

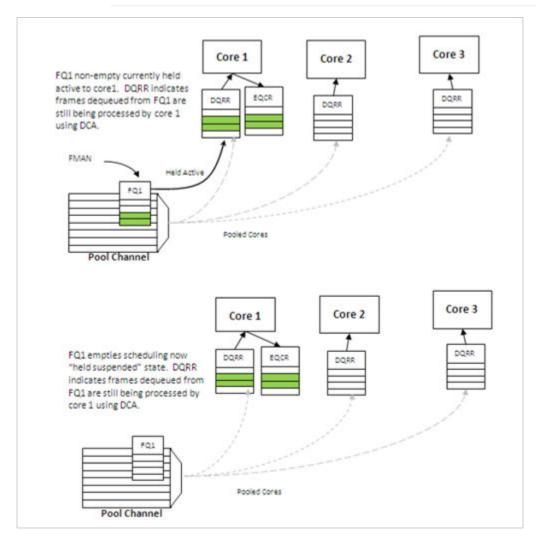

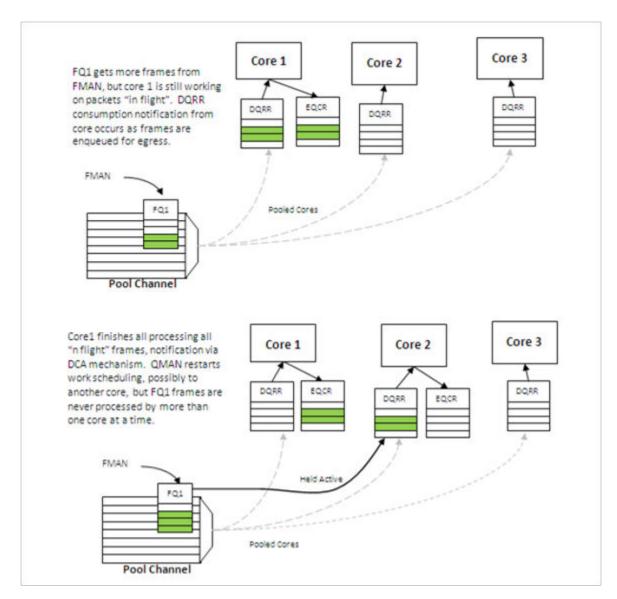

| 5.2.1.5 QMan Scheduling                                                                       | 75  |

| 5.2.1.6 BMan                                                                                  | 79  |

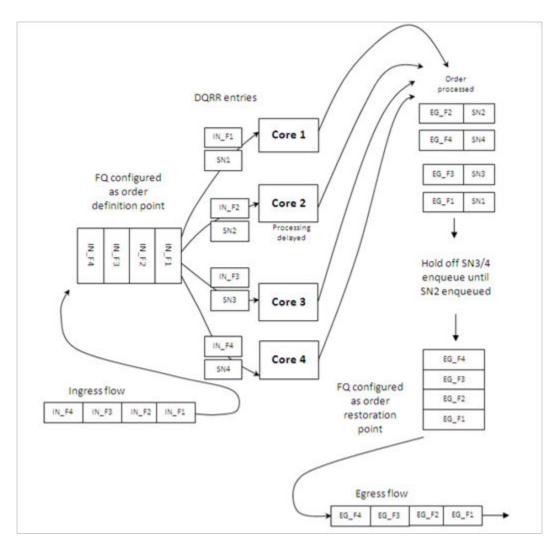

| 5.2.1.7 Order Handling                                                                        | 80  |

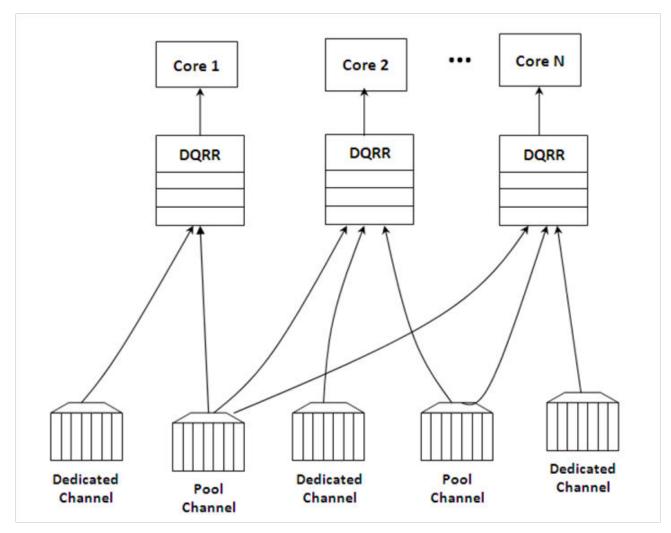

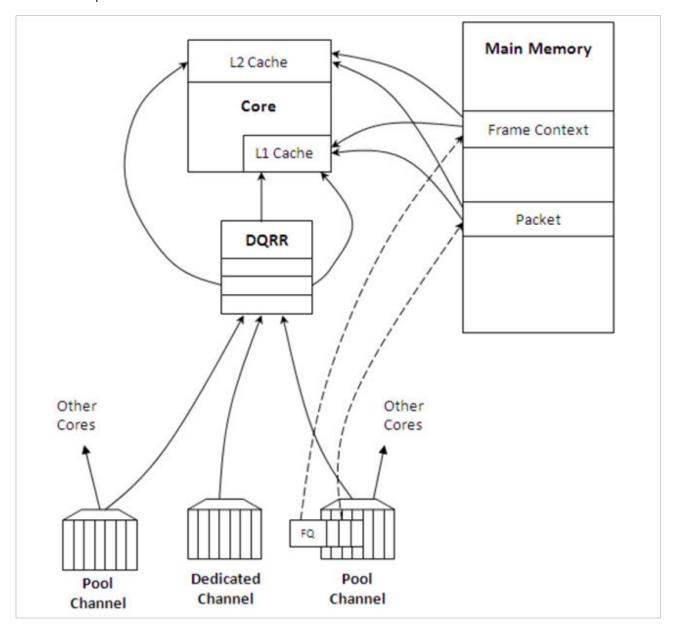

| 5.2.1.8 Pool Channels                                                                         | 83  |

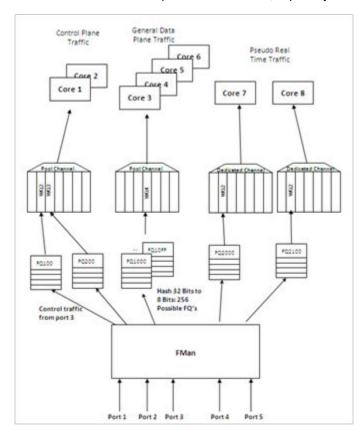

| 5.2.1.9 Application Mapping                                                                   | 87  |

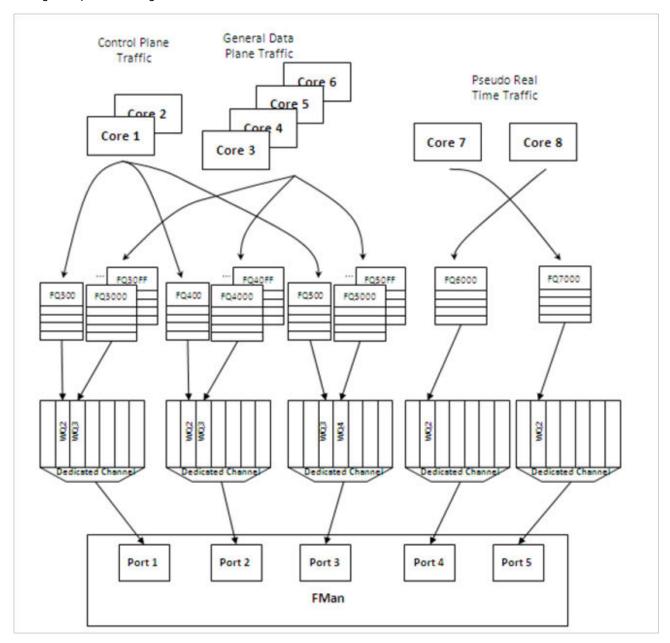

| 5.2.1.10 FQ/WQ/Channel                                                                        | 90  |

| 5.2.2 Queue Manager (QMan) and Buffer Manager (BMan)                                          | 93  |

| 5.2.2.1 QMan/BMan Drivers Release Notes                                                       | 93  |

| 5.2.2.2 QMan BMan API Reference Manual                                                        | 101 |

| 5.2.2.2.1 About this document                                                                 |     |

| 5.2.2.2.2 Introduction to the Queue Manager and the Buffer Manager                            | 101 |

| 5.2.2.2.3 Buffer Manager                                                                      |     |

| 5.2.2.2.4 BMan CoreNet portal APIs                                                            | 106 |

| 5.2.2.2.5 Queue Manager                                                                       |     |

| 5.2.2.2.6 QMan portal APIs                                                                    | 120 |

| 5.2.2.2.7 QMAN CEETM APIs                                                                     |     |

| 5.2.2.2.8 Other QMan APIs                                                                     | 152 |

| 5.2.2.2.9 USDPAA-specific APIs                                                                |     |

| 5.2.2.2.10 Sysfs and debugfs QMan/BMan interfaces                                             |     |

| 5.2.2.2.11 Error handling and reporting                                                       |     |

| 5.2.2.2.12 Operating system specifics                                                         |     |

| 5.2.3 Configuring DPAA Frame Queues                                                           |     |

| 5.2.3.1 Introduction                                                                          |     |

| 5.2.3.2 FMan Network interface Frame Queue Configuration                                      |     |

| 5.2.3.3 FMan network interface ingress FQs configuration                                      |     |

| 5.2.3.4 Ingress FQs common configuration guidelines                                           |     |

| 5.2.3.5 Dynamic load balancing with order preservation - ingress FQs configuration guidelines |     |

| 5.2.3.6 Dynamic load balancing with order restoration - ingress FQs configuration guidelines  |     |

| 5.2.3.7 Static distribution - Ingress FQs Configuration Guidelines                            |     |

| 5.2.3.8 FMan network interface egress FQs configuration                                       | 175 |

| 5.2.3.9 Accelerator Frame Queue Configuration.                      |     |

|---------------------------------------------------------------------|-----|

| 5.2.3.10 DPAA Frame Queue Configuration Guideline Summary           |     |

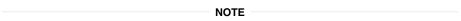

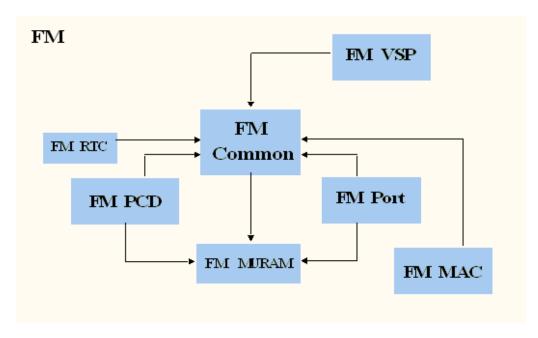

| 5.2.4 Frame Manager                                                 |     |

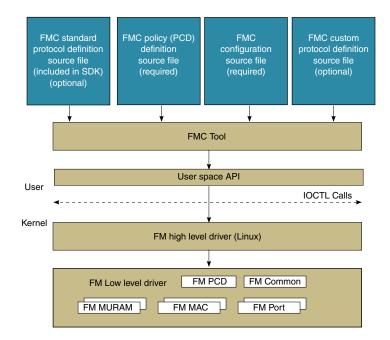

| 5.2.4.1 Frame Manager Linux Driver User Guide                       | 179 |

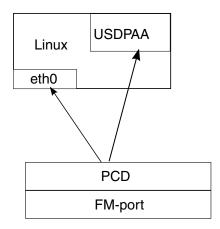

| 5.2.4.1.1 Introduction                                              |     |

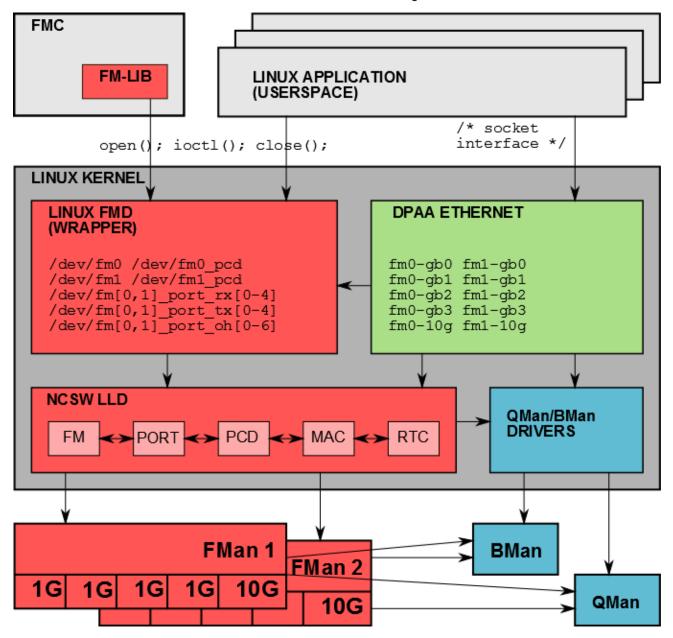

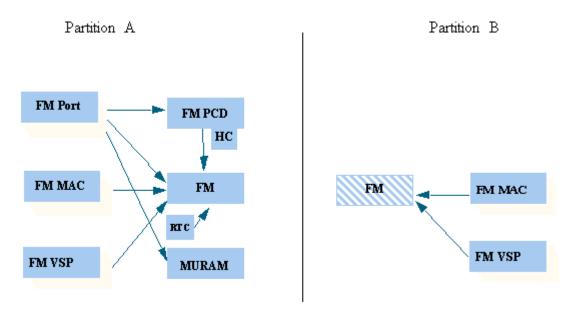

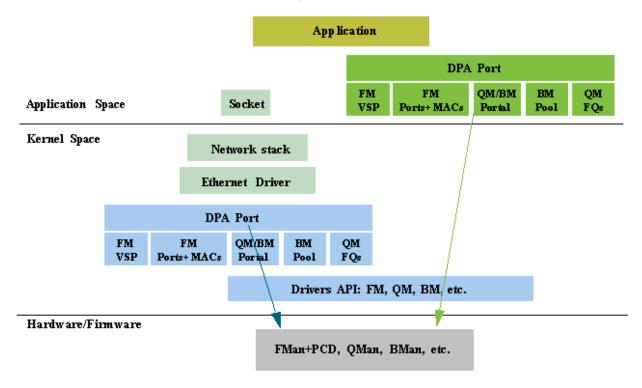

| 5.2.4.1.2 The Linux FMD Devices                                     | 181 |

| 5.2.4.1.3 Linux FMD Programming Model                               | 184 |

| 5.2.4.1.4 The Linux FMan Device                                     | 185 |

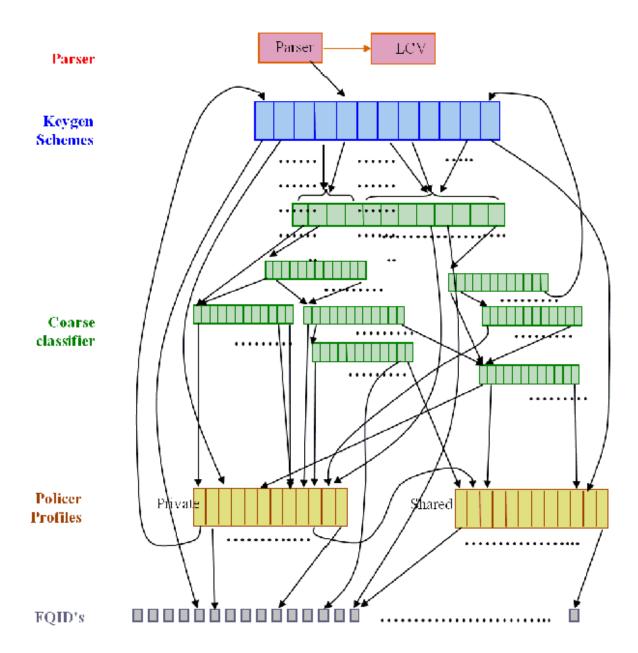

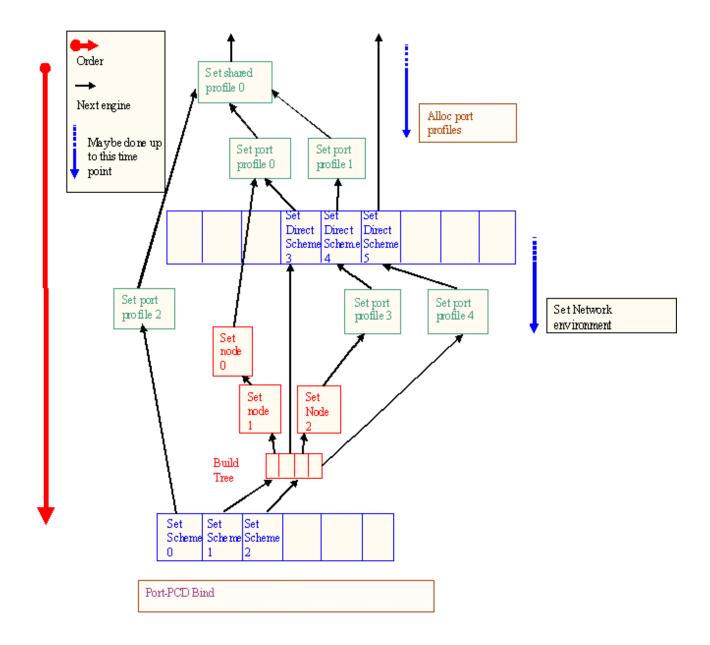

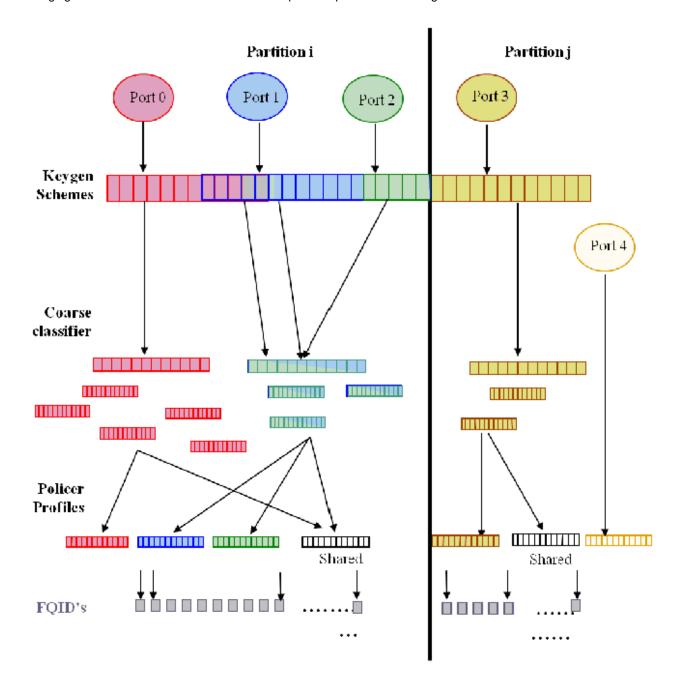

| 5.2.4.1.5 The Linux PCD Device                                      | 186 |

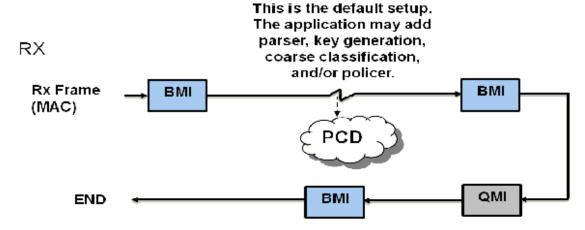

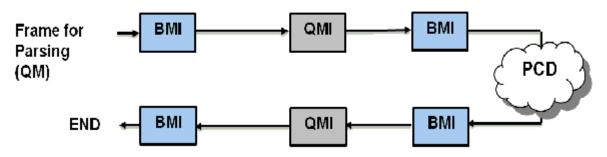

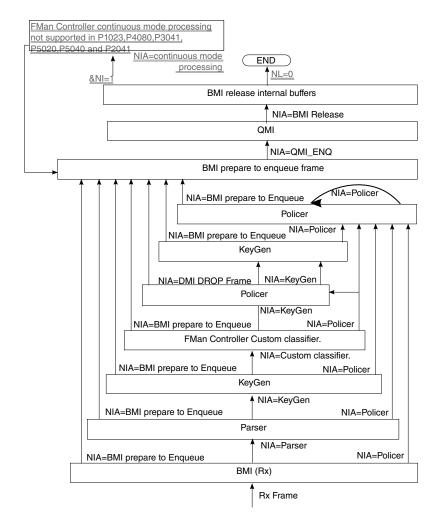

| 5.2.4.1.6 The Linux Port Devices                                    | 193 |

| 5.2.4.2 Frame Manager Linux Driver API Reference                    |     |

| 5.2.4.3 Frame Manager Driver User Guide                             |     |

| 5.2.4.3.1 Frame Manager Driver                                      |     |

| 5.2.4.4 Frame Manager Driver API Reference                          |     |

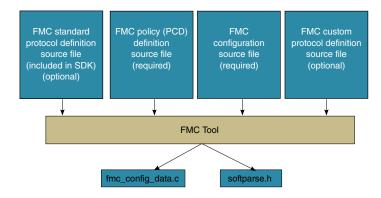

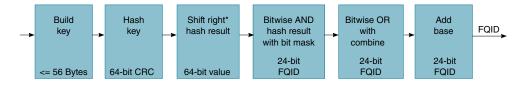

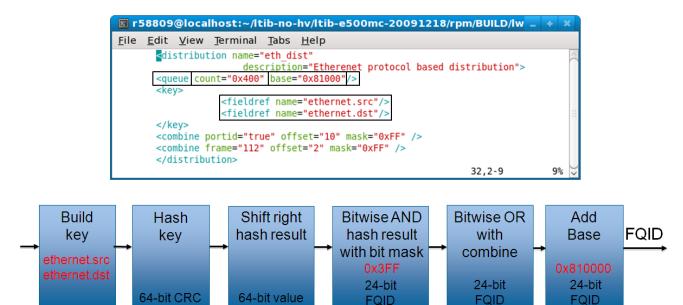

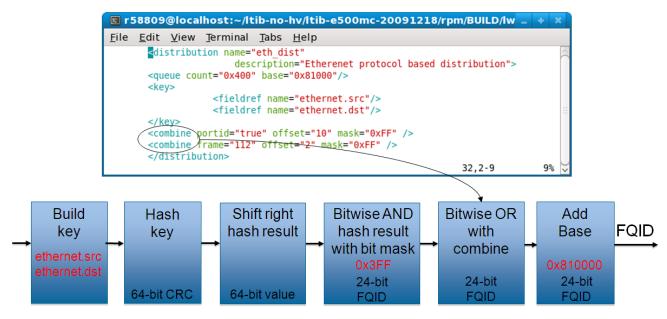

| 5.2.4.5 Frame Manager Configuration Tool User Guide                 |     |

| 5.2.4.5.1 Frame Manager Configuration Tool User Guide               |     |

| 5.2.5 Security Engine (SEC)                                         |     |

| 5.2.5 Security Engine (SEO)                                         |     |

|                                                                     |     |

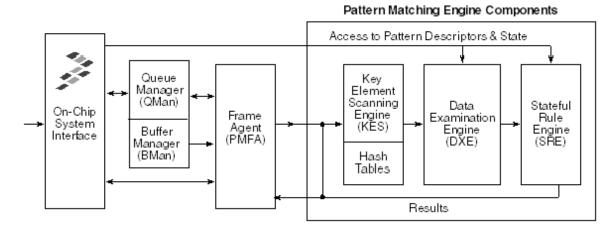

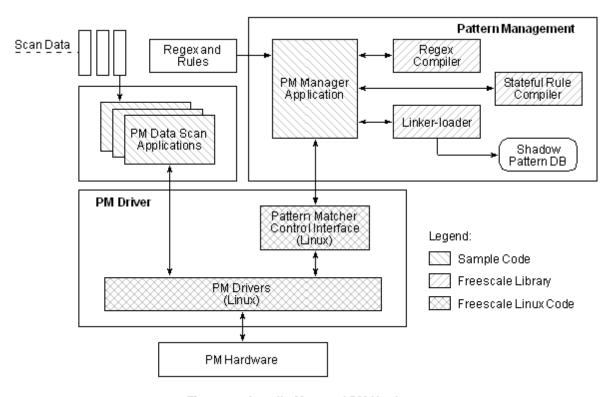

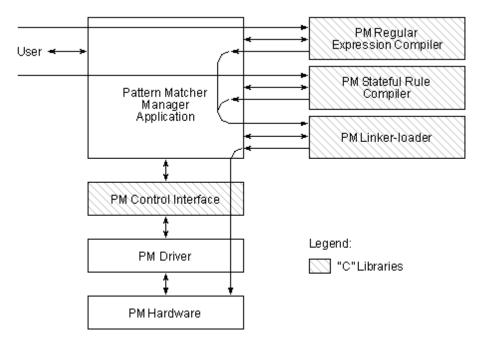

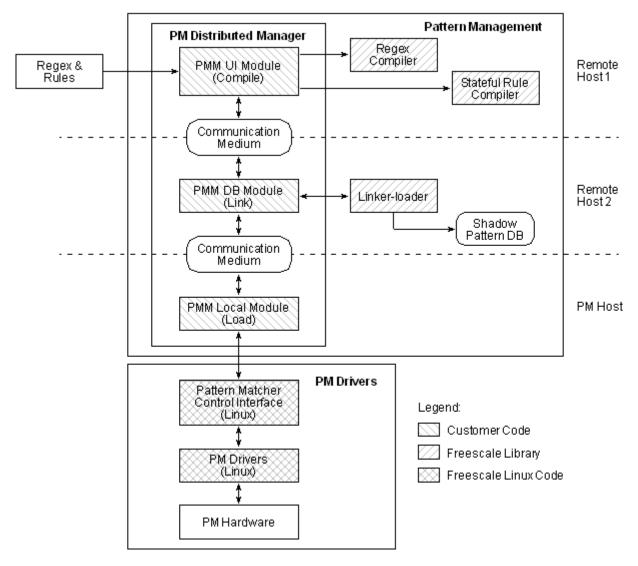

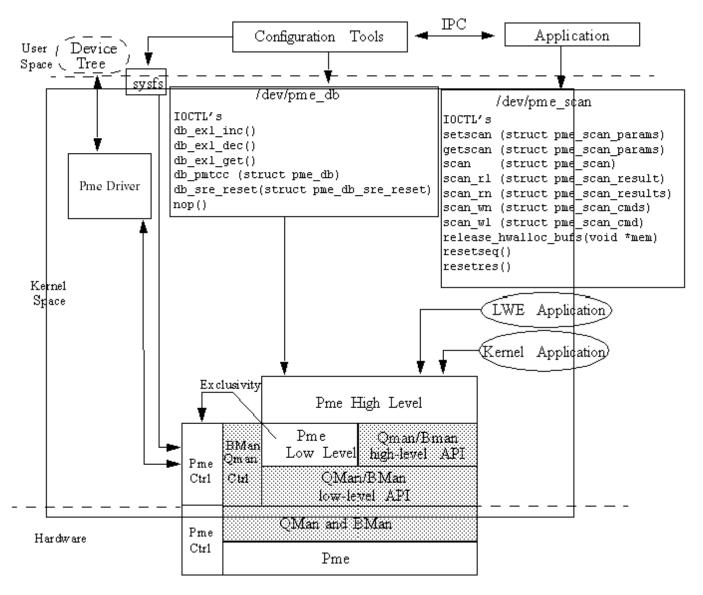

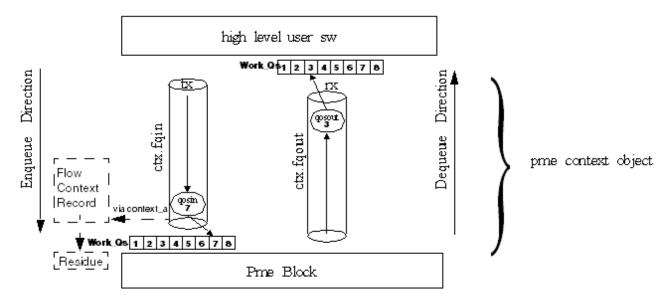

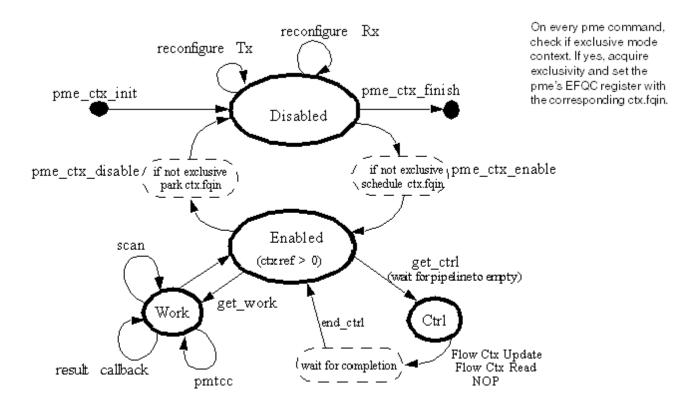

| 5.2.6 Pattern Matching Engine (PME)                                 |     |

|                                                                     |     |

| 5.2.6.2 Pattern Matcher 2.0 Software User's Guide                   |     |

| 5.2.6.2.1 Preface                                                   |     |

| 5.2.6.2.2 Overview                                                  |     |

| 5.2.6.2.3 Regular Expressions                                       |     |

| 5.2.6.2.4 Application Interface                                     |     |

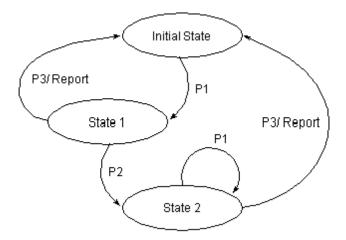

| 5.2.6.2.5 Stateful Rules                                            |     |

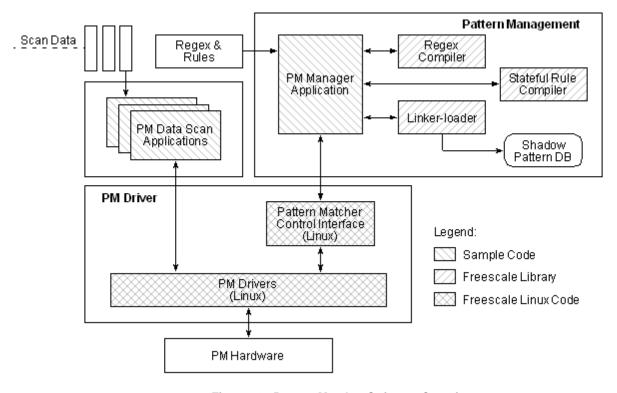

| 5.2.6.2.6 Pattern Management Software                               |     |

| 5.2.6.2.7 Pattern Matcher Driver Software                           |     |

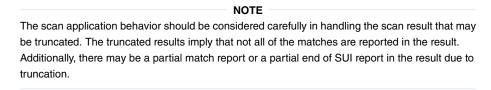

| 5.2.6.2.8 Data Scan Sample Application                              |     |

| 5.2.6.2.9 Software Components                                       | 377 |

| 5.2.6.2.10 Pattern Matcher FAQ                                      | 378 |

| 5.2.6.2.11 Revision History                                         | 381 |

| 5.2.6.3 Pattern Matcher 2.0, 2.1, 2.2 Software API Reference Manual | 381 |

| 5.2.6.3.1 Introduction                                              | 381 |

| 5.2.6.3.2 Software Component Overview                               | 382 |

| 5.2.6.3.3 Regular Expression Compiler                               |     |

| 5.2.6.3.4 Stateful Rule Compiler                                    |     |

| 5.2.6.3.5 Pattern Matcher Configuration (PMC) API                   |     |

| 5.2.6.3.6 Linker-Loader                                             |     |

| 5.2.6.3.7 Pattern Matcher Driver                                    |     |

| 5.2.6.3.8 Control Interface                                         |     |

| 5.2.6.3.9 Appendix: PMP Message Format                              |     |

| 5.2.7 Decompression/Compression Acceleration (DCE)                  |     |

| 5.2.7.1 DCE Drivers Release Notes                                   |     |

| 5.3 Enhanced Secured Digital Host Controller (eSDHC)                | 400 |

| 5.3.1 eSDHC Driver User Manual                                      | 470 |

|                                                                     |     |

| 5.4 Ethernet                                                        |     |

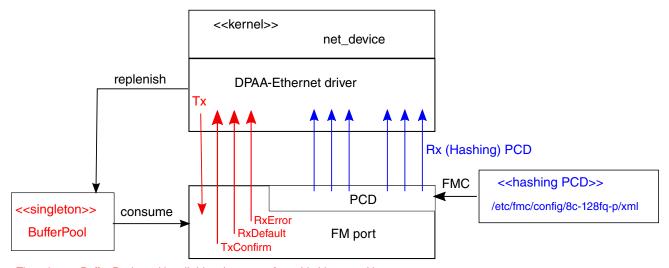

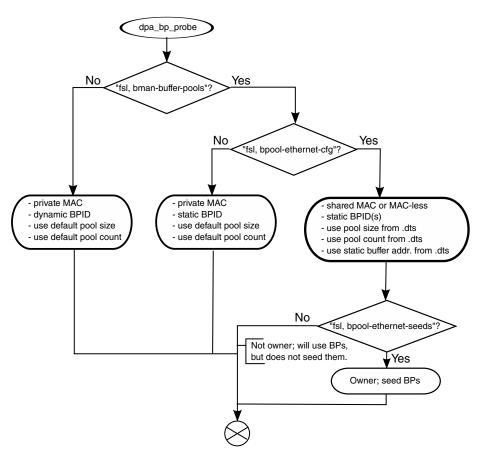

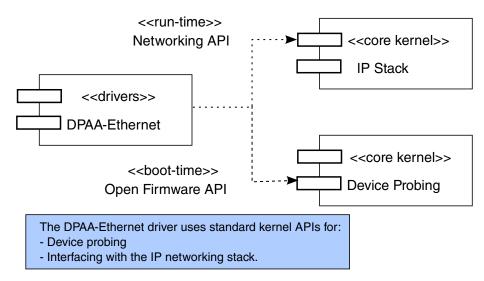

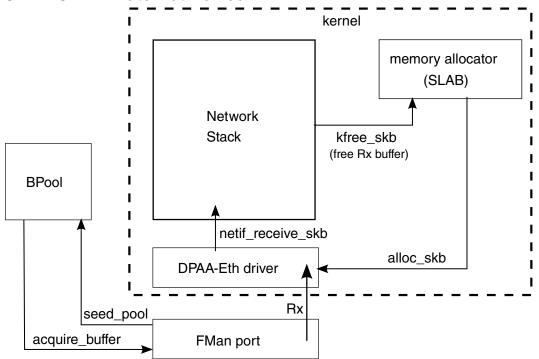

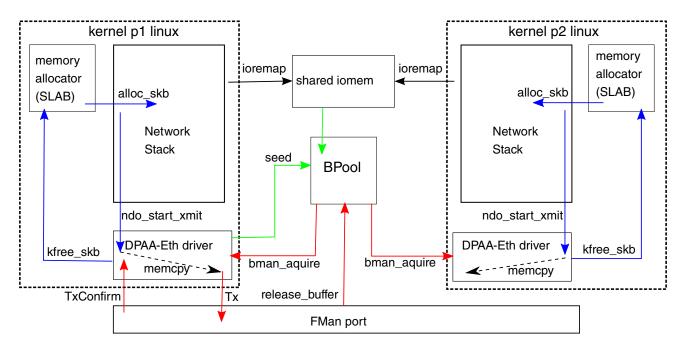

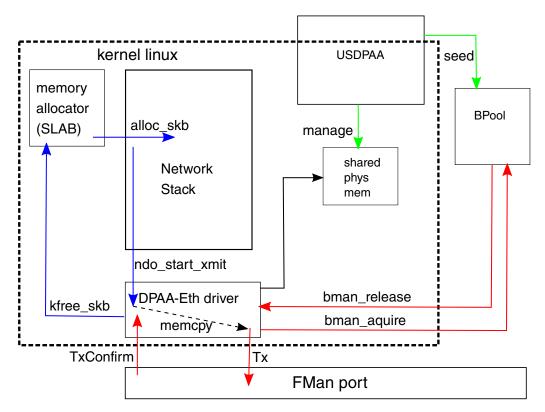

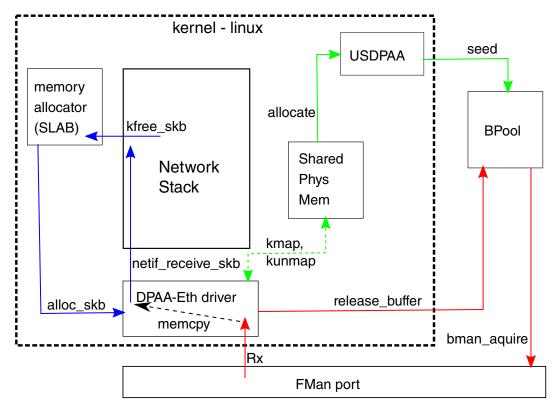

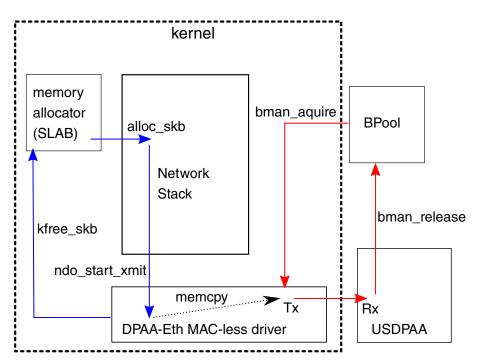

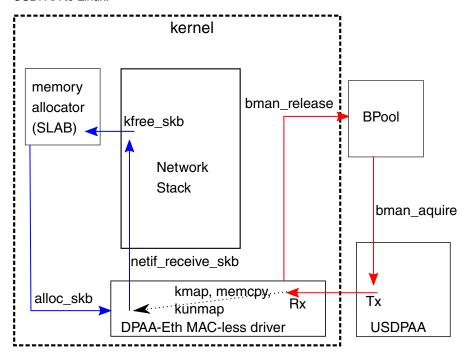

| 5.4.1 Linux Ethernet Driver for DPAA 1.x Family                     |     |

| 5.4.1.1 Linux DPAA 1.x Ethernet Primer                              |     |

| 5.4.1.1 Introduction                                                | _   |

| 5.4.1.1.2 Intended Use Cases                                        |     |

| 5.4.1.1.3 The DPAA-Eth View of the World                            |     |

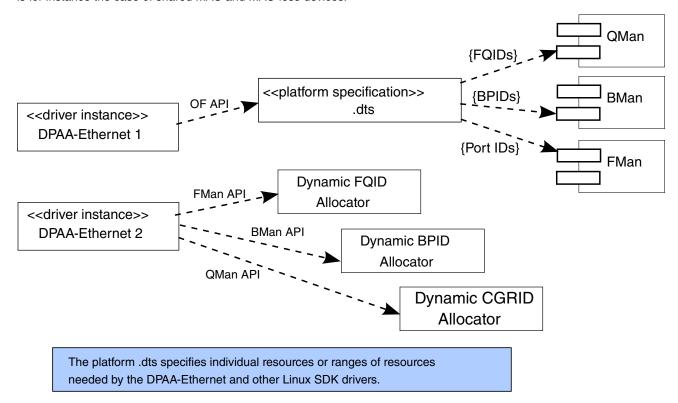

| 5.4.1.1.4 DPAA Resources Initialization                             |     |

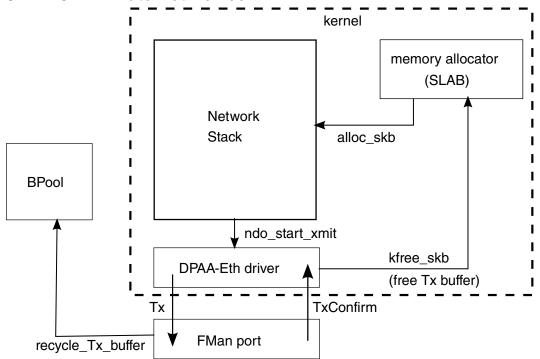

| 5.4.1.1.5 The (Simplified) Life of a Packet                         |     |

| 5.4.1.1.6 Advanced Drivers Use Cases                                | 491 |

|                                                                     |     |

| 5.4.1.1.7 Appendix A: Infrequently Asked Questions             | 493 |

|----------------------------------------------------------------|-----|

| 5.4.1.1.8 Appendix B: Frequently Asked Questions               |     |

| 5.4.1.2 Linux DPAA 1.x Ethernet Drivers                        | 494 |

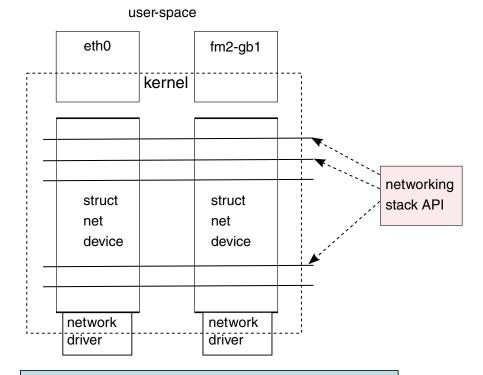

| 5.4.1.2.1 Introduction                                         | 494 |

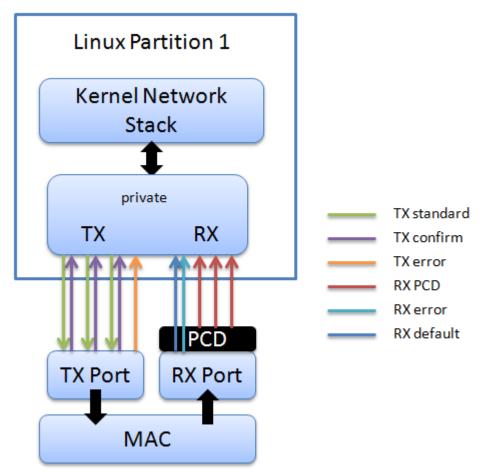

| 5.4.1.2.2 Private DPAA Ethernet Driver                         | 495 |

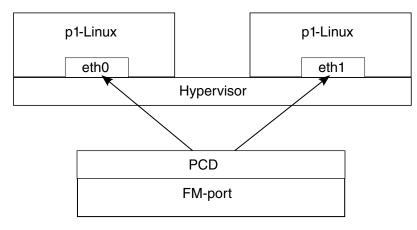

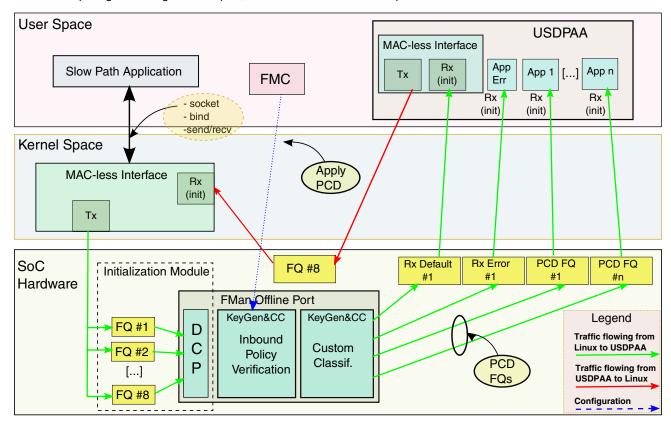

| 5.4.1.2.3 Ethernet Advanced Drivers                            | 510 |

| 5.4.1.2.4 Offline Parsing Port Driver                          | 523 |

| 5.4.1.2.5 Link Management                                      | 525 |

| 5.4.1.2.6 Debugging                                            | 527 |

| 5.4.1.2.7 Adding support for DPAA Ethernet in Topaz Hypervisor | 529 |

| 5.4.1.2.8 MACsec                                               | 531 |

| 5.4.1.2.9 Changes from previous versions                       | 544 |

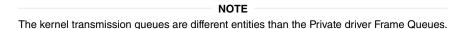

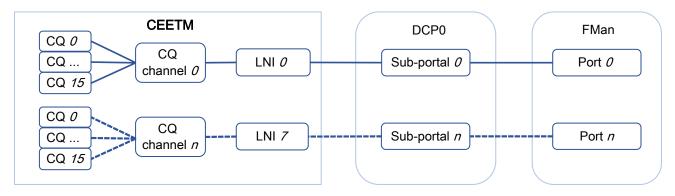

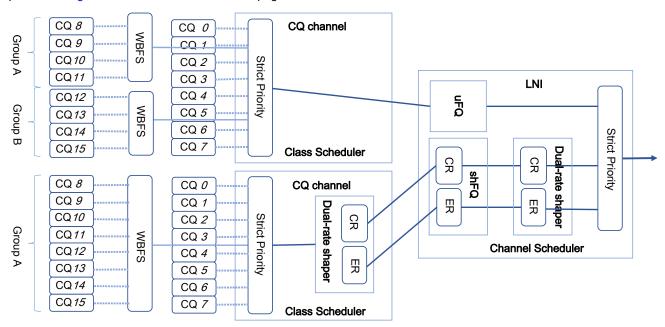

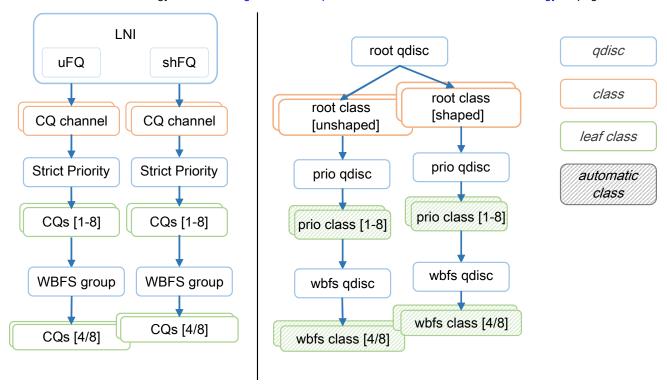

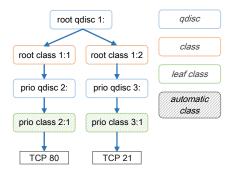

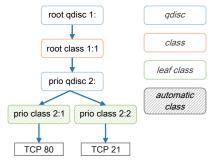

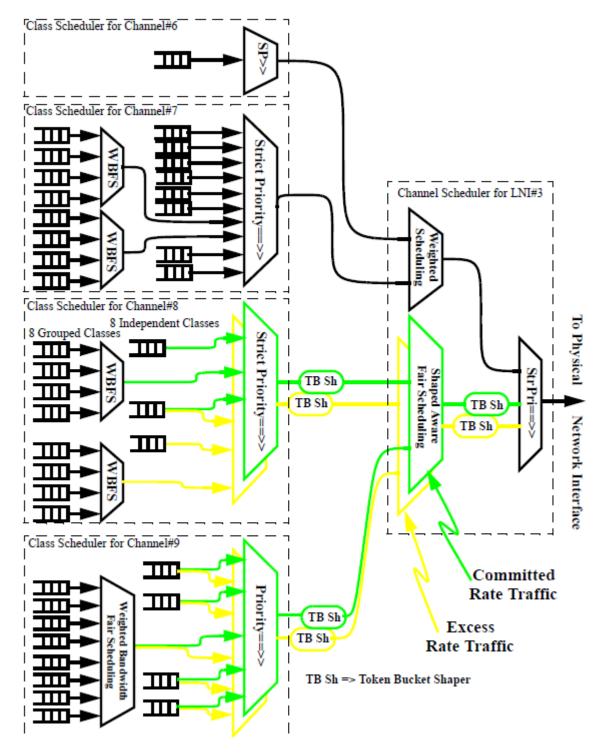

| 5.4.1.3 Quality of Service                                     | 547 |

| 5.4.1.3.1 Features                                             | 547 |

| 5.4.1.3.2 Policing                                             |     |

| 5.4.1.3.3 Scheduling and Shaping                               |     |

| 5.5 Flash Memory                                               |     |

| 5.5.1 JFFS2 on NOR Flash Device Driver User Manual             |     |

| 5.5.2 JFFS2 on NAND Flash Device Driver User Manual            |     |

| 5.5.3 IFC NOR Flash User Manual                                |     |

| 5.5.4 IFC NAND Flash User Manual                               |     |

| 5.6 IEEE 1588 Timer Module                                     |     |

| 5.6.1 IEEE 1588 Device Driver User Manual                      |     |

| 5.7 Low Power UART User Guide                                  |     |

| 5.7.1 Low Power UART User Guide                                |     |

| 5.8 PCI Express Interface Controller                           |     |

| 5.8.1 PCIe Linux Driver                                        |     |

| 5.8.2 EDAC Driver User Manual                                  |     |

| 5.8.3 PCIe Advanced Error Reporting User Manual                |     |

| 5.8.4 PCIe Remove and Rescan User Manual                       |     |

| 5.8.5 PCIe Endpoint User Manual5.9 SATA Controller             |     |

| 5.9.1 External SATA Controller User Manual                     |     |

| 5.9.2 NXP Native SATA User Manual                              |     |

| 5.10 Serial Peripheral Interface                               |     |

| 5.10.1 QuadSPI Driver for TWR-LS1021A User Manual              |     |

| 5.10.1.1 QuadSPI Driver User Manual                            |     |

| 5.11 Universal Serial Bus Interfaces                           |     |

| 5.11.1 USB 2.0 Host Driver                                     |     |

| 5.11.1.1 USB 2.0 Host Driver User Manual                       |     |

| 5.11.2 USB Gadget Memory Driver User Manual                    |     |

| 5.11.2.1 USB Gadget for Memory Devices                         |     |

| 5.11.3 USB Gadget Network Driver User Manual                   |     |

| 5.11.3.1 USB Gadget for Network Devices                        |     |

| 5.11.4 USB 3.0 Host/Peripheral Linux Driver User Manual        | 633 |

| 5.11.4.1 USB 3.0 Host/Peripheral Linux Driver User Manual      | 633 |

| 5.12 Watchdog Timers                                           | 643 |

| 5.12.1 Watchdog Device Driver User Manual                      | 643 |

| Chapter 6 Additional Linux Use Cases                           | 648 |

| 6.1 Power Management                                           |     |

| 6.1.1 Power Management User Manual                             |     |

| 6.1.2 CPU Frequency Switching User Manual                      |     |

| 6.1.3 System Monitor                                           |     |

| /                                                              |     |

| 6.1.3.1 Power Monitor User Manual                                  | 654 |

|--------------------------------------------------------------------|-----|

| 6.1.3.2 Thermal Monitor User Manual                                | 659 |

| 6.1.3.3 Web-based System Monitor User Guide                        | 660 |

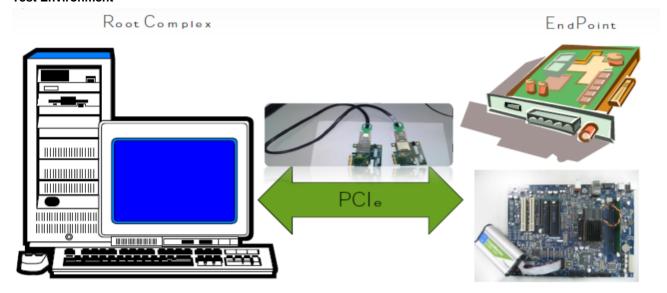

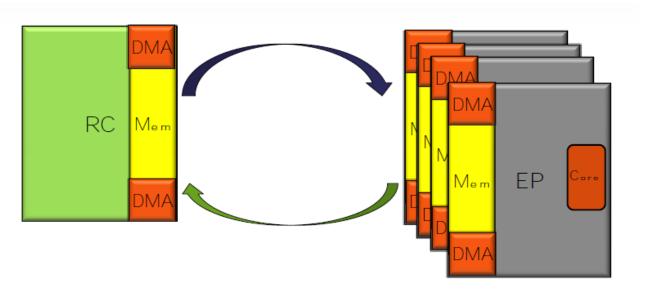

| 6.2 PCIe DMA Test User Manual                                      | 662 |

| 6.2.1 Introduction to PCI DMA Test                                 |     |

| 6.2.2 PCI DMA EP Application                                       | 664 |

| 6.2.3 PCI DMA Host Driver Module                                   |     |

| 6.2.4 Test Procedure                                               |     |

|                                                                    |     |

| Chantar 7 Linux Hoor Space                                         | 672 |

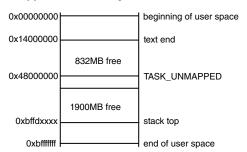

| Chapter 7 Linux User Space                                         |     |

| 7.1 Linux HugeTLBFS User Guide                                     |     |

| 7.1.1 Introduction                                                 |     |

| 7.1.2 Objectives                                                   |     |

| 7.1.3 TLBFS Basics                                                 |     |

| 7.1.3.1 4KB TLB0 Miss Issues                                       |     |

| 7.1.3.2 e500 Family TLB1                                           |     |

| 7.1.3.3 HugeTLB Basics                                             |     |

| 7.1.3.4 Normal vs. Gigantic hugepages                              |     |

| 7.1.4 Building and Booting Linux with Hugetlb                      |     |

| 7.1.4.1 Booting Linux for HugeTLB                                  |     |

| 7.1.4.2 Setting Up Mount Points with hugeadm                       |     |

| 7.1.4.3 Running Hugepage mount/query Example                       |     |

| 7.1.5 Hugepage Allocation in User Programs                         |     |

| 7.1.5.1 Using Shared Memory Hugepages: SHM_HUGETLB                 |     |

| 7.1.5.2 Running the SHM_HUGETLB Example                            |     |

| 7.1.5.3 Using Shared Memory Hugepages: Link with libhugetlbfs      |     |

| 7.1.6 Manipulating Shared Memory System Tunables                   |     |

| 7.1.6.1 Allocating hugepages for Heap Memory                       |     |

| 7.1.6.2 Invoking Applications with Huge Heap (mallock()/new)       |     |

| 7.1.6.3 Moving the Heap for Hugepage Allocations                   |     |

| 7.1.7 Using Hugepages for .text, .data, and/or .bss (gnu ld 2.17+) |     |

| 7.1.8 Performing mmap on a Hugepage-backed File                    |     |

| 7.1.8.1 Exercising the mmap() File Example                         |     |

| 7.1.8.2 Requesting Anonymous mmap() with Hugepages                 |     |

| 7.1.8.3 Using HugeTLB mmap(): Arguments and Error Checking         |     |

| 7.1.8.4 Using HugeTLB munmap(): Arguments and Error Checking       |     |

| 7.1.9 Running the Test                                             |     |

| 7.1.9.1 When to Use Hugepages                                      |     |

| 7.1.10 Matching Hugetlb Methods with Program Characteristics       |     |

| 7.1.11 Using Multiple Types of Hugepage Allocation Methods         |     |

| 7.1.12 Hugetlb Benefits and Limitations                            |     |

| 7.1.13 Understand the Differences Between Applications             |     |

| 7.1.14 HugeTLB Status and Support                                  |     |

| 7.1.15 HugeTLB Resources                                           |     |

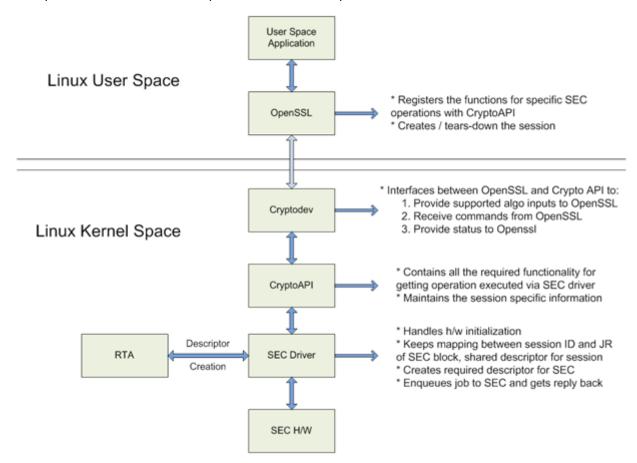

| 7.2 OpenSSL Offload User's Guide                                   |     |

| 7.2.1 Overview                                                     |     |

| 7.2.1.1 OpenSSL Software architecture                              |     |

| 7.2.1.1.1 OpenSSL's ENGINE Interface                               |     |

| 7.2.1.1.2 NXP solution for OpenSSL hardware offloading             |     |

| 7.2.2 Valid TLS Ciphersuites based on TLS protocol version         |     |

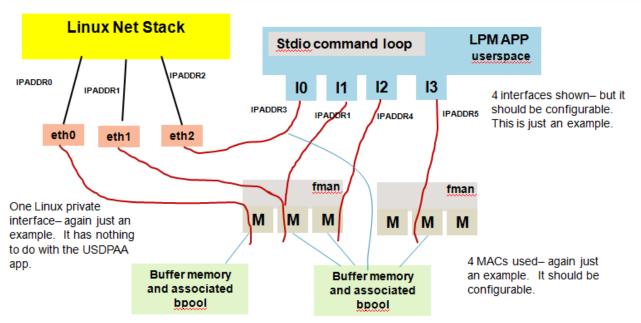

| 7.3 USDPAA                                                         |     |

| 7.3.1 USDPAA User Guide                                            |     |

| 7.3.1.1 Introduction                                               |     |

| 7.3.1.1.1 Intended audience                                        | 693 |

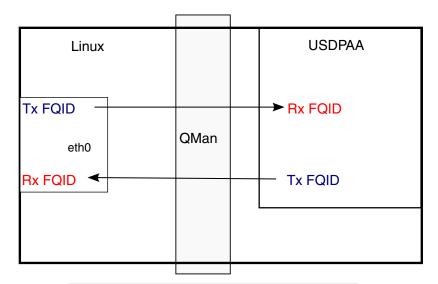

| 7.3.1.1.2 USDPAA overview                                         |     |

|-------------------------------------------------------------------|-----|

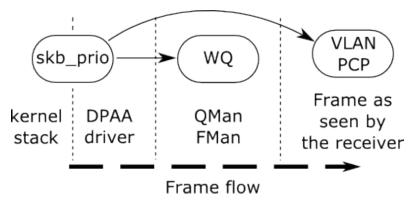

| 7.3.1.1.3 USDPAA and legacy Linux software                        | 694 |

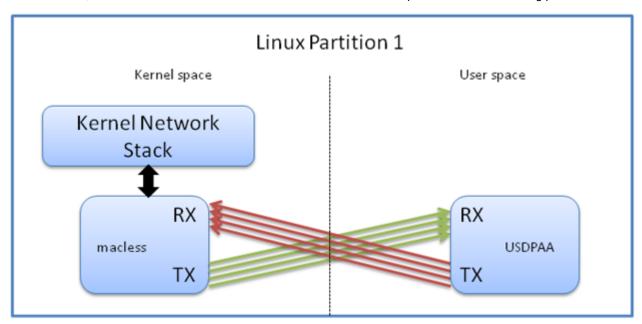

| 7.3.1.2 USDPAA assumptions and use cases                          | 694 |

| 7.3.1.2.1 Assumptions                                             | 694 |

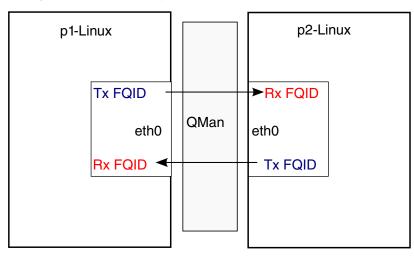

| 7.3.1.2.2 Use cases                                               | 695 |

| 7.3.1.3 USDPAA components                                         | 696 |

| 7.3.1.3.1 Device-tree handling                                    | 696 |

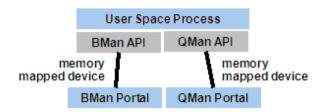

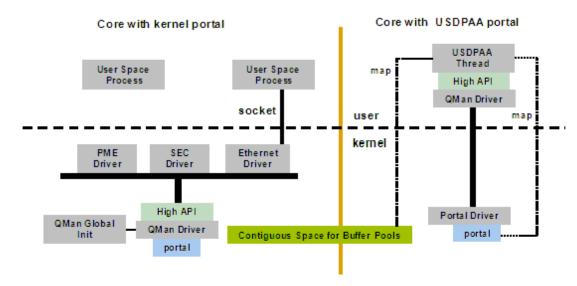

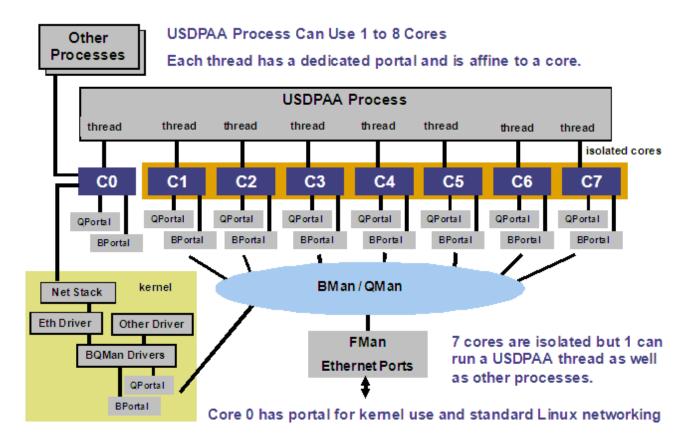

| 7.3.1.3.2 QMan and BMan drivers and C API                         | 696 |

| 7.3.1.3.3 DMA memory management                                   | 699 |

| 7.3.1.3.4 Network configuration                                   |     |

| 7.3.1.3.5 CPU isolation                                           |     |

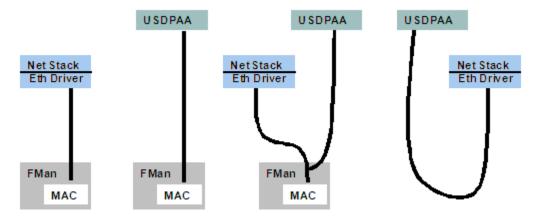

| 7.3.1.4 Relationship to SDK Linux ethernet subsystem              |     |

| 7.3.1.4.1 Selecting ethernet interfaces for USDPAA                |     |

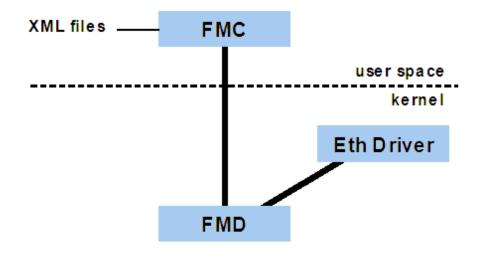

| 7.3.1.4.2 FMC, FMD, and the ethernet Driver                       |     |

| 7.3.1.5 Supported hardware platforms                              |     |

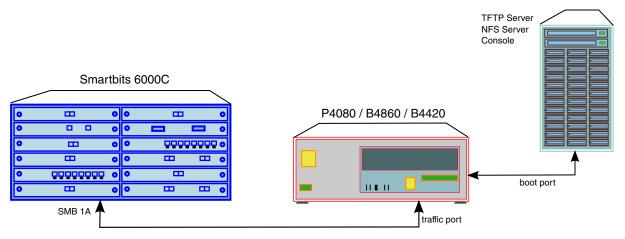

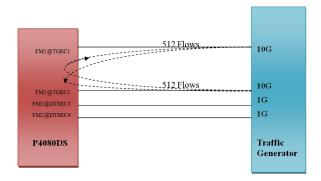

| 7.3.1.5.1 P4080DS                                                 |     |

| 7.3.1.5.2 P3041DS                                                 |     |

| 7.3.1.5.3 P5020DS                                                 |     |

| 7.3.1.5.4 P5040DS                                                 |     |

| 7.3.1.5.5 P2041RDB                                                |     |

| 7.3.1.5.6 B4860QDS                                                |     |

| 7.3.1.5.7 T4240QDS                                                |     |

| 7.3.1.6 Example applications                                      |     |

| 7.3.1.7 USDPAA installation and execution                         |     |

| 7.3.1.7.1 Files needed to boot Linux on the P4080DS system        |     |

| 7.3.1.7.2 About U-Boot and network interfaces                     |     |

| 7.3.1.7.3 P4080DS NOR flash banks                                 |     |

| 7.3.1.7.4 Programming the P4080DS NOR flash bank 4                |     |

| 7.3.1.7.5 Boot into bank 4 and set more variables                 |     |

| 7.3.1.7.6 Environment variable hwconfig and optical 10G           |     |

| 7.3.1.7.7 Booting Linux                                           |     |

| 7.3.1.7.8 Using tftp for the kernel, device-tree, and file-system |     |

| 7.3.1.8 Using configurations other than SerDes 0xe                |     |

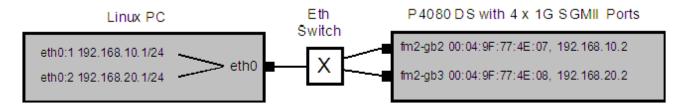

| 7.3.1.8.1 SGMII (4 x 1 Gbps) card and one XAUI (10 Gbps) card     |     |

| 7.3.1.8.2 SGMII (4 x 1 Gbps) card and no XAUI (10 Gbps) card      |     |

| 7.3.1.9 Known limitations                                         |     |

| 7.3.1.10 Document history                                         |     |

| 7.3.2 USDPAA Multiple Process Support                             |     |

| 7.3.2.1 USDPAA Multiple Process Support                           |     |

| 7.3.2.2 USDPAA Waltiple Flocess Support                           |     |

| 7.3.2.3 USDPAA Resource Management                                |     |

| 7.3.2.4 BMan and QMan API                                         |     |

| 7.3.2.5 USDPAA Thread and Global API                              |     |

| 7.3.2.6 USDPAA DMA API                                            |     |

| 7.3.2.7 USDPAA netcfg.h                                           |     |

| 7.3.2.8 Kernel configuration                                      |     |

| 7.3.2.9 Device Tree (Excluding QMan/BMan Resource Ranges)         |     |

| 7.3.2.10 Device Tree (QMan/BMan Resource Ranges)                  |     |

| 7.3.2.10 Device free (QMan/BMan Resource Ranges)                  |     |

| 7.3.2.12 USDPAA Virtualisation and Partitioning                   |     |

| <del>-</del>                                                      |     |

| 7.3.2.13 Multi-process PPAC Applications                          |     |

|                                                                   |     |

| 7.4 USDPAA Applications                                           | 700 |

| 7.4.1 USDPAA ceetm Demo User Guide                                |     |

| 7.4. I. I IIIII OUUGIIOII                                         |     |

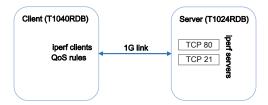

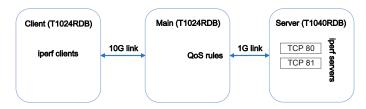

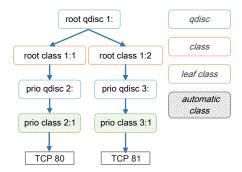

| 7.4.1.2 Overview of ceetm demo                                                   | 729 |

|----------------------------------------------------------------------------------|-----|

| 7.4.1.3 Features of ceetm demo                                                   | 729 |

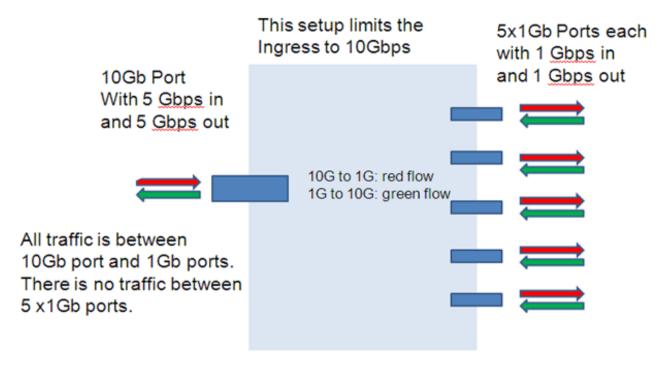

| 7.4.1.4 CEETM use case                                                           | 729 |

| 7.4.1.5 CEETM configuration file                                                 | 731 |

| 7.4.1.6 Running ceetm_demo                                                       | 733 |

| 7.4.1.7 Generate trafflic flows                                                  |     |

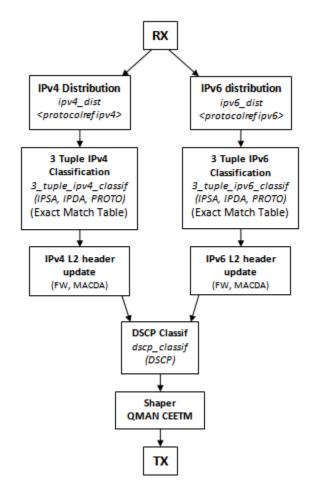

| 7.4.2 DPAA Offloading Applications Users Guide                                   |     |

| 7.4.2.1 Introduction                                                             |     |

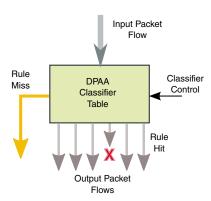

| 7.4.2.2 Altering the classifier_demo application                                 |     |

| 7.4.2.2.1 Overview                                                               |     |

| 7.4.2.2.2 Running classifier_demo                                                |     |

| 7.4.2.3 Adapting the fragmentation_demo application                              |     |

| 7.4.2.3.1 Overview                                                               |     |

| 7.4.2.3.1 Overview                                                               |     |

| 7.4.2.4 Manipulating the reassembly_demo application                             |     |

| 7.4.2.4 Manipulating the reassembly_demo application                             |     |

|                                                                                  |     |

| 7.4.2.4.2 Running reasembly_demo                                                 |     |

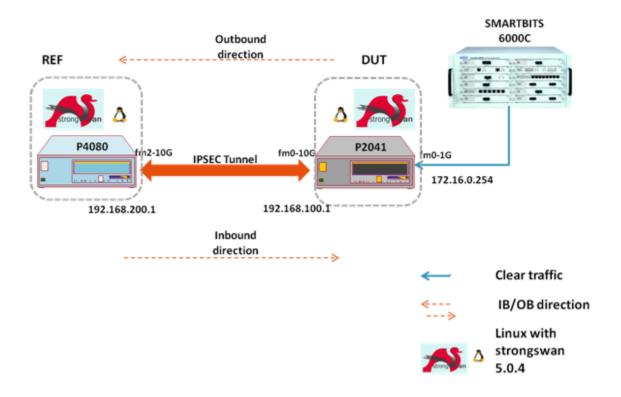

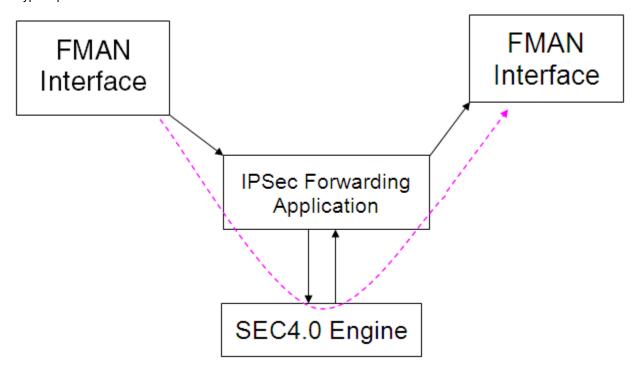

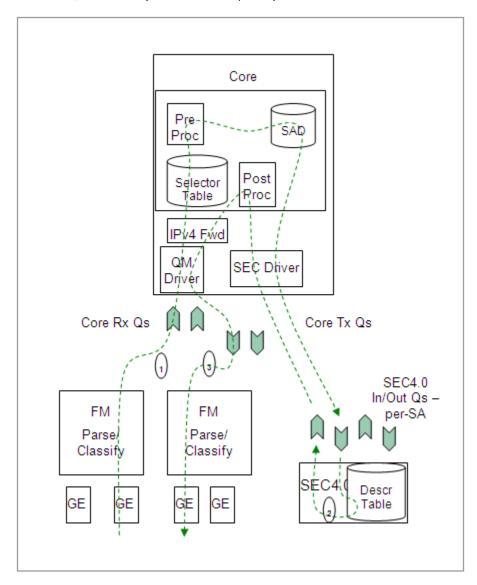

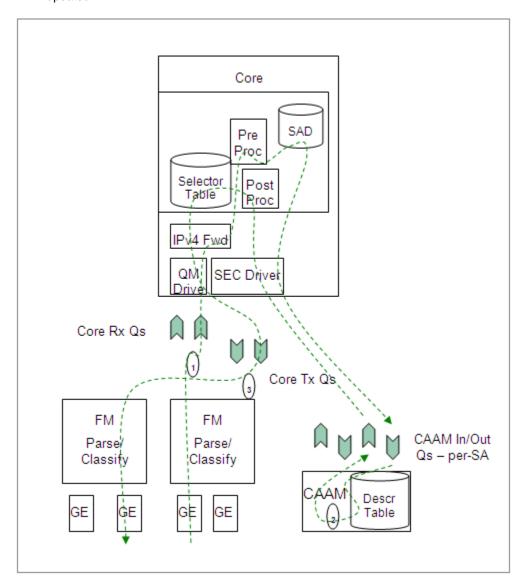

| 7.4.2.5 Customizing the ipsec_offload application                                |     |

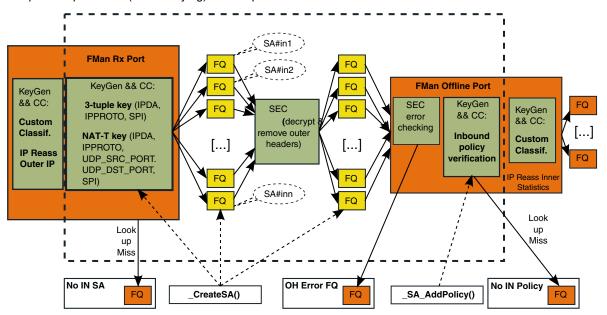

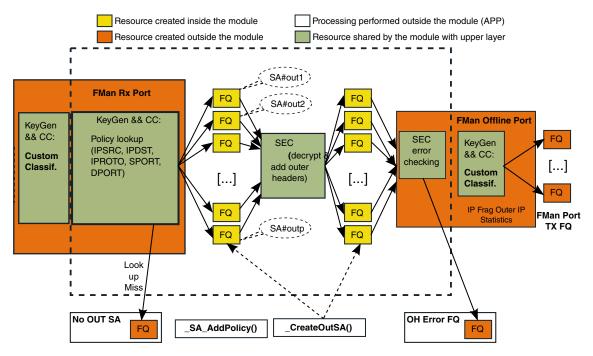

| 7.4.2.5.1 IPSec_offload application overview                                     |     |

| 7.4.2.5.2 Running the Application                                                |     |

| 7.4.2.5.3 ipsec_offload application flow                                         |     |

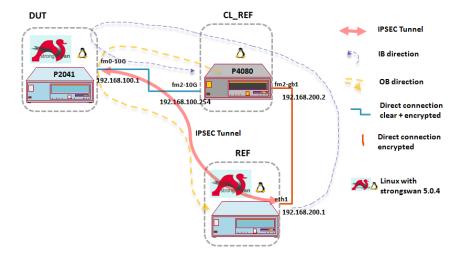

| 7.4.2.5.4 IPSEC tunnel setup using ipsec offload application and Strongswan with |     |

| 7.4.2.5.5 Ipsec offload application in multiple instances configuration          |     |

| 7.4.2.5.6 Host to host tunnels                                                   |     |

| 7.4.2.6 Using the dpa_offload - the NF API offloading demo application           |     |

| 7.4.2.6.1 Overview                                                               |     |

| 7.4.2.6.2 Running dpa_offload                                                    |     |

| 7.4.2.7 References                                                               |     |

| 7.4.2.8 Appendix A – Preparing DPA Offloading DTB Files                          |     |

| 7.4.2.8.1 Compiling the device tree for USDPAA applications                      |     |

| 7.4.2.8.2 Compiling the device tree for IP offloading                            |     |

| 7.4.2.8.3 Compiling the device tree for IP reassembly                            |     |

| 7.4.2.8.4 Compiling the device tree for ipsec offload                            |     |

| 7.4.2.8.5 Compiling the device tree for Network Function Layer offloading        |     |

| 7.4.2.9 Appendix B - Enabling DPA Offloading Drivers in the Linux Kernel         |     |

| 7.4.2.10 Revision history                                                        |     |

| 7.4.3 DPAA Offloading Drivers Reference Manual                                   |     |

| 7.4.3.1 Introduction                                                             |     |

| 7.4.3.2 DPA Classifier                                                           |     |

| 7.4.3.2.1 Table                                                                  |     |

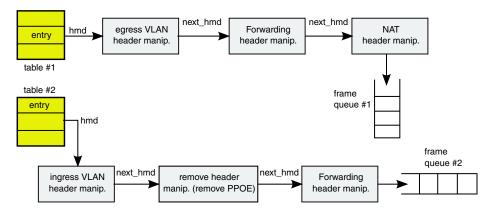

| 7.4.3.2.2 Header Manipulation                                                    | 810 |

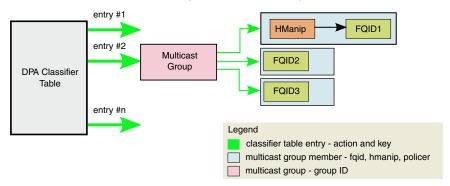

| 7.4.3.2.3 Multicast                                                              | 839 |

| 7.4.3.3 DPA IPSec                                                                |     |

| 7.4.3.3.1 Initialization                                                         | 845 |

| 7.4.3.3.2 DPA IPSec API                                                          |     |

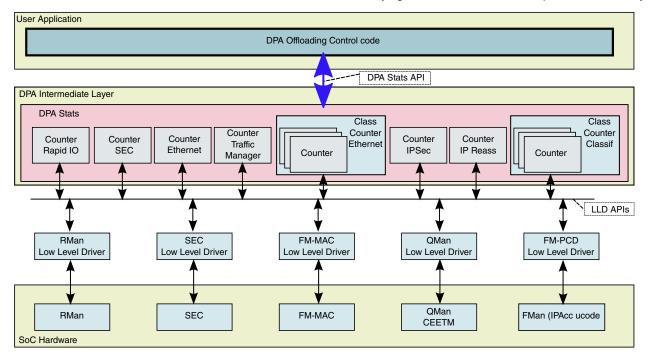

| 7.4.3.4 DPA Statistics                                                           | 870 |

| 7.4.3.4.1 Initialization                                                         |     |

| 7.4.3.4.2 DPA Statistics API                                                     |     |

| 7.4.3.5 Network Function Layer                                                   | 889 |

| 7.4.3.6 References                                                               |     |

| 7.4.4 USDPAA PPAC User Manual                                                    |     |

| 7.4.4.1 USDPAA PPAC Users Manual                                                 | 890 |

| 7.4.4.2 Overview of PPAC                                                         |     |

| 7.4.4.3 Overview of PPAC Method and Implementation                               | 892 |

| 7.4.4 PPAC Files                                                                 | 893 |

| 7.4.4.5 PPAM Files                                           | 894 |

|--------------------------------------------------------------|-----|

| 7.4.4.6 Packet-processing data structures                    | 895 |

| 7.4.4.7 PPAM-provided Functions                              | 897 |

| 7.4.4.8 PPAM Rx and Tx                                       | 898 |

| 7.4.4.9 PPAC Provided Functions                              | 900 |

| 7.4.4.10 PPAC Setting                                        | 902 |

| 7.4.4.11 PPAC Buffers                                        | 903 |

| 7.4.4.12 Chronology of a DPAA application                    | 904 |

| 7.4.4.13 A non-PPAC comparison, "hello_reflector"            |     |

| 7.4.5 USDPAA Reflector and PPAC User Guide SDK               | 906 |

| 7.4.5.1 Introduction                                         | 906 |

| 7.4.5.1.1 Intended audience                                  | 907 |

| 7.4.5.1.2 Change history                                     | 907 |

| 7.4.5.2 Overview of reflector                                |     |

| 7.4.5.3 Overview of PPAC                                     | 908 |

| 7.4.5.4 PPAC details                                         | 908 |

| 7.4.5.4.1 IRQ mode for sleeping when idle                    |     |

| 7.4.5.4.2 Buffers                                            |     |

| 7.4.5.4.3 Compile-time configuration                         |     |

| 7.4.5.5 Running reflector                                    |     |

| 7.4.5.6 PPAC (and reflector) CLI commands                    |     |

| 7.4.5.7 Running hello_reflector                              |     |

| 7.4.5.8 Running hello_reflector (short circuit)              |     |

| 7.4.5.9 Testing reflector                                    |     |

| 7.4.6 NXP USDPAA IPFWD User Manual Rev. 1.2                  |     |

| 7.4.6.1 About this Book                                      |     |

| 7.4.6.2 Introduction                                         |     |

| 7.4.6.2.1 Purpose                                            |     |

| 7.4.6.3 Overview                                             |     |

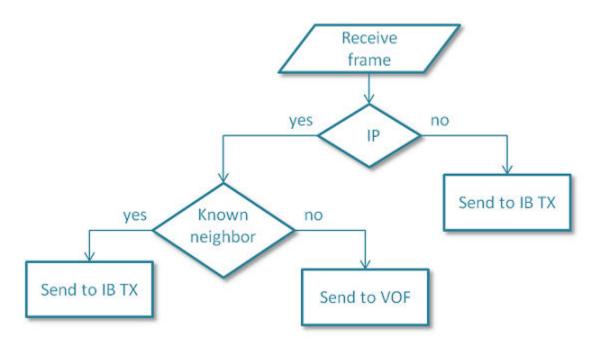

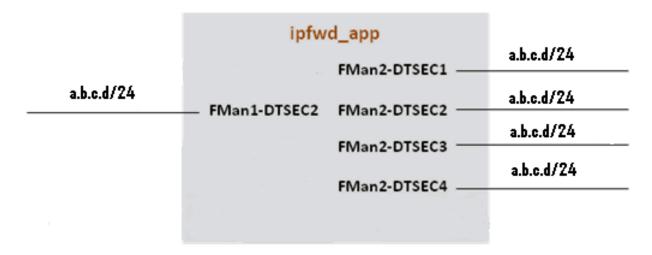

| 7.4.6.3.1 USDPAA IPv4 forwarding application flow            |     |

| 7.4.6.4 Overview of PPAC                                     |     |

| 7.4.6.5 IPFwd related PPAC Details                           |     |

| 7.4.6.5.1 Compile-time configuration                         |     |

| 7.4.6.6 PPAM related compile time configuration              |     |

| 7.4.6.6.1 One million route support                          |     |

| 7.4.6.7 IPFWD Application Suite                              |     |

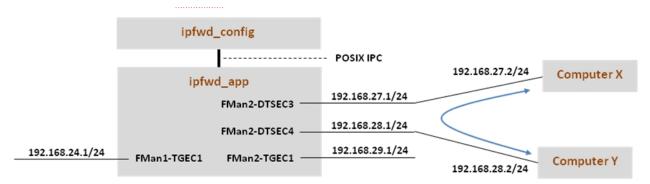

| 7.4.6.8 Possible configuration scenario for IPFWD            |     |

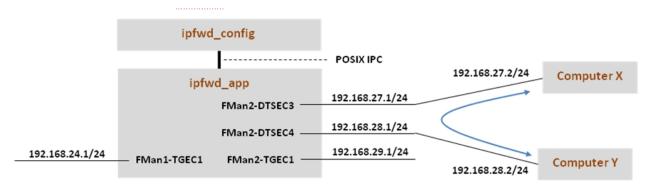

| 7.4.6.9 Using Two Computers to Test the IPFWD Application Su |     |

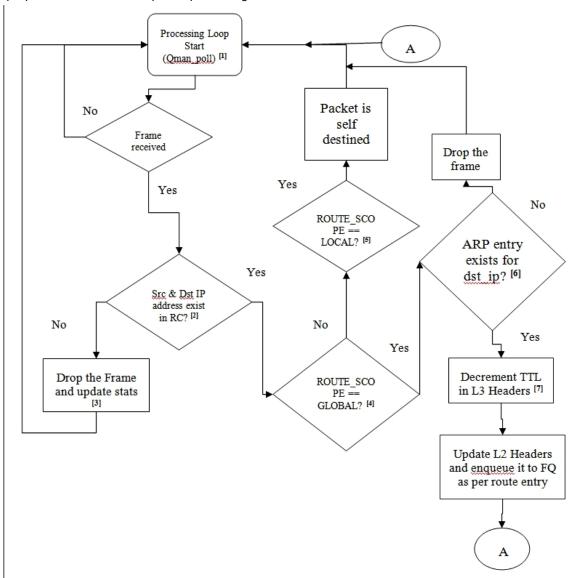

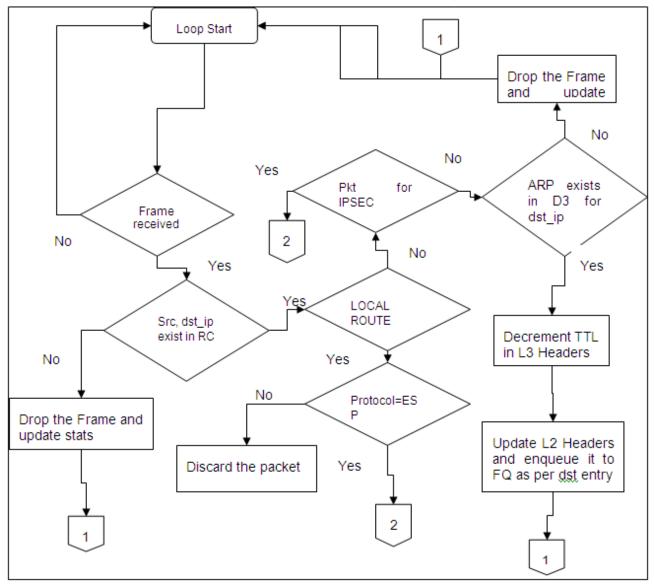

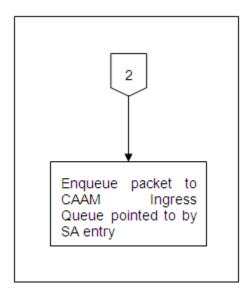

| 7.4.6.10 Flowchart for packet processing                     |     |

| 7.4.6.10.1 Description of Flow chart                         |     |

| 7.4.6.10.2 Running IPv4 forwarding on P4080DS board.         |     |

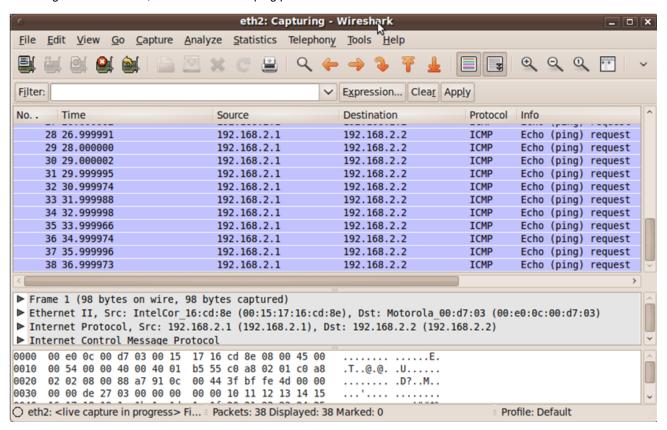

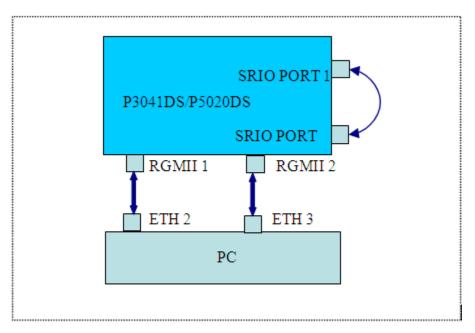

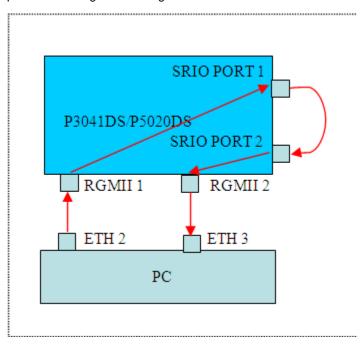

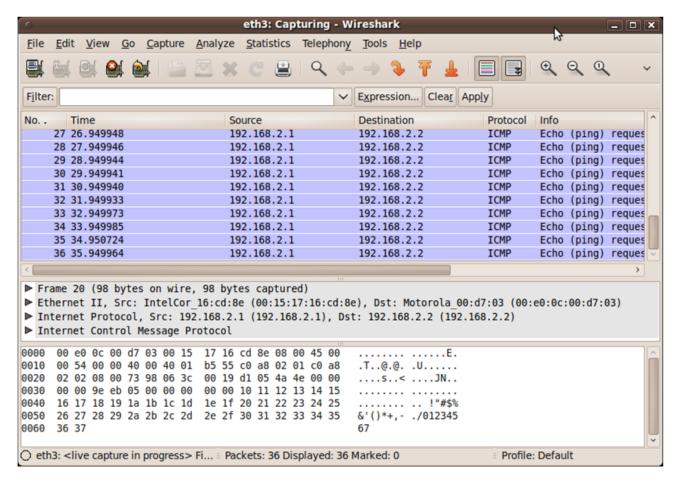

| 7.4.6.10.3 Running IPv4 forwarding on P3041/P5020 bo         |     |

| 7.4.6.10.4 Running IPv4 forwarding on T4240 board            |     |

| 7.4.6.10.5 Running IPv4 forwarding on B4860 board            |     |

| 7.4.6.10.6 Performance gap between 8 core and 6 core.        |     |

| 7.4.6.10.7 PPAC (and IPFwd) CLI commands                     |     |

| 7.4.6.11 IPv4 forward application Configuration command      |     |

| 7.4.6.11.1 Syntax                                            |     |

| 7.4.6.12 Traffic Generation                                  |     |

| 7.4.6.13 References                                          |     |

| 7.4.7 NXP USDPAA IPSecfwd User Manual                        |     |

| 7.4.7.1 Introduction                                         |     |

| 7.4.7.1 Purpose                                              |     |

| 7.4.7.1.2 Change History                                     |     |

| 7.4.7.2 USDPAA IPSecfwd application                          |     |

| Cobine in Cooling application                                |     |

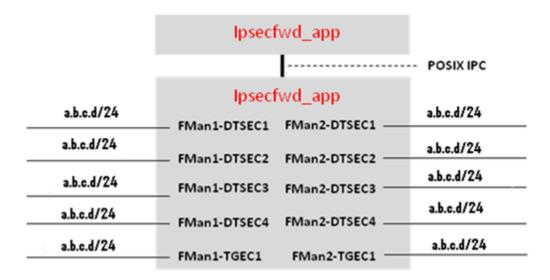

| 7.4.7.2.1 Application Overview                                    | 944 |

|-------------------------------------------------------------------|-----|

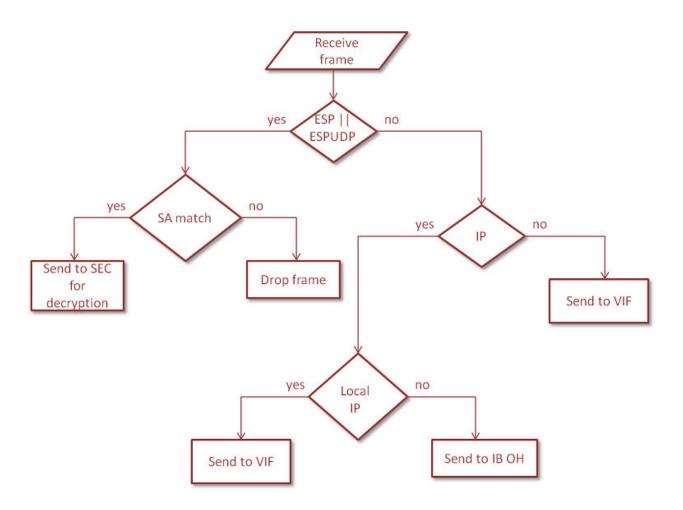

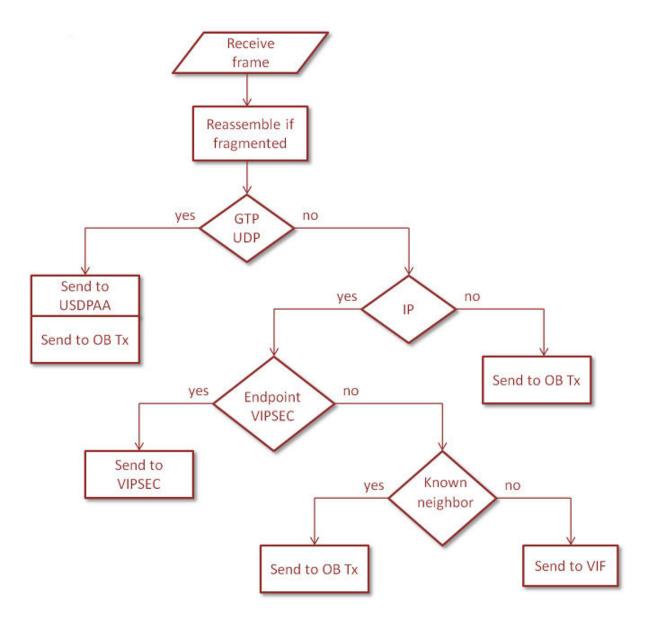

| 7.4.7.2.2 Packet Flow                                             | 944 |

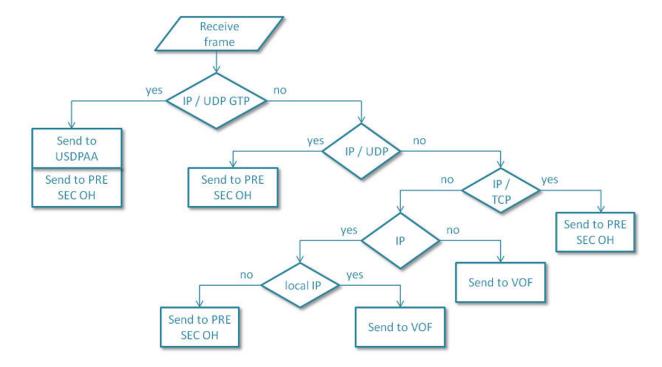

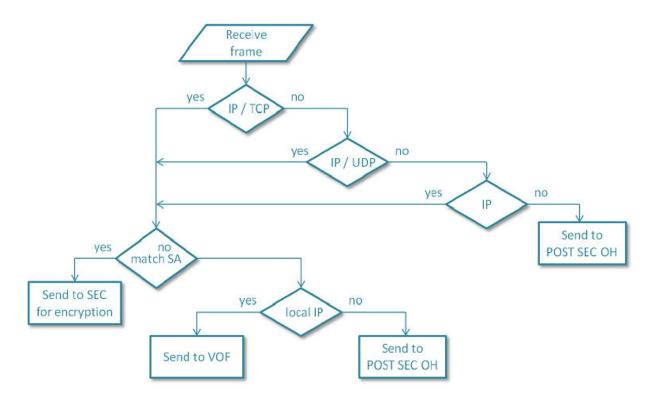

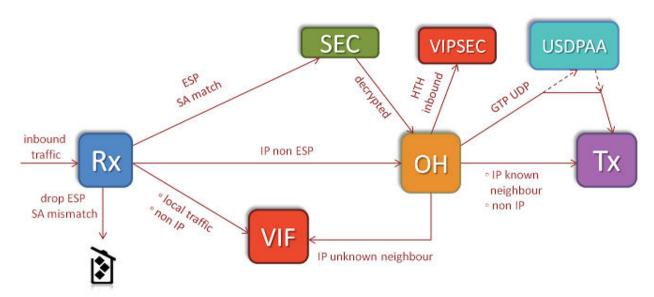

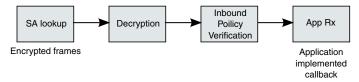

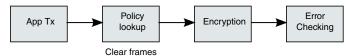

| 7.4.7.2.3 Overview of IPSecfwd packet processing                  | 945 |

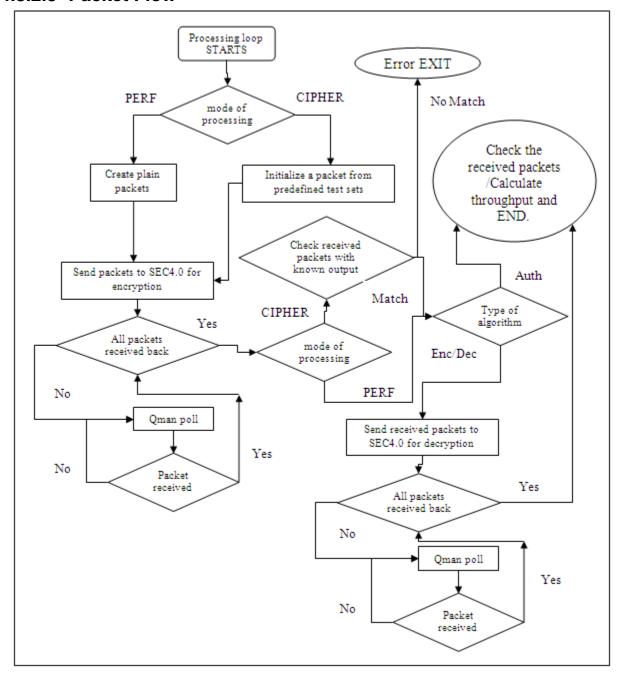

| 7.4.7.2.4 Flow chart for IpSecfwd packet processing               | 948 |

| 7.4.7.3 Overview of PPAC                                          | 949 |

| 7.4.7.4 IPSecfwd related PPAM Details                             | 949 |

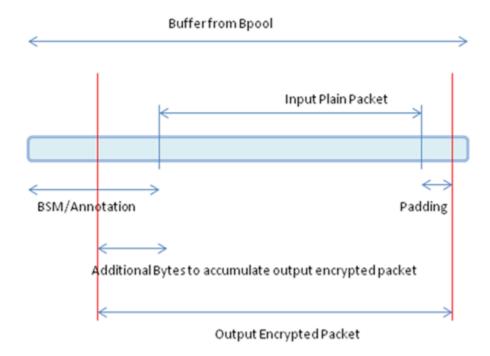

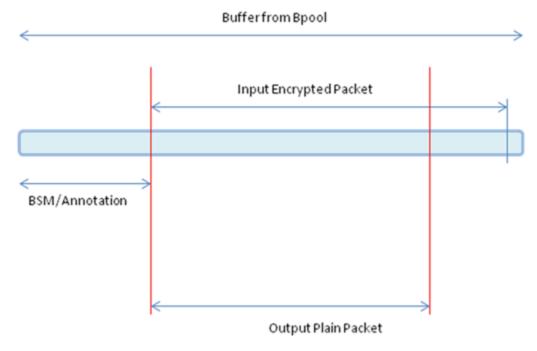

| 7.4.7.4.1 In-Place Encryption/Decryption                          | 949 |

| 7.4.7.5 Secfwd application suite                                  |     |

| 7.4.7.5.1 Using Two Computers to Test the IPFWD Application Suite | 952 |

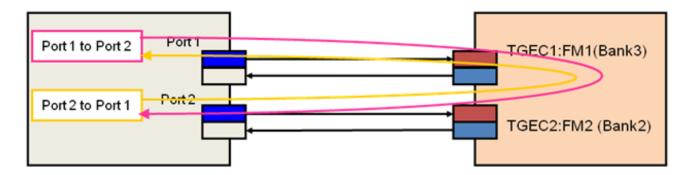

| 7.4.7.5.2 Running IPSecfwd on P4080DS board                       |     |

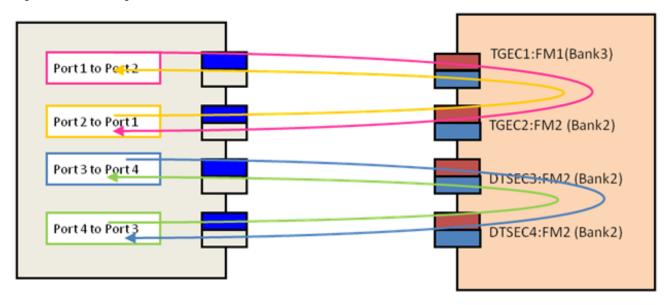

| 7.4.7.5.3 Running IPv4 forwarding on P3041/P5020 board            |     |

| 7.4.7.5.4 Running IPv4 forwarding on T4240 board                  |     |

| 7.4.7.5.5 Running IPv4 forwarding on B4860 board                  |     |

| 7.4.7.5.6 PPAC (and IPSecfwd) CLI commands                        |     |

| 7.4.7.5.7 IPSecfwd application Configuration command              |     |

| 7.4.7.6 References                                                |     |

| 7.4.7.7 Revision History                                          |     |

| 7.4.8 NXP Simple Crypto User Manual                               |     |

| 7.4.8.1 Introduction                                              |     |

| 7.4.8.2 USDPAA Simple Crypto Application                          |     |

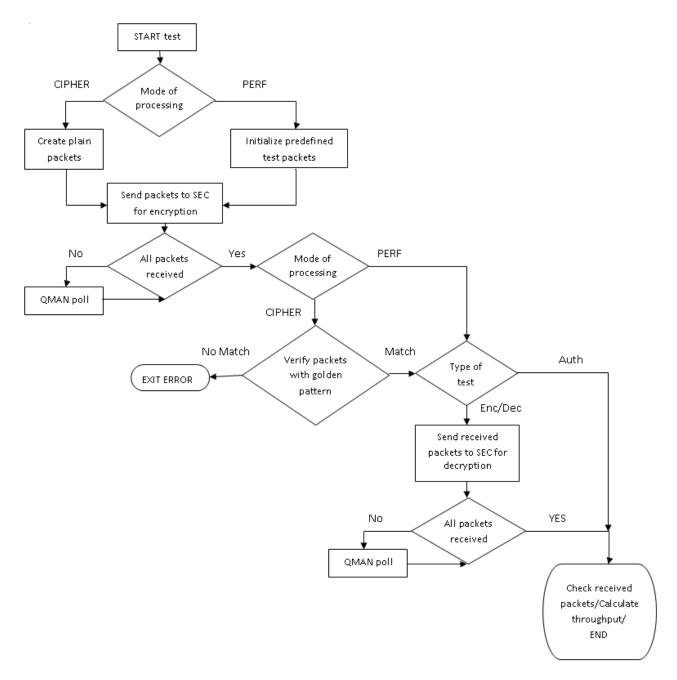

| 7.4.8.2.1 Overview                                                |     |

|                                                                   |     |

| 7.4.8.2.2 Parameters to the application                           |     |

| 7.4.8.2.3 Packet Flow                                             |     |

| 7.4.8.2.4 Throughput calculation                                  |     |

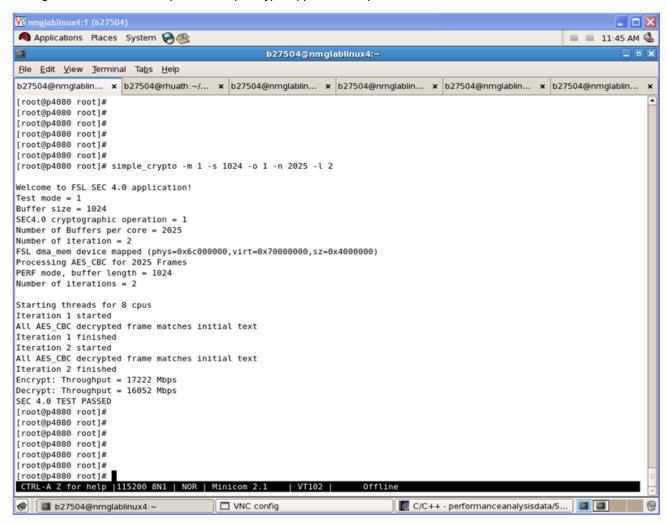

| 7.4.8.2.5 Running Simple Crypto Application on board              |     |

| 7.4.8.2.6 Simple Crypto command syntax                            |     |

| 7.4.8.2.7 Snapshot of Simple Crypto output                        |     |

| 7.4.9 NXP Simple Proto User Manual                                |     |

| 7.4.9.1 Introduction                                              |     |

| 7.4.9.2 USDPAA Simple Proto Application                           |     |

| 7.4.9.3 Overview                                                  |     |

| 7.4.9.4 Parameters to the application                             |     |

| 7.4.9.5 Packet Flow                                               |     |

| 7.4.9.6 Throughput calculation                                    |     |

| 7.4.9.7 Running Simple Proto Application on board                 |     |

| 7.4.9.8 Simple Proto command syntax                               |     |

| 7.4.9.9 MACSec protocol options                                   |     |

| 7.4.9.10 WiMAX protocol options                                   | 978 |

| 7.4.9.11 PDCP protocol options                                    | 978 |

| 7.4.9.12 RSA operations options                                   | 980 |

| 7.4.9.13 TLS protocol options                                     | 980 |

| 7.4.9.14 IPsec protocol options                                   | 981 |

| 7.4.9.15 MBMS protocol options                                    | 981 |

| 7.4.10 SEC Descriptor construction library (DCL)                  |     |

| 7.4.10.1 SEC Descriptor construction library (DCL)                |     |

| 7.4.10.2 DCL Description                                          |     |

| 7.4.10.3 DCL Packaging                                            |     |

| 7.4.10.4 DCL Files                                                |     |

| 7.4.10.5 DCL Functional Description                               |     |

| 7.4.10.6 Command Generator                                        |     |

| 7.4.10.7 Descriptor Disassembler                                  |     |

| 7.4.10.8 Upper-Tier DCL Descriptor Constructors                   |     |

| 7.4.10.9 API Reference                                            |     |

| 7.4.10.9 APT Reference Command Generator                          |     |

|                                                                   |     |

| 7.4.10.9.2 Descriptor Constructors                                | 997 |

| 7.4.10.9.3 Disassembler                                                                              | 1016                                                                            |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 7.4.11 Runtime Assembler Library Reference                                                           | 1016                                                                            |

| 7.4.11.1 Runtime Assembler Library Reference                                                         |                                                                                 |

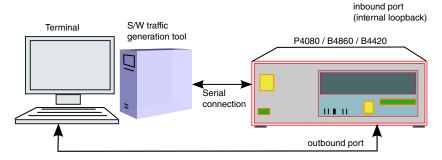

| 7.4.12 USDPAA PME Loopback User Guide                                                                |                                                                                 |

| 7.4.12.1 Introduction                                                                                |                                                                                 |

| 7.4.12.1.1 Purpose                                                                                   |                                                                                 |

| 7.4.12.1.2 Change history                                                                            |                                                                                 |

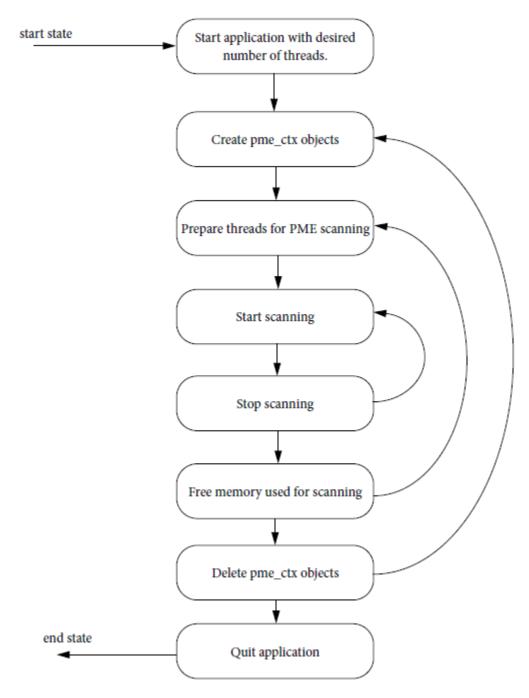

| 7.4.12.2 Overview of pme_loopback                                                                    |                                                                                 |

| 7.4.12.2.1 pme_loopback application flow                                                             |                                                                                 |

| 7.4.12.3 pme_loopback application syntax                                                             |                                                                                 |

| 7.4.12.3.1 pme_loopback_test                                                                         |                                                                                 |

| 7.4.12.3.2 create_ctx_direct_mode                                                                    |                                                                                 |

| 7.4.12.3.3 create_ctx_flow_mode                                                                      |                                                                                 |

| 7.4.12.3.4 prep_scan                                                                                 |                                                                                 |

| 7.4.12.3.5 prep_scan_2                                                                               |                                                                                 |

| 7.4.12.3.6 start_scan                                                                                |                                                                                 |

| 7.4.12.3.7 stop_scan                                                                                 |                                                                                 |

| 7.4.12.3.8 free_mem                                                                                  |                                                                                 |

| 7.4.12.3.9 delete_ctx                                                                                |                                                                                 |

| 7.4.12.3.10 rm                                                                                       |                                                                                 |

| 7.4.12.3.10 m                                                                                        |                                                                                 |

| 7.4.12.3.11 add                                                                                      |                                                                                 |

| 7.4.12.3.13 display_stats                                                                            |                                                                                 |

| 7.4.12.3.14 clear_stats                                                                              |                                                                                 |

|                                                                                                      |                                                                                 |

| 7.4.12.3.15 help                                                                                     |                                                                                 |

| 7.4.12.3.16 quit                                                                                     |                                                                                 |

| 7.4.12.4 Running pme_loopback                                                                        |                                                                                 |

| 7/10 HCDDA A IDDud Longoot Drofix Motab Hoor Manual                                                  |                                                                                 |

| 7.4.13 USDPAA IPFwd Longest Prefix Match User Manual                                                 |                                                                                 |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 1031                                                                            |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031                                                                    |

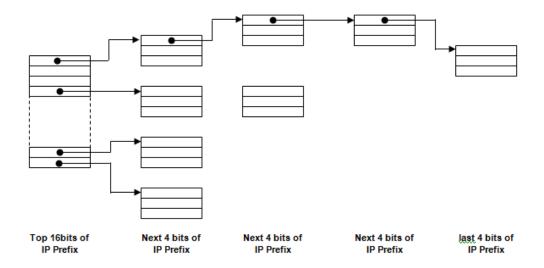

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031<br>1031                                                            |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031<br>1031<br>1032                                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031<br>1032<br>1032                                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031<br>1032<br>1032<br>1034                                            |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031<br>1032<br>1032<br>1034                                            |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031<br>1031<br>1032<br>1032<br>1034<br>1035                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031 1031 1032 1034 1035 1037                                                   |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031103110321032103510371038                                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031103110321032103510371038                                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 10311031103210321035103710381038                                                |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031 1031 1032 1032 1035 1037 1038 1038 1039                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031 1031 1032 1035 1035 1037 1038 1038 1039                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual 7.4.13.1.1 Introduction | 1031 1031 1032 1035 1035 1037 1038 1039 1039                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 1031 1031 1032 1035 1037 1038 1038 1039 1039                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 1031 1031 1032 1032 1035 1037 1038 1038 1039 1039 1039                          |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 10311031103210321035103710381039103910391039                                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 103110311032103210351037103810381039103910401042                                |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 1031 1031 1032 1035 1035 1037 1038 1039 1039 1040 1042 1048 1050                |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 10311031103210351035103610381039103910391040104210451045                        |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 10311031103210351035103610381038103910391040104210421045                        |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 103110311032103510371036103810381039103910401042104210521053                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 103110311032103510371036103810391039103910401042104210521053                    |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 1031 1031 1032 1032 1035 1037 1038 1038 1039 1039 1040 1042 1043 1053 1053 1053 |

| 7.4.13.1 NXP P4080/P5020/P3041 USDPAA IPFwd Longest Prefix Match User Manual                         | 1031 1031 1032 1032 1035 1037 1038 1038 1039 1040 1042 1043 1053 1053 1053 1053 |

| 7.4.13.1.27 Help for assign IP address to interfaces | 1057 |

|------------------------------------------------------|------|

| 7.4.13.1.28 Adding a Route Entry                     | 1057 |

| 7.4.13.1.29 Help for Route Entry Addition            | 1058 |

| 7.4.13.1.30 Deleting a Route Entry                   |      |

| 7.4.13.1.31 Help for Deleting a Route Entry          |      |

| 7.4.13.1.32 Adding an ARP Entry                      |      |

| 7.4.13.1.33 Help for ARP Entry Addition              |      |

| 7.4.13.1.34 Deleting an ARP Entry                    |      |

| 7.4.13.1.35 Help for Deleting an ARP Entry           |      |

| 7.4.13.1.36 References                               |      |

| 7.4.14 NXP USDPAA FRA Configuration User Manual      |      |

| 7.4.14.11 Introduction                               |      |

|                                                      |      |

| 7.4.14.0 FDA Our frager live                         |      |

| 7.4.14.2 FRA Configuration                           |      |

| 7.4.14.2.1 Rman_cfg Element                          |      |

| 7.4.14.2.2 Network_cfg Element                       |      |

| 7.4.14.2.3 Transaction Element                       |      |

| 7.4.14.2.4 Distribution Element                      |      |

| 7.4.14.2.5 Policy Element                            |      |

| 7.4.14.3 Revision History                            | 1071 |

| 7.4.15 NXP USDPAA FRA User Manual                    |      |

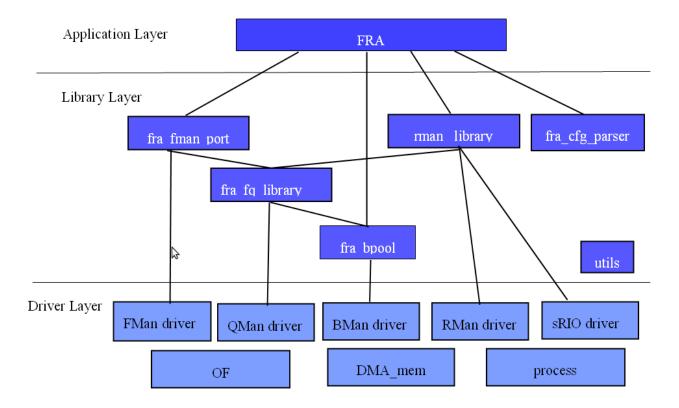

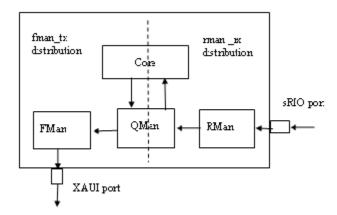

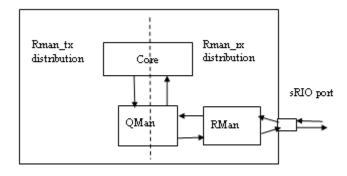

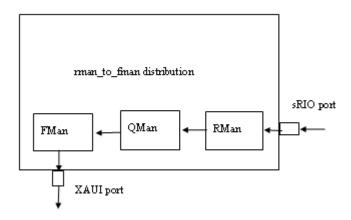

| 7.4.15.1 Overview                                    | 1072 |

| 7.4.15.2 Introduction                                | 1072 |

| 7.4.15.2.1 Purpose                                   | 1072 |

| 7.4.15.2.2 Definitions and Acronyms                  | 1072 |

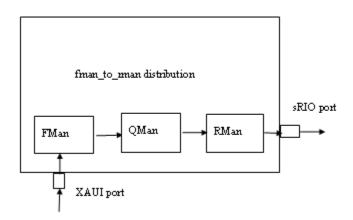

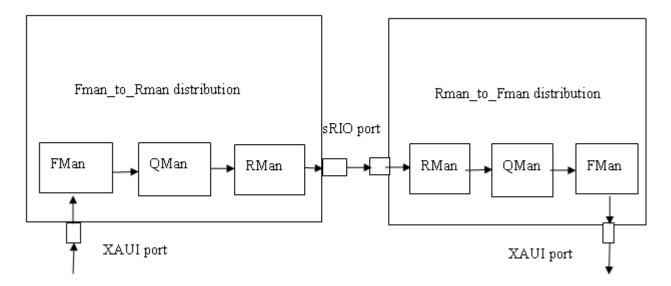

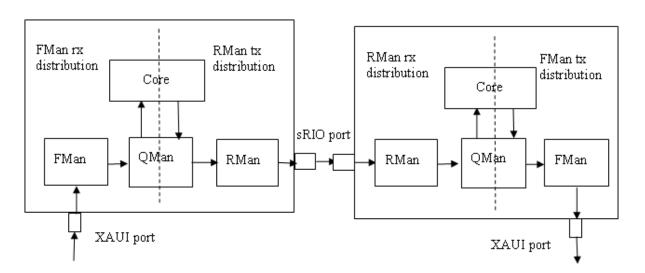

| 7.4.15.3 Overview of FRA                             | 1072 |

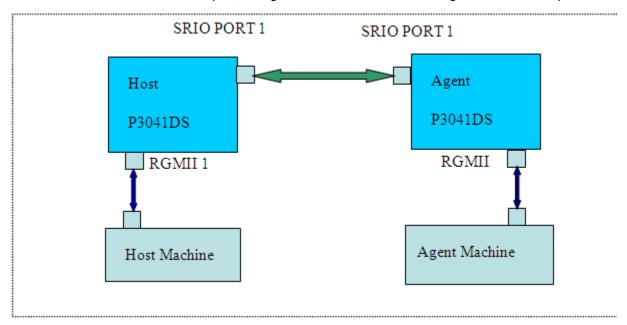

| 7.4.15.4 Running FRA on Two Boards                   | 1080 |

| 7.4.15.4.1 Installation                              | 1080 |

| 7.4.15.4.2 Compilation                               |      |

| 7.4.15.4.3 Configuring FRA                           |      |

| 7.4.15.4.4 Prepare the Hardware                      |      |

| 7.4.15.4.5 Managing RCW and U-boot Image             |      |

| 7.4.15.4.6 Booting Linux                             |      |

| 7.4.15.4.7 Running FRA                               |      |

| 7.4.15.4.8 Testing FRA                               |      |

| 7.4.15.4.9 Debugging FRA                             |      |

| 7.4.15.4.10 Testing Port Write                       |      |

| 7.4.15.5 Running FRA with flow control               |      |

| <del>-</del>                                         |      |

| 7.4.15.5.1 Booting Linux                             |      |

| 7.4.15.5.2 Compilation FRA with flow control         |      |

| 7.4.15.5.3 Running FRA                               |      |

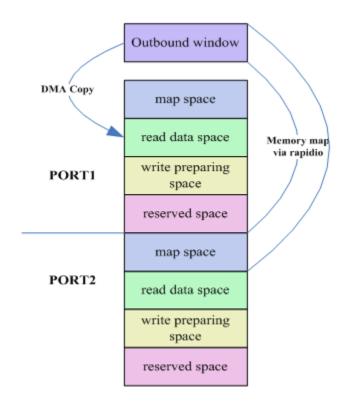

| 7.4.15.6 Running FRA on One Board                    |      |

| 7.4.15.6.1 Prepare the Hardware (one board)          |      |

| 7.4.15.6.2 Configuring FRA (one board)               |      |

| 7.4.15.6.3 Managing RCW                              |      |

| 7.4.15.6.4 Running FRA                               |      |

| 7.4.15.6.5 Testing FRA (one board)                   |      |

| 7.4.15.7 Revision History                            |      |

| 7.4.16 NXP USDPAA SRA User Manual                    |      |

| 7.4.16.1 Serial RapidIO application                  |      |

| 7.4.16.1.1 Overview                                  |      |

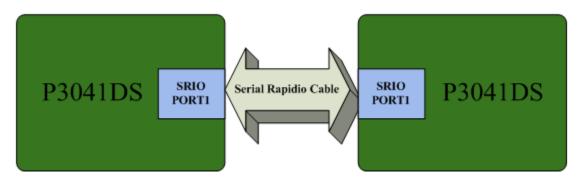

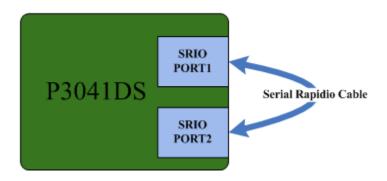

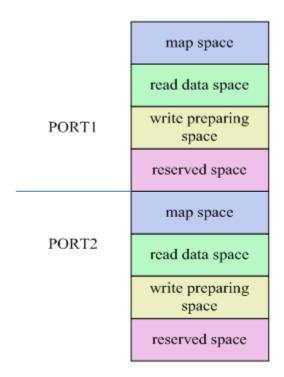

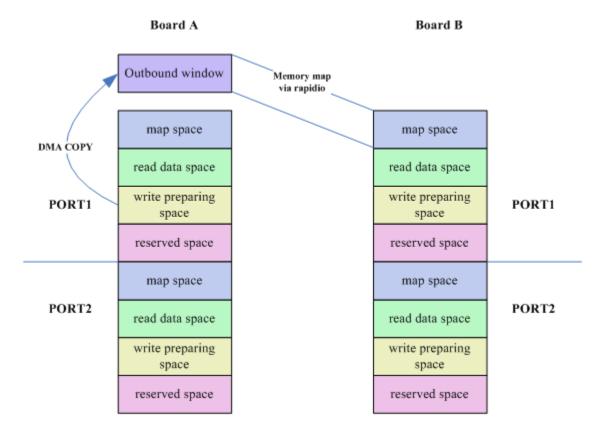

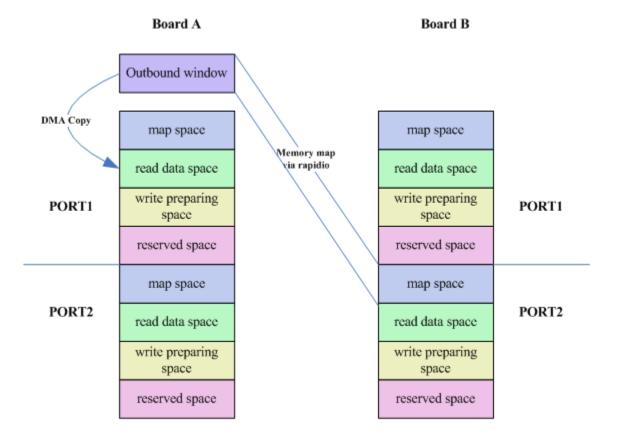

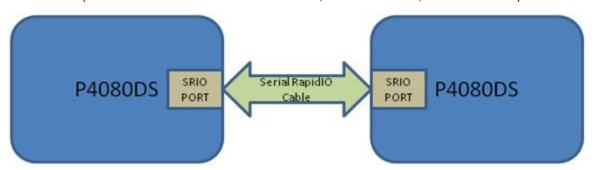

| 7.4.16.1.2 SRA environment setup                     | 1096 |

| 7.4.16.1.3 Boot                                      | 1099 |

| 7.4.16.1.4 SRA Demo                                  | 1099 |

| 7.4.16.1.5 SRA Command Description                   | 1100 |

|                                               | 7.4.16.1.6 SRA command Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1101                                                                  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                               | 7.4.16.1.7 Run SRA Demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1105                                                                  |

|                                               | 7.4.16.2 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1108                                                                  |

| 7.4.1                                         | 7 USDPAA RMU User Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1109                                                                  |

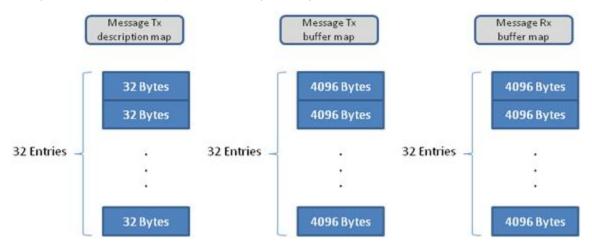

|                                               | 7.4.17.1 RapidIO Message Unit Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       |

|                                               | 7.4.17.2 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                       |

|                                               | 7.4.17.3 RMU Environment Setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |

|                                               | 7.4.17.3.1 Hardware Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |

|                                               | 7.4.17.3.2 SDK Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                       |

|                                               | 7.4.17.3.3 RCW Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |

|                                               | 7.4.17.3.4 Kernel Building Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       |

|                                               | 7.4.17.4 Boot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                       |

|                                               | 7.4.17.5 RMU Demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                       |

|                                               | 7.4.17.6 RMU Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                       |

|                                               | 7.4.17.7 Run RMU Demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                       |

| 7.4.1                                         | 8 USDPAA SRIO IPSec Offload User Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                       |

|                                               | 7.4.18.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                       |

|                                               | 7.4.18.2 Overview of srio_ipsec_offlaod demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1117                                                                  |

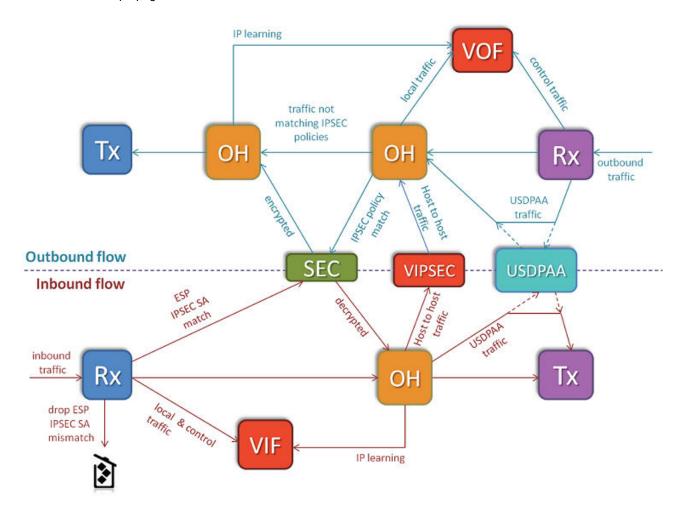

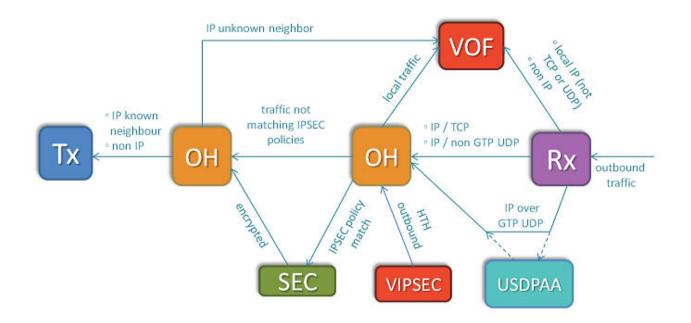

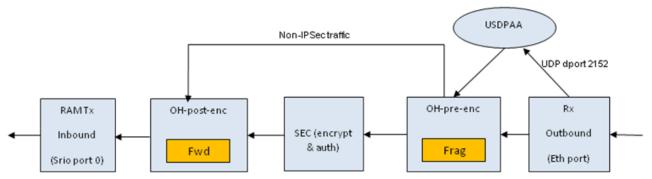

|                                               | 7.4.18.2.1 Srio_IPSec_offload outbound flows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1118                                                                  |

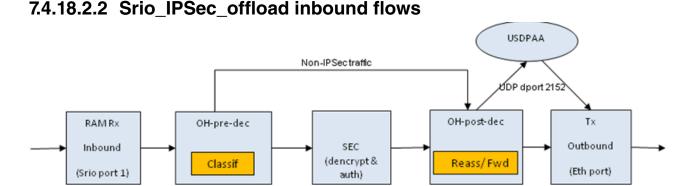

|                                               | 7.4.18.2.2 Srio_IPSec_offload inbound flows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1118                                                                  |

|                                               | 7.4.18.2.3 Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1118                                                                  |

|                                               | 7.4.18.3 Running srio_ipsec_offload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1119                                                                  |

|                                               | 7.4.18.3.1 Application environment specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                       |

|                                               | 7.4.18.3.2 Running srio_ipsec_offload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                       |

|                                               | 7.4.18.3.3 Application configuration for IPsec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

|                                               | 7.4.18.3.4 Running Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |

|                                               | 7.4.18.4 Compiling the device tree and enabling kernel options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

|                                               | 7.4.18.4.1 Compiling the device tree for B4860                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

|                                               | 7. 1. 10. 1. 1 Complining the device tree for B 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1120                                                                  |

|                                               | 74 18 4.2 Enabling DPA Offloading and RMAN Drivers in the Linux Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1121                                                                  |