Design Workbook

MVPX2DW/D Rev. 0.3, 11/2001

MVP X2 Multiprocessor **Evaluation System** Design Workbook

Gary Milliorn CPD Applications

# Introduction

This document describes the design information on the MVP reference platform. MVP, short for Multiprocessing Verification Platform, is a dual-processor MPC7450-based platform which allows evaluation of the 60X or MPX bus interfaces. It provides all necessary computing platform devices needed to boot Linux, QNX, VxWorks, or other OSes.

This version of the design document describes the "X2" version, which has slight architectural changes over the first X1 version.

## 1.1 Features

The MVP includes the following features:

- Two MPC745X Processors (MPC7450 or MPC7451 "V'ger" or compatible)

- 2MB pipelined-burst (PB) L3 Cache

- GD64260 System Controller ("Discovery")

- Dual Processor (60X bus mode) or Single-processor (MPX bus mode) interface

- SDRAM controller

- Dual PCI Interfaces

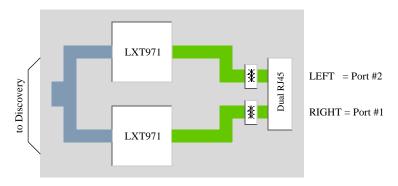

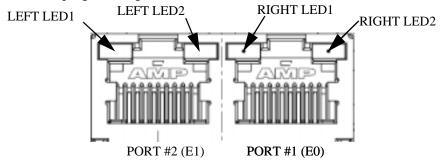

- Dual 10/100base-T Ethernet interfaces

- Dual serial ports

- SDRAM Modules

- 2 PC133 SDRAM DIMM sockets

- 2GB maximum memory (256MB standard)

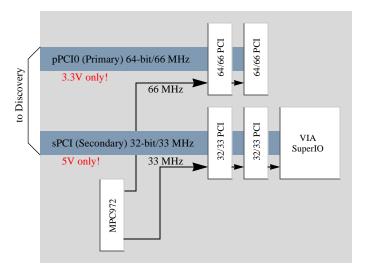

- PCI Interface #1

- Two slots, 32 or 64 bit, 66 MHz, 3V

- PCI Interface #2

- Two slots, 32 bit, 33 MHz, 5V

- Super IO

- Dual USB 1.0/UHCI v1.1 interface

- Dual UltraDMA 33 IDE Disk interface

- PS/2 keyboard and mouse interfaces

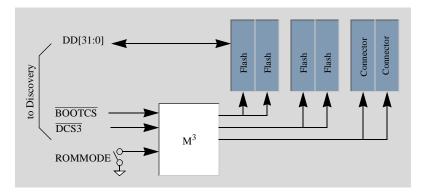

- Flash/ROM Interface

- 32-bit Boot ROM (1-16 MB, 8 MB standard)

- 32-bit OS/User ROM (1-16 MB, 8 MB standard)

- Ethernet

- Dual 10/100baseT Ethernet

- Dual UART

- Standard 9-pin serial port, baud rates up to ~500kpbs

- Power Supplies

- Individual 18A 1.3 to 2.5V switching power supplies for each MPC7450

- Adjustable 10A 1.8V and 2.5V switching power supplies for L3 cache, Discovery, etc.

- ATX Motherboard Form-factor

## 1.2 Overview

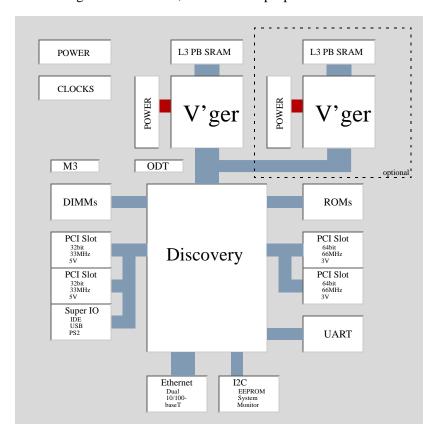

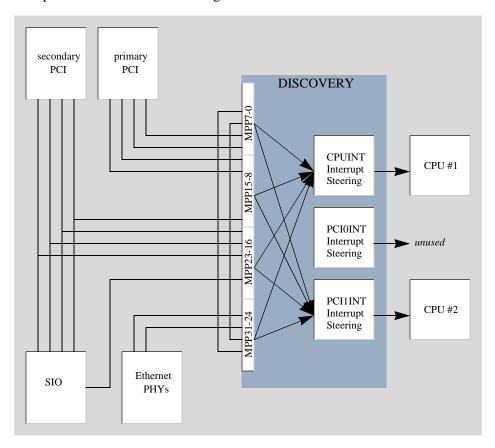

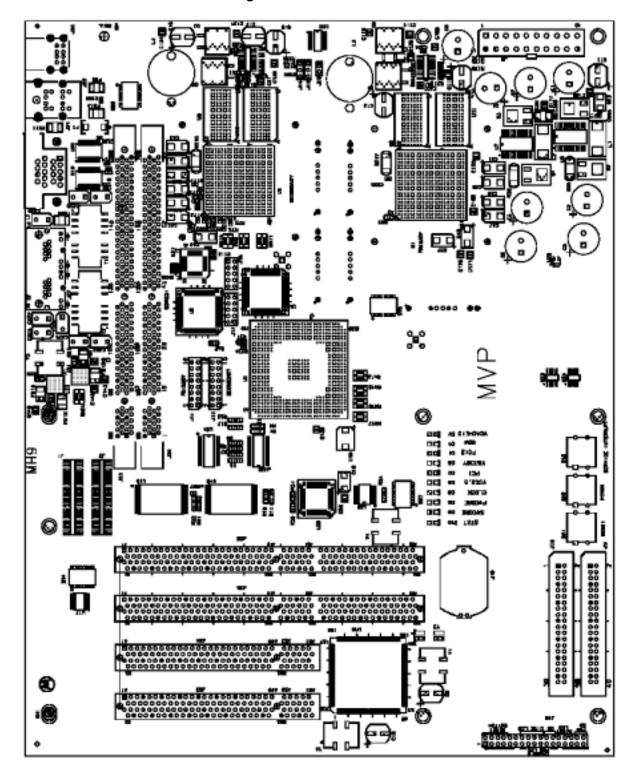

Figure 1 shows a block diagram of the MVP, for reference purposes.

Figure 1. MVP Block Diagram

# 1.3 Difference between X1 and X2

This version of the MVP Design Document has been adjusted to accommodate revisions between X1 and X2. The board is architecturally similar, but numerous changes and enhancements were made, as described in Table 2.

|             | Table 1. MV1 AT to AZ Gridinges |                                                                                                                               |  |  |  |  |

|-------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Category    | Version                         | Change                                                                                                                        |  |  |  |  |

| Memory      | X1                              | Cannot detect registered DIMMs Bank selects are interleaved: CS0/2 for DIMM #1, CS1/3 for DIMM #2.                            |  |  |  |  |

|             | X2                              | Can detect registered DIMMs via GPIO bit.<br>Bank selects are linear: CS0/1 for DIMM #1, CS2/3 for<br>DIMM #2.                |  |  |  |  |

| Serial Port | X1                              | UART baud rate generator must be clocked from bus clock. Serial port speed changes with bus speed.                            |  |  |  |  |

|             | X2                              | Baud rate generator can be clocked from constant 14.318MHz clock. Serial port speed settings are invariant against bus speed. |  |  |  |  |

Table 1. MVP X1 to X2 Changes

### Difference between X1 and X2

Table 1. MVP X1 to X2 Changes

| Category | Version | Change                                                                                             |

|----------|---------|----------------------------------------------------------------------------------------------------|

| ARB      | X1      | Requires external arbiter for MP-60X systems.<br>Second CPU enabled via MPP port bit.              |

|          | X2      | Uses internal arbiter for MP-60X systems.<br>Second CPU enabled via internal GT64260 register bit. |

| Config   | X1      | Uses pullup/pulldown resistors to configure all GT64260 bits.                                      |

|          | X2      | Most options fixed to defaults, others have switch settings.                                       |

| Clock    | X1      | Uses SDCLK_OUT from Galileo to drive SDRAM.                                                        |

|          | X2      | Uses TCLK from main clock to drive SDRAM.                                                          |

| GT64260  | X1      | Uses 'rev 0'.                                                                                      |

|          | X2      | Uses 'rev A'.                                                                                      |

|          | X1      | Default register base: 0x1400_0000                                                                 |

|          | X2      | Default register base: 0xF100_0000                                                                 |

## 2 Architecture

The following sections cover the MVP design in more detail. To describe the MVP system details, it is (perhaps) useful to track what devices are present on particular buses. The buses described in Table 2 are present on the MVP system.

**Table 2. MVP Bus Architecture**

| Bus       | Connections                                                               | Size                                                              | Max. Speed | Description                | Notes |

|-----------|---------------------------------------------------------------------------|-------------------------------------------------------------------|------------|----------------------------|-------|

| Processor | CPU #1<br>CPU #2<br>Discovery<br>Mictor Debug Headers                     | 32-bit address 4-bit address parity 64-bit data 8-bit data parity | 133 MHz    | 60X or MPX bus             |       |

| Cache     | CPU #1<br>CPU #2<br>PB SRAM                                               | 22-bit address<br>64-bit data<br>8-bit data parity                | 200 MHz    | Cache data bus             |       |

| Memory    | SDRAM DIMM #1<br>SDRAM DIMM #2                                            | 64 bits<br>8 parity/ECC bits                                      | 133 MHz    | SDRAM bus                  |       |

| Device    | Boot ROM #1<br>Aux ROM #2                                                 | 32-bits                                                           | 100 MHz    | IO bus                     |       |

| Fast PCI  | PCI Slot #1<br>PCI Slot #2                                                | 64-bits                                                           | 66 MHz     | Primary PCI bus            |       |

| Slow PCI  | PCI Slot #3<br>PCI Slot #4<br>SuperIO                                     | 32-bits                                                           | 33 MHz     | Secondary PCI bus          |       |

| I2C       | DIMM #1 SPD EEPROM<br>DIMM #2 SPD EEPROM<br>Info EEPROM<br>System Monitor | 2 bits                                                            | 1 MHz      | I <sup>2</sup> C bus       |       |

| MII       | PHY #1<br>PHY #2                                                          | 15 bits                                                           | 25 MHz     | Interface to Ethernet PHYs |       |

| Serial    | Serial #1<br>Serial #2                                                    | 5 bits                                                            | 500 kbps   | Serial ports               |       |

| USB       | USB #1<br>USB #2                                                          | 4 bits                                                            | 1.5 Mbps   | USB 1.1 Host Port          |       |

| PS/2      | PS/2 Keyboard<br>PS/2 Mouse                                               | 4 bits                                                            | ~100 kbps  | PS/2 Peripheral Port       |       |

# 2.1 Processors

The MVP platform supports two MPC7450 "V'ger" processors. The system bus interface connects between the two V'ger processors and the "Discovery" system controller, using either the MPX bus protocol or the 60X bus protocol.

## 2.1.1 BVSEL/L2VSEL

In addition to bus mode configuration, the V'ger processor must be configured for bus I/O voltage (BVSEL) and L3 I/O voltage (L3VSEL). MVP only supports 2.5V I/O on the system bus (for Discovery

#### **System Controller**

compatibility) and 2.5V I/O on the L3 bus (for PB2 compatibility), so these options are not switch/resistors selectable on MVP.

### 2.1.2 **BMODE**

The V'ger BMODE pins are controlled to select both the bus mode (MPX or 60X) and the processor ID. Processor ID is controlled with hardware, but bus mode is switch-selectable (however, changing bus mode requires changing two separate switches - see section 3 for details).

**BMODE0 BMODE1 Processor Bus Mode Processor ID** V'ger #1 0 (ON) OVDD MPX Bus 0 V'ger #1 1 (OFF) **OVDD** 60X Bus 0 V'ger #2 0 (ON) not HRESET MPX Bus 1 not HRESET V'ger #2 1 (OFF) 60X Bus

Table 3. V'Ger Bus Mode/ID Selection

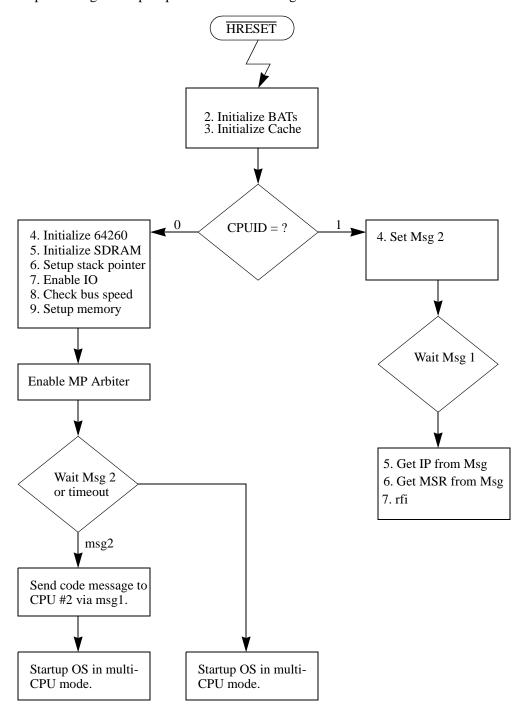

Each processor detects its own ID by examining bit 26 (CPUID) of the MSSCR0 register.

### 2.1.3 L3 Cache

Each V'ger processor has a 2MB back-side L3 cache, implemented with two (2) 8Mbit PB SRAM devices operating in the range of 133-200 MHz. The maximum speed of the L3 on MVP will depend upon parts used and may vary subject to availability.

The L3 SRAMs require a 3.3V core power supply and use 2.5V I/O signalling, compatible with V'ger. No other voltage options are provided for.

# 2.2 System Controller

The system controller is the Galileo GT64260 "Discovery", which provides the following features:

- Multiprocessing 60X bus OR Single-processor MPX bus

- SDRAM memory controller, 133 MHz

- Dual 10/100-base-T Ethernet ports

- Dual serial ports

- I2C interface

- Interrupt Controller

- PCI Bus arbiters

The GT64260 does not support two processors in MPX bus protocol, so the Discovery must be configured to single-processor mode when MPX bus mode is configured (section 3).

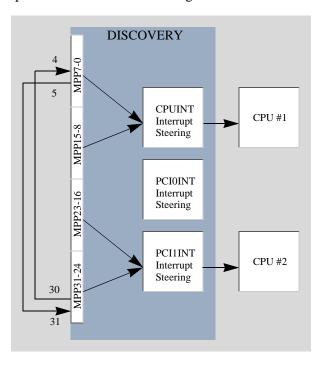

## 2.2.1 Discovery MPP Configuration

Discovery provides many more features than pins. To use particular functions, the MPP (Multi-Purpose Port) must be programmed to provide one of 16 selectable functions per port pin. MVP relies on each MPP

port being set to the proper configuration option as described in Table 4; otherwise, the system may not operate properly.

Table 4. MVP MPP Usage

| MPP Bit   MPP Definition   MPP Programming   Usage   Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                | Table 4. WIVI  | Joago                             |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|----------------|-----------------------------------|-------|

| 1 REQ0[0]* MPPCTL0[7:4] pPCI slot 1 REQ# 2 GNT0[1]* MPPCTL0[11:8] pPCI slot 2 GNT# 3 REQ0[1]* MPPCTL0[15:12] pPCI slot 2 GNT# 4 GPP[4] MPPCTL0[19:16] Cross-processor 1->0 interrupt 5 GPP[6] MPPCTL0[23:20] Cross-processor 0->1 output drive 6 GPP[6] MPPCTL0[27:24] pPCI INT 0 (Slot 1 INTA#, Slot 2 INTD#) 7 GPP[7] MPPCTL0[31:28] pPCI INT 1 (Slot 1 INTB#, Slot 2 INTA#) 8 GPP[8] MPPCTL1[3:0] pPCI INT 2 (Slot 1 INTC#, Slot 2 INTA#) 9 GPP[9] MPPCTL1[7:4] pPCI INT 3 (Slot 1 INTD#, Slot 2 INTB#) 10 GPP[10] MPPCTL1[11:8] sPCI INT 0 (Slot 3 INTA#, Slot 4 INTD#) 11 GPP[11] MPPCTL1[15:12] sPCI INT 1 (Slot 3 INTB#, Slot 4 INTB#) 12 GPP[12] MPPCTL1[19:16] sPCI INT 1 (Slot 3 INTC#, Slot 4 INTB#) 13 GPP[13] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTB#) 14 GPP[14] MPPCTL1[27:24] PHY1 INT* 15 GPP[15] MPPCTL1[27:24] PHY1 INT* 16 GNT1[0]* MPPCTL2[7:4] sPCI slot 3 GNT# 17 REQ1[0]* MPPCTL2[7:4] sPCI slot 3 GNT# 18 GNT1[1]* MPPCTL2[11:8] sPCI slot 3 GNT# 19 REQ1[1]* MPPCTL2[11:8] sPCI slot 4 GNT# 19 REQ1[1]* MPPCTL2[15:12] sPCI slot 4 GNT# 19 REQ1[1]* MPPCTL2[15:12] sPCI slot 4 REQ# 20 GNT2[1]* MPPCTL2[23:20] sPCI slot 6 GNT# 21 REQ2[1]* MPPCTL2[23:20] sPCI Slo GNEQ# 22 GPP[22] MPPCTL2[27:24] SIOINT 1 23 GPP[23] MPPCTL2[27:24] SIOINT 1 24 GPP[24] MPPCTL2[27:24] SIOINT 1 25 GPP[25] MPPCTL2[31:28] BG1_EN 2 24 GPP[24] MPPCTL3[3:0] SYSSTAT 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MPP Bit | MPP Definition |                | Usage                             | Notes |

| 2 GNT0[1]* MPPCTL0[11:8] pPCI slot 2 GNT#  3 REQ0[1]* MPPCTL0[15:12] pPCI slot 2 REQ#  4 GPP[4] MPPCTL0[19:16] Cross-processor 1->0 interrupt  5 GPP[6] MPPCTL0[23:20] Cross-processor 0->1 output drive  6 GPP[6] MPPCTL0[27:24] pPCI INT 0 (Slot 1 INTA#, Slot 2 INTA#)  7 GPP[7] MPPCTL0[31:28] pPCI INT 1 (Slot 1 INTB#, Slot 2 INTA#)  8 GPP[8] MPPCTL1[3:0] pPCI INT 2 (Slot 1 INTC#, Slot 2 INTA#)  9 GPP[9] MPPCTL1[7:4] pPCI INT 3 (Slot 1 INTD#, Slot 2 INTA#)  10 GPP[10] MPPCTL1[11:8] sPCI INT 3 (Slot 1 INTD#, Slot 4 INTA#)  11 GPP[11] MPPCTL1[15:12] sPCI INT 1 (Slot 3 INTB#, Slot 4 INTA#)  12 GPP[12] MPPCTL1[19:16] sPCI INT 2 (Slot 3 INTC#, Slot 4 INTB#)  13 GPP[13] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTB#)  14 GPP[14] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)  15 GPP[15] MPPCTL1[27:24] PHY1 INT*  16 GNT1[0]* MPPCTL2[3:0] sPCI Slot 3 GNT#  17 REQ1[0]* MPPCTL2[7:4] sPCI Slot 3 GNT#  18 GNT1[1]* MPPCTL2[1:18] sPCI Slot 3 GNT#  19 REQ1[1]* MPPCTL2[1:18] sPCI Slot 4 REQ#  20 GNT2[1]* MPPCTL2[15:12] sPCI Slot 6 REQ#  21 REQ2[1]* MPPCTL2[23:20] sPCI Slo GNT#  22 GPP[22] MPPCTL2[21:28] BG1_EN  23 GPP[23] MPPCTL2[31:28] BG1_EN  24 GPP[24] MPPCTL3[3:0] SYSSTAT  3 GPP[25] MPPCTL3[7:4] REGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0       | GNT0[0]*       | MPPCTL0[3:0]   | pPCI slot 1 GNT#                  |       |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | REQ0[0]*       | MPPCTL0[7:4]   | pPCI slot 1 REQ#                  |       |

| 4 GPP[4] MPPCTL0[19:16] Cross-processor 1->0 interrupt  5 GPP[5] MPPCTL0[23:20] Cross-processor 0->1 output drive  6 GPP[6] MPPCTL0[27:24] PPCI INT 0 (Slot 1 INTA#, Slot 2 INTD#)  7 GPP[7] MPPCTL0[31:28] PPCI INT 1 (Slot 1 INTB#, Slot 2 INTD#)  8 GPP[8] MPPCTL1[3:0] PPCI INT 2 (Slot 1 INTC#, Slot 2 INTB#)  9 GPP[9] MPPCTL1[7:4] PPCI INT 3 (Slot 1 INTD#, Slot 2 INTC#)  10 GPP[10] MPPCTL1[11:8] SPCI INT 0 (Slot 3 INTA#, Slot 4 INTD#)  11 GPP[11] MPPCTL1[15:12] SPCI INT 3 (Slot 3 INTA#, Slot 4 INTD#)  12 GPP[12] MPPCTL1[15:12] SPCI INT 1 (Slot 3 INTE#, Slot 4 INTA#)  13 GPP[13] MPPCTL1[23:20] SPCI INT 3 (Slot 3 INTC#, Slot 4 INTE#)  14 GPP[14] MPPCTL1[27:24] PHY1 INT*  15 GPP[15] MPPCTL1[31:28] PHY2 INT*  16 GNT1[0]* MPPCTL2[3:0] SPCI Slot 3 GNT#  17 REQ1[0]* MPPCTL2[3:0] SPCI Slot 3 GNT#  18 GNT1[1]* MPPCTL2[11:8] SPCI Slot 4 GNT#  19 REQ1[1]* MPPCTL2[11:8] SPCI Slot 4 GNT#  20 GNT2[1]* MPPCTL2[15:12] SPCI Slot 4 GNT#  21 REQ2[1]* MPPCTL2[15:12] SPCI Slot 6 GNT#  22 GPP[22] MPPCTL2[3:20] SPCI Slot REQ#  23 GPP[23] MPPCTL2[3:20] SPCI Slot REQ#  24 GPP[24] MPPCTL2[3:12] BG1_EN  25 GPP[25] MPPCTL3[3:0] SYSSTAT  3 GPGI Slot A REGE  5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2       | GNT0[1]*       | MPPCTL0[11:8]  | pPCI slot 2 GNT#                  |       |

| 5 GPP[5] MPPCTL0[23:20] Cross-processor 0->1 output drive 6 GPP[6] MPPCTL0[27:24] pPCI INT 0 (Slot 1 INTA#, Slot 2 INTD#) 7 GPP[7] MPPCTL0[31:28] pPCI INT 1 (Slot 1 INTA#, Slot 2 INTA#) 8 GPP[8] MPPCTL1[3:0] pPCI INT 2 (Slot 1 INTC#, Slot 2 INTA#) 9 GPP[9] MPPCTL1[7:4] pPCI INT 3 (Slot 1 INTD#, Slot 2 INTB#) 10 GPP[10] MPPCTL1[11:8] sPCI INT 0 (Slot 3 INTA#, Slot 4 INTD#) 11 GPP[11] MPPCTL1[15:12] sPCI INT 1 (Slot 3 INTA#, Slot 4 INTD#) 12 GPP[12] MPPCTL1[19:16] sPCI INT 1 (Slot 3 INTC#, Slot 4 INTA#) 13 GPP[13] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#) 14 GPP[14] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#) 15 GPP[15] MPPCTL1[31:28] PHY2 INT* 16 GNT1[0]* MPPCTL2[3:0] sPCI slot 3 GNT# 17 REC1[0]* MPPCTL2[3:0] sPCI slot 3 REQ# 18 GNT1[1]* MPPCTL2[7:4] sPCI slot 3 REQ# 19 REQ1[1]* MPPCTL2[15:12] sPCI slot 4 REQ# 20 GNT2[1]* MPPCTL2[19:16] sPCI Slot 4 REQ# 21 REQ2[1]* MPPCTL2[23:20] sPCI Slot REQ# 22 GPP[22] MPPCTL2[27:24] SIOINT 1 REQ2[1]* MPPCTL2[27:24] SIOINT 1 REQ2[1]* MPPCTL2[27:24] SIOINT 1 REQ2[1]* MPPCTL2[27:24] SIOINT 1 REQ2[1]* MPPCTL2[27:24] SIOINT 1 AREGE 2 GPP[23] MPPCTL2[31:28] BG1_EN 2 GPP[24] MPPCTL3[31:0] SYSSTAT 3 GPP[25] MPPCTL3[7:4] REGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3       | REQ0[1]*       | MPPCTL0[15:12] | pPCI slot 2 REQ#                  |       |

| 6 GPP[6] MPPCTL0[27:24] pPCI INT 0 (Slot 1 INTA#, Slot 2 INTD#)  7 GPP[7] MPPCTL0[31:28] pPCI INT 1 (Slot 1 INTB#, Slot 2 INTA#)  8 GPP[8] MPPCTL1[3:0] pPCI INT 2 (Slot 1 INTC#, Slot 2 INTA#)  9 GPP[9] MPPCTL1[7:4] pPCI INT 3 (Slot 1 INTD#, Slot 2 INTB#)  10 GPP[10] MPPCTL1[11:8] sPCI INT 0 (Slot 3 INTA#, Slot 4 INTD#)  11 GPP[11] MPPCTL1[15:12] sPCI INT 1 (Slot 3 INTB#, Slot 4 INTD#)  12 GPP[12] MPPCTL1[19:16] sPCI INT 1 (Slot 3 INTC#, Slot 4 INTB#)  13 GPP[13] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)  14 GPP[14] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)  15 GPP[15] MPPCTL1[23:20] sPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)  16 GNT1[0]* MPPCTL2[3:0] sPCI Slot 3 GNT#  17 REC1[0]* MPPCTL2[3:0] sPCI slot 3 GNT#  18 GNT1[1]* MPPCTL2[7:4] sPCI slot 3 REQ#  19 REQ1[1]* MPPCTL2[15:12] sPCI slot 4 REQ#  20 GNT2[1]* MPPCTL2[19:16] sPCI Slot 4 REQ#  21 REQ2[1]* MPPCTL2[23:20] sPCI Slot REQ#  22 GPP[22] MPPCTL2[27:24] SIOINT  1 REQ2[1]* MPPCTL2[27:24] SIOINT  1 REQ2[1]* MPPCTL2[23:20] SPCI SIO REQ#  22 GPP[23] MPPCTL2[27:24] SIOINT  1 GPP[24] MPPCTL2[31:28] BG1_EN  2 GPP[25] MPPCTL2[31:28] SPCI SIO REQ#  2 GPP[26] MPPCTL2[31:28] SPCI SIO REQ#  3 GPP[27] MPPCTL2[31:28] SPCI SIOINT  4 GPP[28] MPPCTL2[31:28] SPCI SIOINT  4 GPP[28] MPPCTL2[31:28] SPCI SIOINT  5 GPP[28] MPPCTL2[31:28] SPCI SIOINT  5 GPP[28] MPPCTL2[31:28] SPCI SIOINT  5 GPP[28] MPPCTL2[31:28] SPCI SIOINT  6 GPP[30] SPCI SIOINT  7 GPP[30] SPCI SIOINT  8 GPP[30] MPPCTL2[31:28] SPCI SIOINT  9 GPCI SIOINT  9 GPCI INT 2 (Slot 1 INTC#, Slot 2 INTC#, Slot 2 INTC#  1 GPP[30] SPCI SIOINT  1 GPP[30] SP | 4       | GPP[4]         | MPPCTL0[19:16] | Cross-processor 1->0 interrupt    |       |

| INTD#)   To all the content of the   | 5       | GPP[5]         | MPPCTL0[23:20] | Cross-processor 0->1 output drive |       |

| SPP[8]   MPPCTL1[3:0]   PPCI INT 2 (Slot 1 INTC#, Slot 2 INTB#)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6       | GPP[6]         | MPPCTL0[27:24] | · ·                               |       |

| NTB#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7       | GPP[7]         | MPPCTL0[31:28] |                                   |       |

| INTC#    INTC#    INTC#    INTC#    INTC#    INTC#    INTC#    INTC#    INTC#    INTD#    INTO#    INTD#    INTO#    INTD#    I   | 8       | GPP[8]         | MPPCTL1[3:0]   | · ·                               |       |

| INTD#)   11   GPP[11]   MPPCTL1[15:12]   SPCI INT 1 (Slot 3 INTB#, Slot 4 INTA#)   12   GPP[12]   MPPCTL1[19:16]   SPCI INT 2 (Slot 3 INTC#, Slot 4 INTB#)   13   GPP[13]   MPPCTL1[23:20]   SPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)   14   GPP[14]   MPPCTL1[27:24]   PHY1 INT*     15   GPP[15]   MPPCTL1[31:28]   PHY2 INT*     16   GNT1[0]*   MPPCTL2[3:0]   SPCI Slot 3 GNT#     17   REQ1[0]*   MPPCTL2[7:4]   SPCI Slot 3 REQ#     18   GNT1[1]*   MPPCTL2[11:8]   SPCI Slot 4 GNT#     19   REQ1[1]*   MPPCTL2[15:12]   SPCI Slot 4 REQ#     20   GNT2[1]*   MPPCTL2[19:16]   SPCI Slo GNT#     21   REQ2[1]*   MPPCTL2[23:20]   SPCI Slo REQ#     22   GPP[22]   MPPCTL2[27:24]   SIOINT   1     23   GPP[23]   MPPCTL2[31:28]   BG1_EN   2     24   GPP[24]   MPPCTL3[3:0]   SYSSTAT   3     25   GPP[25]   MPPCTL3[7:4]   REGE   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9       | GPP[9]         | MPPCTL1[7:4]   |                                   |       |

| INTA#)   12   GPP[12]   MPPCTL1[19:16]   SPCI INT 2 (Slot 3 INTC#, Slot 4 INTB#)   13   GPP[13]   MPPCTL1[23:20]   SPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)   14   GPP[14]   MPPCTL1[27:24]   PHY1 INT*   15   GPP[15]   MPPCTL1[31:28]   PHY2 INT*   16   GNT1[0]*   MPPCTL2[3:0]   SPCI Slot 3 GNT#   17   REQ1[0]*   MPPCTL2[7:4]   SPCI Slot 3 REQ#   18   GNT1[1]*   MPPCTL2[11:8]   SPCI Slot 4 GNT#   19   REQ1[1]*   MPPCTL2[15:12]   SPCI Slot 4 REQ#   20   GNT2[1]*   MPPCTL2[19:16]   SPCI SlO GNT#   21   REQ2[1]*   MPPCTL2[23:20]   SPCI SlO REQ#   22   GPP[22]   MPPCTL2[27:24]   SIOINT   1   23   GPP[23]   MPPCTL2[31:28]   BG1_EN   2   24   GPP[24]   MPPCTL3[7:4]   REGE   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10      | GPP[10]        | MPPCTL1[11:8]  |                                   |       |

| INTB#)   13   GPP[13]   MPPCTL1[23:20]   SPCI INT 3 (Slot 3 INTD#, Slot 4 INTC#)   14   GPP[14]   MPPCTL1[27:24]   PHY1 INT*     15   GPP[15]   MPPCTL1[31:28]   PHY2 INT*     16   GNT1[0]*   MPPCTL2[3:0]   SPCI Slot 3 GNT#     17   REQ1[0]*   MPPCTL2[7:4]   SPCI Slot 3 REQ#     18   GNT1[1]*   MPPCTL2[11:8]   SPCI Slot 4 GNT#     19   REQ1[1]*   MPPCTL2[15:12]   SPCI Slot 4 REQ#     20   GNT2[1]*   MPPCTL2[19:16]   SPCI SlO GNT#     21   REQ2[1]*   MPPCTL2[23:20]   SPCI SlO REQ#     22   GPP[22]   MPPCTL2[27:24]   SIOINT   1     23   GPP[23]   MPPCTL2[31:28]   BG1_EN   2     24   GPP[24]   MPPCTL3[7:4]   REGE   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11      | GPP[11]        | MPPCTL1[15:12] |                                   |       |

| INTC#)   14   GPP[14]   MPPCTL1[27:24]   PHY1 INT*     15   GPP[15]   MPPCTL1[31:28]   PHY2 INT*     16   GNT1[0]*   MPPCTL2[3:0]   sPCI slot 3 GNT#     17   REQ1[0]*   MPPCTL2[7:4]   sPCI slot 3 REQ#     18   GNT1[1]*   MPPCTL2[11:8]   sPCI slot 4 GNT#     19   REQ1[1]*   MPPCTL2[15:12]   sPCI slot 4 REQ#     20   GNT2[1]*   MPPCTL2[19:16]   sPCI SIO GNT#     21   REQ2[1]*   MPPCTL2[23:20]   sPCI SIO REQ#     22   GPP[22]   MPPCTL2[27:24]   SIOINT   1     23   GPP[23]   MPPCTL2[31:28]   BG1_EN   2     24   GPP[24]   MPPCTL3[3:0]   SYSSTAT   3     25   GPP[25]   MPPCTL3[7:4]   REGE   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12      | GPP[12]        | MPPCTL1[19:16] | · ·                               |       |

| 15 GPP[15] MPPCTL1[31:28] PHY2 INT*  16 GNT1[0]* MPPCTL2[3:0] sPCI slot 3 GNT#  17 REQ1[0]* MPPCTL2[7:4] sPCI slot 3 REQ#  18 GNT1[1]* MPPCTL2[11:8] sPCI slot 4 GNT#  19 REQ1[1]* MPPCTL2[15:12] sPCI slot 4 REQ#  20 GNT2[1]* MPPCTL2[19:16] sPCI SlO GNT#  21 REQ2[1]* MPPCTL2[23:20] sPCI SlO REQ#  22 GPP[22] MPPCTL2[27:24] SIOINT  1 23 GPP[23] MPPCTL2[31:28] BG1_EN  2 4 GPP[24] MPPCTL3[3:0] SYSSTAT  2 5 GPP[25] MPPCTL3[7:4] REGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13      | GPP[13]        | MPPCTL1[23:20] |                                   |       |

| 16       GNT1[0]*       MPPCTL2[3:0]       sPCI slot 3 GNT#         17       REQ1[0]*       MPPCTL2[7:4]       sPCI slot 3 REQ#         18       GNT1[1]*       MPPCTL2[11:8]       sPCI slot 4 GNT#         19       REQ1[1]*       MPPCTL2[15:12]       sPCI slot 4 REQ#         20       GNT2[1]*       MPPCTL2[19:16]       sPCI SIO GNT#         21       REQ2[1]*       MPPCTL2[23:20]       sPCI SIO REQ#         22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14      | GPP[14]        | MPPCTL1[27:24] | PHY1 INT*                         |       |

| 17       REQ1[0]*       MPPCTL2[7:4]       sPCI slot 3 REQ#         18       GNT1[1]*       MPPCTL2[11:8]       sPCI slot 4 GNT#         19       REQ1[1]*       MPPCTL2[15:12]       sPCI slot 4 REQ#         20       GNT2[1]*       MPPCTL2[19:16]       sPCI SIO GNT#         21       REQ2[1]*       MPPCTL2[23:20]       sPCI SIO REQ#         22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15      | GPP[15]        | MPPCTL1[31:28] | PHY2 INT*                         |       |

| 18       GNT1[1]*       MPPCTL2[11:8]       sPCI slot 4 GNT#         19       REQ1[1]*       MPPCTL2[15:12]       sPCI slot 4 REQ#         20       GNT2[1]*       MPPCTL2[19:16]       sPCI SIO GNT#         21       REQ2[1]*       MPPCTL2[23:20]       sPCI SIO REQ#         22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16      | GNT1[0]*       | MPPCTL2[3:0]   | sPCI slot 3 GNT#                  |       |

| 19       REQ1[1]*       MPPCTL2[15:12]       sPCI slot 4 REQ#         20       GNT2[1]*       MPPCTL2[19:16]       sPCI SIO GNT#         21       REQ2[1]*       MPPCTL2[23:20]       sPCI SIO REQ#         22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17      | REQ1[0]*       | MPPCTL2[7:4]   | sPCI slot 3 REQ#                  |       |

| 20       GNT2[1]*       MPPCTL2[19:16]       sPCI SIO GNT#         21       REQ2[1]*       MPPCTL2[23:20]       sPCI SIO REQ#         22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18      | GNT1[1]*       | MPPCTL2[11:8]  | sPCI slot 4 GNT#                  |       |

| 21       REQ2[1]*       MPPCTL2[23:20]       sPCI SIO REQ#         22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19      | REQ1[1]*       | MPPCTL2[15:12] | sPCI slot 4 REQ#                  |       |

| 22       GPP[22]       MPPCTL2[27:24]       SIOINT       1         23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20      | GNT2[1]*       | MPPCTL2[19:16] | sPCI SIO GNT#                     |       |

| 23       GPP[23]       MPPCTL2[31:28]       BG1_EN       2         24       GPP[24]       MPPCTL3[3:0]       SYSSTAT       3         25       GPP[25]       MPPCTL3[7:4]       REGE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21      | REQ2[1]*       | MPPCTL2[23:20] | sPCI SIO REQ#                     |       |

| 24     GPP[24]     MPPCTL3[3:0]     SYSSTAT     3       25     GPP[25]     MPPCTL3[7:4]     REGE     5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22      | GPP[22]        | MPPCTL2[27:24] | SIOINT                            | 1     |

| 25 GPP[25] MPPCTL3[7:4] REGE 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23      | GPP[23]        | MPPCTL2[31:28] | BG1_EN                            | 2     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24      | GPP[24]        | MPPCTL3[3:0]   | SYSSTAT 3                         |       |

| 26 GPP[26] MPPCTL3[11:8] reserved 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25      | GPP[25]        | MPPCTL3[7:4]   | REGE                              | 5     |

| ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26      | GPP[26]        | MPPCTL3[11:8]  | reserved 4                        |       |

| 27 GPP[27] MPPCTL3[15:12] reserved 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27      | GPP[27]        | MPPCTL3[15:12] | reserved 4                        |       |

| 28 GPP[28] MPPCTL3[19:16] reserved 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28      | GPP[28]        | MPPCTL3[19:16] | reserved 4                        |       |

| 29 GPP[29] MPPCTL3[23:20] reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29      | GPP[29]        | MPPCTL3[23:20] | reserved                          |       |

| 30 GPP[30] MPPCTL3[27:24] Cross-processor 0->1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30      | GPP[30]        | MPPCTL3[27:24] | Cross-processor 0->1 interrupt    |       |