Reference Manual

Document identifier: MCXW72SRM

Rev. 3, 2025-12-02

# MCX W72 Security Reference Manual

# **Contents**

| Chapter 1 About this Manual             |     |

|-----------------------------------------|-----|

| 1.1 Audience                            |     |

| 1.2 Organization                        |     |

| 1.3 Module descriptions                 |     |

| 1.4 Register descriptions               |     |

| 1.5 Conventions                         |     |

| 1.0 00110111011011111111111111111111111 |     |

| Chapter 2 Security Overview             |     |

| 2.1 Disclaimer                          |     |

| 2.2 Security features                   |     |

| •                                       |     |

| Chapter 3 Lifecycle States              | 21  |

| 3.1 Overview                            |     |

| 3.2 Lifecycle states and transitions    |     |

| 3.3 Lifecycle states                    |     |

| 3.4 Customer lifecycle state            |     |

| 3.5 Field return states                 |     |

|                                         |     |

| Chapter 4 ROM Bootloader                |     |

| 4.1 Overview                            | 26  |

| 4.2 Boot ROM                            |     |

| 4.3 Security features of boot ROM       | 39  |

|                                         |     |

| Chapter 5 ROM API                       | 73  |

| 5.1 Overview                            | 73  |

| 5.2 SPI Flash API                       | 73  |

| 5.3 nboot API                           | 75  |

| 5.4 kb API                              | 81  |

| 5.5 Flash API                           |     |

| 5.6 runBootloader API                   | 91  |

|                                         |     |

| Chapter 6 ROM ISP                       |     |

| 6.1 Overview                            |     |

| 6.2 Available peripherals               |     |

| 6.3 Available ISP commands              |     |

| 6.4 ISP protocol                        |     |

| 6.5 ISP packet type                     | 98  |

| 6.6 Bootloader command set              |     |

| 6.7 LPUART ISP                          |     |

| 6.8 LPI2C ISP                           |     |

| 6.9 LPSPI ISP                           |     |

| 6.10 CAN ISP                            | 130 |

|                                         |     |

| Chapter 7 EdgeLock Secure Enclave (ELE) | 133 |

| ( 4 ( )                                 | 400 |

Contents

| Chapter 13 Secure Miscellaneous System Control Module (SMSCM)                     | 308 |

|-----------------------------------------------------------------------------------|-----|

| 13.3 SMSCM Memory Map/Register Definition                                         | 308 |

| Appendix A Release notes                                                          | 345 |

| A.1 About this manual changes                                                     | 345 |

| A.2 Security Overview changes                                                     | 345 |

| A.3 Lifecycle changes                                                             | 345 |

| A.4 ROM Bootloader changes                                                        | 345 |

| A.5 ROM API changes                                                               | 345 |

| A.6 ISP Path changes                                                              | 345 |

| A.7 ELE changes                                                                   |     |

| A.8 ELE Software Architecture and API changes                                     |     |

| A.9 ELE Messaging Unit (ELEMU)                                                    |     |

| A.10 Key Management changes                                                       |     |

| A.11 Debug Subsystem (DBGMB)                                                      |     |

| A.12 Flash Memory Controller (FMC) with NVM PRINCE Encryption and Decryption (NPX |     |

| A.13 Secure Miscellaneous System Control Module (SMSCM)                           | 346 |

| Legal information                                                                 | 348 |

# **Figures**

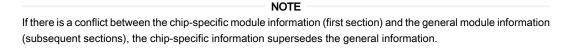

| Figure 1. Example: chapter chip-specific information and general module information      | 13  |

|------------------------------------------------------------------------------------------|-----|

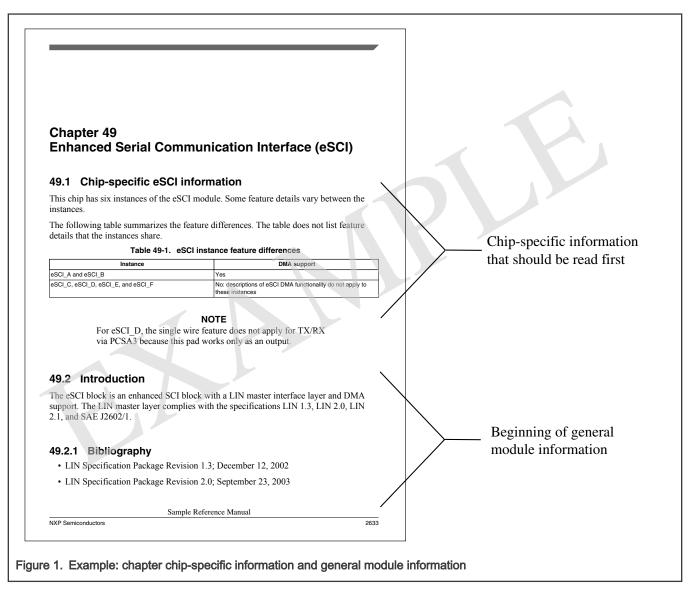

| Figure 2. Example: chip-specific information that supersedes content in the same chapter | 14  |

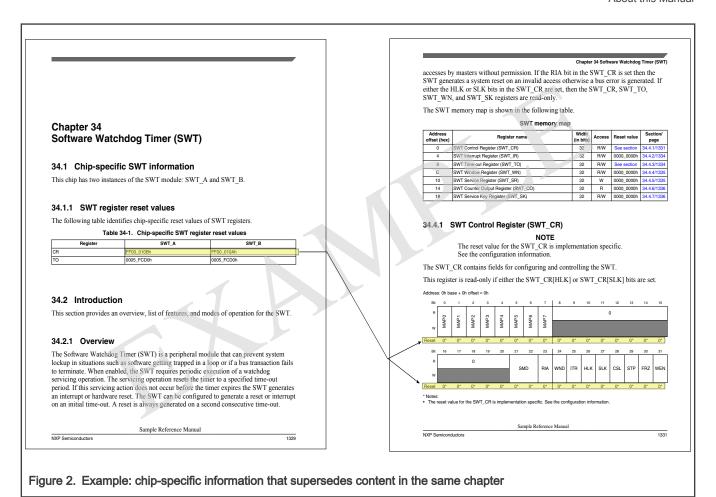

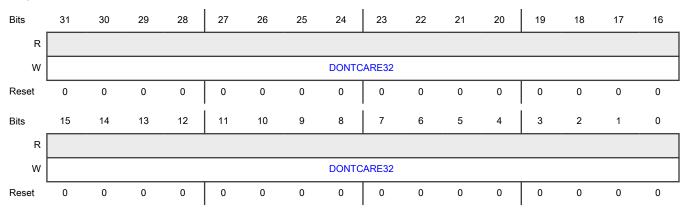

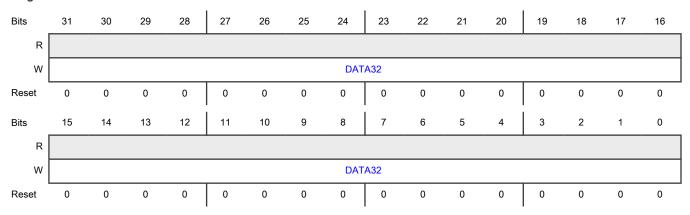

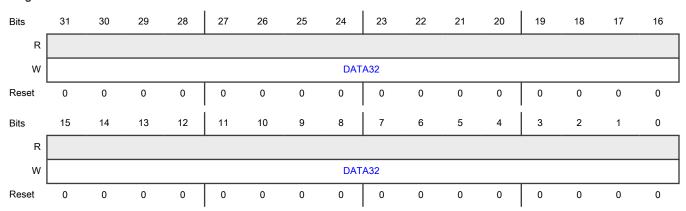

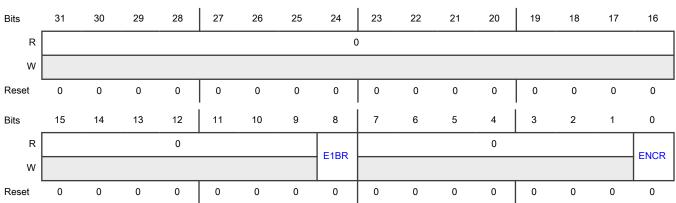

| Figure 3. Register figure conventions                                                    | 15  |

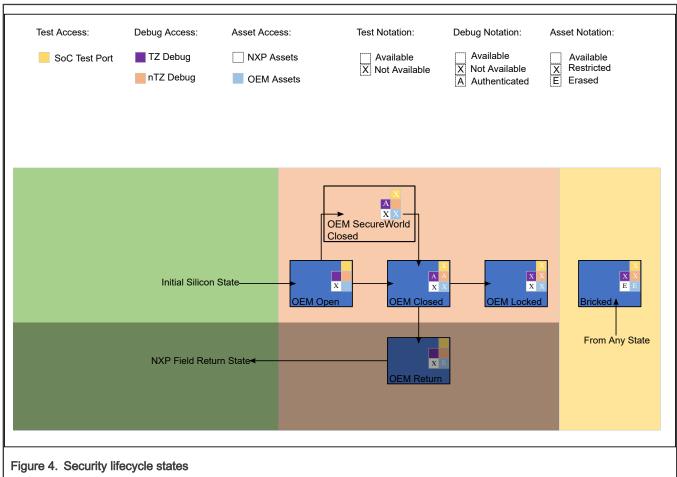

| Figure 4. Security lifecycle states                                                      | 21  |

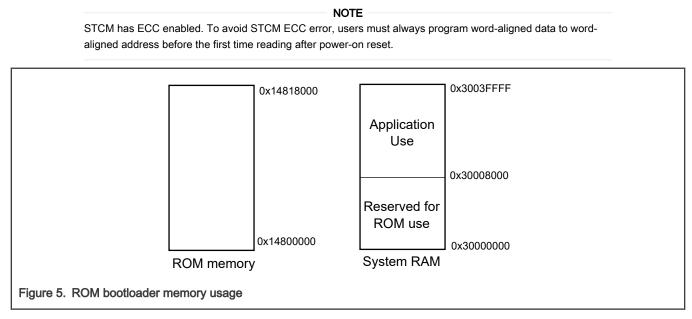

| Figure 5. ROM bootloader memory usage                                                    | 26  |

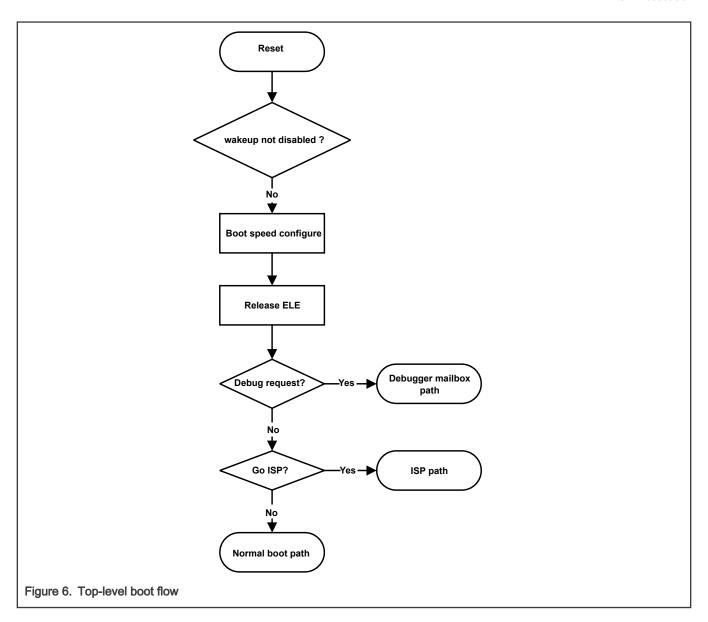

| Figure 6. Top-level boot flow                                                            | 27  |

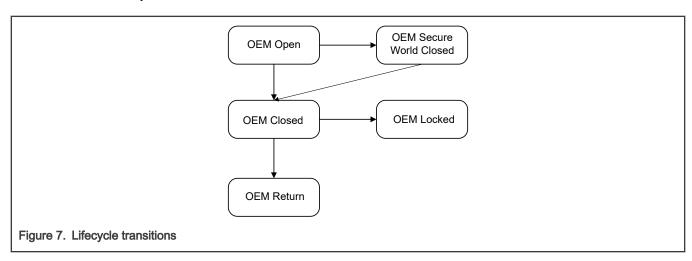

| Figure 7. Lifecycle transitions                                                          | 28  |

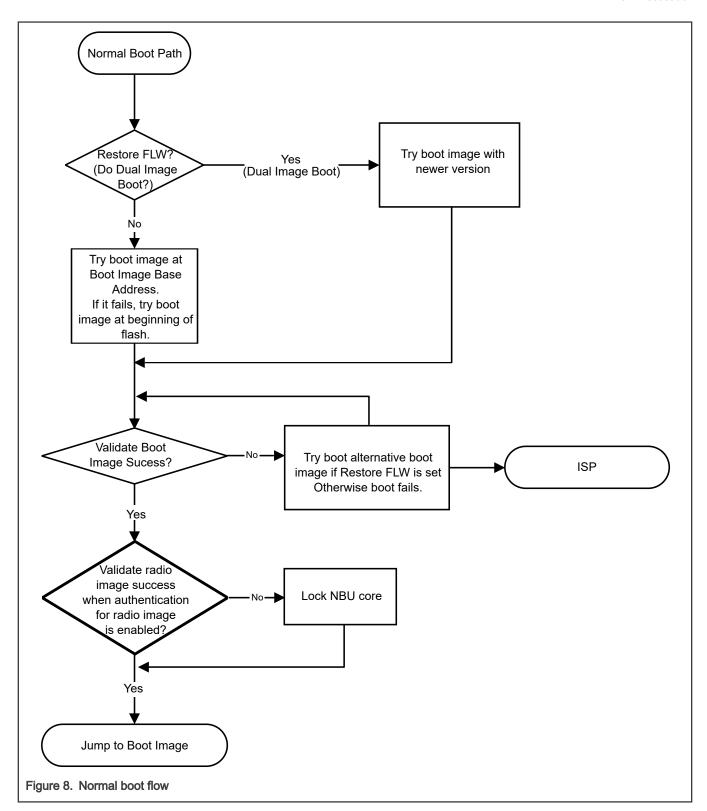

| Figure 8. Normal boot flow                                                               | 35  |

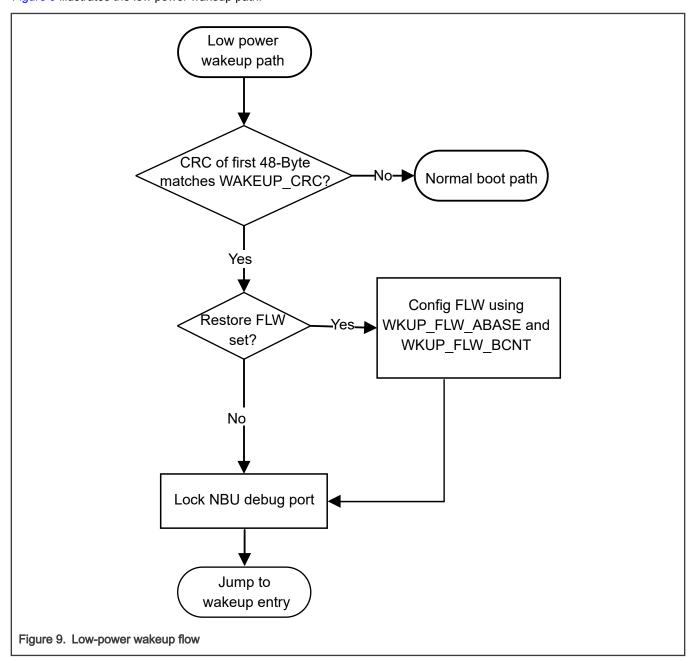

| Figure 9. Low-power wakeup flow                                                          | 37  |

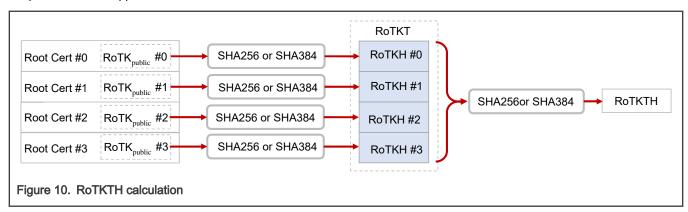

| Figure 10. RoTKTH calculation                                                            | 41  |

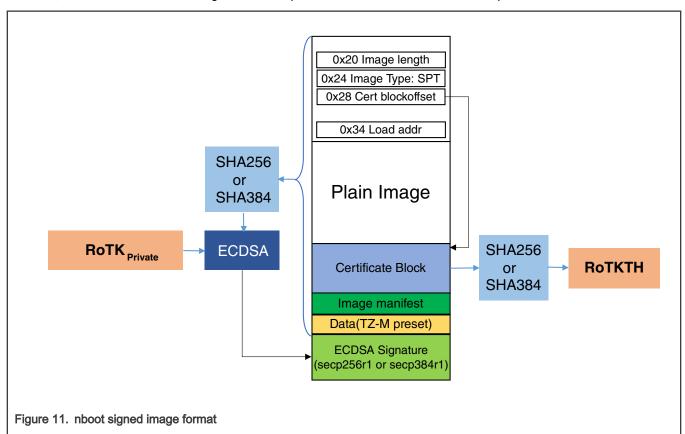

| Figure 11. nboot signed image format                                                     | 42  |

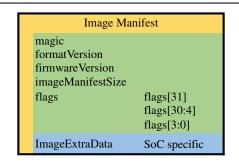

| Figure 12. Image Manifest                                                                | 44  |

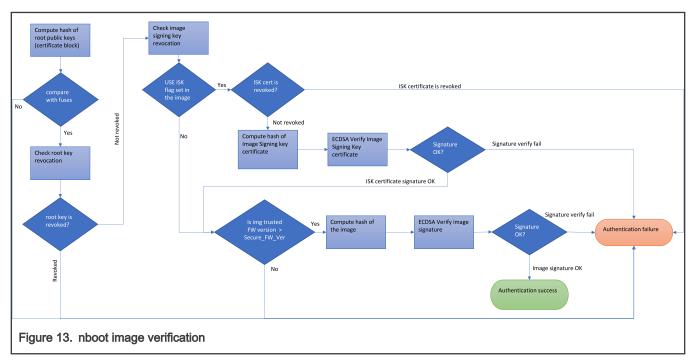

| Figure 13. nboot image verification                                                      | 45  |

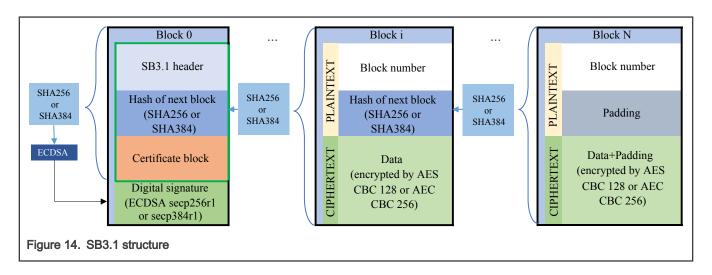

| Figure 14. SB3.1 structure                                                               | 46  |

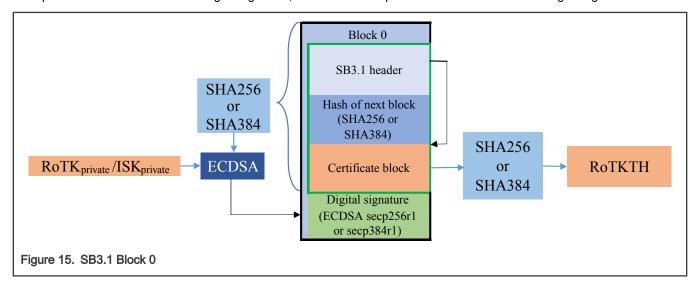

| Figure 15. SB3.1 Block 0                                                                 | 46  |

| Figure 16. SB3.1 Block 0 full structure                                                  | 47  |

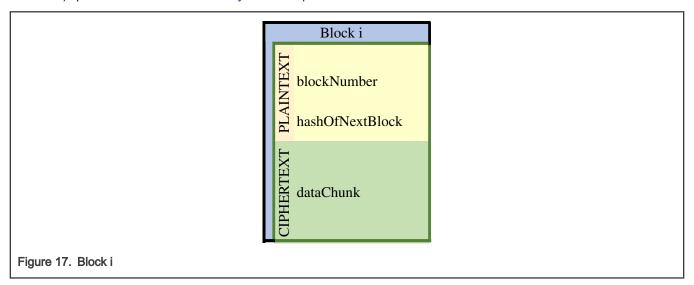

| Figure 17. Block i                                                                       | 48  |

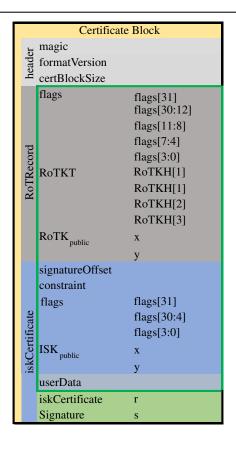

| Figure 18. Certificate Block                                                             | 51  |

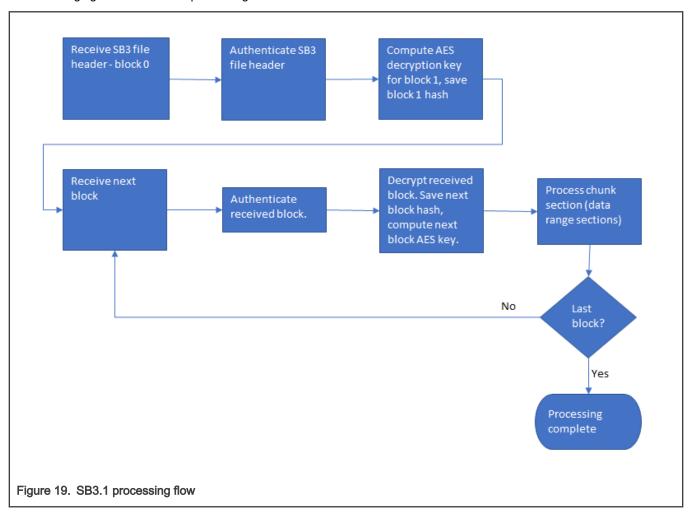

| Figure 19. SB3.1 processing flow                                                         | 57  |

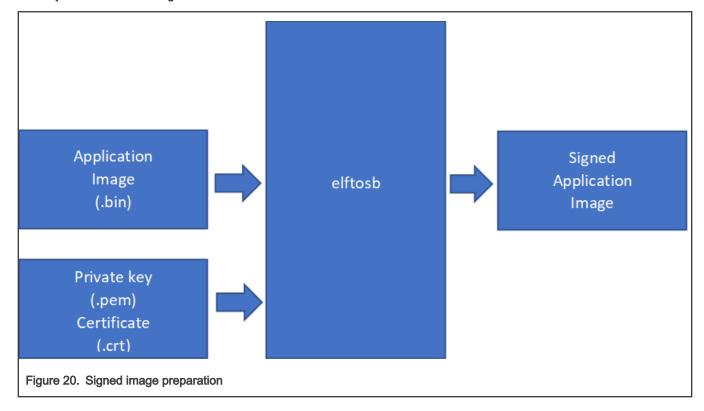

| Figure 20. Signed image preparation                                                      | 71  |

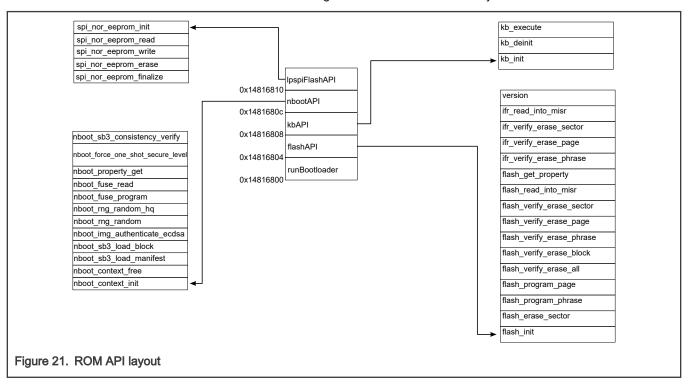

| Figure 21. ROM API layout                                                                | 73  |

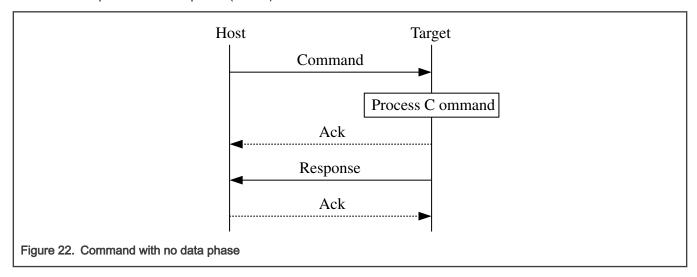

| Figure 22. Command with no data phase                                                    | 96  |

| Figure 23. Command with incoming data phase                                              | 97  |

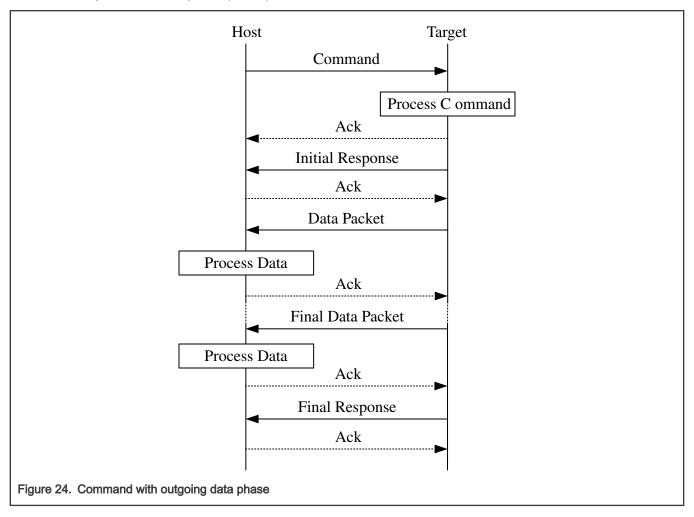

| Figure 24. Command with outgoing data phase                                              | 98  |

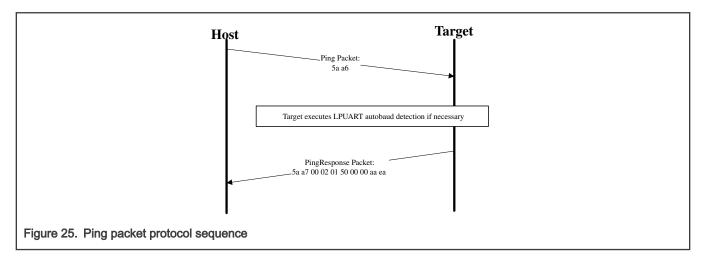

| Figure 25. Ping packet protocol sequence                                                 | 99  |

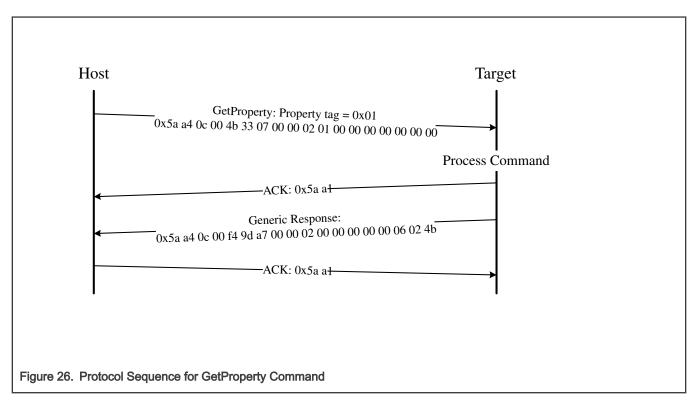

| Figure 26. Protocol Sequence for GetProperty Command                                     | 106 |

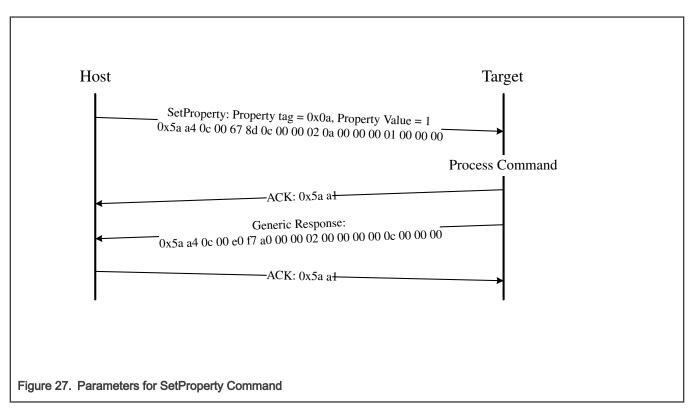

| Figure 27. Parameters for SetProperty Command                                            | 108 |

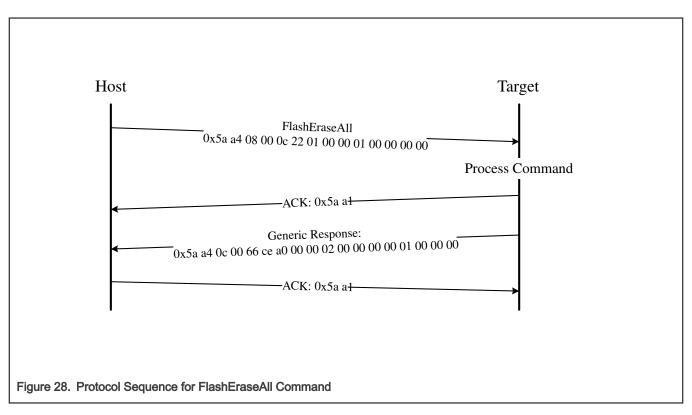

| Figure 28. Protocol Sequence for FlashEraseAll Command                                   | 110 |

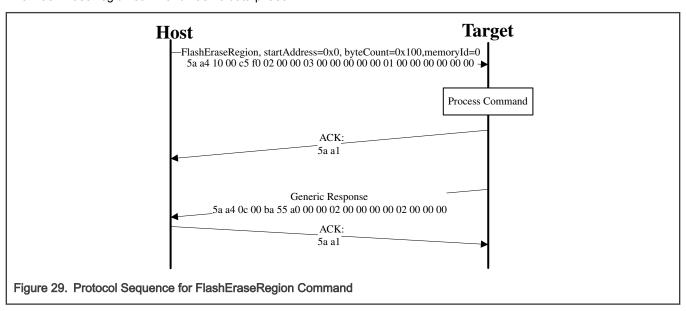

| Figure 29. Protocol Sequence for FlashEraseRegion Command                                | 111 |

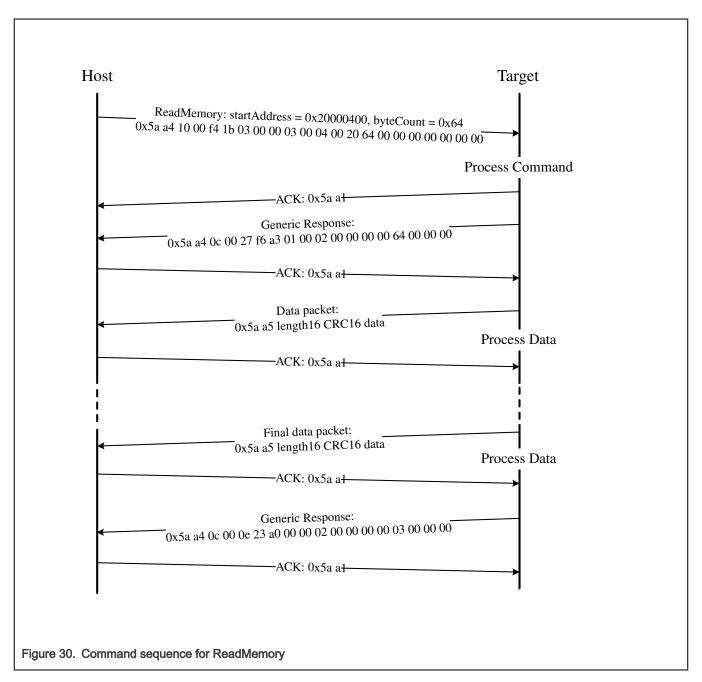

| Figure 30. Command sequence for ReadMemory                                               | 113 |

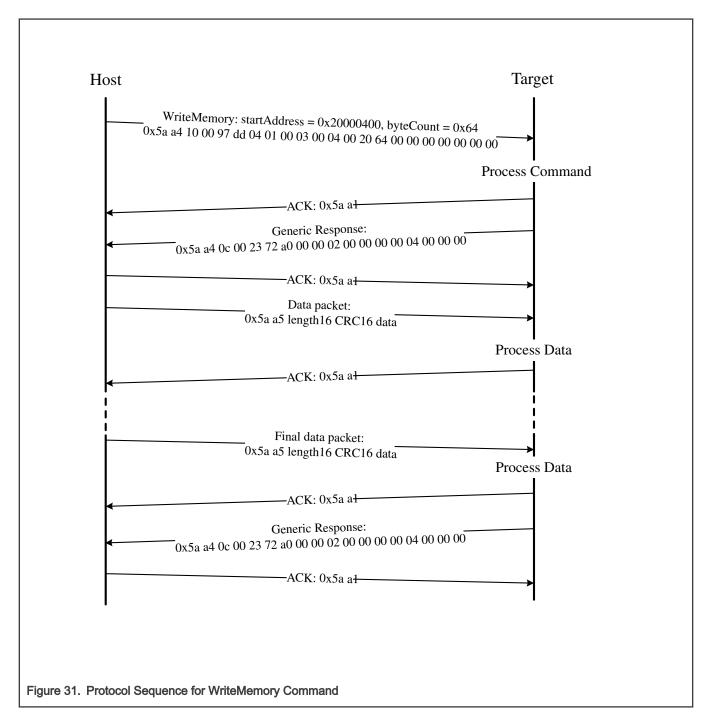

| Figure 31. Protocol Sequence for WriteMemory Command                                     | 115 |

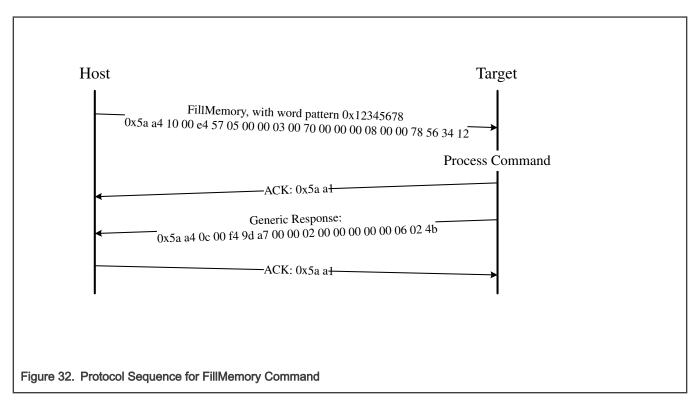

| Figure 32. Protocol Sequence for FillMemory Command                                      | 117 |

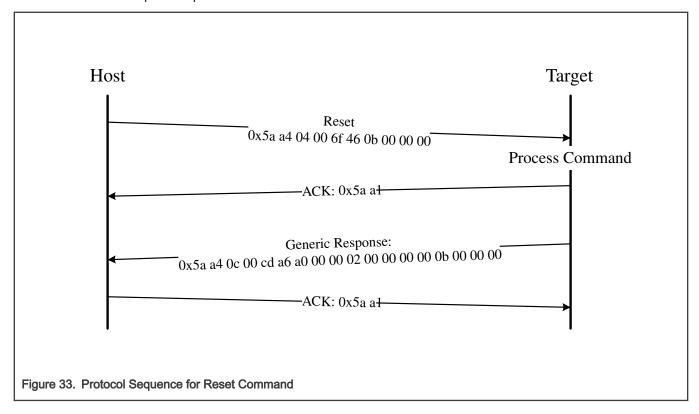

| Figure 33. Protocol Sequence for Reset Command                                           | 118 |

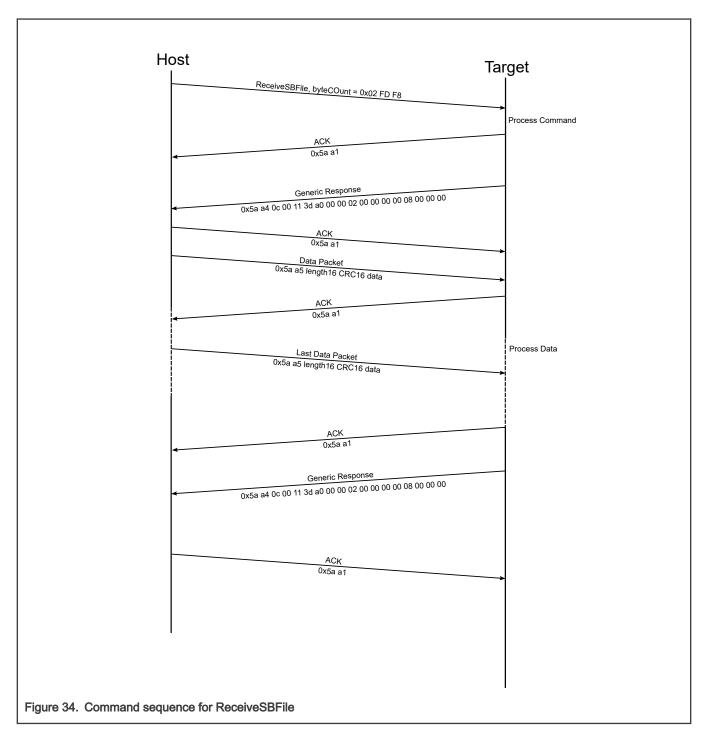

| Figure 34. Command sequence for ReceiveSBFile                                            | 120 |

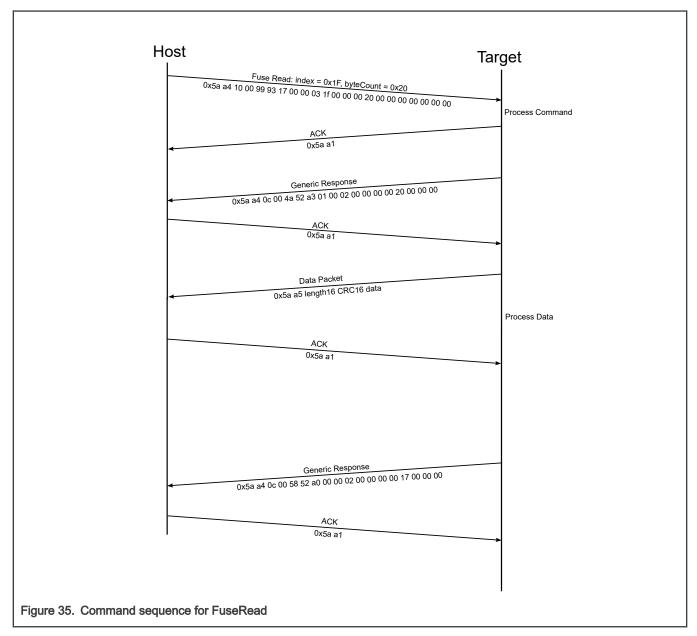

| Figure 35. Command sequence for FuseRead                                                 | 122 |

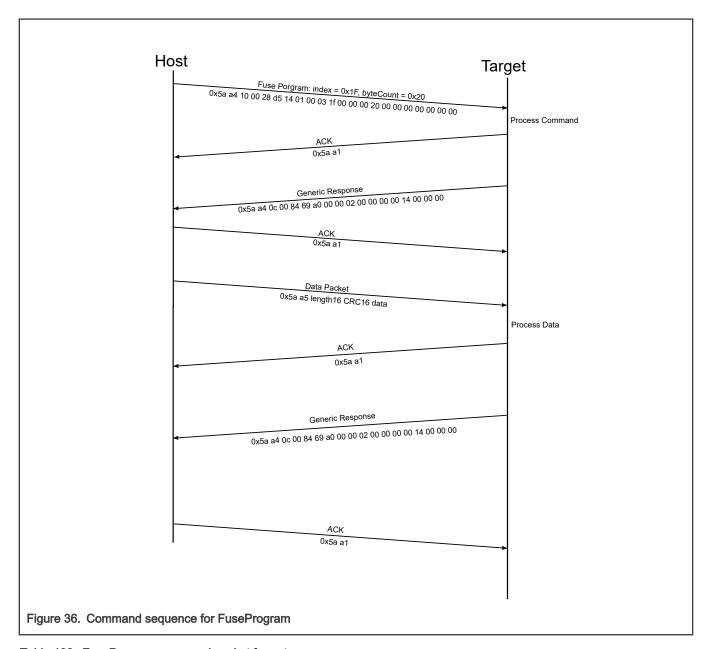

| Figure 36. Command sequence for FuseProgram                                              | 124 |

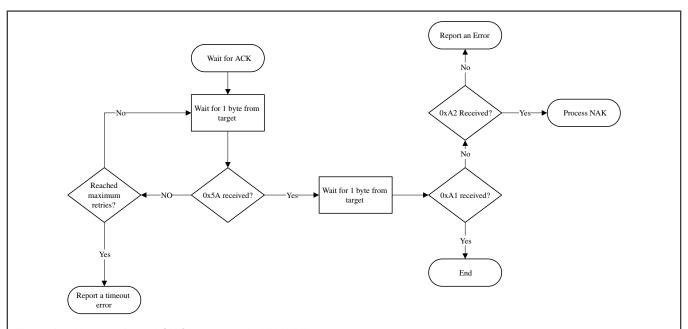

| Figure 37. Host reads an ACK from target via LPUART                                      | 126 |

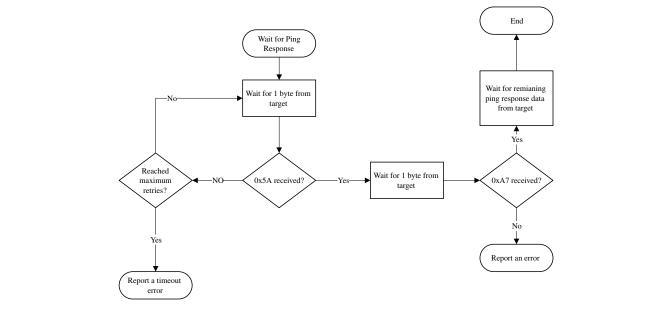

| Figure 38. Host reads a ping response from target via LPUART                             | 126 |

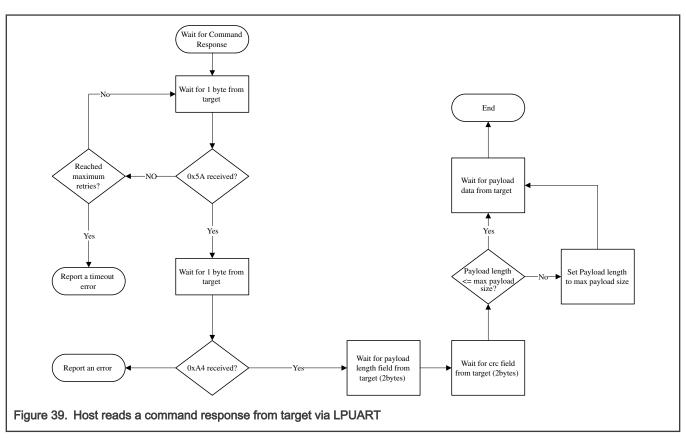

| Figure 39. Host reads a command response from target via LPUART                          | 127 |

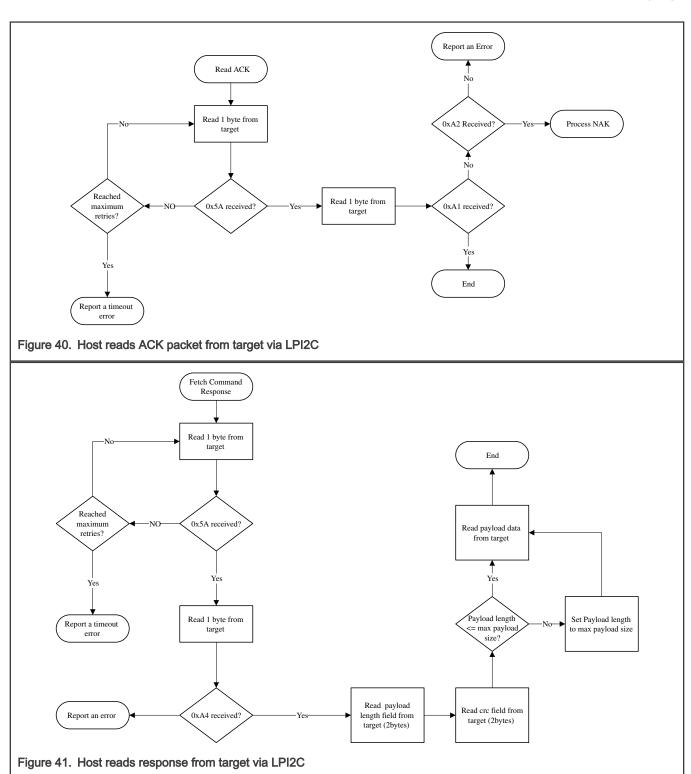

| Figure 40. Host reads ACK packet from target via LPI2C                                   | 128 |

| Figure 41. Host reads response from target via LPI2C                                     | 128 |

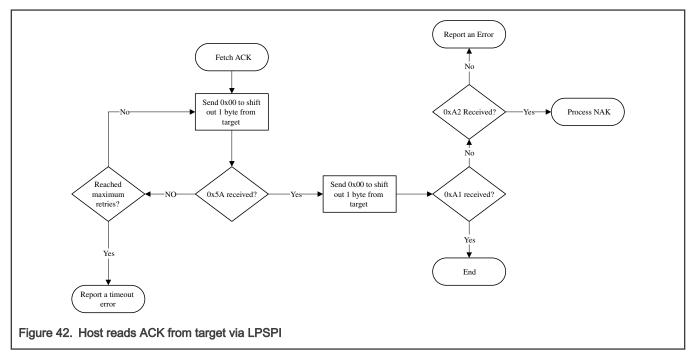

| Figure 42. Host reads ACK from target via LPSPI                                          | 129 |

|            |                                                      | Figures |

|------------|------------------------------------------------------|---------|

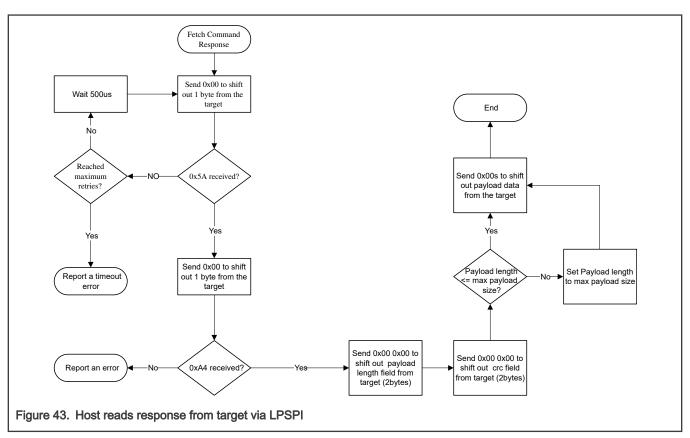

| Figure 43. | Host reads response from target via LPSPI            | 130     |

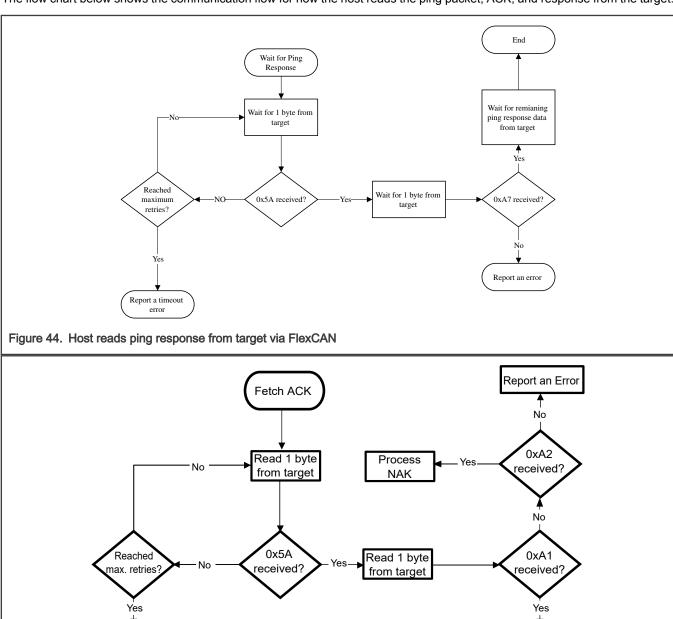

| Figure 44. | Host reads ping response from target via FlexCAN     | 131     |

| Figure 45. | Host reads ACK packet from target via FlexCAN        | 131     |

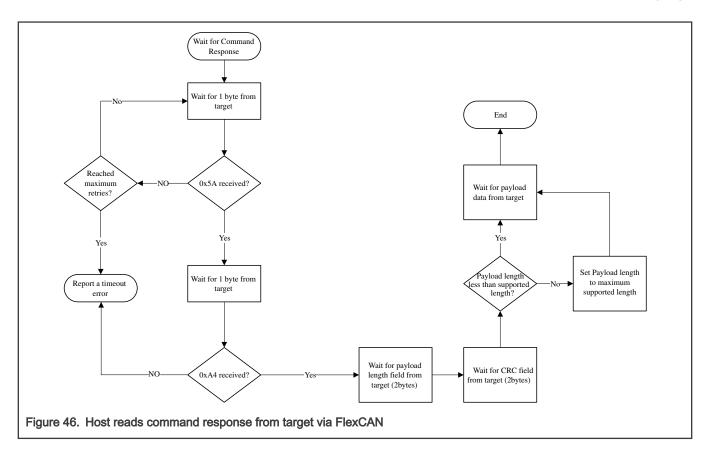

| Figure 46. | Host reads command response from target via FlexCAN  | 132     |

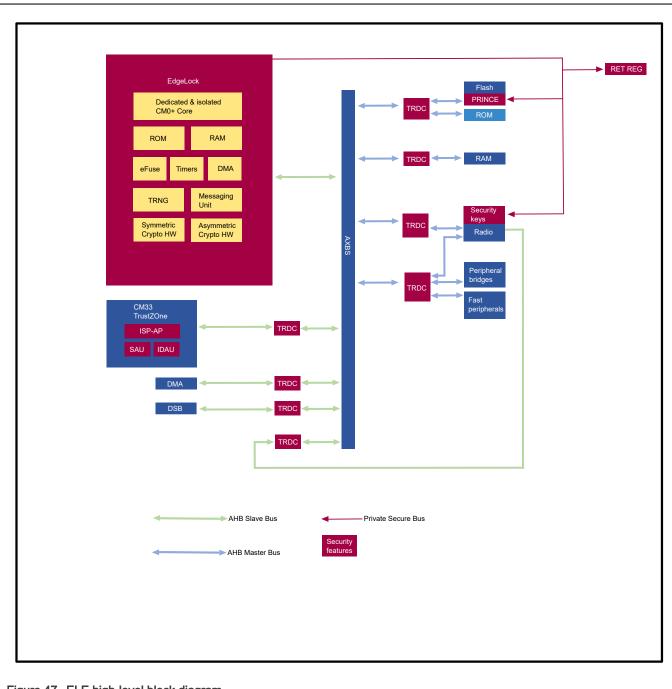

| Figure 47. | ELE high-level block diagram                         | 134     |

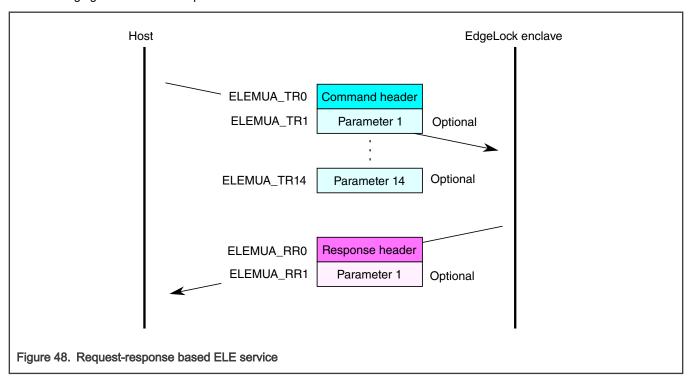

| Figure 48. | Request-response based ELE service                   |         |

| Figure 49. | Command message format                               |         |

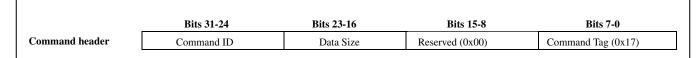

| Figure 50. | Command Header format                                | 144     |

| Figure 51. | Response message format                              | 144     |

| Figure 52. | Response Header format                               | 144     |

| Figure 53. | Asymmetric key format                                | 174     |

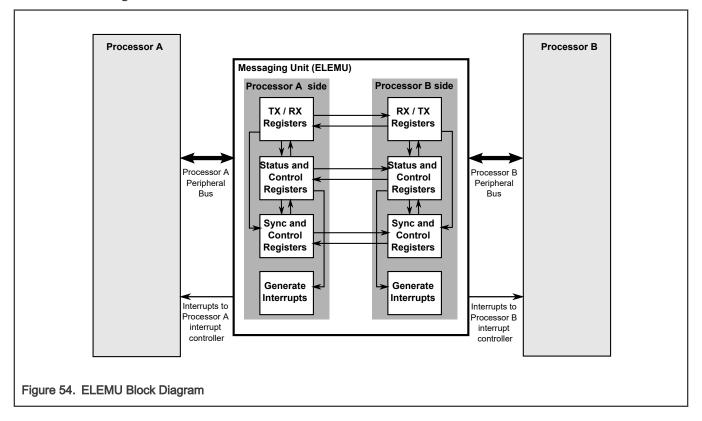

| Figure 54. | ELEMU Block Diagram                                  | 202     |

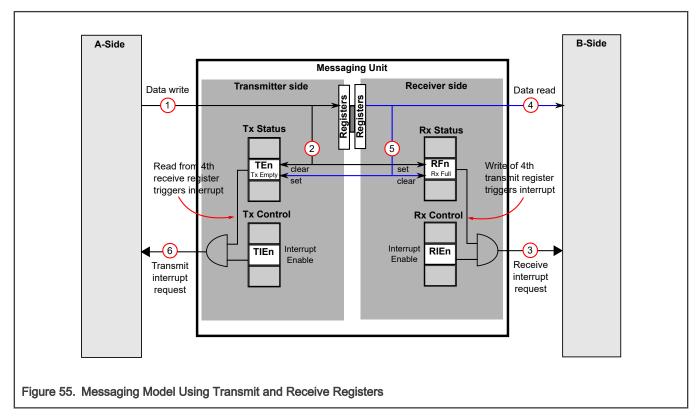

| Figure 55. | Messaging Model Using Transmit and Receive Registers | 205     |

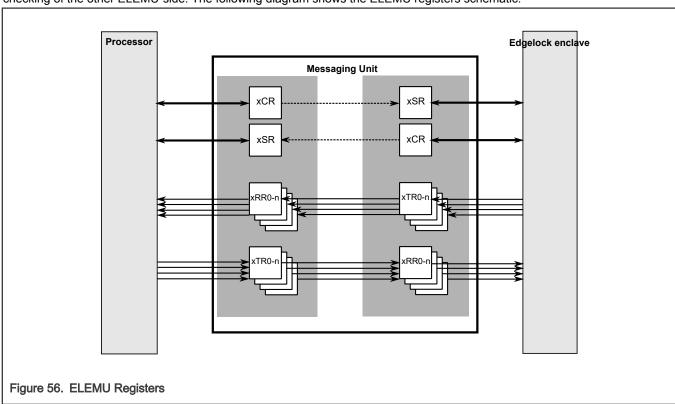

| Figure 56. | ELEMU Registers                                      | 207     |

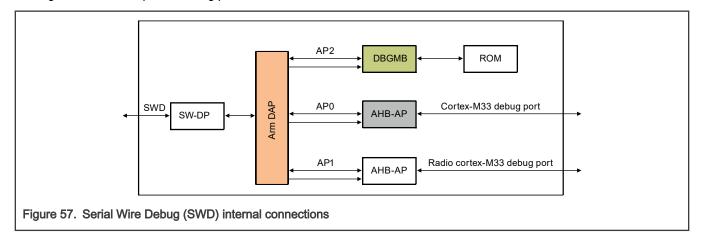

| Figure 57. | Serial Wire Debug (SWD) internal connections         | 237     |

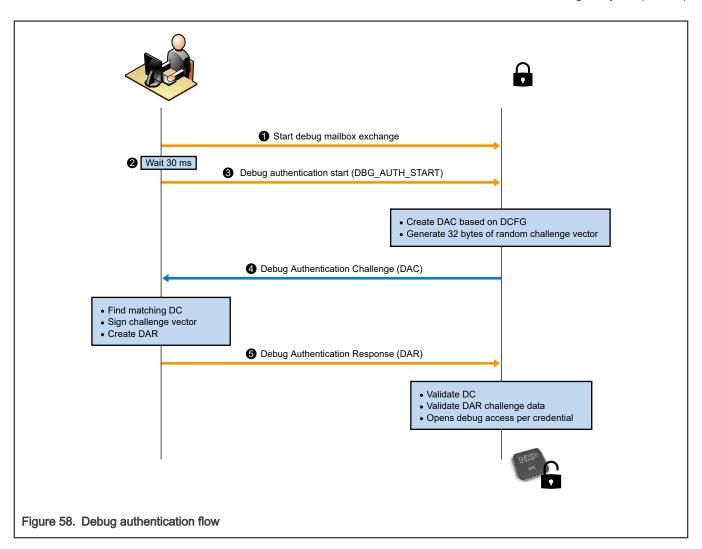

| Figure 58. | Debug authentication flow                            | 248     |

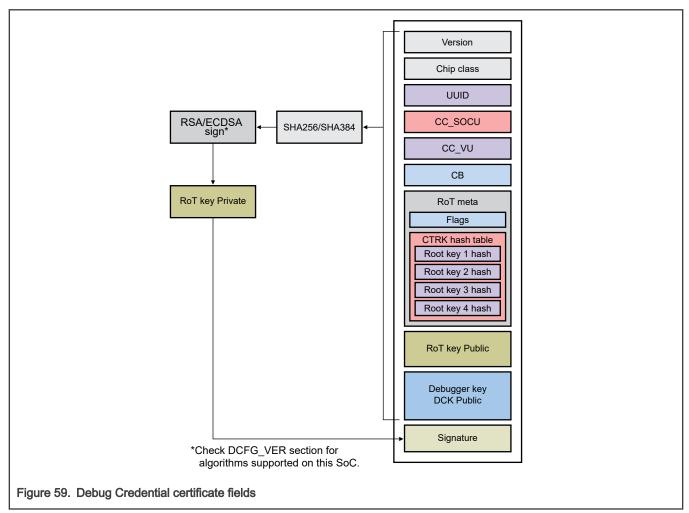

| Figure 59. | Debug Credential certificate fields                  | 253     |

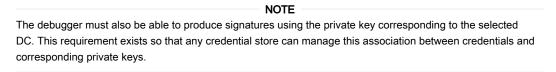

| Figure 60. | DAC fields                                           | 256     |

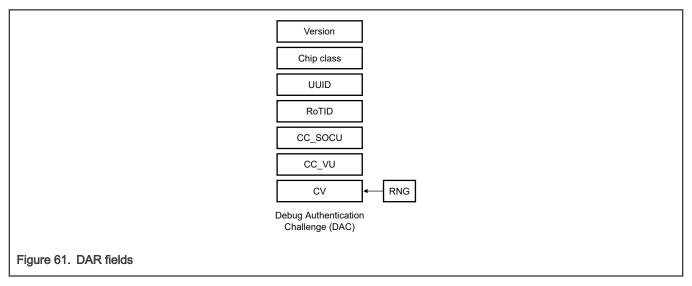

| Figure 61. | DAR fields                                           | 257     |

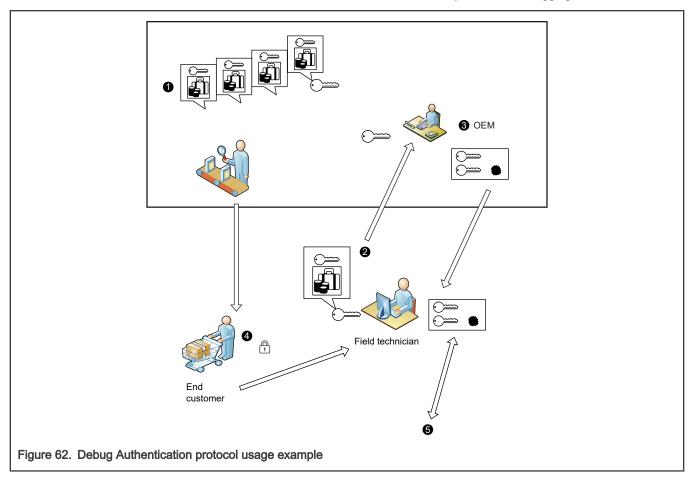

| Figure 62. | Debug Authentication protocol usage example          | 259     |

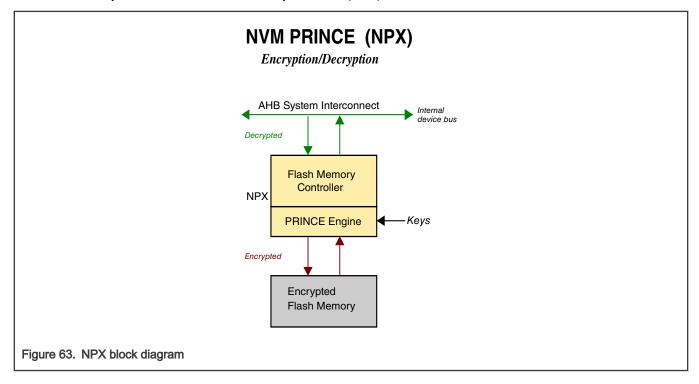

| Figure 63. | NPX block diagram                                    | 269     |

# **Tables**

| Table 1. Cryptographic operations                                                            | 18 |

|----------------------------------------------------------------------------------------------|----|

| Table 2. Lifecycle states                                                                    | 22 |

| Table 3. Lifecycle states                                                                    | 27 |

| Table 4. User IFR allocation                                                                 | 28 |

| Table 5. ROM configuration fields                                                            | 29 |

| Table 6. Boot speed                                                                          | 32 |

| Table 7. IFR0 sector 2 configuration fields                                                  | 33 |

| Table 8. OTA update configuration                                                            | 34 |

| Table 9. LPSPI1 pin assignment when external flash used and LPSPI1 configured to master mode | 38 |

| Table 10. Boot image vector table                                                            | 42 |

| Table 11. Details of imageType (word at offset 0x24)                                         | 43 |

| Table 12. Image Manifest                                                                     | 44 |

| Table 13. SB3.1 key derivation process                                                       | 49 |

| Table 14. Key derivation data                                                                | 49 |

| Table 15. Example configuration of user ROM IFR boot option                                  | 58 |

| Table 16. tzm_control variable definition                                                    | 69 |

| Table 17. cm33_misc_ctrl variable definition                                                 | 69 |

| Table 18. Secure boot status code                                                            | 72 |

| Table 19. spi_eeprom_init parameters                                                         | 73 |

| Table 20. spi_eeprom_read parameters                                                         | 74 |

| Table 21. spi_eeprom_write parameter                                                         | 74 |

| Table 22. spi_eeprom_erase parameters                                                        | 75 |

| Table 23. SPI Flash API status code                                                          | 75 |

| Table 24. nboot_context_init parameters                                                      | 76 |

| Table 25. nboot_sb3_load_manifest parameters                                                 | 76 |

| Table 26. nboot_sb3_load_block parameters                                                    | 77 |

| Table 27. nboot_img_authenticate_ecdsa                                                       | 77 |

| Table 28. nboot_rng_random                                                                   | 78 |

| Table 29. nboot_rng_random_hq                                                                | 78 |

| Table 30. nboot_fuse_program                                                                 | 78 |

| Table 31. nboot_fuse_read                                                                    | 79 |

| Table 32. nboot_property_get parameters                                                      | 79 |

| Table 33. Supported property IDs                                                             | 79 |

| Table 34. nboot_force_one_shot_secure_level parameters                                       | 80 |

| Table 35. Supported security levels                                                          | 80 |

| Table 36. nboot_sb3_consistency_verify parameters                                            | 81 |

| Table 37. nboot API status code                                                              | 81 |

| Table 38. kb_deinit parameters                                                               | 82 |

| Table 39. kb_execute parameters                                                              | 82 |

| Table 40. kb API status code                                                                 | 82 |

| Table 41. flash_init parameters                                                              | 83 |

| Table 42. flash_erase_sector parameters                                                      | 84 |

| Table 43. flash_program_phrase parameters.  26. Table 44. flash.program_page parameters.  27. Table 46. flash.program_page parameters.  28. Table 46. flash verify_erase_plase parameters.  28. Table 47. flash verify_erase_plase parameters.  28. Table 47. flash verify_erase_plase parameters.  28. Table 48. flash verify_erase_plase parameters.  28. Table 48. flash verify_erase_plase parameters.  28. Table 49. flash verify_erase_psep parameters.  28. Table 49. flash verify_erase_psep parameters.  28. Table 49. flash verify_erase_psep parameters.  29. Table 51. flr_verify_erase_psep parameters.  29. Table 51. flr_verify_erase_psep parameters.  29. Table 52. flr_verify_erase_psep parameters.  29. Table 53. fir_verify_erase_psep parameters.  29. Table 54. flr_read_into_misr_parameters.  29. Table 55. flash get_property parameters.  29. Table 56. Property definition.  20. Table 58. unBootloader parameter.  20. Table 59. unBootloader parameter.  20. Table 59. Insh API status code.  20. Table 59. Insh API status code.  20. Table 60. Peripheral instances and pin assignments used by ISP.  20. Table 60. Peripheral instances and pin assignments used by ISP.  20. Table 61. Available ISP commands for different iffecycle.  20. Table 63. Ping packet format.  20. Table 63. Ping packet format.  20. Table 64. ping response packet format.  20. Table 65. Special framing packet format.  20. Table 65. Special framing packet format.  20. Table 66. Special framing packet format.  20. Table 67. packetType field.  20. Table 67. PacketType freld.  20. Tab |              |                                                      | rables |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------|--------|

| Table 45. flash_verify_erase_blok parameters.         86           Table 46. flash_verify_erase_blok parameters.         87           Table 48. flash_verify_erase_brase parameters.         88           Table 48. flash_verify_erase_page parameters.         81           Table 49. flash_verify_erase_sector parameters.         81           Table 50. flash_read_into_mis parameters.         85           Table 51. ifr_verify_erase_sector parameters.         86           Table 52. ifr_verify_erase_page parameters.         86           Table 55. iff_verify_erase_sector parameters.         86           Table 54. ifr_read_into_misr_parameters.         86           Table 55. flash_get_property parameters.         86           Table 56. flash_get_property definition         90           Table 57. Flash API status code.         91           Table 58. runBootloader parameter.         91           Table 69. Peripheral instances and pin assignments used by ISP.         92           Table 60. Peripheral instances and pin assignments used by ISP.         93           Table 61. Available ISP commands for different lifecycle.         94           Table 62. ping packet format.         96           Table 63. Ping packet format.         96           Table 64. ping response packet format.         96           Table 65. Charact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 43. f  | flash_program_phrase parameters                      | 85     |

| Table 46. flash, verify_erase_block parameters.         86           Table 47. flash, verify_erase_phrase parameters.         88           Table 49. flash verify erase sector parameters.         81           Table 49. flash verify erase sector parameters.         85           Table 50. flir_verify_erase_phrase parameters.         86           Table 51. ifr_verify_erase_phrase parameters.         86           Table 53. ifr_verify_erase_page parameters.         86           Table 54. ifr_read_into_misr parameters.         86           Table 53. ifr_verify_erase_page parameters.         86           Table 54. ifr_read_into_misr parameters.         86           Table 54. ifr_ead_into_misr parameters.         86           Table 55. Isash_get_property parameters.         96           Table 56. Property definition         96           Table 57. Flash API status code.         91           Table 59.         91           Table 60. Peripheral instances and pin assignments used by ISP.         99           Table 63. Ping parket format.         96           Table 63. Ping packet format.         96           Table 64. ping response packet format.         96           Table 65. Framing packet format.         100           Table 66. Special framing packet format.         100 <t< td=""><td>Table 44. f</td><td>ilash_program_page parameters</td><td> 85</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 44. f  | ilash_program_page parameters                        | 85     |

| Table 47. flash_verify_erase_page parameters.         86           Table 48. flash_verify_erase_page parameters.         87           Table 49. flash_verify_erase_sector parameters.         87           Table 50. flash read into misr parameters.         88           Table 51. iff_verify_erase_page parameters.         88           Table 52. iff_verify_erase_page parameters.         88           Table 53. iff_verify_erase_page parameters.         88           Table 54. iff_read_into_misr parameters.         88           Table 55. flash_get_property parameters.         88           Table 55. flash_get_property definition         90           Table 57. Flash API status code.         91           Table 58. runBootloader parameter.         91           Table 58. runBootloader parameter.         91           Table 69. Peripheral instances and pin assignments used by ISP.         91           Table 60. Peripheral instances and pin assignments used by ISP.         92           Table 61. Available ISP commands for different lifecycle.         94           Table 62. Supported properties in GetProperty and SetProperty.         94           Table 63. Framing packet format.         96           Table 64. ping response packet format.         100           Table 65. Framing packet format.         101           Table 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 45. f  | lash_verify_erase_all parameters                     | 86     |

| Table 48. flash_verify_erase_page parameters.  Table 49. flash_verify_erase_sector parameters.  87. Table 50. flash_read_into_misr parameters.  88. Table 51. ffr_verify_erase_phrase parameters.  88. Table 52. ifr_verify_erase_phrase parameters.  88. Table 52. ifr_verify_erase_phrase parameters.  88. Table 53. ifr_verify_erase_sector parameters.  88. Table 54. ifr_read_into_misr_parameters.  88. Table 54. ifr_read_into_misr_parameters.  88. Table 55. flash_get_property parameters.  88. Table 55. flash_get_property parameters.  89. Table 56. Property definition.  90. Table 57. Property definition.  91. Table 58. runBootloader parameter.  91. Table 59. "91. Table 59. Table 59. "91. Table 59. Table 59. Table 59. "91. Table 59. Tab | Table 46. f  | lash_verify_erase_block parameters                   | 86     |

| Table 49. flash verify erase sector parameters.         87           Table 50. flash read_into_misr parameters.         88           Table 51. ifr verify_erase_phrase parameters.         88           Table 52. ifr verify_erase_page parameters.         88           Table 53. ifr_verify_erase_sector parameters.         88           Table 53. ifr_verify_erase_sector parameters.         88           Table 54. if read_into_misr parameters.         88           Table 55. Property definition.         90           Table 56. Property parameters.         91           Table 57. Flash API status code.         91           Table 58. runBootloader parameter.         91           Table 59.         91           Table 60. Peripheral instances and pin assignments used by ISP.         92           Table 61. Available ISP commands for different lifecycle.         94           Table 62. Invalidate ISP commands for different lifecycle.         94           Table 63. Ping packet format.         96           Table 64. ping response packet format.         96           Table 65. Framing packet format.         97           Table 66. Special framing packet format.         100           Table 67. packetType field.         101           Table 68. Characteristics of the XMODEM variant.         102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 47. f  | lash_verify_erase_phrase parameters                  | 86     |

| Table 50. flash_read_into_misr parameters         86           Table 51. ifr. verify_erase_phrase parameters         88           Table 52. ifr. verify_erase_page parameters         86           Table 53. ifr. verify_erase_sector parameters         86           Table 54. ifr_read_into_misr parameters         86           Table 55. flash_get_property parameters         96           Table 56. Property definition         97           Table 57. Flash API status code         99           Table 59.         91           Table 59.         91           Table 60. Peripheral instances and pin assignments used by ISP.         95           Table 61. Available ISP commands for different lifecycle.         94           Table 62. Supported properties in GetProperty and SetProperty         94           Table 63. Ping packet format.         96           Table 64. Ping response packet format.         96           Table 65. Framing packet format.         96           Table 66. Special framing packet format.         100           Table 67. packetType field.         101           Table 68. Characteristics of the XMODEM variant.         101           Table 69. Command packet format.         100           Table 67. packetType field.         101           Table 67. Seconse tags         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 48. f  | lash_verify_erase_page parameters                    | 87     |

| Table 51. ifr_verify_erase_phrase parameters.  Table 52. ifr_verify_erase_se_parameters.  88. Table 52. ifr_verify_erase_se_sector parameters.  88. Table 53. ifr_verify_erase_se_sector parameters.  88. Table 55. fire_sed_into_misr_parameters.  88. Table 55. flash_get_property parameters.  89. Table 56. Property definition.  99. Table 56. Property definition.  99. Table 57. Flash API status code.  99. Table 58. runBootloader parameter.  99. Table 59. Peripheral instances and pin assignments used by ISP.  30. Table 60. Peripheral instances and pin assignments used by ISP.  30. Table 60. Peripheral instances and pin assignments used by ISP.  30. Table 61. Pavailable ISP commands for different lifecycle.  90. Table 62. Supported properties in GetProperty and SetProperty.  30. Table 62. Supported properties in GetProperty and SetProperty.  30. Table 63. Ping packet format.  30. Table 64. Ping response packet format.  30. Table 65. Framing packet format.  30. Table 66. Special framing packet format.  30. Table 66. Special framing packet format.  30. Table 67. packetType field.  30. Table 69. Command packet format (32 bytes).  30. Table 69. Command packet format (32 bytes).  30. Table 71. Command tags The command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.  30. Table 72. Response tags.  30. Table 73. GenericResponse parameters.  30. Table 75. ReadMemoryResponse parameters.  30. Table 76. FlashReadOnceResponse parameters.  30. Table 77. Parameters for GetProperty Command.  30. Table 78. GetProperty Response parameters.  30. Table 79. GetProperty Response Packet Format (Example).  30. Table 80. Parameters for SetProperty Command.  30. Table 81. SetProperty Command Packet Format (Example).  30. Table 83. Parameters for FlashEraseAll Command.  30. Table 84. FlashEraseAll Command Packet Format (Example).  30. Table 86. FlashEraseAll Command Packet Format (Example).  30. Table 86. FlashEraseAll Command Packet Format (Example).  30. Table 86. Flash | Table 49. f  | lash_verify_erase_sector parameters                  | 87     |

| Table 52. ifr_verify_erase_page parameters.  Table 53. ifr_verify_erase_sector parameters.  88. Table 54. ifr_read_into_misr_parameters.  88. Table 54. ifr_read_into_misr_parameters.  89. Table 56. Property definition.  90. Table 57. Flash API status code.  91. Table 58. runBootloader parameter.  91. Table 59. Table 50. Property definition.  92. Table 50. Property definition.  93. Table 50. Property definition.  94. Table 50. Property definition.  95. Table 50. Property definition.  96. Table 50. Property definition.  97. Table 50. Property definition.  98. Table 50. Property definition.  99. Table 60. Peripheral instances and pin assignments used by ISP.  71. Table 60. Peripheral instances and pin assignments used by ISP.  71. Table 60. Peripheral instances and pin assignments used by ISP.  71. Table 60. Supported properties in GetProperty and SetProperty.  94. Table 63. Ping packet format.  95. Table 64. ping response packet format.  96. Table 65. Framing packet format.  100. Table 66. Special framing packet format.  101. Table 67. packetType field.  102. Table 68. Characteristics of the XMODEM variant.  103. Table 69. Command packet format.  104. Table 69. Command header format.  105. Table 70. Command header format.  106. Table 71. Command header format.  107. Table 72. Response tags.  108. Table 73. GenericResponse parameters.  109. Table 74. GetProperty Response parameters.  109. Table 75. ReadMemoryResponse parameters.  100. Table 76. FlashReadOnceResponse parameters.  100. Table 77. GetProperty Response parameters.  101. Table 79. GetProperty Response parameters.  102. Table 79. GetProperty Response Parameters.  103. Table 79. GetProperty Response Parameters.  104. Table 79. GetProperty Response Parameters.  105. Table 79. GetProperty Response Parameters.  106. Table 79. GetProperty Response Parameters.  107. Table 79. GetProperty Response Parameters.  108. Table 79. GetProperty Response Parameters.  109. Table 79. GetProperty Response Parameters.  100. Table 80. Parameters for FlashEraseRejon Command.  | Table 50. f  | flash_read_into_misr parameters                      | 88     |

| Table 53. ifr_verify_erase_sector parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 51. if | fr_verify_erase_phrase parameters                    | 88     |

| Table 54. ifr_read_into_misr parameters       85         Table 55. flash get_property parameters       95         Table 57. Flash API status code.       97         Table 58. runBootloader parameter       91         Table 59.       97         Table 60. Peripheral instances and pin assignments used by ISP.       93         Table 61. Available ISP commands for different lifecycle       94         Table 62. Supported properties in GetProperty and SetProperty       94         Table 63. Ping packet format.       95         Table 64. ping response packet format.       96         Table 65. Framing packet format.       96         Table 66. Special framing packet format.       100         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 69. Command packet format (32 bytes).       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       100         Table 72. Response tags.       102         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       106         Table 75. ReadMemoryResponse parameters.       106         Table 76. FlashReadOnceResponse parameters.       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 52. if | fr_verify_erase_page parameters                      | 89     |

| Table 55. flash_get_property parameters       96         Table 56. Property definition       95         Table 57. Flash API status code.       97         Table 58. runBootloader parameter       97         Table 59.       99         Table 60. Peripheral instances and pin assignments used by ISP.       93         Table 61. Available ISP commands for different lifecycle       94         Table 62. Supported properties in GetProperty and SetProperty       94         Table 63. Ping packet format.       95         Table 64. ping response packet format.       96         Table 65. Framing packet format.       100         Table 65. Framing packet format.       100         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 69. Command packet format (32 bytes).       102         Table 70. Command header format.       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 53. if | fr_verify_erase_sector parameters                    | 89     |

| Table 56. Property definition         96           Table 57. Flash API status code         97           Table 58. runBootloader parameter         99           Table 60. Peripheral instances and pin assignments used by ISP.         99           Table 61. Available ISP commands for different lifecycle.         94           Table 62. Supported properties in GetProperty and SetProperty         96           Table 63. Ping packet format.         96           Table 64. Ping response packet format.         96           Table 65. Framing packet format.         100           Table 66. Special framing packet format.         100           Table 67. packetType field.         101           Table 68. Characteristics of the XMODEM variant.         101           Table 69. Command packet format (32 bytes).         102           Table 70. Command header format.         102           Table 71. Command tags for the bootloader are listed here.         103           Table 72. Response tags.         103           Table 73. GenericResponse parameters.         104           Table 74. GetPropertyResponse parameters.         104           Table 75. ReadMemoryResponse parameters.         105           Table 76. BlashReadOnceResponse parameters.         105           Table 77. Parameters for GetProperty Command         105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 54. if | fr_read_into_misr parameters                         | 89     |

| Table 57. Flash API status code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 55. f  | lash_get_property parameters                         | 90     |

| Table 58. runBootloader parameter.       91         Table 59.       91         Table 60. Peripheral instances and pin assignments used by ISP.       93         Table 61. Available ISP commands for different lifecycle.       94         Table 62. Supported properties in GetProperty and SetProperty.       94         Table 63. Ping packet format.       95         Table 64. ping response packet format.       96         Table 65. Framing packet format.       100         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 70. Command packet format (32 bytes).       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       104         Table 76. FlashReadOnceResponse parameters.       106         Table 77. Parameters for GetProperty Command.       105         Table 79. GetProperty Command Packet Format (Example).       106         Table 80. Parameters for SetProperty Command.       107         Table 81. SetPro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 56. F  | Property definition                                  | 90     |

| Table 59.       91         Table 60. Peripheral instances and pin assignments used by ISP.       93         Table 61. Available ISP commands for different lifecycle.       94         Table 62. Supported properties in GetProperty and SetProperty.       94         Table 63. Ping packet format.       95         Table 64. ping response packet format.       95         Table 65. Framing packet format.       100         Table 66. Special framing packet format.       101         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 69. Command packet format.       102         Table 70. Command header format.       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       104         Table 76. FlashReadOnceResponse parameters.       105         Table 77. Parameters for GetProperty Command.       106         Table 78. GetProperty Command Packet Format (Example).       106         Table 80. Parameters for SetPrope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 57. F  | Flash API status code                                | 91     |

| Table 60. Peripheral instances and pin assignments used by ISP.  Table 61. Available ISP commands for different lifecycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 58. r  | runBootloader parameter                              | 91     |

| Table 61. Available ISP commands for different lifecycle.       94         Table 62. Supported properties in GetProperty and SetProperty.       94         Table 63. Ping packet format.       95         Table 64. ping response packet format.       95         Table 65. Framing packet format.       100         Table 66. Special framing packet format.       101         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 69. Command packet format (32 bytes).       102         Table 70. Command header format.       102         Table 71. Command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       104         Table 76. FlashReadOnceResponse parameters.       105         Table 77. Parameters for GetProperty Command.       106         Table 79. GetProperty Response Packet Format (Example).       106         Table 80. Parameters for SetProperty Command Packet Format (Example).       107         Table 81. SetProperty Response Status Codes.       106         Table 83. Parameters for FlashEraseAll Command.       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table 59     |                                                      | 91     |

| Table 62. Supported properties in GetProperty and SetProperty.       94         Table 63. Ping packet format.       95         Table 64. ping response packet format.       100         Table 65. Framing packet format.       100         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 69. Command packet format (32 bytes).       102         Table 70. Command header format.       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       104         Table 76. FlashReadOnceResponse parameters.       105         Table 77. Parameters for GetProperty Command.       105         Table 78. GetProperty Response Packet Format (Example).       106         Table 80. Parameters for SetProperty Command.       107         Table 81. SetProperty Response Status Codes.       105         Table 82. SetProperty Response Status Codes.       105         Table 83. Parameters for FlashEraseAll Command.       105         Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 60. F  | Peripheral instances and pin assignments used by ISP | 93     |

| Table 63. Ping packet format       98         Table 64. ping response packet format       98         Table 65. Framing packet format       100         Table 66. Special framing packet format       101         Table 67. packetType field       101         Table 68. Characteristics of the XMODEM variant       101         Table 69. Command packet format (32 bytes)       102         Table 70. Command header format       102         Table 71. Command tags The command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags       103         Table 73. GenericResponse parameters       104         Table 74. GetPropertyResponse parameters       104         Table 75. ReadMemoryResponse parameters       104         Table 76. FlashReadOnceResponse parameters       104         Table 77. Parameters for GetProperty Command       105         Table 78. GetProperty Response Packet Format (Example)       106         Table 79. GetProperty Response Packet Format (Example)       107         Table 80. Parameters for SetProperty Command       107         Table 81. SetProperty Response Status Codes       108         Table 82. SetProperty Response Status Codes       105         Table 83. Parameters for FlashEraseAll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 61. A  | Available ISP commands for different lifecycle       | 94     |

| Table 64. ping response packet format       99         Table 65. Framing packet format       100         Table 66. Special framing packet format       101         Table 67. packetType field       101         Table 68. Characteristics of the XMODEM variant       101         Table 69. Command packet format (32 bytes)       102         Table 70. Command header format       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters       104         Table 74. GetPropertyResponse parameters       104         Table 75. ReadMemoryResponse parameters       104         Table 76. FlashReadOnceResponse parameters       105         Table 77. Parameters for GetProperty Command       105         Table 78. GetProperty Command Packet Format (Example)       106         Table 80. Parameters for SetProperty Command       107         Table 80. Parameters for SetProperty Command       107         Table 81. SetProperty Response Packet Format (Example)       106         Table 82. SetProperty Response Status Codes       108         Table 83. Parameter for FlashEraseAll Command       106         Table 84. FlashErase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 62. S  | Supported properties in GetProperty and SetProperty  | 94     |

| Table 65. Framing packet format.       100         Table 66. Special framing packet format.       101         Table 67. packetType field.       101         Table 68. Characteristics of the XMODEM variant.       101         Table 69. Command packet format (32 bytes).       102         Table 70. Command header format.       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       104         Table 76. FlashReadOnceResponse parameters.       105         Table 77. Parameters for GetProperty Command.       105         Table 78. GetProperty Command Packet Format (Example).       106         Table 79. GetProperty Response Packet Format (Example).       107         Table 80. Parameters for SetProperty Command.       107         Table 81. SetProperty Response Status Codes.       108         Table 82. SetProperty Response Status Codes.       106         Table 83. Parameter for FlashEraseAll Command.       106         Table 84. FlashEraseAll Command Packet Format (Example).       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 63. F  | Ping packet format                                   | 99     |

| Table 66. Special framing packet format       101         Table 67. packetType field       101         Table 68. Characteristics of the XMODEM variant       101         Table 69. Command packet format (32 bytes)       102         Table 70. Command header format       102         Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here.       103         Table 72. Response tags       103         Table 73. GenericResponse parameters       104         Table 74. GetPropertyResponse parameters       104         Table 75. ReadMemoryResponse parameters       104         Table 76. FlashReadOnceResponse parameters       105         Table 77. Parameters for GetProperty Command       105         Table 78. GetProperty Command Packet Format (Example)       106         Table 79. GetProperty Response Packet Format (Example)       107         Table 80. Parameters for SetProperty Command       107         Table 81. SetProperty Response Status Codes       108         Table 82. SetProperty Response Status Codes       105         Table 83. Parameter for FlashEraseAll Command       106         Table 84. FlashEraseAll Command Packet Format (Example)       106         Table 85. Parameters for FlashEraseRegion Command       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 64. p  | ping response packet format                          | 99     |

| Table 67. packetType field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 65. F  | Framing packet format                                | 100    |

| Table 68. Characteristics of the XMODEM variant. 101 Table 69. Command packet format (32 bytes). 102 Table 70. Command header format. 102 Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here. 103 Table 72. Response tags. 103 Table 73. GenericResponse parameters. 104 Table 74. GetPropertyResponse parameters. 104 Table 75. ReadMemoryResponse parameters. 104 Table 76. FlashReadOnceResponse parameters. 105 Table 77. Parameters for GetProperty Command. 105 Table 78. GetProperty Command Packet Format (Example). 106 Table 79. GetProperty Response Packet Format (Example). 107 Table 80. Parameters for SetProperty Command. 107 Table 81. SetProperty Command Packet Format (Example). 106 Table 82. SetProperty Response Status Codes. 105 Table 83. Parameter for FlashEraseAll Command. 105 Table 84. FlashEraseAll Command Packet Format (Example). 116 Table 85. Parameters for FlashEraseRegion Command. 117 Table 86. FlashEraseRegion Response Status Codes. 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 66. S  | Special framing packet format                        | 101    |

| Table 69. Command packet format (32 bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 67. p  | packetType field                                     | 101    |

| Table 70. Command header format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 68. 0  | Characteristics of the XMODEM variant                | 101    |

| Table 71. Command tagsThe command tag specifies one of the commands supported by the bootloader. The valid command tags for the bootloader are listed here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 69. 0  | Command packet format (32 bytes)                     | 102    |

| command tags for the bootloader are listed here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 70. 0  | Command header format                                | 102    |

| Table 72. Response tags.       103         Table 73. GenericResponse parameters.       104         Table 74. GetPropertyResponse parameters.       104         Table 75. ReadMemoryResponse parameters.       105         Table 76. FlashReadOnceResponse parameters.       105         Table 77. Parameters for GetProperty Command.       105         Table 78. GetProperty Command Packet Format (Example).       106         Table 79. GetProperty Response Packet Format (Example).       107         Table 80. Parameters for SetProperty Command.       107         Table 81. SetProperty Command Packet Format (Example).       108         Table 82. SetProperty Response Status Codes.       108         Table 83. Parameter for FlashEraseAll Command.       109         Table 84. FlashEraseAll Command Packet Format (Example).       110         Table 85. Parameters for FlashEraseRegion Command.       111         Table 86. FlashEraseRegion Response Status Codes.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                      | 103    |