Rev. 1, 2025-09-26

# MCX A255, and A256 Security Reference Manual

Supports MCX A255VPN, A255VLH, A255VLL, A255VLQ, A256VPN, A256VLH, A256VLL, and A256VLQ

## **Contents**

| Chapter 1 About This Manual                                   | 5   |

|---------------------------------------------------------------|-----|

| 1.1 Audience                                                  |     |

| 1.2 Organization                                              |     |

| 1.3 Module descriptions                                       |     |

| 1.4 Register descriptions                                     |     |

| 1.5 Conventions                                               |     |

| 1.6 Editorial changes                                         |     |

|                                                               |     |

| Chapter 2 Introduction                                        | 13  |

| 2.1 Overview                                                  |     |

| 2.2 Target applications                                       |     |

| 2.3 Block diagram                                             |     |

| 2.4 Features                                                  |     |

| 2.5 Functional overview                                       |     |

|                                                               |     |

| Chapter 3 Core Overview                                       |     |

| 3.1 Introduction                                              | 25  |

| 3.2 Cortex-M33 Code and System buses                          |     |

| 3.3 Nested Vectored Interrupt Controller (NVIC)               | 25  |

| 3.4 System memory map                                         |     |

| 3.5 Peripheral Bridge                                         | 26  |

|                                                               |     |

| Chapter 4 Security Overview                                   |     |

| 4.1 Non-claims                                                |     |

| 4.2 Overview                                                  |     |

| 4.3 Security features                                         | 28  |

| Observation Ed. W. O. also Otation                            | 0.0 |

| Chapter 5 Life Cycle States                                   |     |

| 5.1 Overview                                                  |     |

| 5.2 Life cycle state transitioning                            |     |

| 5.3 Life cycle states                                         |     |

| 5.4 Identify the life cycle (LC) state                        |     |

| 5.5 Read-out protection (ROP)                                 | 31  |

|                                                               | 00  |

| Chapter 6 ROM API                                             |     |

| 6.1 Overview                                                  | 33  |

|                                                               | 0.0 |

| Chapter 7 Extended Bootloader and In-System Programming (ISP) |     |

| 7.1 Overview                                                  |     |

| 7.2 Boot peripherals and default pins                         |     |

| 7.3 Functional description                                    |     |

| 7.4 Flash swap path                                           |     |

| 7.5 ISP protocol                                              |     |

| 7.6 Bootloader packet types                                   |     |

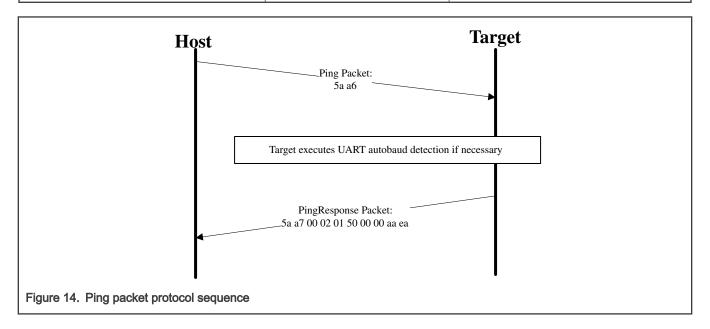

| 7.7 Ping packet                                               | 45  |

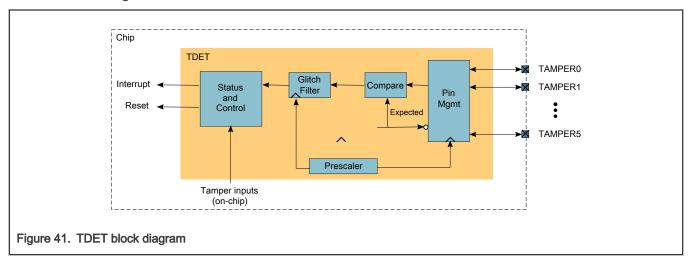

13.1 Chip-specific TDET information......289

|                                                     | Contents |

|-----------------------------------------------------|----------|

| 13.2 Overview                                       | 290      |

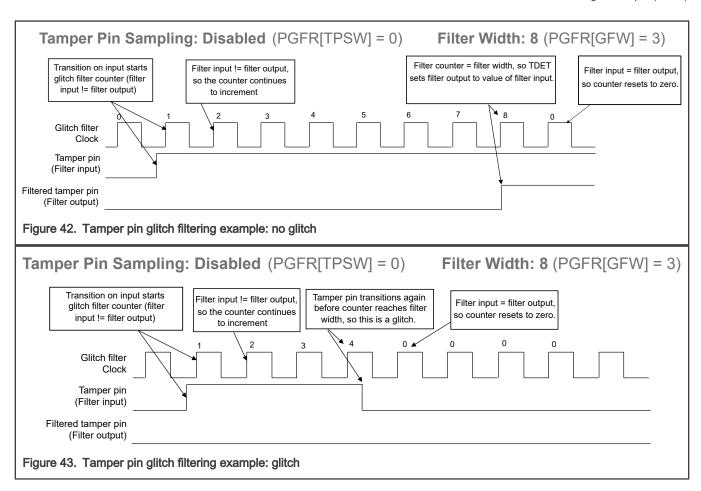

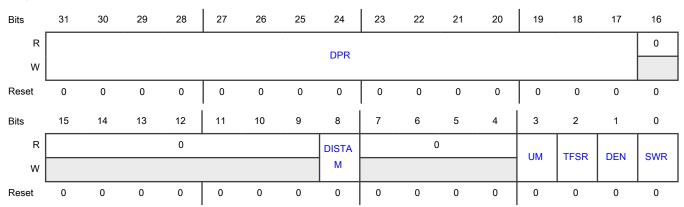

| 13.3 Functional description                         |          |

| 13.4 External signals.                              |          |

| 13.5 Initialization                                 |          |

| 13.6 Register definitions                           |          |

|                                                     | 0.00     |

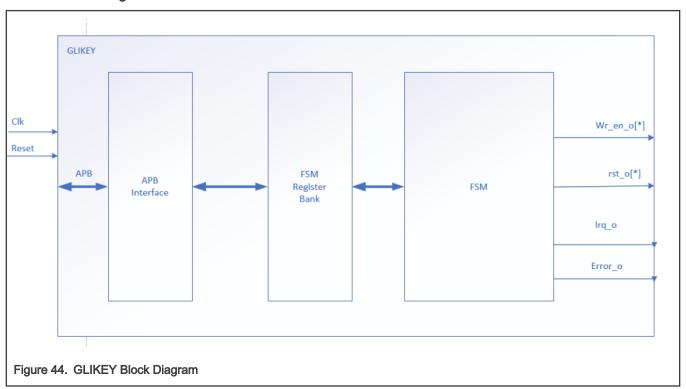

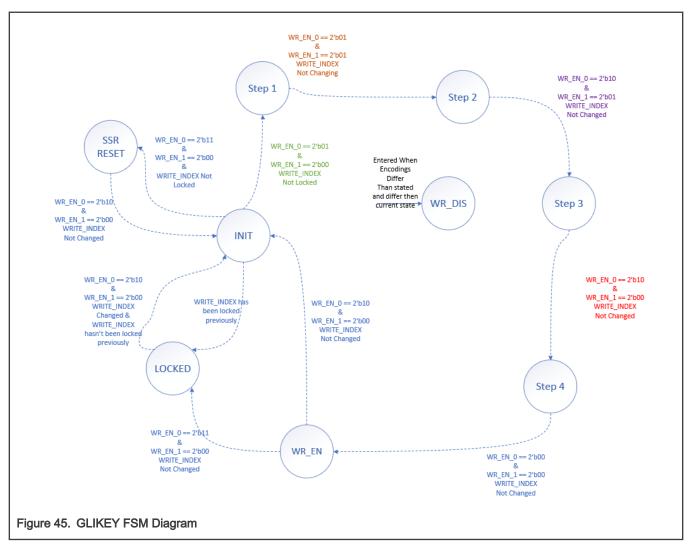

| Chapter 14 GLIKEY                                   |          |

| 14.1 Chip-specific GLIKEY information               |          |

| 14.2 Terms and definitions                          |          |

| 14.3 Overview                                       |          |

| 14.4 Configuration                                  |          |

| 14.5 Architecture description                       | 309      |

| Chapter 15 Secure Generic Interface (SGI)           | 321      |

| 15.1 Chip-specific SGI information                  |          |

| 15.2 Overview                                       |          |

| 15.3 Functional description                         |          |

| 15.4 Application information                        |          |

| 15.5 Registers description (SFRs)                   |          |

| 15.6 Terms and definitions                          |          |

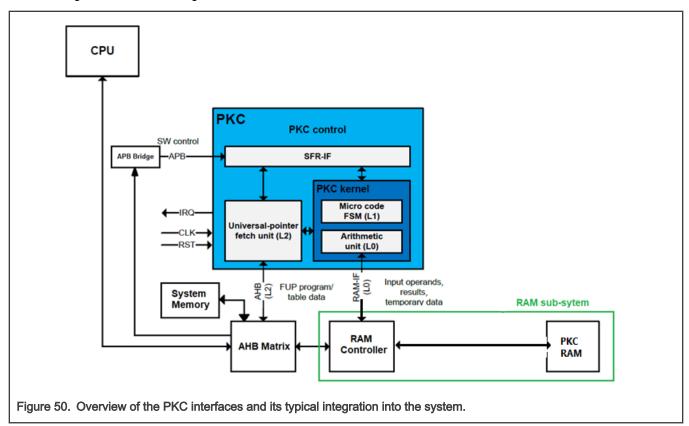

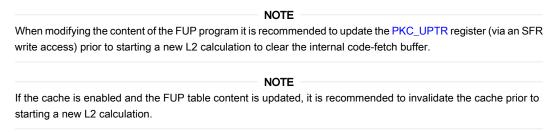

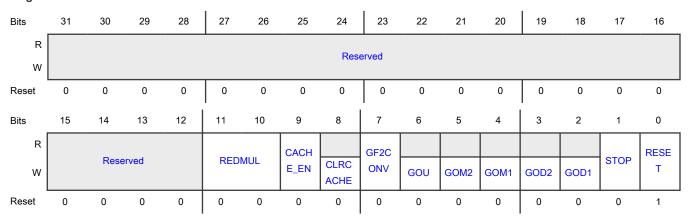

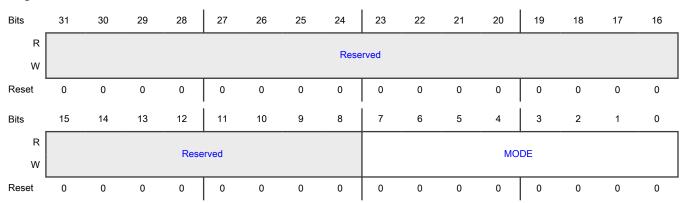

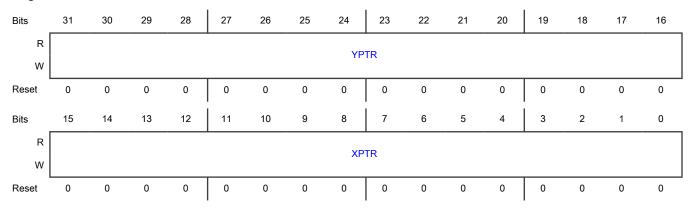

| Chapter 16 Public-Key Crypto Coprocessor (PKC)      | 433      |

| 16.1 Chip-specific PKC information                  |          |

| 16.2 Overview                                       |          |

| 16.3 Block diagram                                  |          |

| 16.4 Functional description                         |          |

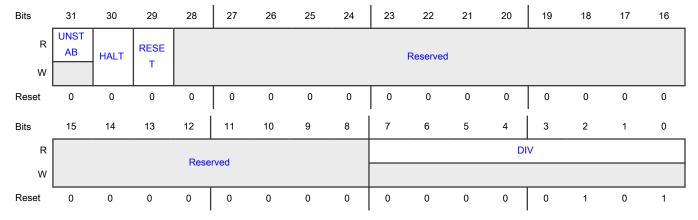

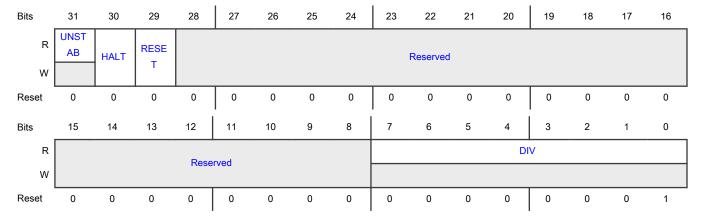

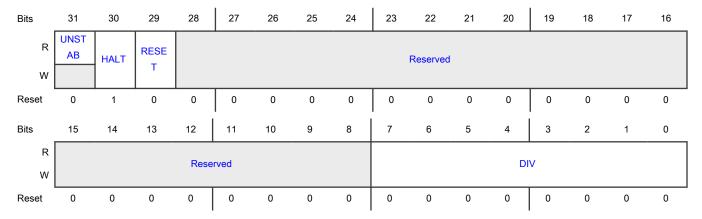

| 16.5 Handling of PKC_CTRL[RESET] and PKC_CTRL[STOP] |          |

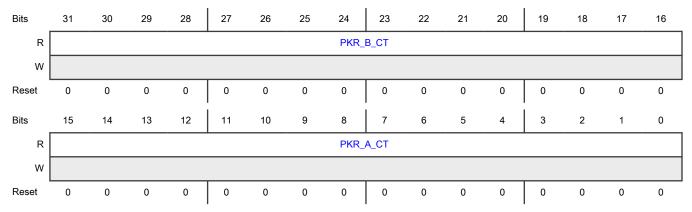

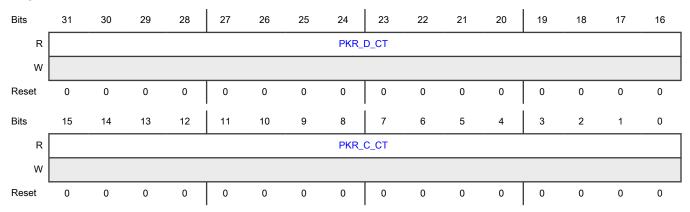

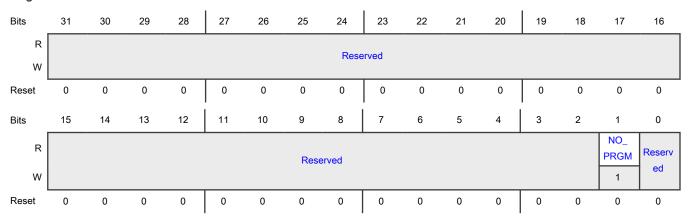

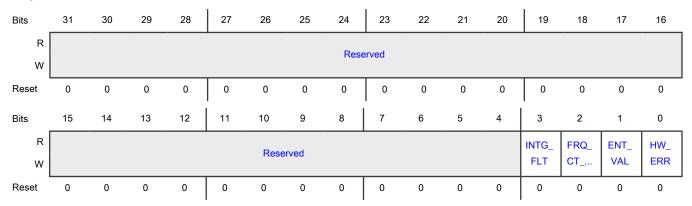

| 16.6 PKC register descriptions                      |          |

| Objection 47 Taxon Devidence Occupants (TDNO)       | 500      |

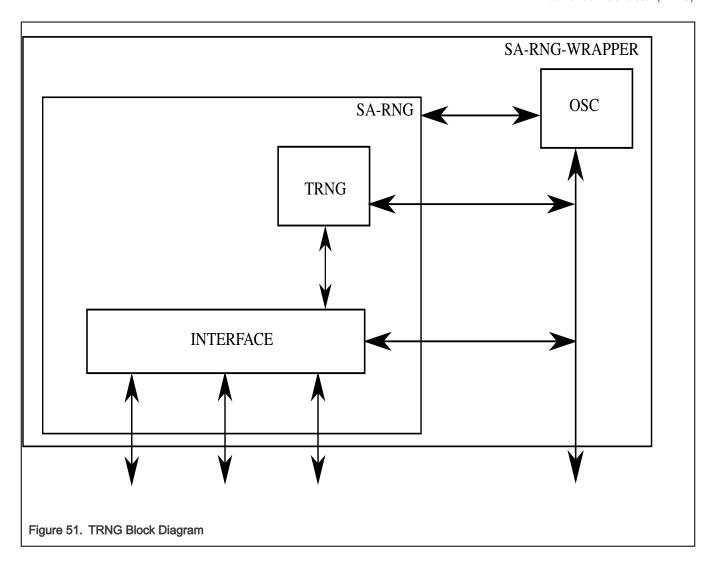

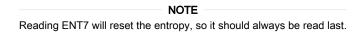

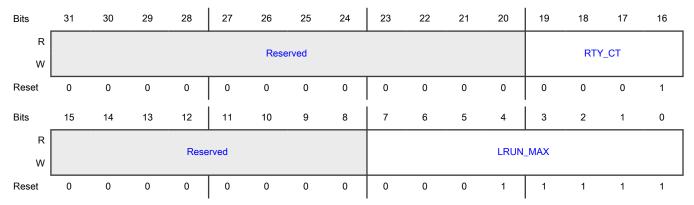

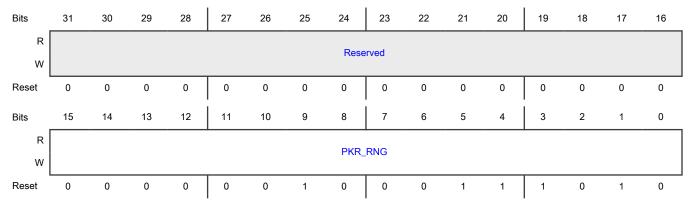

| Chapter 17 True Random Generator (TRNG)             |          |

| 17.1 Chip-specific TRNG information                 |          |

| 17.2 Overview                                       |          |

| 17.3 Functional Description                         |          |

| 17.4 Register Interface Usage                       |          |

| 17.5 Operation                                      |          |

| 17.6 Other Applications                             |          |

| 17.7 TRNG register descriptions                     | 528      |

|                                                     |          |

| Appendix A Release notes                            | 581      |

| A.1 Revision history                                | 581      |

| Legal information                                   | 582      |

## Chapter 1 About This Manual

#### 1.1 Audience

This reference manual (RM) is intended for system software, hardware developers, and applications programmers who need to develop products using this chip. It assumes that its users understand operating systems, microprocessor system design, and basic principles of software and hardware.

#### 1.2 Organization

This manual has two main sets of chapters.

- Chapters in the first set contain information that applies to all components on the chip.

- · Chapters in the second set are organized into functional groupings that detail particular areas of functionality.

- Examples of these groupings are clocking, timers, and communication interfaces.

- Each grouping includes chapters that provide a technical description of individual modules.

#### 1.2.1 Attachments

This manual includes key information in the files attached to it. For example, memory map and I/O details. Use the content in these attachments in conjunction with this manual's content.

| NOTE                                                                                         |

|----------------------------------------------------------------------------------------------|

| Select the paperclip icon on the left side of the PDF window to see the list of attachments. |

#### 1.3 Module descriptions

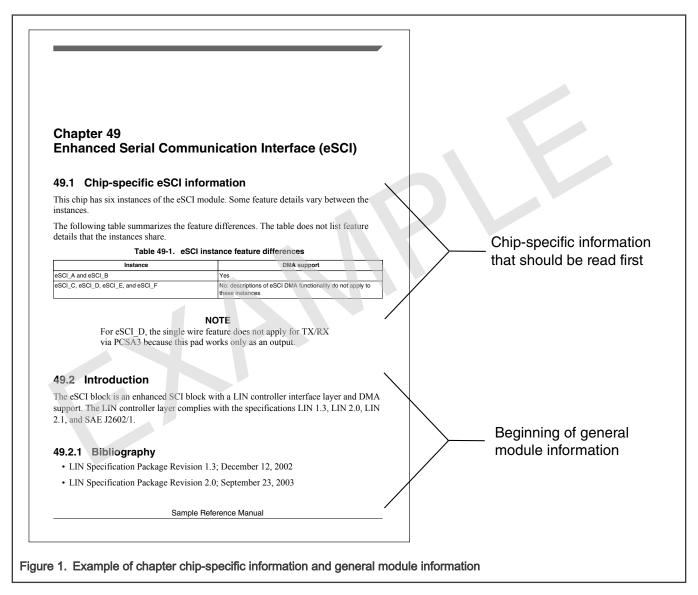

Each module chapter has two main parts:

- The first section, chip-specific [module name] information, provides details such as the number of module instances on the

chip and connections between that module and the other ones. Read this section first because its content is crucial for

understanding the information in the other sections of the chapter.

- The subsequent sections provide general information about the module, including its signals, registers, and functional description.

The following figure shows you an example of this demarcation.

Reference Manual 5 / 584

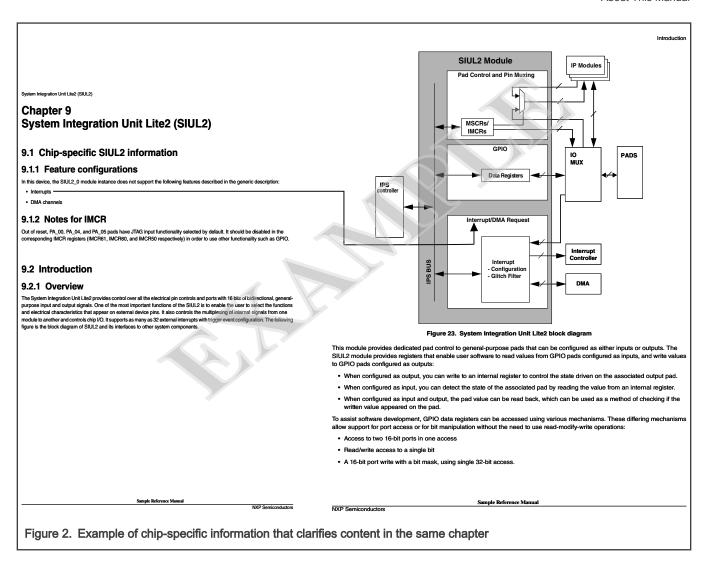

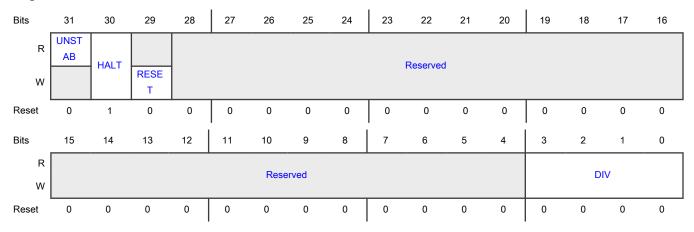

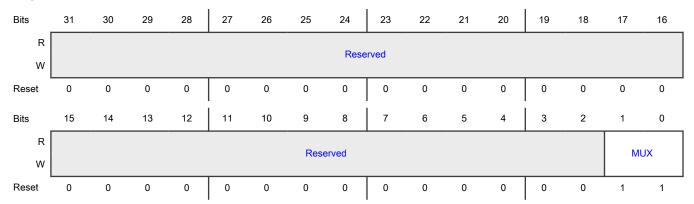

### 1.3.1 Chip-specific information that clarifies content in the same chapter

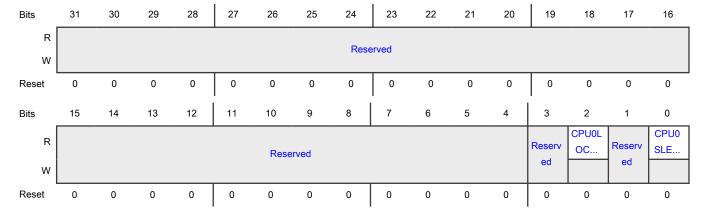

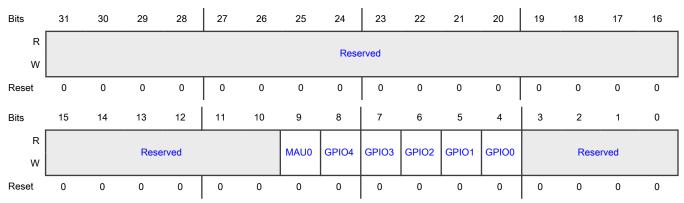

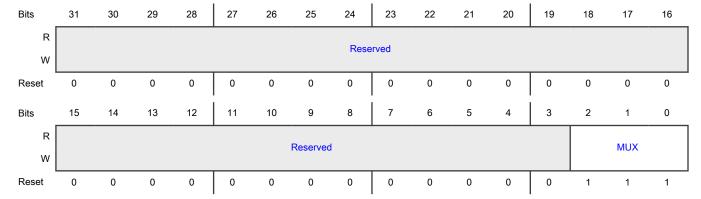

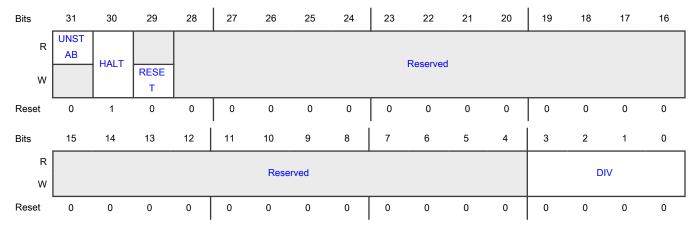

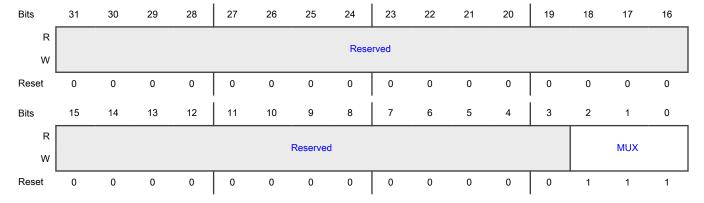

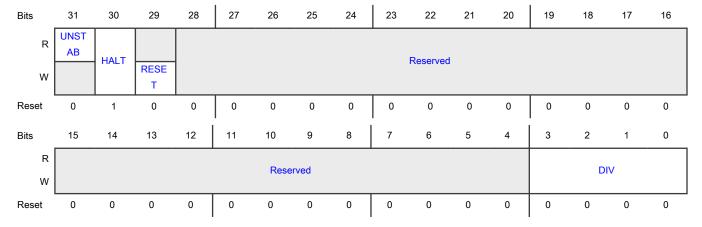

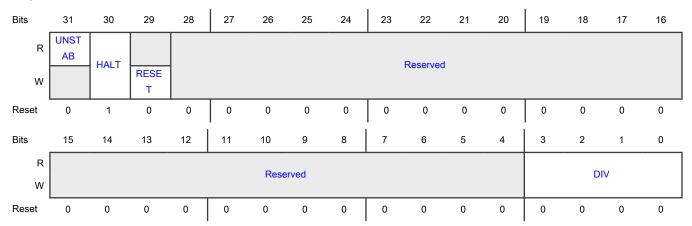

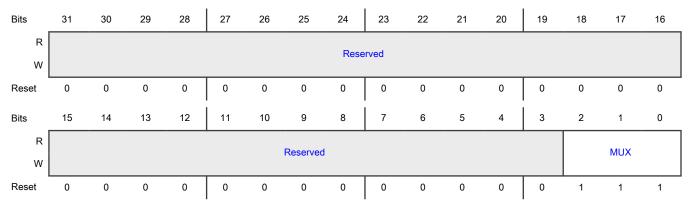

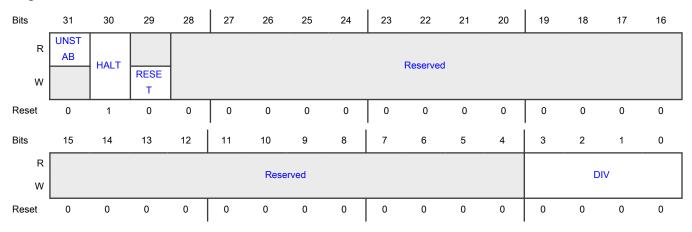

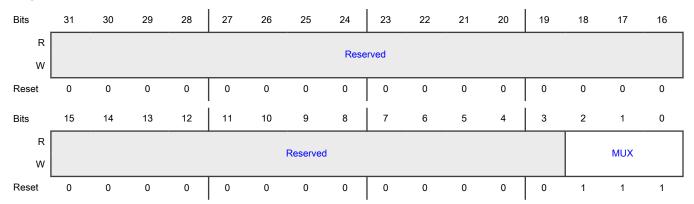

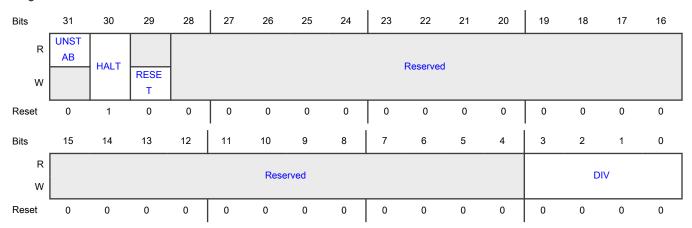

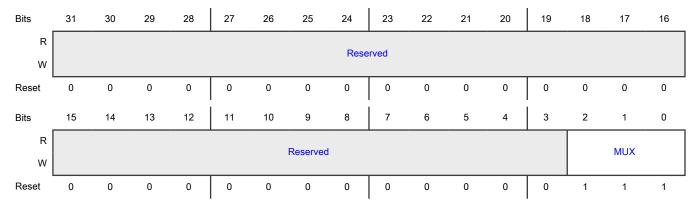

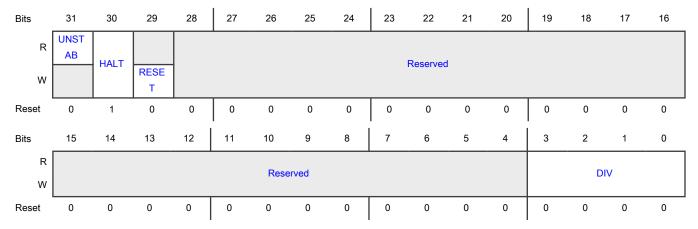

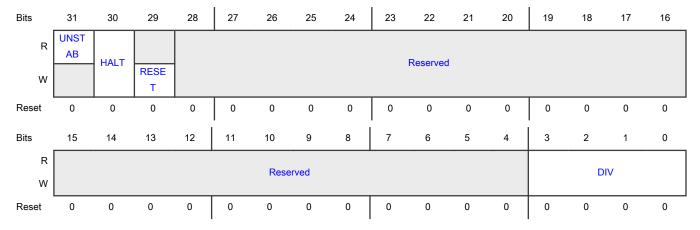

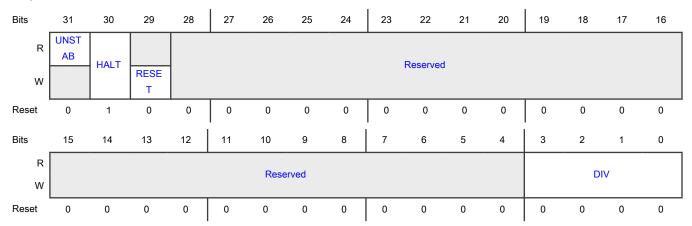

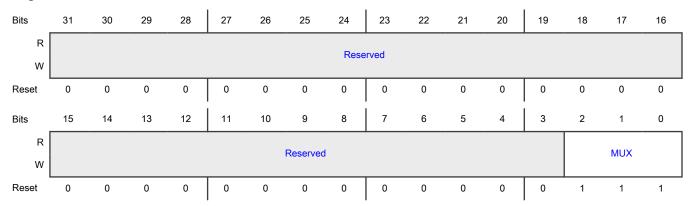

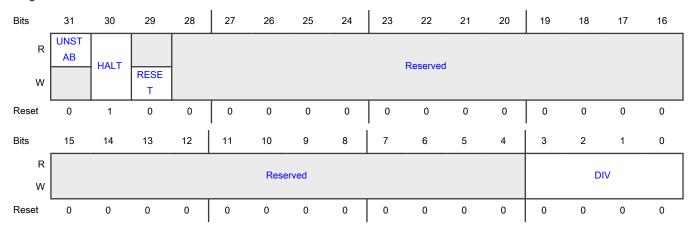

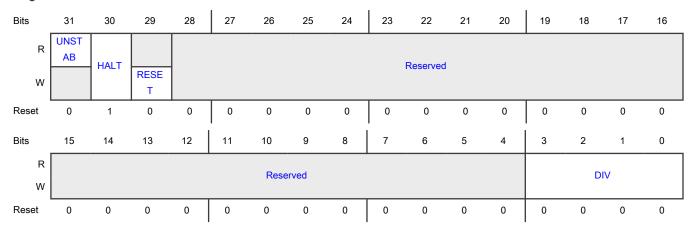

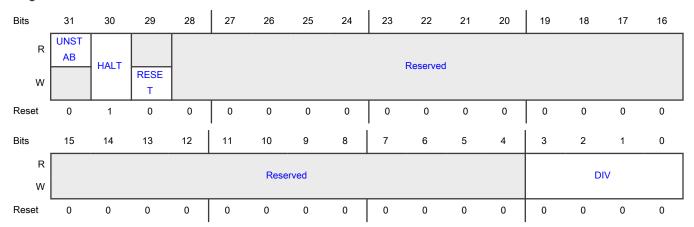

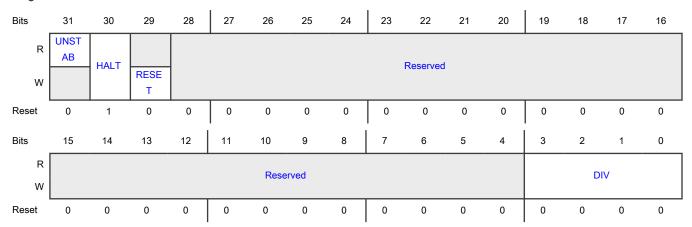

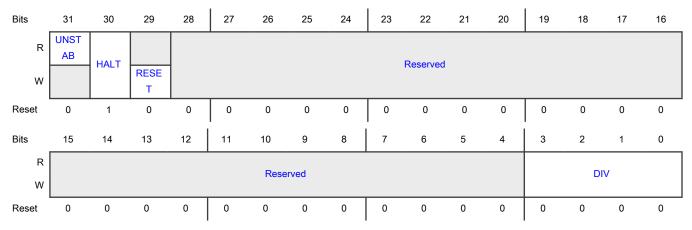

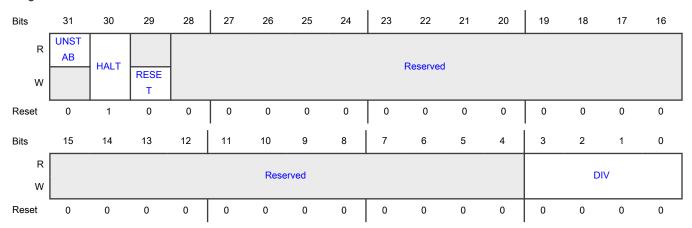

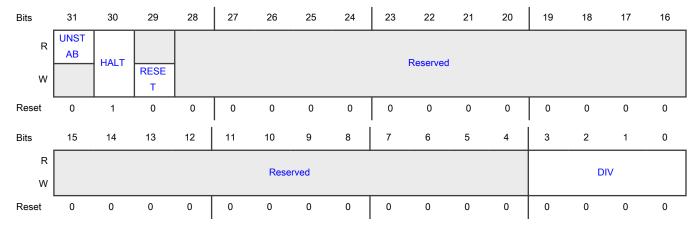

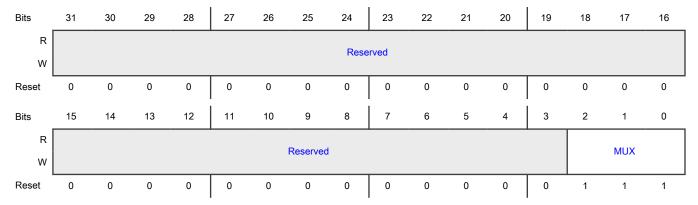

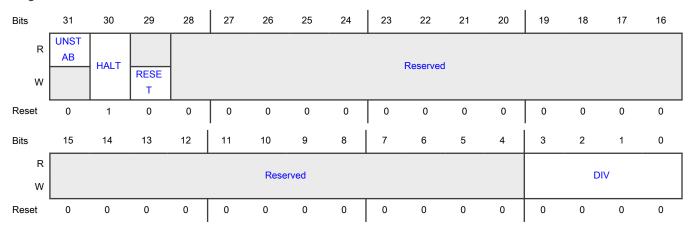

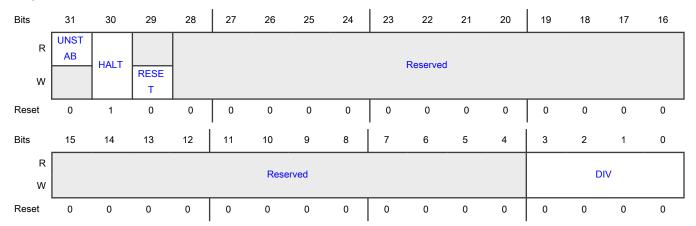

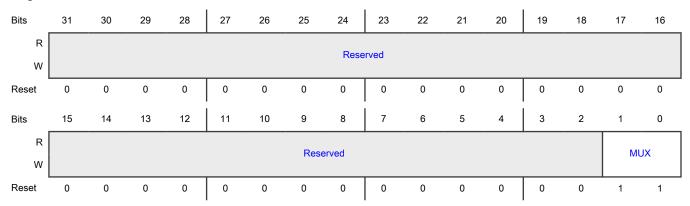

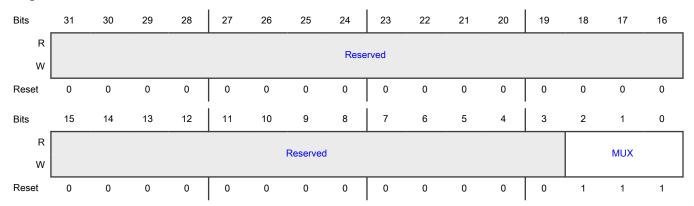

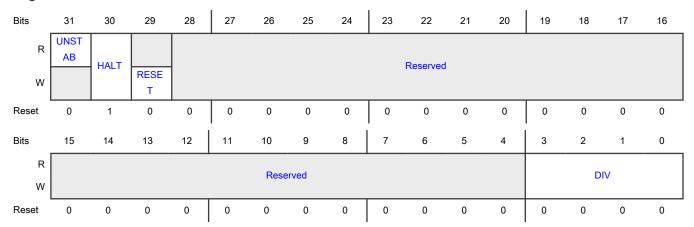

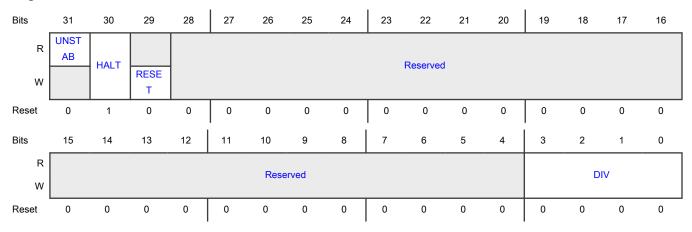

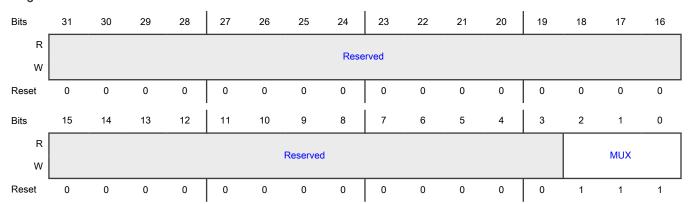

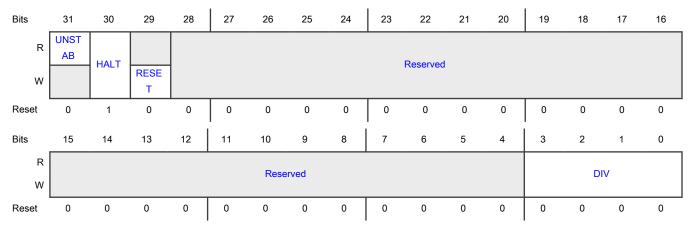

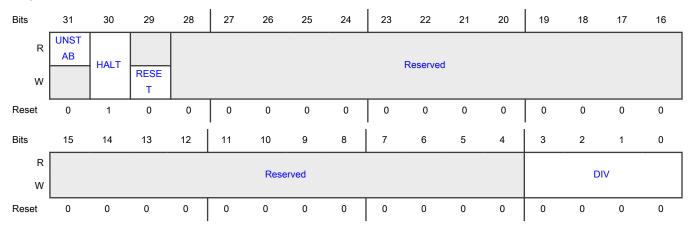

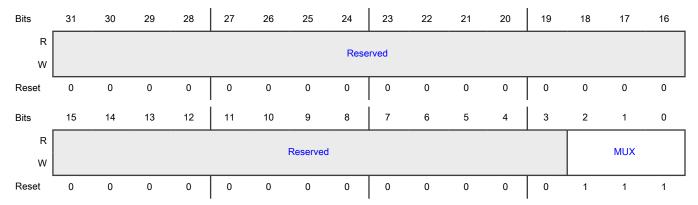

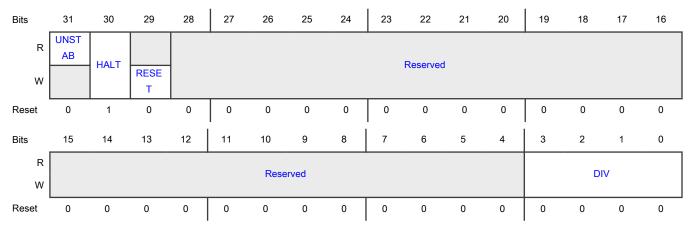

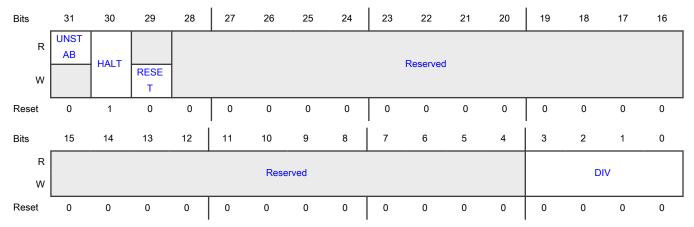

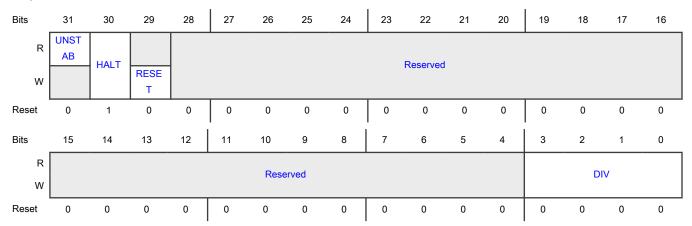

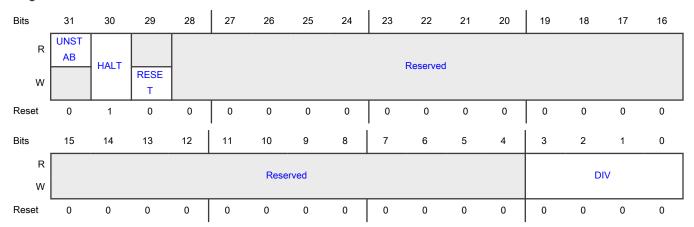

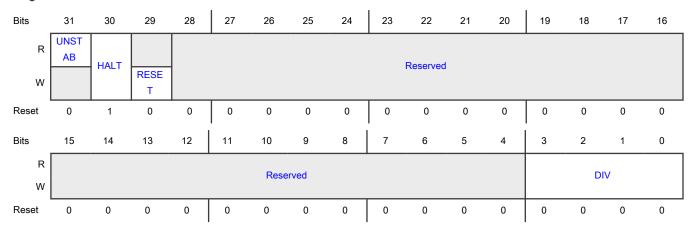

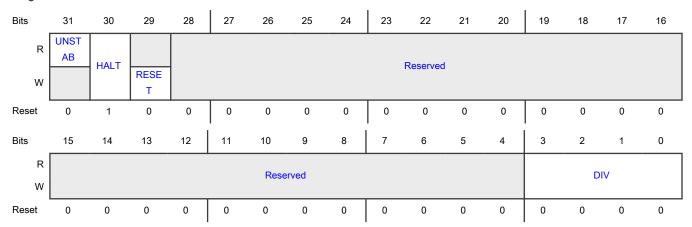

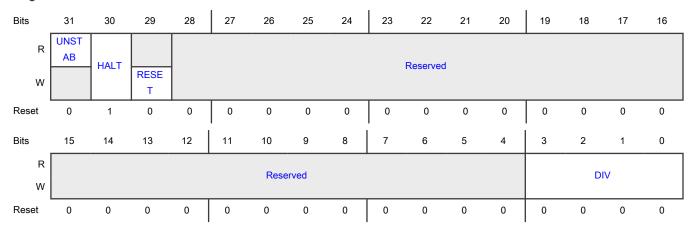

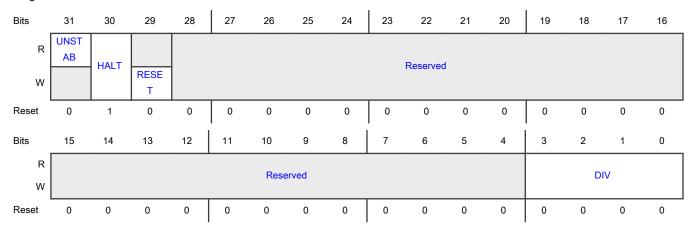

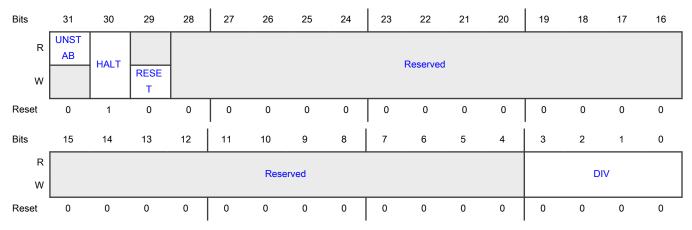

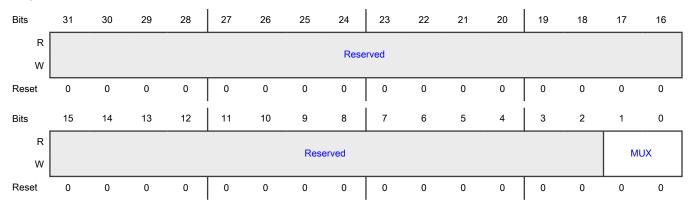

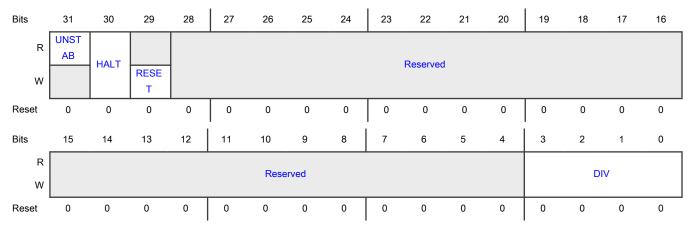

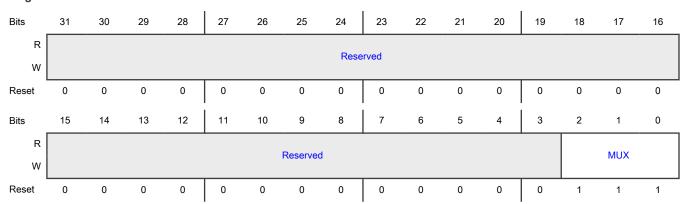

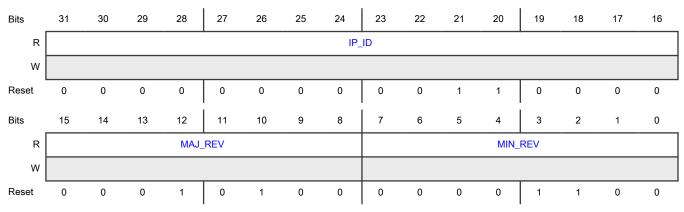

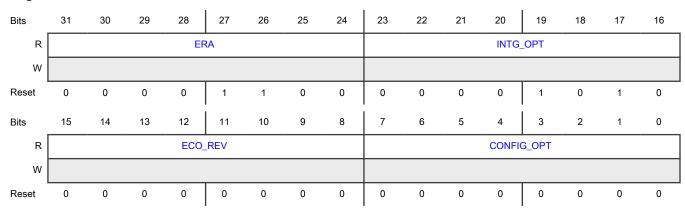

The following figure shows an example of chip-specific information that clarifies general module information presented later in the chapter. In this case, the chip-specific register reset values supersede the reset values that appear in the register diagram.

7 / 584

## 1.3.2 Chip-specific information that refers to a different chapter

Related chip-specific information may be provided in different chapters of the manual. The following figure shows an example of two such connected pieces of information. In this case, read both before you proceed.

#### Chapter 10 Chapter 9 Crossbar Integrity Checker (XBIC) Crossbar Switch (XBAR) 10.1 Chip-specific XBIC information 9.1 Chip-specific XBAR information This chip has one instance of the XBIC module. This chip has one instance of the XBAR module. 10.1.1 XBIC controller and target assignments 9.1.1 XBAR controller and target assignments The XBIC identifies each XBAR controller and target in terms of the controller or target' The following table lists the XBAR physical port numbers and logical IDs for all controller ports on this SoC. Each port number matches the default priority assigned to the corresponding physical controller port. This default priority equals the reset value of the priority field for each controller port in the PRSy registers. physical port number. See the "Physical controller port" assignments in Table 9-1 and the "target port" assignments in Table 9-2. •A priority value of 0 is the highest priority. There is no "disabled" value for the 10.1.2 Unimplemented MCR and ESR fields •A Nexus\_3 module and core data bus share the same physical controller port for each On this chip, the MCR[SE5] and ESR[DPSE5] fields are not implemented. In XBIC Module Control Register (XBIC\_MCR) and XBIC Error Status Register (XBIC\_ESR), these fields are reserved. The logical controller ID corresponds to the logical address provided by the controller module and is unique for each module. The logical controller IDs are used by the bus controllers connected to the XBAR. The Nexus controller is identified by setting the MSB in the 4-bit field that supplies the controller ID number. 10.2 Overview Table 9-1.XBAR controller ports and logical controller IDs The Crossbar Integrity Checker (XBIC) verifies the integrity of the crossbar transfers For forward signals (controller to target), it is done by verifying the integrity of the attribute information using an 8-bit Error Detection Code (EDC). The EDC detects any single- or double-bit errors in the attribute information and signals the Fault Collection and Control Unit (FCCU) when an error is detected. For feedback signals (target to controller), it is done by comparing the consistency of the signals during the AHB dataphase. There are three signals from target to controller, hready, hresp0, and hresp2. If any of the controller signals is different from the target signals during dataphase, the error will be reported in the Error Status Register. Sample Reference Manual

#### Figure 3. Example of chip-specific information that refers to a different chapter

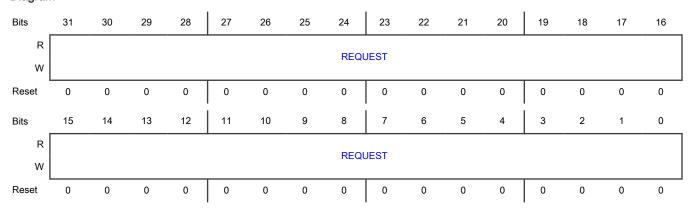

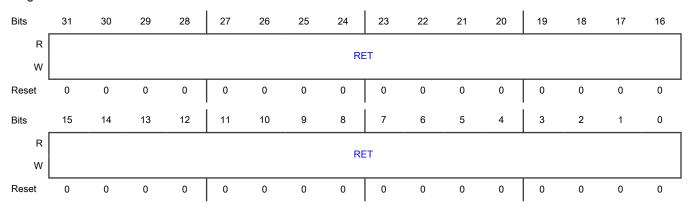

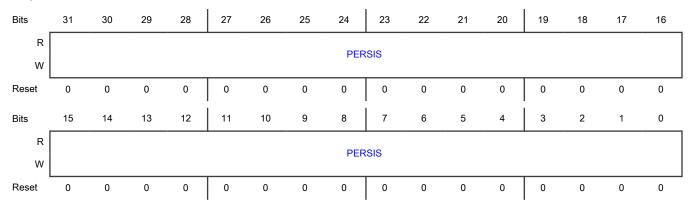

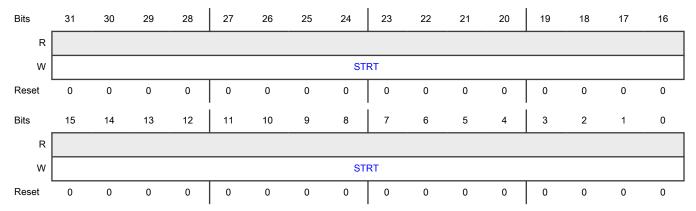

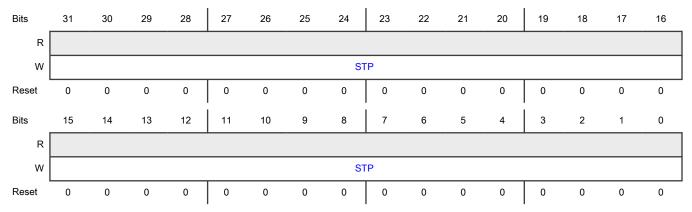

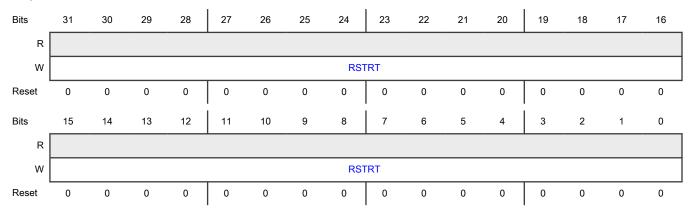

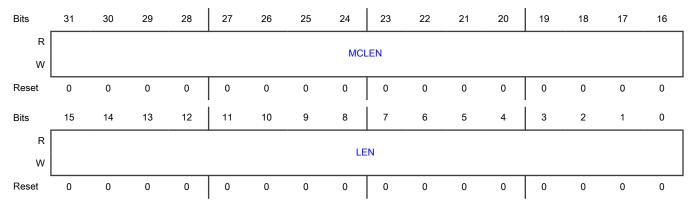

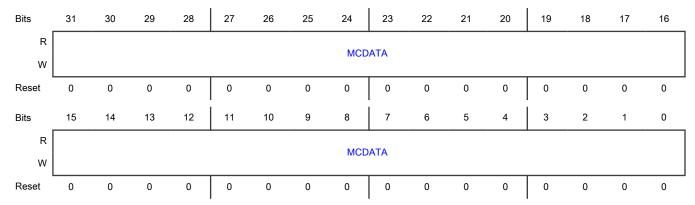

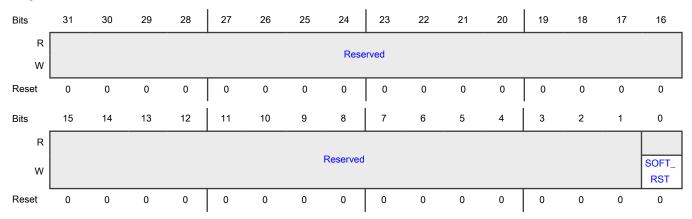

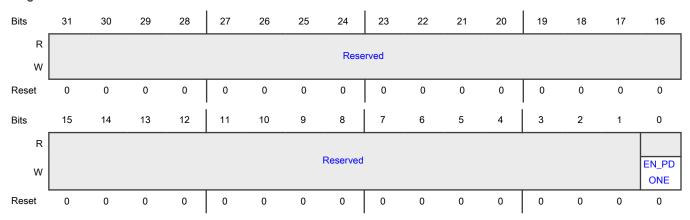

#### 1.4 Register descriptions

Module chapters present register information in the following:

- · Memory maps, which contain:

- An offset from the module's base address

- The mnemonic and name of each register

- The width of each register (in bits)

- The reset value of each register

- Register figures

- · Field-description tables

- · Associated text

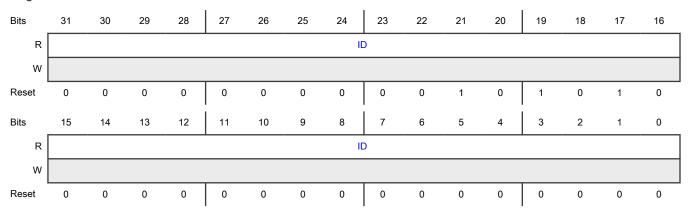

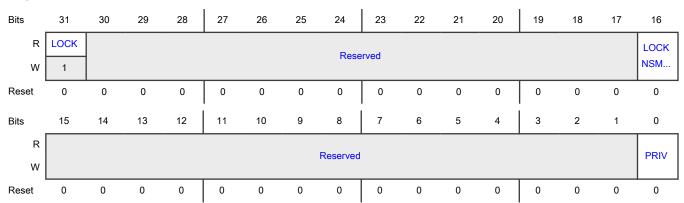

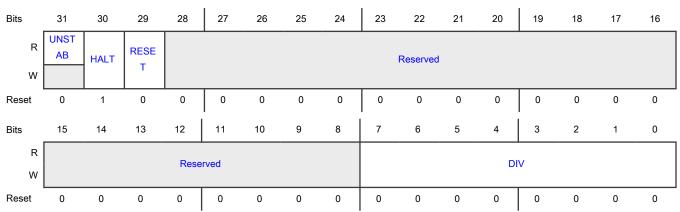

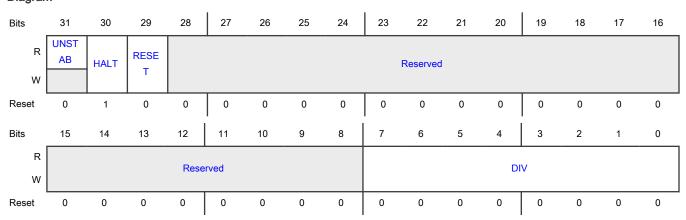

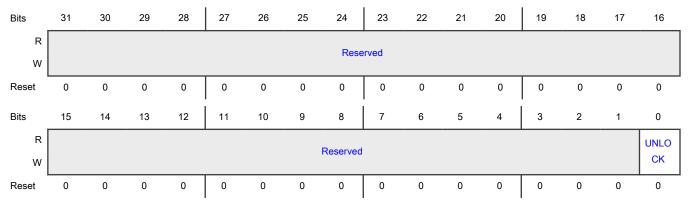

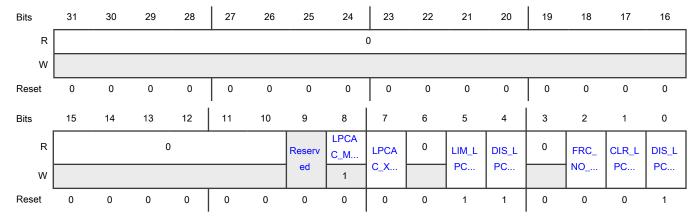

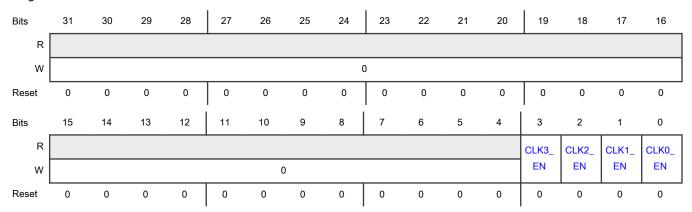

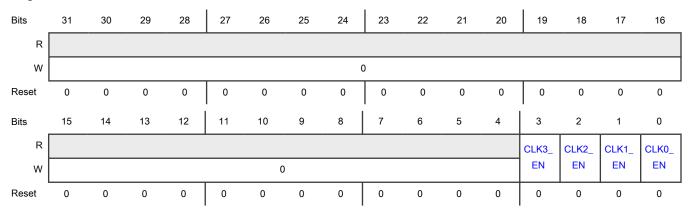

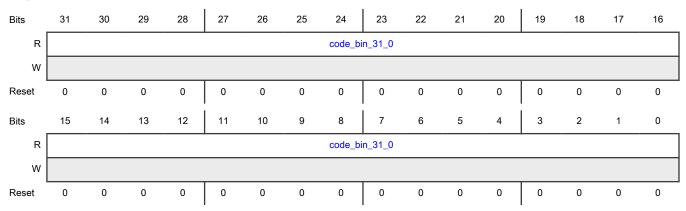

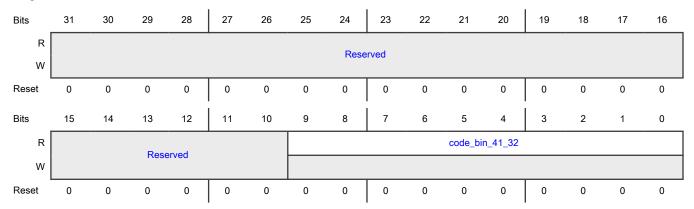

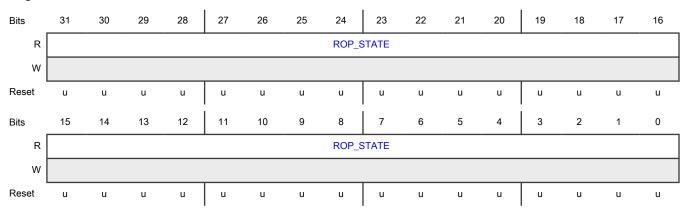

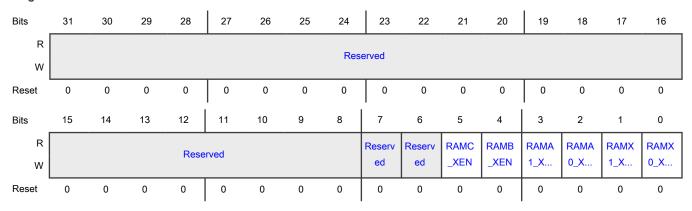

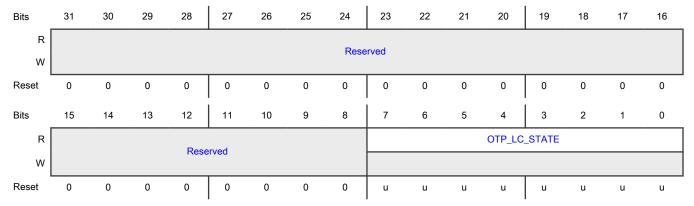

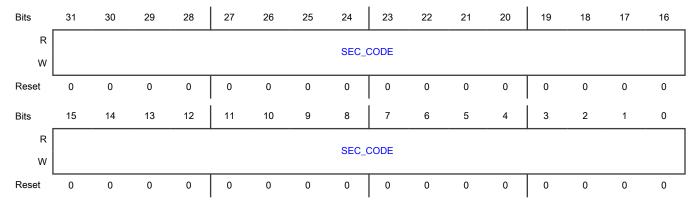

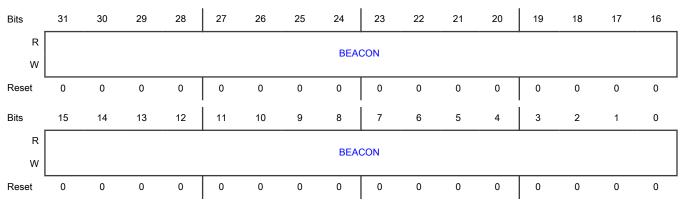

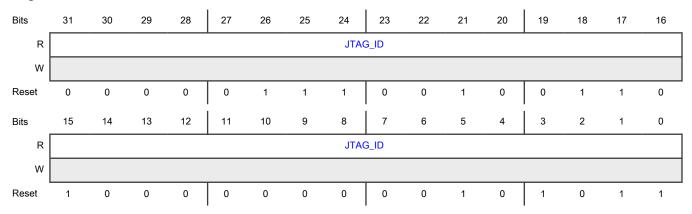

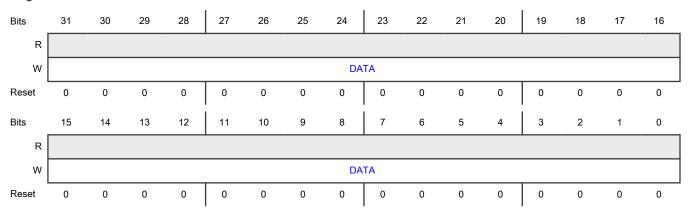

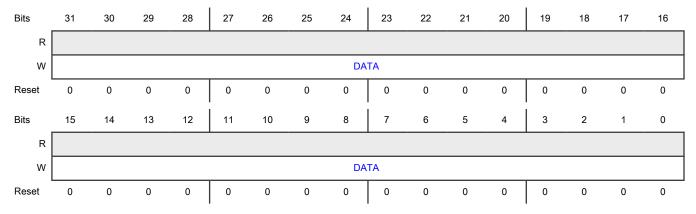

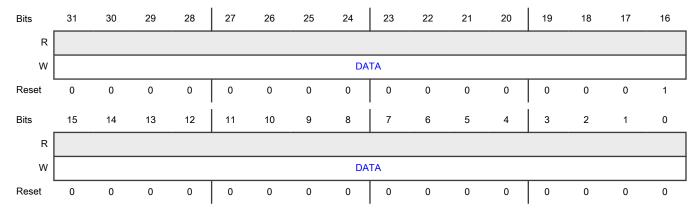

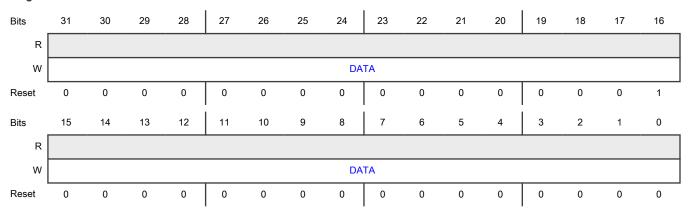

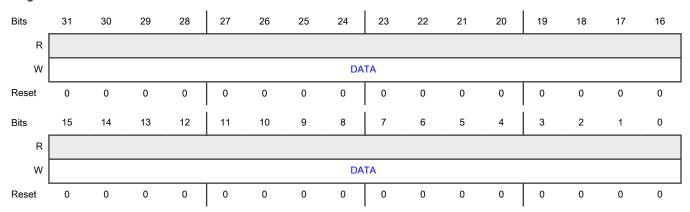

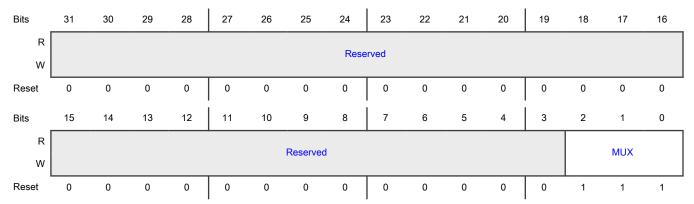

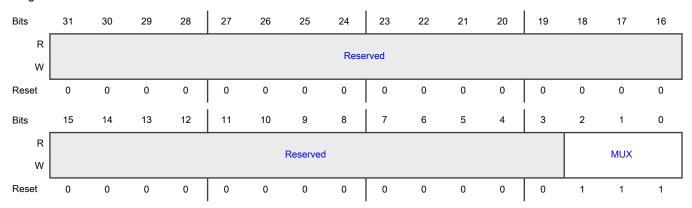

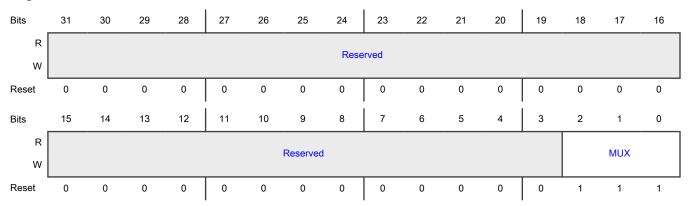

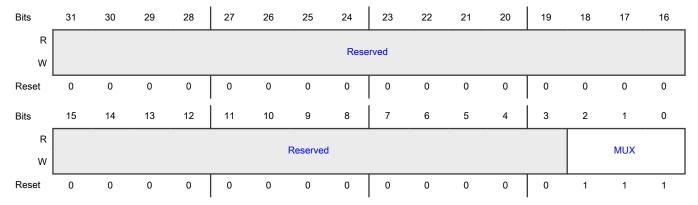

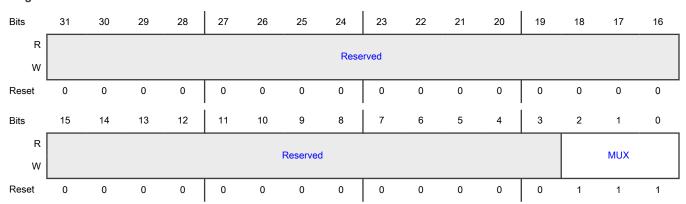

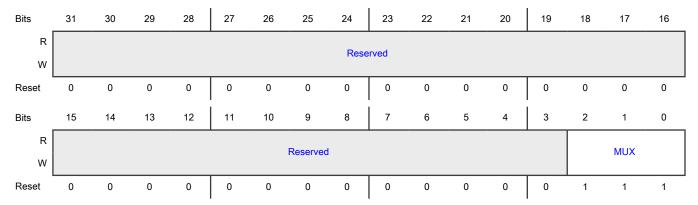

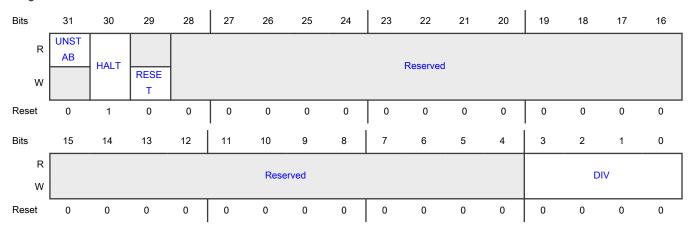

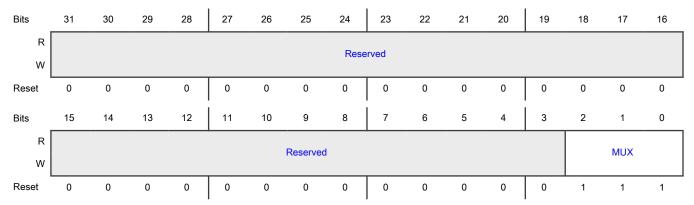

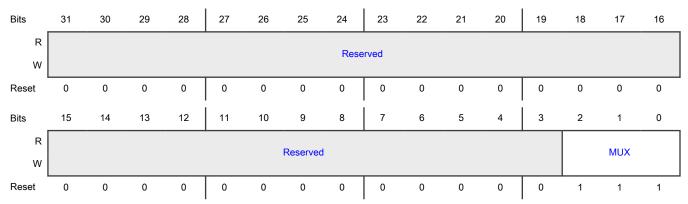

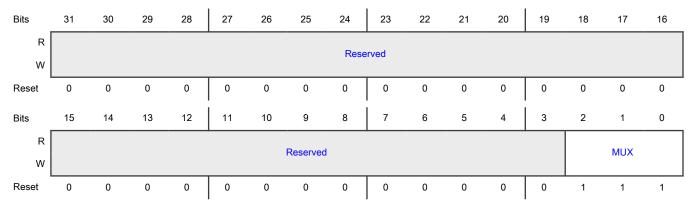

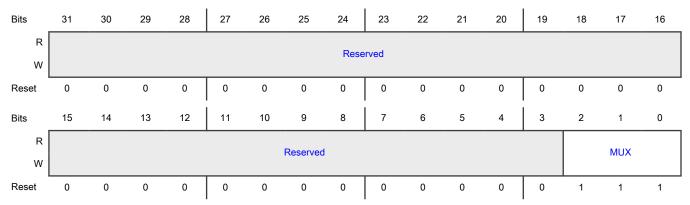

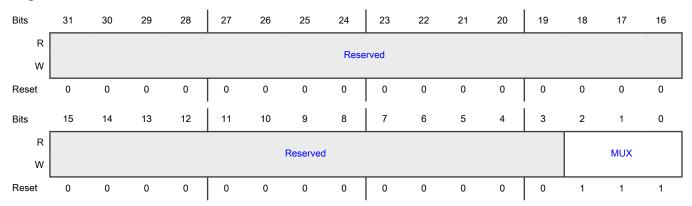

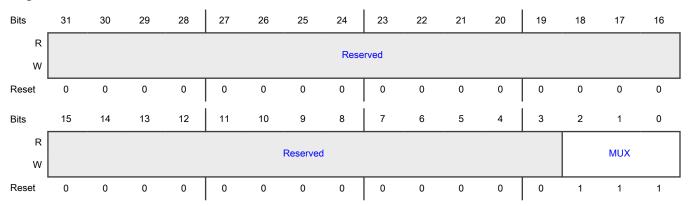

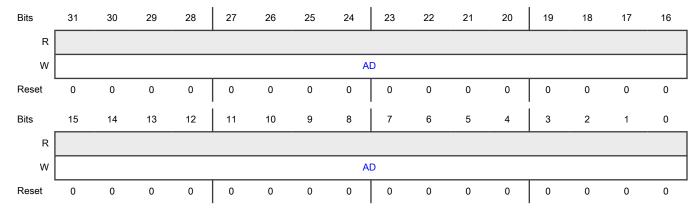

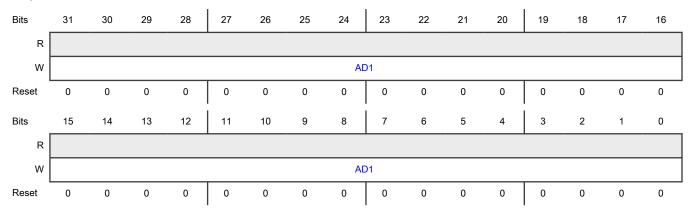

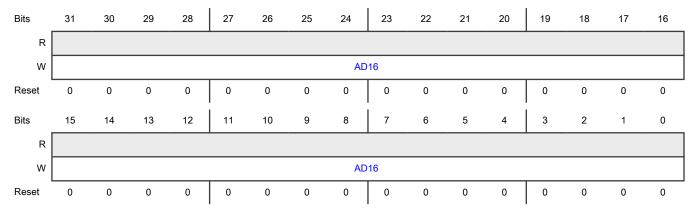

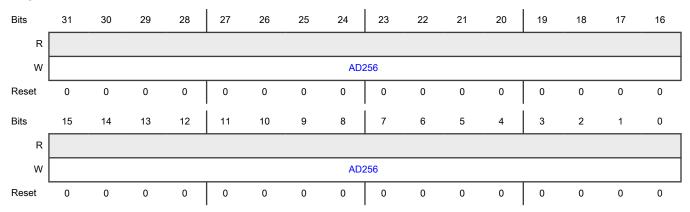

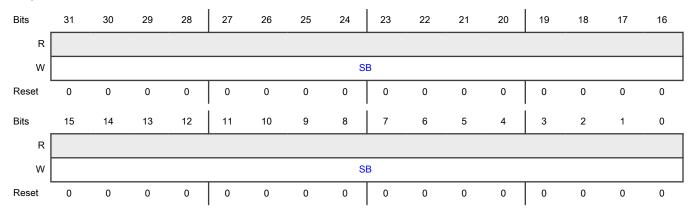

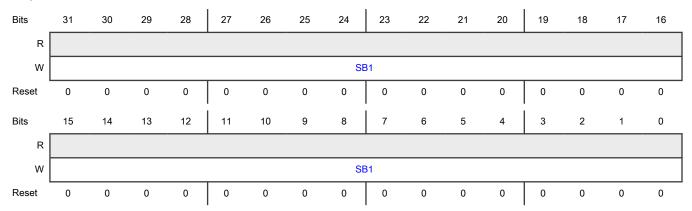

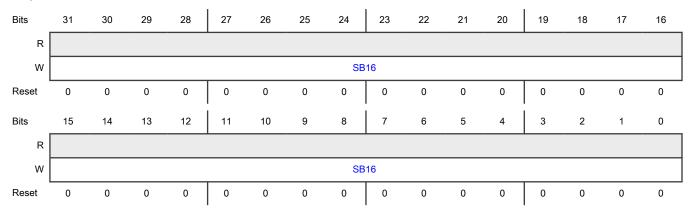

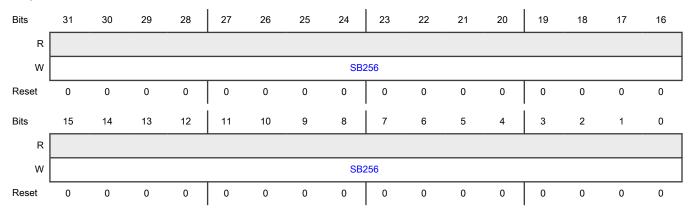

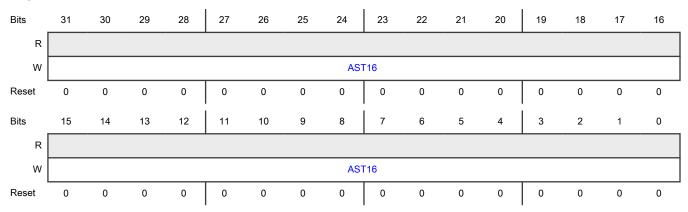

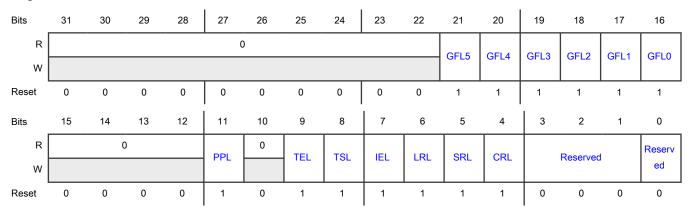

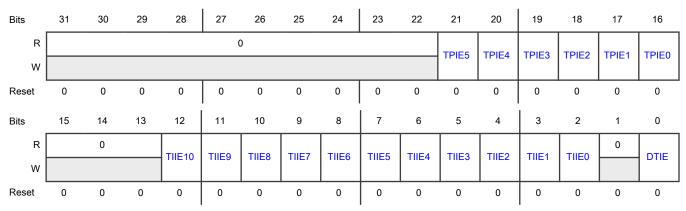

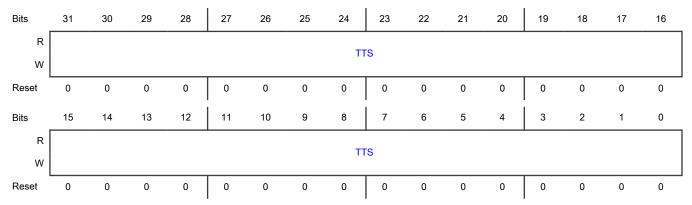

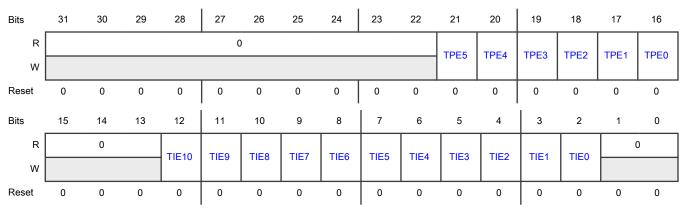

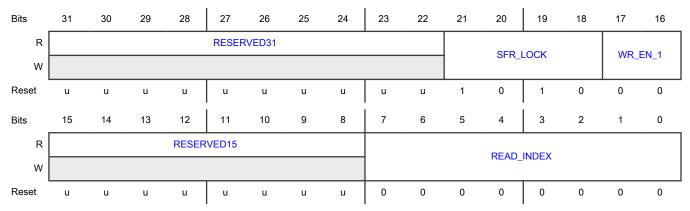

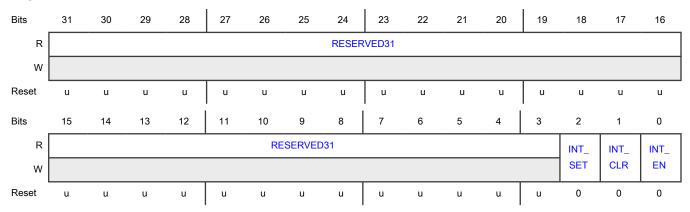

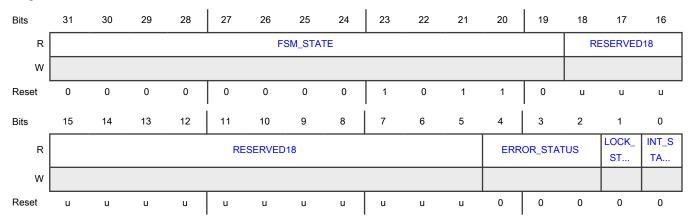

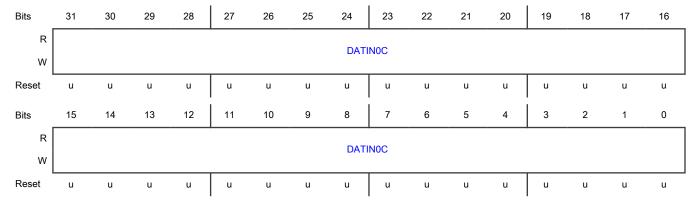

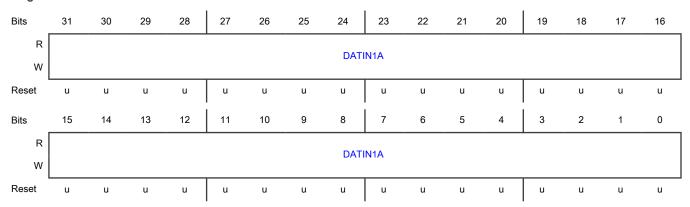

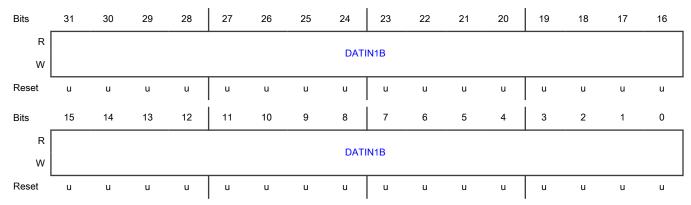

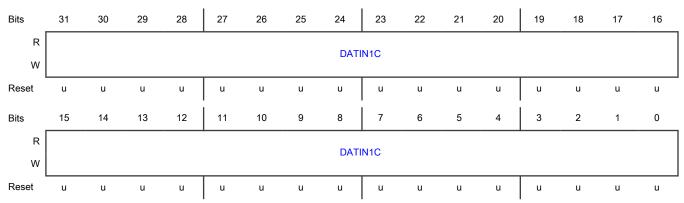

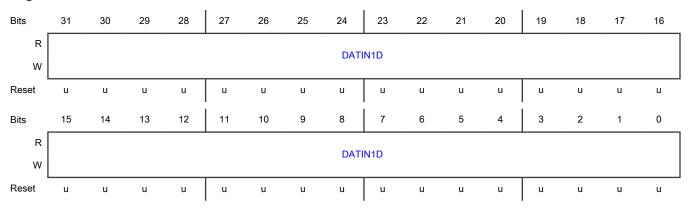

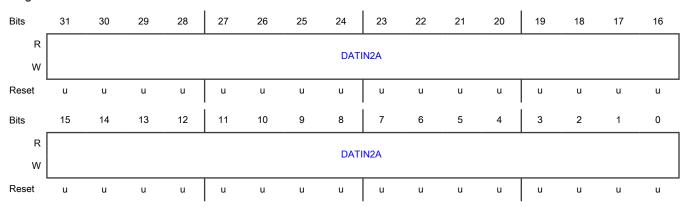

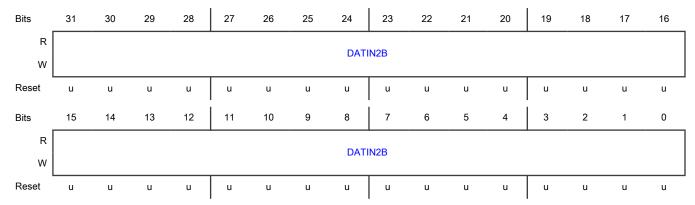

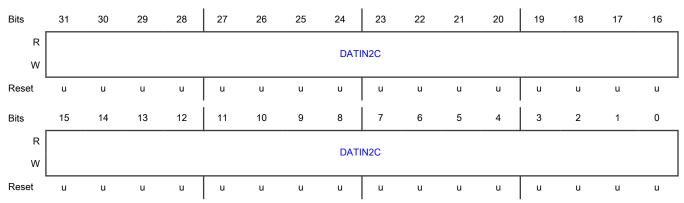

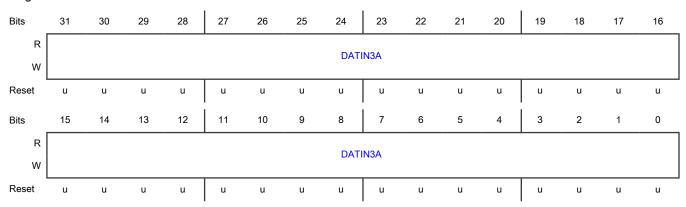

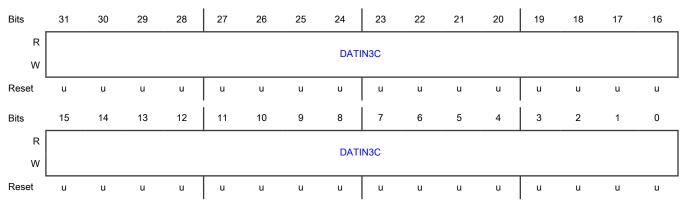

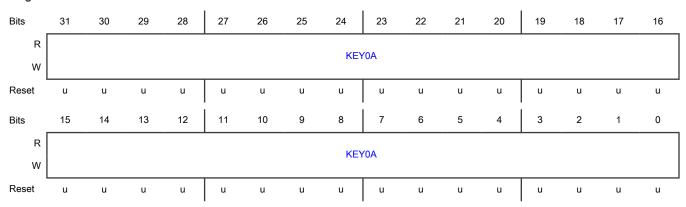

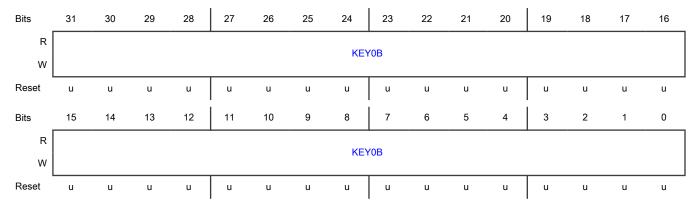

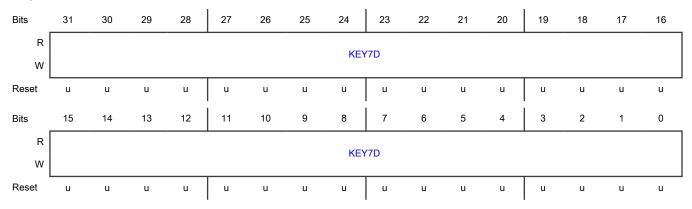

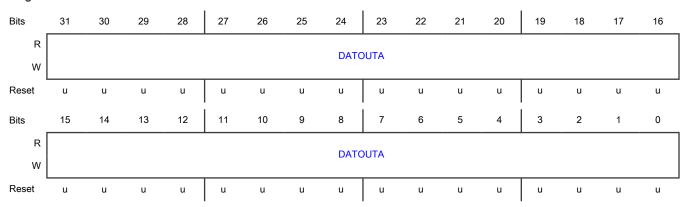

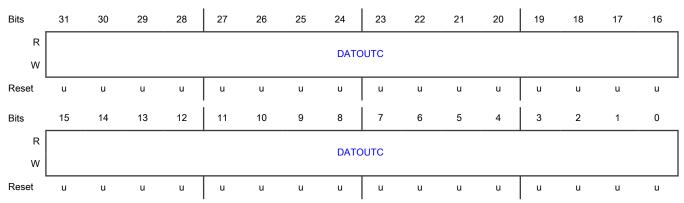

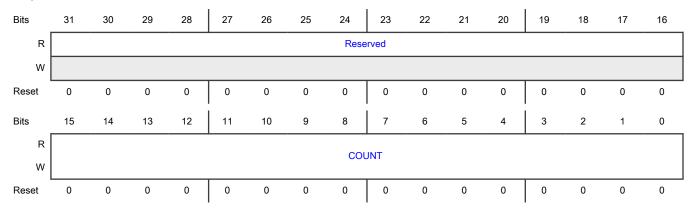

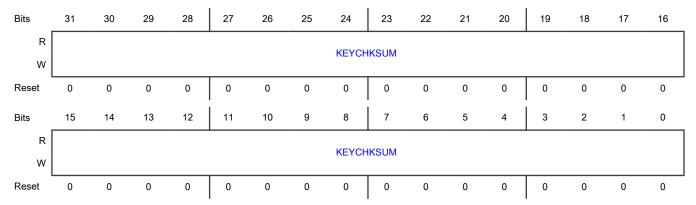

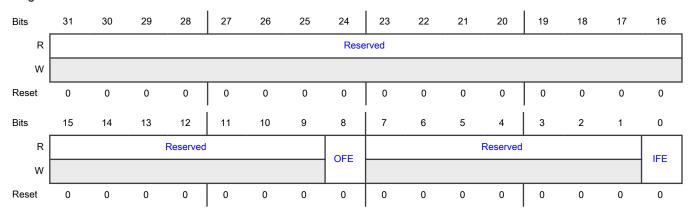

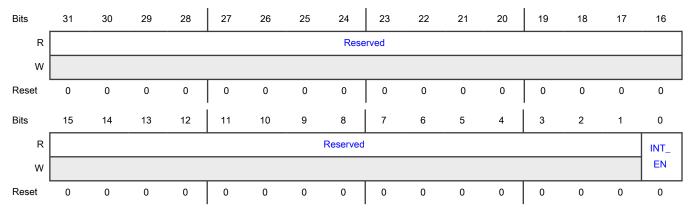

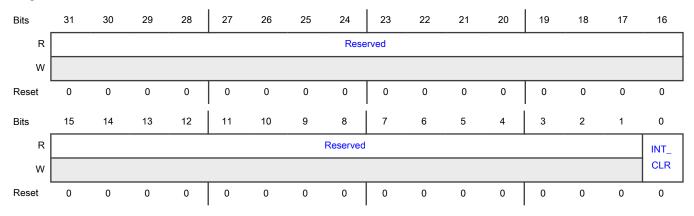

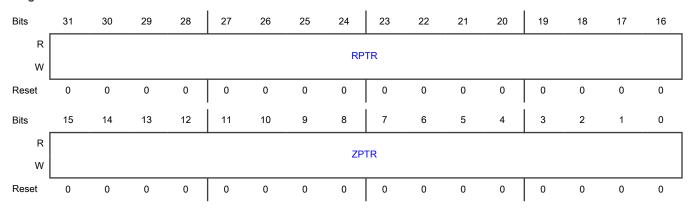

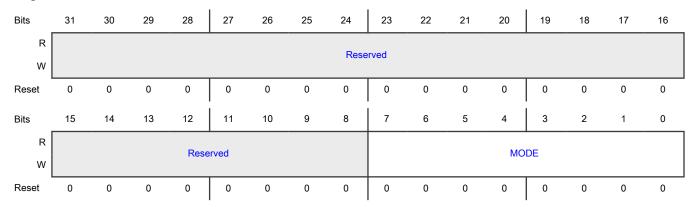

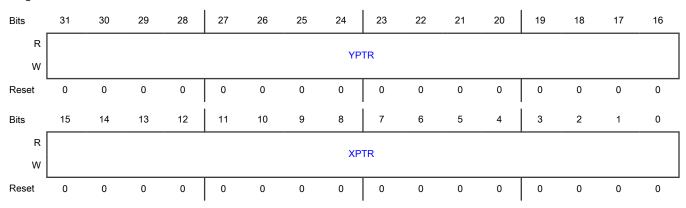

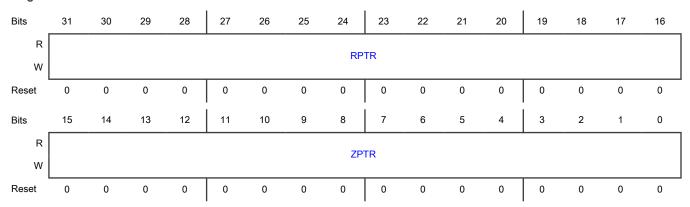

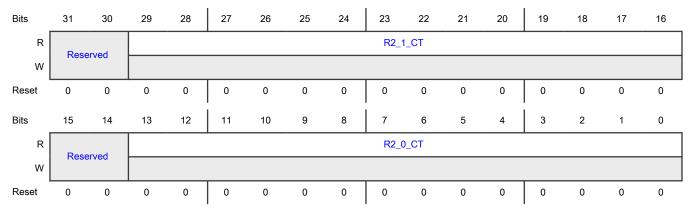

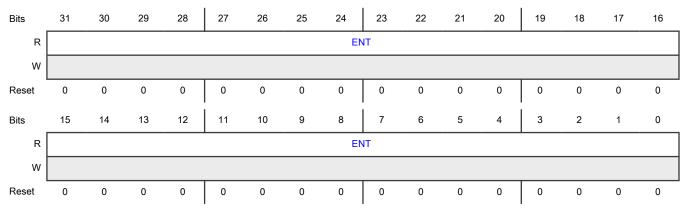

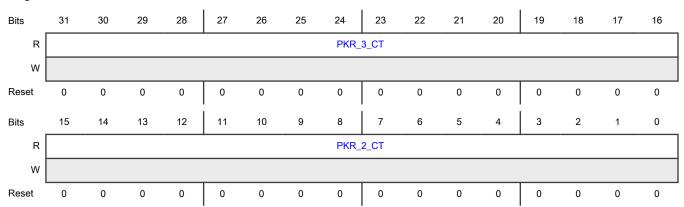

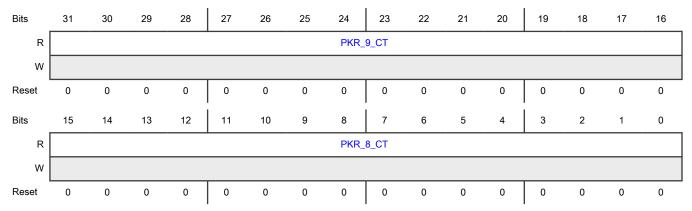

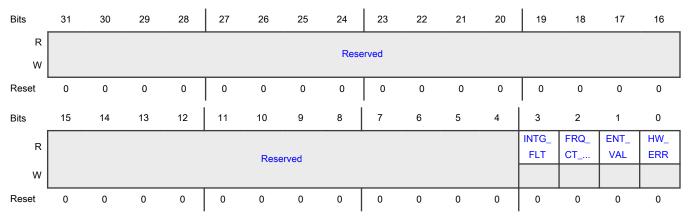

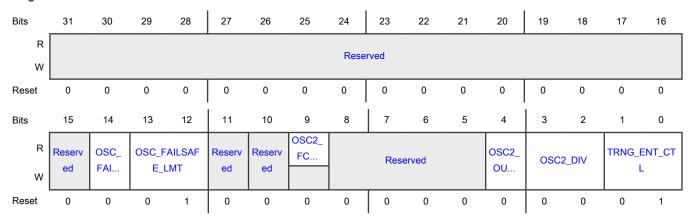

The following figure shows register figure conventions used throughout the manual.

| Access type | Access description           | DITA output         | Effect of Write on Value                                                                                                        | Readback<br>Value   |

|-------------|------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|

| RW          | Read/write                   | R<br>W Mnemonic     | Changes to Written Value                                                                                                        | Current Valu        |

| RO          | Read-only                    | R Mnemonic          | No Effect                                                                                                                       | Current Valu        |

| RU          | Reserved,<br>unimplemented   | R<br>W Reserved     | No Effect                                                                                                                       | Value<br>Undefined  |

| ROZ         | Reserved,<br>Read-only zero  | R 0<br>W            | No Effect                                                                                                                       | Returns All<br>Zero |

| ROO         | Reserved,<br>Read-only one   | R 1<br>W            | No Effect                                                                                                                       | Returns All<br>Ones |

| wo          | Write-only                   | R<br>W Mnemonic     | Changed to Written Value                                                                                                        | Value<br>Undefined  |

| woz         | Reserved,<br>Write-only zero | R<br>W 0            | Write Value Must Be All 0s.                                                                                                     | Value<br>Undefined  |

| woo         | Reserved,<br>Write-only one  | R<br>W 1            | Write Value Must Be All 1s.                                                                                                     | Value<br>Undefined  |

| WOC         | Write zero to clear          | R Mnemonic<br>W w0c | If a Bit in the Written Value is a 0, the Corresponding Bit in the Field is Set to 0. Otherwise, the Field Bit is Not Affected. | Current Valu        |

| W1C         | Write one to clear           | R Mnemonid<br>W w1c | If a Bit in the Written Value is a 1, the Corresponding Bit in the Field is set to 0. Otherwise, the Field Bit is Not Affected. | Current Valu        |

| R2C         | Read to clear                |                     | Value is cleared following the read operation                                                                                   | Current Valu        |

| ROWZ        | Read-only, writes zero       | R Mnemonid<br>W 0   | Write Value Must Be All 0s                                                                                                      | Current Valu        |

| ROWO        | Read-only writes one         | R Mnemonic<br>W 1   | Write Value Must Be All 1s                                                                                                      | Current Valu        |

| ROWU        | Ready-only writes undefined  | R Mnemonic W —      | Writes Operation Undefine                                                                                                       | Current Valu        |

| WORZ        | Write-only reads zero        | R 0<br>W Mnemonic   | Changes to Written Value                                                                                                        | Returns All<br>Zero |

| WORO        | Write-only reads one         | R 1<br>W Mnemonic   | Changes to Written Value                                                                                                        | Returns All<br>Ones |

| WORU        | Write-only reads undefined   | R —<br>W Mnemonic   | Changes to Written Value                                                                                                        | Value<br>Undefined  |

Figure 4. Register figure conventions

#### NOTE

Reset values of reserved locations documented in this manual are subject to change and must not be used for diagnostic purposes.

#### 1.5 Conventions

#### 1.5.1 Notes and cautions

Specific information is provided as part of notes and cautions throughout this manual.

NOTE

Emphasizes information that deserves extra attention.

CAUTION

Informs you of situations that could lead to highly undesirable outcomes—such as damage to the chip or irreversible malfunction.

#### 1.5.2 Numbering systems

The following suffixes identify different numbering systems:

Table 1. Numbering systems

| This suffix | Identifies a                                                                                                                                                      |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b           | Binary number. For example, the binary equivalent of the number 5 is mentioned as 101b. In some cases, <i>0b</i> is prefixed to binary numbers.                   |

| d           | Decimal number. Decimal numbers are followed by this suffix only when there is a possibility of confusion. In general, decimal numbers are used without a suffix. |

| h           | Hexadecimal number. For example, the hexadecimal equivalent of the number 60 is mentioned as 3Ch. In some cases, <i>0x</i> is prefixed to hexadecimal numbers.    |

#### 1.5.3 Typographic notation

The following typographic notations are used throughout this document:

Table 2. Typographic notation

| Example                     | Description                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x and other italicized text | The italicized, lowercase <i>x</i> is used as a placeholder for replaceable numbers. In general, italicized text is used for titles of publications and for emphasis. Additionally, italics could be used for metasymbols in syntax descriptions. Plain lowercase letters are used as placeholders for single letters and numbers. |

| code font                   | Fixed-width font (such as Courier) used for code. It is used for a letter, word, or phrase that you want the user to type. For example, "Type Read and press Enter."                                                                                                                                                               |

|                             | This type of font is also used for instruction mnemonics, directives, symbols, subcommands, parameters, operators, computer-language elements, code listings, commands that appear in running text, and for sample code. Instruction mnemonics and directives in text and tables are mentioned in all caps; for example, BSR.      |

| SR[SCM]                     | A mnemonic in square brackets represents the name of a register field. This example refers to the Scaling Mode (SCM) field in the Status Register (SR).                                                                                                                                                                            |

| REVNO[6:4], XAD[7:0]        | Numbers in brackets that are separated by a colon represent either:                                                                                                                                                                                                                                                                |

|                             | A subset of a register's named field                                                                                                                                                                                                                                                                                               |

Table 2. Typographic notation (continued)

| Description                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For example, REVNO[6:4] refers to bits 6-4 that are part of the COREREV field occupying bits 6-0 of the REVNO register.                                                                                                                                        |

| A continuous range of individual signals of a bus                                                                                                                                                                                                              |

| For example, XAD[7:0] refers to signals 7-0 of the XAD bus.                                                                                                                                                                                                    |

| A period separates the elements of a hierarchy: subsystem.module.register. For example:     SWT.TO means that the TO register is located in the SWT module.     SMU.XRDC.CR means that the CR register is located in the XRDC module within the SMU subsystem. |

|                                                                                                                                                                                                                                                                |

## 1.5.4 Special terms

The following terms have special meanings.

Table 3. Special terms

| Term                   | Meaning                                                                                                                                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asserted               | Refers to the state of a signal as follows:                                                                                                                                                                               |

|                        | An active-high signal is asserted when high (1).                                                                                                                                                                          |

|                        | An active-low signal is asserted when low (0).                                                                                                                                                                            |

| Deasserted             | Refers to the state of a signal as follows:                                                                                                                                                                               |

|                        | An active-high signal is deasserted when low (0).                                                                                                                                                                         |

|                        | An active-low signal is deasserted when high (1).                                                                                                                                                                         |

|                        | In some cases, deasserted signals are described as <i>negated</i> .                                                                                                                                                       |

| Reserved               | Refers to memory space, register, field, or programming setting. Writes to a reserved location can result in unpredictable functionality or behavior. You must:                                                           |

|                        | <ul> <li>Before writing to a location which contain reserved bits user must make sure the write<br/>operation will write the reserved bit with value specified as the reset value in NXP reference<br/>manual.</li> </ul> |

|                        | Consider undefined locations in memory to be reserved as reset value 0 shall be assumed. You might get a BERR(transfer error) response on access to undefined locations in memory.                                        |

|                        | If user reads data from memory area containing reserved bit, the value of reserved bits should be ignored and not used for any functional purposes.                                                                       |

|                        | NOTE                                                                                                                                                                                                                      |

|                        | BootROM could modify the reserved bit values after reset. Please refer to the BootROM settings attachment.                                                                                                                |

| Write 1 to clear (w1c) | Refers to the access type of a register field that is used to clear the field by writing the value 1 to it.                                                                                                               |

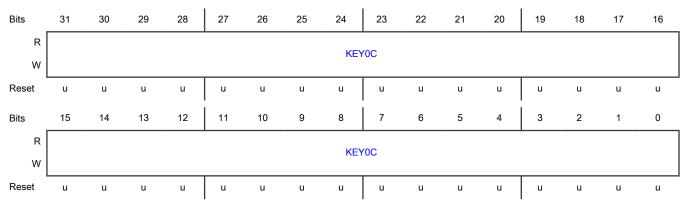

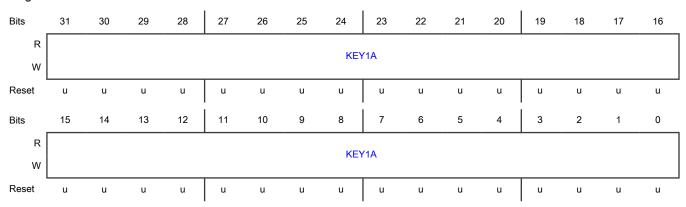

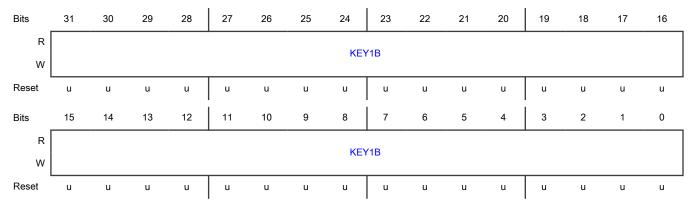

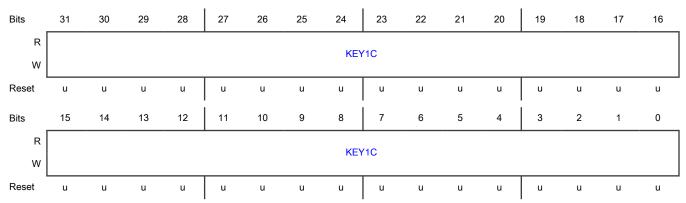

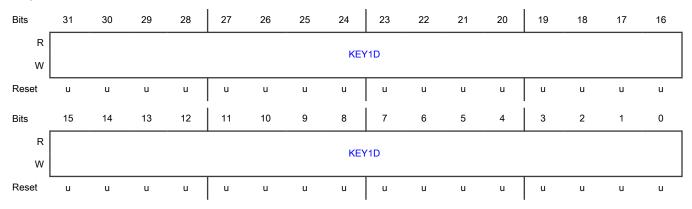

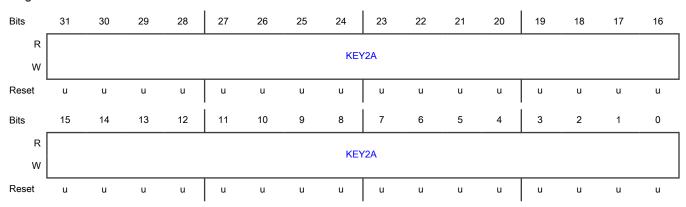

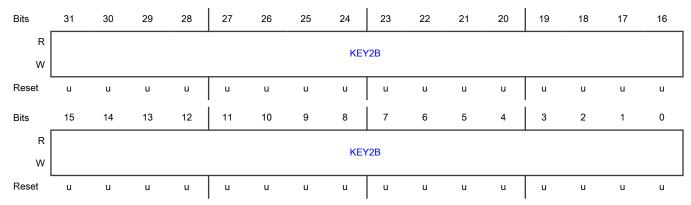

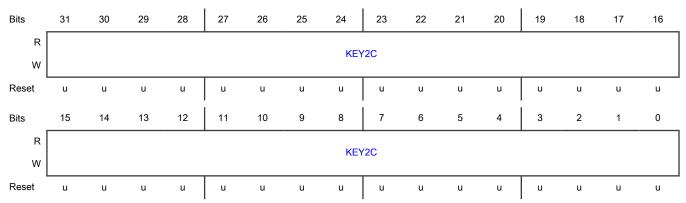

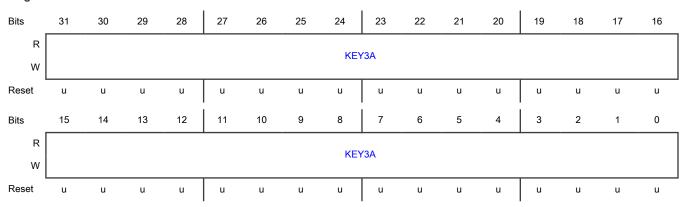

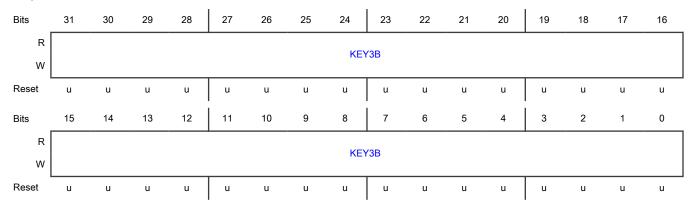

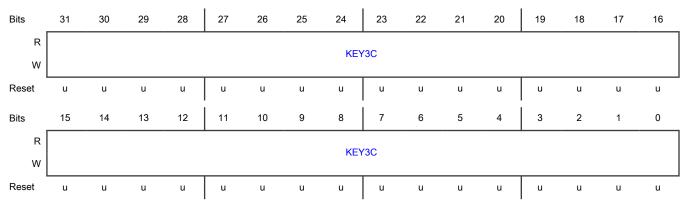

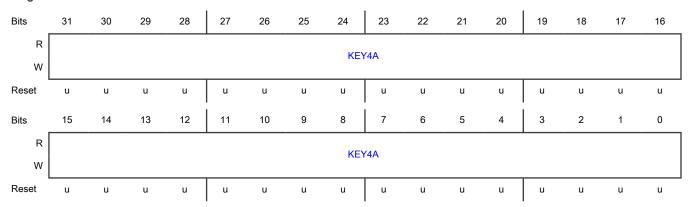

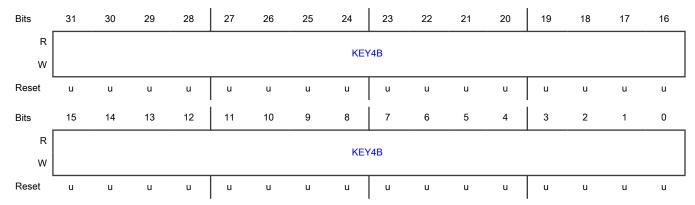

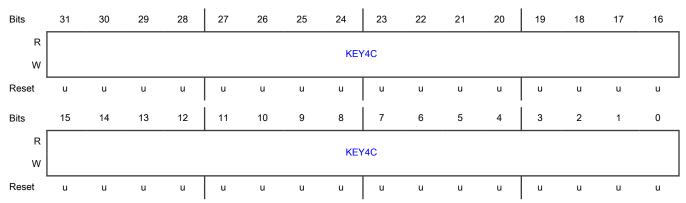

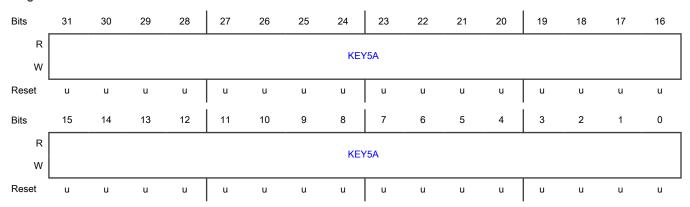

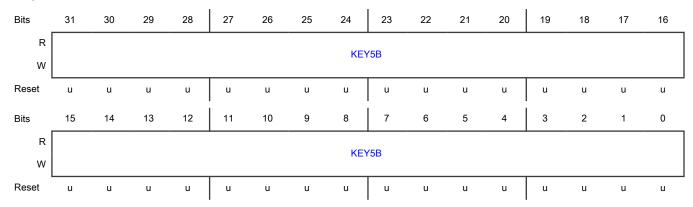

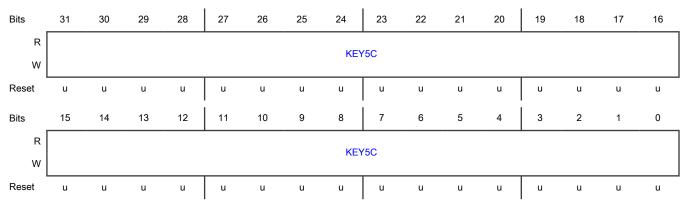

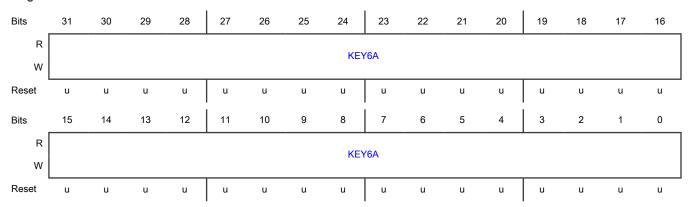

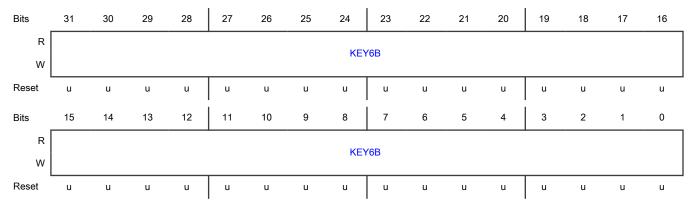

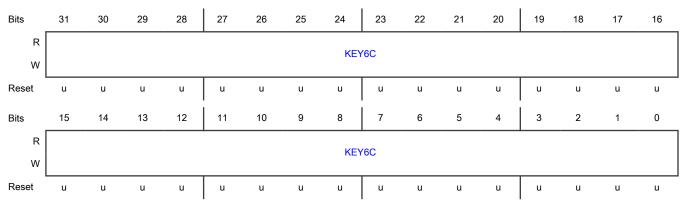

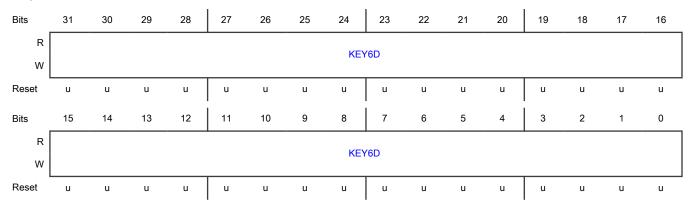

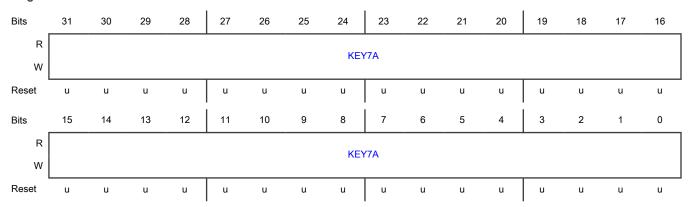

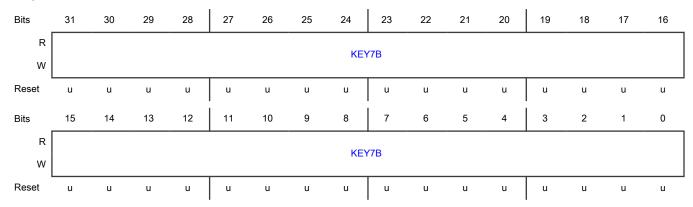

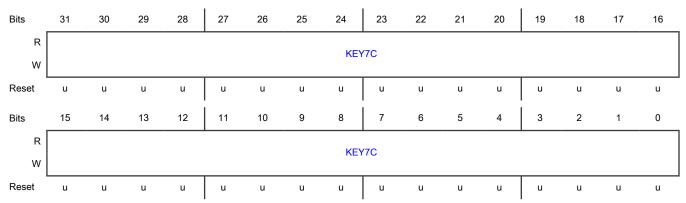

| Undefined (u)          | Refers to undefined reset values                                                                                                                                                                                          |

## 1.6 Editorial changes

Each new release of this document includes editorial improvements such as:

- Spelling

- Grammar

- Punctuation

- Voice

- Tense

- Capitalization

- Formatting

- Presentation

- Navigation

Reference Manual 12 / 584

## Chapter 2 Introduction

#### 2.1 Overview

This group of products expand the MCX Arm® Cortex®-M33 product offerings with multiple high-speed connectivity, operating up to 180 MHz, serial peripherals, timers, analog and low power consumption.

### 2.2 Target applications

This device has following target applications:

#### Industrial

- · Energy Storage and Management System

- · Smart Metering

- · Factory Automation

- Industrial HMI

- · Mobile Robotics Ecosystem

- · Motion Control and Robotics

- · Motor Drives

- Brushless DC Motor (BLDC) Control

- · Permanent Magnet Synchronous Motor (PMSM) Control

#### **Smart Home**

- · Home Control Panel

- · Major Home Appliances

- · Robotic Appliance

- · Smart Speaker

- Soundbar

- · Gaming Accessories

- · Smart Lighting

- · Smart Power Socket and Light Switch

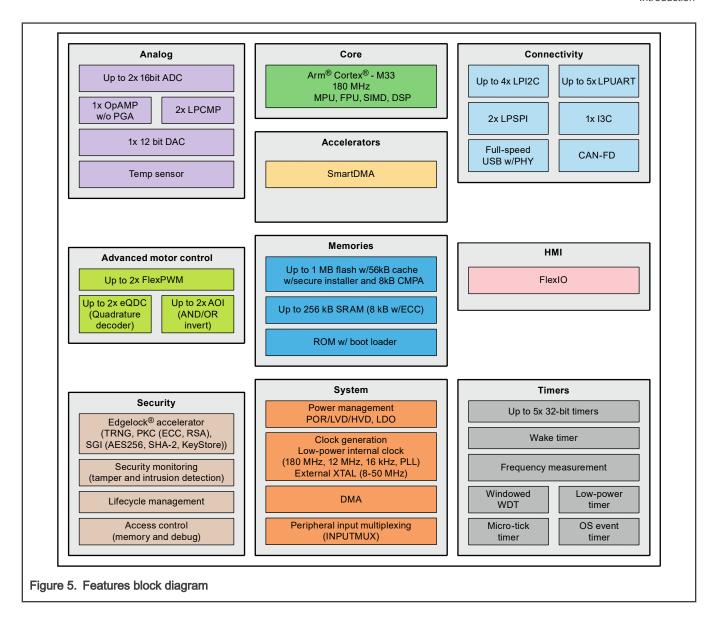

### 2.3 Block diagram

The following figure shows a top-level organization of the modules within the chip organized by functional category.

#### 2.4 Features

This group of products offer the following features:

- Core

- Arm 32-bit Cortex-M33 CPU, with FPU and DSP extension instruction set and MPU, no Trust Zone. 45 MHz at Mid Drive mode (1.0 V), 180 MHz at Over Drive mode (1.2 V)

- Nested Vectored Interrupt Controller

- Clock gating for core processor

- Multilayer AHB Bus Matrix

- MAU (Math Accelerator Unit), supports trigonometric, reciprocal, square, square root, sine, cosine and arctan algorithms

- SmartDMA, co-processor for applications such as parallel camera interface and keypad scanning

- Memories

- 1 MB Flash array implemented as single array. The smallest programming phrase should be 16 bytes.

- 128-bit + 9-bit ECC, 8 KB sector size

- 32 KB IFR0 + 8 KB IFR1 for Implicit-protected Flash Region(IFR)

- Flash Memory Controller

- · Line buffer

- · Prefetch buffer

- Swap

- 4 wait states at 180 MHz (OD mode), 1 wait state at 45 MHz (MD mode)

- Memory Block Checker (MBC)

- Protect flash read, write and execute permission.

- Main array granularity is 16 KB

- IFR0 granularity is 8 KB.

- IFR1 granularity is 4 KB

- RAM

- 8 KB LPCAC to support on-chip Flash caching. 8 KB LPCAC RAM can be used as Code SRAM when LPCAC is disabled.

- 16 KB Code SRAM

- Up to 256 KB System SRAM (8 KB with ECC)

- System ROM

- Timers

- 5x 32-bit standard general-purpose asynchronous timers/counters, which support up to four capture inputs and four compare outputs, PWM mode, and external count input. Specific timer events can be selected to generate DMA requests.

- Low power timer

- Frequency measurement timer

- Windowed watchdog timer

- Wake timer

- Micro-tick timer (UTICK) running from the watchdog oscillator can be used to wake-up the device from sleep and deep-sleep modes. Includes 4 capture registers with pin inputs.

- OS event timer

- 42-bit free running OS Timer as continuous time-base for the system.

- · Advanced Motor Control

- 2x FlexPWM

- 4 sub-modules per each FlexPWM, providing 16 complementary outputs of PWM (no Nanoedge module)

- · 4 fault inputs are supported

- 2x Quadrature Decoder (eQDC)

- 2x AOI (AND/OR/Invert) module

- Implements four events output. Each event output represents a user-programmed combinational Boolean function based on four event inputs.

- $^{\circ}\,$  Four event inputs are selected from 16 input

16 / 584

- Security

- Security Monitoring

- Up to 2x Code Watchdog for code flow integrity checking

- · 6x Passive anti tamper pin detect

- GLIKEY enforces security checks before allowing a write to security-sensitive register.

- Implicit-protected Flash Region (IFR)

- 128-bit Universal Unique Identifier (UUID) per device in accordance with IETF's RFC4122 version5 specification

- Device lifecycle management

- EdgeLock Accelerator

- TRNG

- PKC (Public Key Cryptography), supports ECC and RSA encryption and decryption

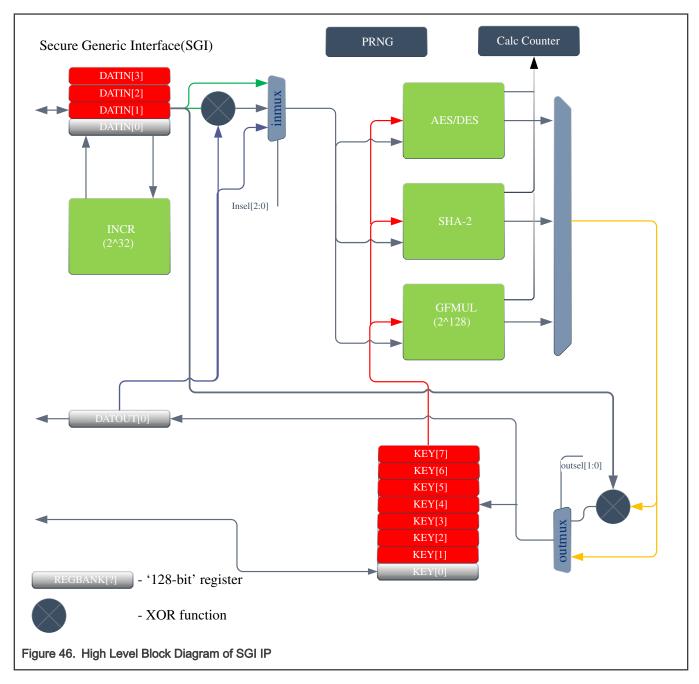

- SGI (Secure Generic Interface), provides AES256, SHA-2 and key generation/derivation

- Secure key store with key usage policies (protection of platform integrity, manufacturing and applications keys)

- · Communication Interfaces for Connectivity

- 4x LPI2C, 2x LPSPI, 5x LPUART

- 1xI3C

- USB Full-speed (Device) with on-chip FS PHY

- 1x FlexCAN with FD

- FlexIO

- Analog

- 1x 12-bit DAC

- 2x 16-bit ADC

- ∘ up to 3.2Msps in 16-bit mode, and 4Msps in 12-bit mode

- up to 43 ADC Input channels (depending on the package)

- One integrated temperature sensor per ADC

- 2x High-speed Comparators with 8 input pins and 8-bit DAC as internal reference

- 1x LPCMP is functional down to DPD mode

- 1x OpAmp without PGA

- · Operating characteristics

- Operating voltage: 1.71 to 3.6 V

- Temperature range: -40 to 125 °C

- Debug

- Minimal debug 4 breakpoint and 2 watch point, no ETM

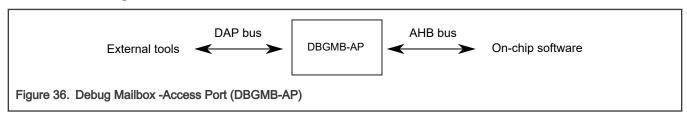

- Debug mailbox for allow tools consistency during power up

- SWD/JTAG

- Packages

- LQFP144

- LQFP100

- LQFP64

- BGA169

See the device data sheet for details on packages.

## 2.5 Functional overview

The following table shows the chip modules organized by functional category.

Table 4. Module functional categories

| Module category | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core            | <ul> <li>The Arm Cortex-M33 is a member of the Cortex-M Series of processors targeting microcontroller cores focused on cost sensitive, deterministic, and interrupt driven environments. The Cortex-M33 processor is based on the Armv8-M Architecture and ThumbR-2 ISA and is upward compatible with the Cortex-M7, M4, M3, M1, and M0/M0+.</li> <li>Math Acceleration Unit (MAU)</li> <li>Smart DMA Controller (SmartDMA)</li> </ul> |

| System          | <ul> <li>Debug Mailbox</li> <li>AHB Cross-Bar Switch (AXBS) Lite</li> <li>Enhanced Direct Memory Access (8-channel eDMA)</li> <li>Wake-Up Unit (WUU)</li> <li>Peripheral Input Mux (INPUTMUX)</li> <li>Error Injection Module (EIM)</li> <li>Error Reporting Module (ERM)</li> <li>System Power Controller (SPC)</li> <li>System Controller</li> <li>RMC (part of CMC)</li> </ul>                                                       |

| Memory          | <ul> <li>Flash Memory Controller (FMC)</li> <li>Flash Management Unit (FMU)</li> <li>ROM-BOOT and ROM-CODE</li> <li>Static Random Access Memory (SRAM)</li> <li>AHB Low Power Cache Controller (LPCAC)</li> </ul>                                                                                                                                                                                                                       |

| Clock           | <ul> <li>VBAT Wrapper</li> <li>— Free Running Oscillator - 16 K (FRO16K)</li> <li>System Clock Generator (SCG)</li> <li>— Crystal Oscillator - System (OSC_SYS)</li> <li>— Free Running Oscillator - 180 M (FRO180M)</li> </ul>                                                                                                                                                                                                         |

Table 4. Module functional categories (continued)

| Module category               | Description                                                                                        |

|-------------------------------|----------------------------------------------------------------------------------------------------|

|                               | Free Running Oscillator - 12 M (FRO12M)      PLL                                                   |

| Security                      | Cyclic Redundancy Check (CRC)     Code Watchdog                                                    |

|                               | Glikey                                                                                             |

|                               | Memory Block Checker (MBC)                                                                         |

|                               | Secure Generic Interface (SGI)                                                                     |

|                               | Public-Key Crypto Coprocessor (PKC)                                                                |

|                               | True Random Generator (TRNG)                                                                       |

|                               | Digital Tamper (TDET)                                                                              |

| Timer                         | Quadrature Decoder (ENC)                                                                           |

|                               | Micro-Tick (UTICK) Timer                                                                           |

|                               | OS Event Timer (OSTIMER)                                                                           |

|                               | Low-power Timer (LPTMR)                                                                            |

|                               | Standard Counter/Timer (CTIMER)                                                                    |

|                               | Windowed Watchdog Timer (WWDT)                                                                     |

|                               | Frequency Measurement (FREQME)                                                                     |

|                               | Wake Timer                                                                                         |

|                               | Real-time counter (RTC)                                                                            |

| Communication                 | Improved Inter-Integrated Circuit (I3C)                                                            |

|                               | Universal Serial Bus - Full Speed (USBFS) and Transceiver                                          |

|                               | USB FS Physical Layer Interface (USBFS PHY)                                                        |

|                               | Low-Power UART (LPUART)                                                                            |

|                               | Low-Power Serial Peripheral Interface (LPSPI)                                                      |

|                               | Low-Power I2C (LPI2C)                                                                              |

|                               | Flexible Data Rate CAN (FlexCAN)                                                                   |

|                               | Flexible I/O (FLEXIO)                                                                              |

| Human Machine Interface (HMI) | General Purpose Input/Output (GPIO)                                                                |

|                               | Port Control (PORT)                                                                                |

| Analog                        | 12-bit Analog-to-Digital Converter (ADC) with 4 Msps conversion<br>rate and 3.2Msps in 16-bit mode |

|                               | • 12-bit DAC                                                                                       |

Table 4. Module functional categories (continued)

| Module category | Description                         |

|-----------------|-------------------------------------|

|                 | Operational Amplifier (OpAmp)       |

|                 | Low Power analog Comparator (LPCMP) |

#### 2.5.1 Core

The following core modules are available on this chip.

Table 5. Core modules

| Module                                      | Description                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                                         | Is an Arm Cortex-M33 processor that runs at a frequency of up to 180 MHz.                                                                                                                                   |

| Nested Vectored Interrupt Controller (NVIC) | The Armv8M exception model and Nested-Vectored Interrupt Controller (NVIC) implement a relocatable vector table supporting external interrupts, a single non-maskable interrupt (NMI), and priority levels. |

| System Tick Timer (SysTick)                 | See the Armv8M Architecture Reference Manual for more information about this system timer.                                                                                                                  |

#### 2.5.2 Clock

The following clock modules are available on this chip.

Table 6. Clock sources

| Module                                      | Description                                                                                                                                                                                         |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Free Running Oscillator - 16 K (FRO16K)     | Is an ultra-low power internal 16.384 kHz clock source. It is functional down to Deep Power Down (DPD) mode. The FRO16K is trimmed to +/-6% accuracy over the entire voltage and temperature range. |

| System Clock Generator (SCG)                | Provides the user with access to the configuration control registers for the system level clock sources.  See SCG chapter in MCX A255, and A256 Reference Manual.                                   |

| Crystal Oscillator - System (OSC_SYS)       | Generates, in conjunction with an external crystal or resonator, a reference clock for the chip.                                                                                                    |

| Free Running Oscillator - 180 MHz (FRO180M) | The free running oscillator can generate 180 MHz for use by the chip.                                                                                                                               |

| Free Running Oscillator - 12 MHz (FRO12M)   | Is an internal clock source that generates a 12 MHz frequency for use by the chip.                                                                                                                  |

#### 2.5.3 Communication

The following communication modules are available on this chip.

Table 7. Communication modules

| Module                                                         | Description                                                                                                                                                                                             |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Power Inter-Integrated Circuit (LPI2C)                     | Allows communication between a number of devices. Also supports the System Management Bus (SMBus) Specification, version 2.                                                                             |

| Improved Inter-Integrated Circuit (I3C)                        | Is an extension of the I2C bus protocol supporting higher speeds.                                                                                                                                       |

| Low Power Serial Peripheral Interface (LPSPI)                  | Synchronous serial bus for communication to an external device.                                                                                                                                         |

| Low Power Universal Asynchronous Receive/<br>Transmit (LPUART) | Asynchronous serial bus communication interface with programmable 8-or 9-bit data format.                                                                                                               |

| Universal Serial Bus Full Speed Device Controller (USBFS)      | In Device mode, the USB FS subsystem working together with the SCG module can use the FIRC to generate a 48 MHz USB controller clock tuned using the incoming Host USB data for crystal-less operation. |

| Flexible Data Rate CAN (FlexCAN)                               | This module is a communication controller implementing the CAN protocol according to the ISO 11898-1:2015 standard and CAN 2.0 B protocol specifications.                                               |

| Flexible I/O (FLEXIO)                                          | Flexible I/O (FLEXIO) is a highly configurable module providing a wide range of functionality, including:                                                                                               |

|                                                                | Emulation of various serial or parallel communication protocols                                                                                                                                         |

|                                                                | Flexible 16-bit timers with support for various trigger, reset, enable, and disable conditions                                                                                                          |

|                                                                | Programmable logic blocks which allow the implementation of digital logic functions on-chip and configurable interaction of internal and external modules                                               |

|                                                                | Programmable state machine for offloading basic system control functions from the CPU                                                                                                                   |

| SmartDMA                                                       | Supports unique reduced instruction sets and performs event- and IO-driven handling to offload the work from the Arm processor.                                                                         |

## 2.5.4 Debug

The following debug modules are available on this chip.

Table 8. Debug modules

| Module                            | Description                                                                                                                                                                              |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Watchpoint and Trace (DWT)   | Is a generic name for modules that allow debug access of the Cortex-M33. The DWT comprises of the Debug Watchpoint and Trace (DWT) module and the Flash Patch and Breakpoint (FPB) unit. |

| Debug Access Port (DAP)           | Enables real-time access to the chip registers from an external debugger without halting the processor cores.                                                                            |

| Instruction Trace Macrocell (ITM) | Provides a memory-mapped register interface that applications can use to write logging or event words for profiling software.                                                            |

Table 8. Debug modules (continued)

| Module                           | Description                                                                                                                              |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Joint Test Action Group (JTAG)   | Implements serial communication protocol for communication with the Test Access Port (TAP).                                              |

| Serial Wire Debug (SWD)          | Is a serial communication interface used for debugging devices with multiple cores while only requiring a single external interface.     |

| Trace Port Interface Unit (TPIU) | Acts as a bridge between the on-chip trace data from the modules such as the ITM, which have separate system IDs, to the external world. |

## 2.5.5 Memory

The following memory modules are available on this chip.

Table 9. Memory modules

| Module                                 | Description                                                                                                                                                                            |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Memory Controller (FMC)          | Is a programmable flash memory — non-volatile flash memory that can store executable program code or data.  See <i>FMC</i> chapter in <i>MCX A255, and A256 Reference Manual</i> .     |

| Flash Management Unit (FMU)            | Manages the interface between the chip and the on-chip flash memory.  See <i>FMU</i> chapter in <i>MCX A255, and A256 Reference Manual</i> .                                           |

| Static Random Access Memory (SRAM)     | Internal system SRAM memory. Each individual block of SRAM can be configured to be retained in low-power modes.                                                                        |

| AHB Low Power Cache Controller (LPCAC) | Is a processor-local level 1 (L1) bus cache controller for use with cores using AMBA-AHB input/output buses.  See <i>LPCAC</i> chapter in <i>MCX A255, and A256 Reference Manual</i> . |

## 2.5.6 System

The following system modules are available on this chip.

Table 10. System modules

| Module                     | Description                                                                                                                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripheral Bridge(PBRIDGE) | Converts an AMBA AHB interface to a peripheral interface that allows the Peripheral Bridge (PBRIDGE) controller to interface to multiple peripherals. This device has two peripheral bridges. |

| System Controller (SYSCON) | Provides controls and configurations of the system and peripherals for the multiple functions.                                                                                                |

| Core Mode Controller (CMC) | The CMC provides control and protection on entry and exit to each power mode, control for the System Power Controller (SPC), and reset entry and exit for the complete device.                |

Table 10. System modules (continued)

| Module                                   | Description                                                                                                                                                       |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | See CMC chapter in MCX A255, and A256 Reference Manual.                                                                                                           |

| Enhanced Direct Memory Access (eDMA)     | Performs source/destination address calculations and data-<br>movement operations.                                                                                |

|                                          | Capable of performing complex data transfers with minimal intervention from a host processor.                                                                     |

|                                          | See eDMA chapter in MCX A255, and A256 Reference Manual.                                                                                                          |

| Wake-up Unit (WUU)                       | Allows selection of external pins and internal modules as interrupt wake-<br>up sources from Deep Sleep and Power Down modes.                                     |

|                                          | See WUU chapter in MCX A255, and A256 Reference Manual.                                                                                                           |

| Peripheral Input Multiplexing (INPUTMUX) | Allows the trigger output of one peripheral to be connected to the trigger input of a second peripheral.                                                          |

|                                          | See INPUTMUX chapter in MCX A255, and A256 Reference Manual.                                                                                                      |

| Error Injection Module (EIM)             | Provides a method for diagnostic coverage of internal memories (for example, system RAM, cache RAMs, and peripheral memories).                                    |

|                                          | See EIM chapter in MCX A255, and A256 Reference Manual.                                                                                                           |

| Error Reporting Module (ERM)             | Provides information and optional interrupt notification on memory error events associated with Error correction code (ECC) and parity.                           |

|                                          | See ERM chapter in MCX A255, and A256 Reference Manual.                                                                                                           |

| System Power Controller (SPC)            | Provides control over the operation and configuration of the system power generation modules to optimize power consumption for the level of functionality needed. |

|                                          | See SPC chapter in MCX A255, and A256 Reference Manual.                                                                                                           |

| Low Drop Out Regulator - Core (LDO_CORE) | A voltage regulator for generating the core voltage for the chip.                                                                                                 |

| RAM_RET_LDO                              | A voltage regulator for generating the voltage for SRAM retention.                                                                                                |

## 2.5.7 Security

The following security modules are available on this chip.

Table 11. Security modules

| Module                        | Description                                                                 |

|-------------------------------|-----------------------------------------------------------------------------|

| Cyclic Redundancy Check (CRC) | Provides error detection for all single, double, and many multi-bit errors. |

|                               | See CRC chapter in MCX A255, and A256 Reference Manual.                     |

| GLIKEY                        | It provides a mechanism to safely access security-sensitive registers.      |

Table 11. Security modules (continued)

| Module                     | Description                                                                                                                                                                                                          |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Block Checker (MBC) | Provides domain-based access control for all system bus references targeted to on-chip internal memories and slave peripherals. It's a part of TRDC module.  See MBC chapter in MCX A255, and A256 Reference Manual. |

#### 2.5.8 Timer

The following timer modules are available on this chip.

Table 12. Timer modules

| Module                          | Description                                                                                                                                          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| FlexPWM                         | Generates various switching patterns, including highly sophisticated waveforms.                                                                      |

|                                 | Controls different Switched Mode Power Supplies (SMPS) topologies.                                                                                   |

|                                 | See FlexPWM chapter in MCX A255, and A256 Reference Manual.                                                                                          |

| Wake Timer                      | Provides time keeping and calendaring functions and additionally provides protection against spurious memory/register updates and battery operation. |

|                                 | See Wake Timer chapter in MCX A255, and A256 Reference Manual.                                                                                       |

| Quadrature Decoder              | Interfaces to position/speed sensors that are used in industrial motor control applications.                                                         |

|                                 | See <i>Quadrature Decoder</i> chapter in <i>MCX A255, and A256 Reference Manual.</i>                                                                 |

| Micro-Tick (UTICK) Timer        | Is a 31-bit timer that provides a fixed time interval between interrupts.                                                                            |

|                                 | See UTICK chapter in MCX A255, and A256 Reference Manual.                                                                                            |

| OS Event Timer (OSTIMER)        | Is a 42-bit Gray code counter.                                                                                                                       |

|                                 | See OSTIMER chapter in MCX A255, and A256 Reference Manual.                                                                                          |

| Low-power Timer (LPTMR)         | Is a 16-bit timer or pulse counter with compare feature.                                                                                             |

|                                 | See LPTMR chapter in MCX A255, and A256 Reference Manual.                                                                                            |

| Standard Counter/Timer (CTimer) | Each Counter/timer is designed to count cycles of the CTIMER function clock.                                                                         |

|                                 | See CTimer chapter in MCX A255, and A256 Reference Manual.                                                                                           |

| Windowed Watchdog Timer (WWDT)  | Helps reset or interrupt an erroneous microcontroller within a programmable time.                                                                    |

|                                 | See WWDT chapter in MCX A255, and A256 Reference Manual.                                                                                             |

Table 12. Timer modules (continued)

| Module                | Description                                                                                                                                                                     |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency Measurement | Provides high-accuracy frequency measurement function for on-chip and off-chip clocks.  See <i>Frequency Measurement</i> chapter in <i>MCX A255, and A256 Reference Manual.</i> |

## 2.5.9 Human Machine Interface (HMI)

The following HMI modules are available on this chip.

Table 13. HMI modules

| Module                              | Description                                                                                                                         |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose Input/Output (GPIO) | All GPIO pins support interrupt and DMA request generation.  See <i>GPIO</i> chapter in <i>MCX A255, and A256 Reference Manual.</i> |

| Port Control (PORT)                 | Provides support for pad control functions.  See PORT chapter in MCX A255, and A256 Reference Manual.                               |

## 2.5.10 Analog

The following analog modules are available on this chip.

Table 14. Analog modules

| Module                            | Description                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-Digital Converter (ADC) | Successive approximation ADC designed for operation within an integrated microcontroller system-on-chip.  See ADC chapter in MCX A255, and A256 Reference Manual.                                                                                                                                                    |

| Low Power Comparator (LPCMP)      | Provides a circuit for comparing two analog input voltages.  See <i>LPCMP</i> chapter in <i>MCX A255, and A256 Reference Manual.</i>                                                                                                                                                                                 |

| LPDAC                             | The Low Power Digital-to-Analog Converter(LPDAC) is a low power, 12-bit general-purpose digital-to-analog converter. The output of the LPDAC can be placed on an external pin or set as one of the inputs to the analog comparator or ADC.  See <i>LPDAC</i> chapter in <i>MCX A255, and A256 Reference Manual</i> . |

| Operational Amplifier (OpAmp)     | The OpAmp is a pure voltage amplifier without any built-in programmable gain stage.                                                                                                                                                                                                                                  |

|                                   | User needs to implement external feedback network to achieve specific inverting or non-inverting gain amplification.                                                                                                                                                                                                 |

|                                   | This module is applicable to the signal processing stage before SARADC.                                                                                                                                                                                                                                              |

## Chapter 3 Core Overview

#### 3.1 Introduction

This section covers the core modules included in this chip.

#### 3.2 Cortex-M33 Code and System buses

This device has one Arm Cortex-M33 processor core, with Floating Point Unit (FPU), Memory Protection Unit (MPU) and without TrustZone-M.

The core implements a modified Harvard memory architecture using two 32-bit bus interfaces: the Code and System buses. The bus interfaces are activated by address range and can include both instruction fetches and operand data references on a given bus port. (A traditional Harvard architecture strictly separates instruction fetches and operand data references onto specific bus ports regardless of access address.) The Code bus is typically used for instruction fetching and data accesses of PC-relative data, while the system bus is typically used for operand data references to the on- and off-chip memories and peripheral accesses. The bus structure fully supports concurrent instruction fetch and data accesses, but the Cortex-M33 implementations can generate both types of references on each bus.

NOTE

It is recommended that performance critical code be located such that it fetches from the Code bus interface as defined by addresses < 0x2000\_0000.

#### 3.2.1 Code Bus access

Code Bus accesses are routed to the Code Cache Controller; code bus of the core goes to LPCAC. This controller then processes the cacheable accesses as needed, while bypassing the non-cacheable accesses or forwarding the cache write-through and cache miss accesses to the downstream memories through the master port of this cache controller.

#### 3.2.2 System bus access

All System bus accesses are routed to the target address in destination memories through multilayer AHB matrix slave port.

#### 3.2.3 Access control

All core Code and System Bus accesses are checked by the core access control logic. All requests that miss or bypass the cache are checked by downstream secure AHB bus logic. The caches include protection control signals (HPROT[3:0]) and processing domain bits as part of the tags. If a fetch address hits the cache but the protection control and/or domain bits are different, the cache controller forces a miss with the allocate location the same as the address hit location in the cache. This policy allows all the downstream checks to take place, and this new miss is loaded in the cache with the updated protection control and domain bits overwriting the line with the same address. This keeps the cache coherent while always checking accesses that need to see the downstream checks.

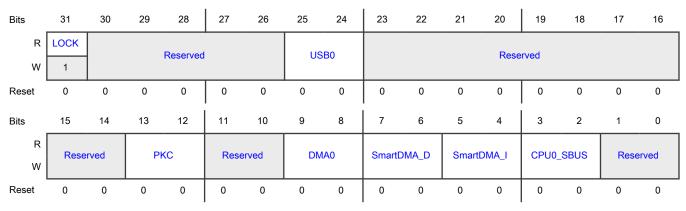

#### 3.3 Nested Vectored Interrupt Controller (NVIC)

#### 3.3.1 Interrupt priority levels

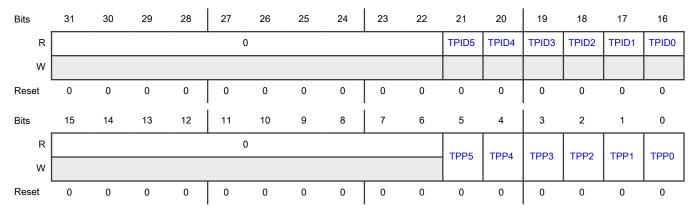

This device supports 8 priority levels for interrupts. Therefore, in the NVIC each source in the IPR registers contains 3 bits. For example, IPR0 is shown below:

Reference Manual 25 / 584

|   | 31 | 30   | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22   | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----|------|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|------|----|----|----|----|---|---|---|------|---|---|---|---|---|---|

| R | Γ, | RQ3  |    | 0  | 0  | 0  | 0  | 0  |    | RQ2  |    | 0  | 0  | 0  | 0  | 0  |    | RQ1  |    | 0  | 0  | 0  | 0 | 0 |   | RQ0  |   | 0 | 0 | 0 | 0 | 0 |

| W |    | ivas |    |    |    |    |    |    |    | INQZ |    |    |    |    |    |    | '  | IVQI |    |    |    |    |   |   |   | INQU |   |   |   |   |   |   |

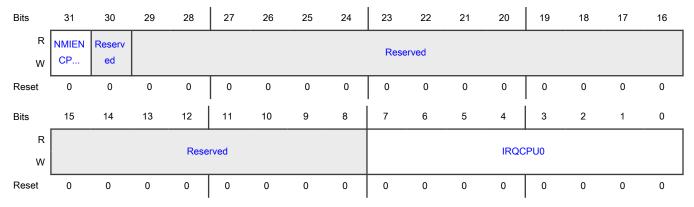

#### 3.3.2 Non-Maskable Interrupt (NMI) configuration

The Non-Maskable Interrupt (NMI) enable bit and source selection bits are implemented for each core in SYSCON register.

#### 3.3.3 Interrupt channel assignments

The interrupt source assignments are defined in the following table.

- · Vector number the value stored on the stack when an interrupt is serviced.

- IRQ number non-core interrupt source count, which is the vector number minus 16.

The IRQ number is used within Arm's NVIC documentation.

See the attached NVIC\_Configuration spreadsheet for the NVIC interrupt assignments.

#### 3.4 System memory map

See the attached Memory Map spreadsheet (Overview tab) for the chip's high-level memory map.

#### 3.5 Peripheral Bridge

The Peripheral Bridge (PBRG) is the portion of the bus fabric that connects the peripherals to the processor elements. Each peripheral has a base address where the processor elements can access them.

#### 3.5.1 Peripheral Bridge (PBRIDGE0-1) memory maps

See the attached Memory Map spreadsheet for PBRIDGE0, PBRIDGE1, and Fast Peripherals (Peripheral Memory Map tab) peripheral memory mapping on this device.

Reference Manual 26 / 584

## Chapter 4 Security Overview

#### 4.1 Non-claims

As system security requirements and the attack surface evolves, it is important for customers to understand the types of attacks (especially advanced physical attacks) which NXP does not claim to protect against, or strongly mitigate, so that appropriate mitigation can be taken by the customer at the system level if necessary.

- This SoC has built-in security event detection features. However, NXP does not guarantee against advanced tamper

attempts, including operation of the device beyond the defined specification limits. The security event detection features

are only effective if the analog glitch detector is enabled in the device configuration. NXP does not guarantee the

protection against semi-invasive and invasive attacks.

- This SoC has a built-in feature addressing side channel attacks. However, there is no claim to be completely resistant.

The effectiveness of these features has not been independently evaluated. Therefore NXP does not guarantee that the result will meet specific customer requirements.

- Several aspects of this SoC's security trust architecture rely on the strength of cryptographic algorithms and digital signatures. If these are subsequently determined to have inherent flaws, then the impact for each flaw must be evaluated and, in this case, NXP does not guarantee the underlying trust architecture claims.

NXP recommends customers to implement appropriate design and operating safeguards based on defined threat models, to minimize the security risks associated with their applications and products.

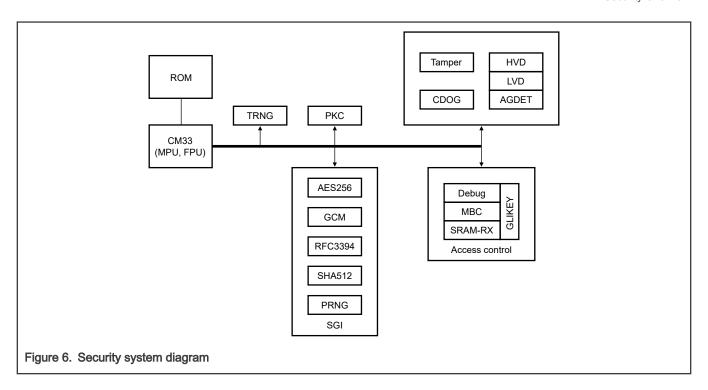

#### 4.2 Overview

This chapter provides an overview of the security features that this chip device implements using the following onchip components.

- · Secure Generic Interface (SGI) that supports secure computation of AES and SHA algorithms.

- Public-Key Cryptography Accelerator (PKC)

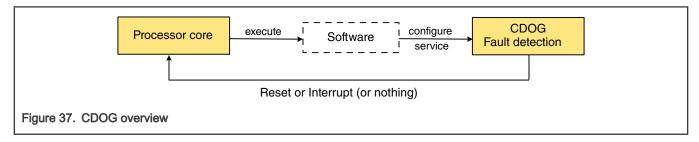

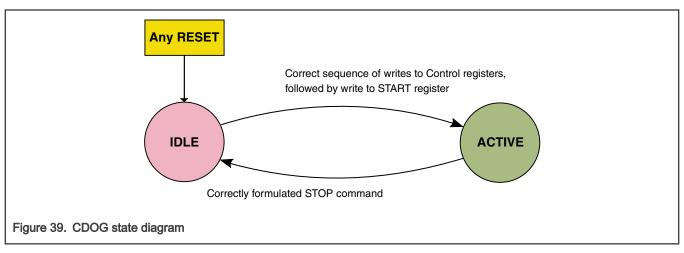

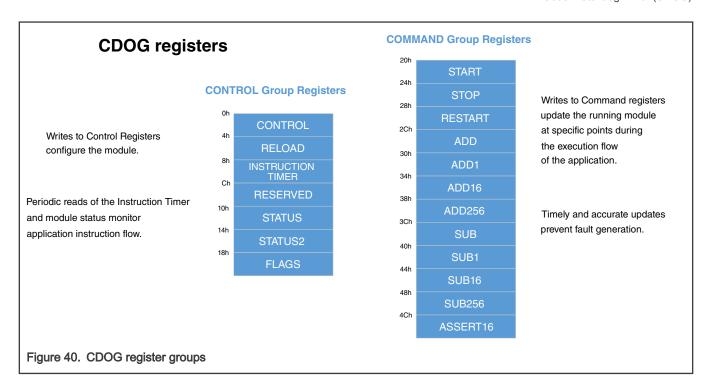

- · Code Watchdog (CDOG) to ensure software integrity by detecting unexpected changes in the code execution flow.

- Memory Block Checker (MBC) that provides read, write, and execute access control per block of internal flash memory. See

the MBC chapter in MCXA 255, and A256 Reference Manual for information about MBC.

- Digital Tamper (TDET) to support tamper detection.

- Cyclic Redundancy Check (CRC) that provides error detection for multi-bit errors. See the CRC chapter in MCXA 255, and A256 Reference Manual for information about CRC.

- GLIKEY to ensure safe access to security-sensitive registers.

- · True Random Number Generator (TRNG)

- · Analog Glitch Detector (AGDET)

The following figure shows the security system diagram of this device.

Reference Manual 27 / 584

#### 4.3 Security features

#### 4.3.1 Immutable Root of Trust

As defined by Trusted Computing Group, "an Immutable Root of Trust (RoT) is expected to remain identical across all devices within a set of device models based on a defined threat model. It is also expected not to change across time and, therefore, will behave the same during each device's lifespan." It consists of truly immutable hardware logic, including analog and digital logic, read-only memory and one-time programmable memory. Immutable RoT is essential for guaranteeing any security feature, including Life-cycle Management, and a number of others. In this device, Immutable RoT is embedded in the Boot ROM and subsequently in an immutable bootloader.

#### 4.3.2 Life cycle management

During its lifespan, a typical device finds itself in various places around the world. It is manufactured in a semiconductor factory, tested and packaged in silicon manufacturer facilities, sold to various distributors, sold further to the Original Equipment Manufacturer (OEM), assembled, tested and provisioned by their Contract Manufacturers and, finally, delivered to the end-customer. In the case of failure, a device is returned to OEM or even back to the silicon manufacturer for further failure analysis.

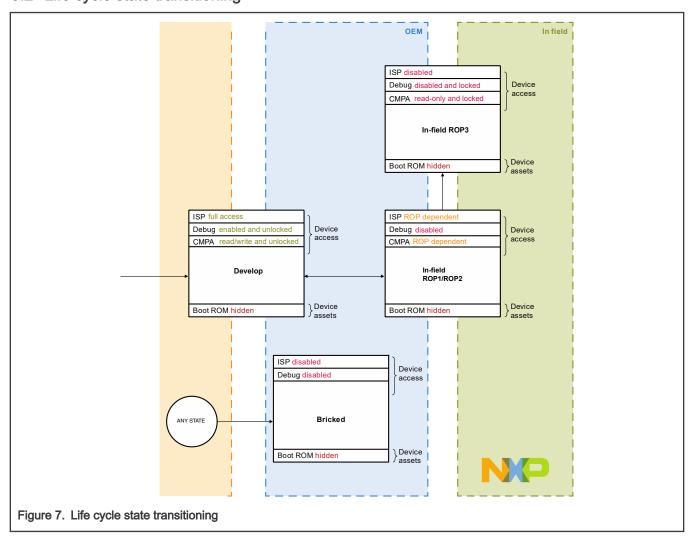

Device life-cycle state is used to reflect the actual state of the device, which is further used to instruct the device on how exactly to protect the assets a device hosts during specific time. For example, when a device is being tested at a silicon manufacturer facility and no OEM or end-customer assets have been provisioned on it, then access to the device, in terms of debug or test, is less restrictive than when a device is with the end-customer.

Life-cycle state is monotonic, meaning it can only always be increased. Immutable RoT is in charge of life-cycle management and it enforces device access policies accordingly. See Life Cycle States for details.

#### 4.3.3 Secure key management

Secure key management is a process of securing valuable keys and various key material which are essential in maintaining security of the end-user, OEM and NXP assets. The process strongly relies on the Immutable RoT and hardware logic. A device-unique master key (DUK) is provided by the Immutable RoT and loaded into write-only key slots 6 and 7 of the Secure Generic Interface (SGI). The DUK can be freely used for AES encryption/decryption of sensitive data, key wrapping/unwrapping

or derivation of further key material. When using the RFC3394 key unwrap feature of the SGI, the unwrapped key will be stored in write-only key slots 4 and 5.

NOTE

SGI key registers are not sticky-lockable and can be used freely, so key isolation is not a feature on this device.

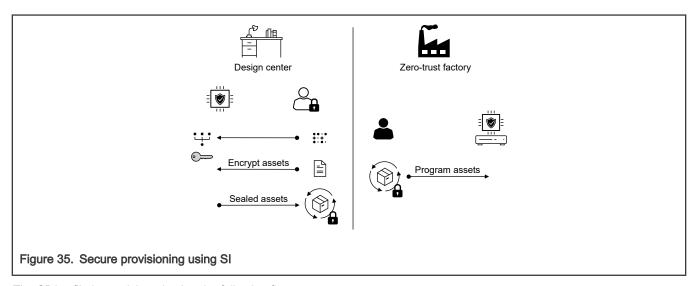

#### 4.3.4 Secure installer

To support cases where outsourcing of device software provisioning to an untrusted Contract Manufacturer is desired, this SoC comes with a pre-installed secure installer firmware which can be accessed through In-System Programming (ISP) mode in the default life cycle state. NXP software tools enable the Original Equipment Manufacturer (OEM) to build an encrypted file containing a sequence of provisioning commands. This encrypted file can be transferred to Contract Manufacturers and securely installed on the devices. The devices are able to decrypt the contents directly into persistent memory and advance the life cycle state so that the Contract Manufacturer is unable to inspect the provisioned code and data. SeeSecure Installer for more details.

**NOTE**In order to protect against several attacks, it is recommended that an OEM advances the life cycle state as soon as possible in their encrypted image.

#### 4.3.5 Anomaly Detection and Reaction

Anomaly Detection and Reaction describes the processes or algorithms that analyze the device input and output such as sensor data, as well as the software integrity and application operation for abnormal events and, if required, trigger and execute an action. Typically these actions encompass logging the anomaly, issuing a message to the cloud backend, resetting the device, and/or changing a life cycle state.

Reference Manual 29 / 584

## Chapter 5 Life Cycle States

#### 5.1 Overview

This device supports a life cycle state model to protect code from reading from the device internal flash, which is called code read-out protection (ROP) feature. There are different levels of protections in the system, so that access to the on-chip flash and use of ISP can be restricted. Also the life cycle state of the device determines the debug access and ISP command availability. Please see other sections details. The life cycle state is controlled by ROP\_STATE (in the CMPA region).

The Boot ROM will check the life cycle state and then determine what Boot flow to run, and debug port to be enabled/locked and available debug mail access command sets. After ROM exits to extended bootloader, life cycle will be checked again to determine available ISP command sets.