# MC68SC302

Passive ISDN

Protocol Engine

User's Manual

Home Page:

www.freescale.com

email:

support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French)

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

support@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

# **PREFACE**

The complete documentation package for the MC68SC302 consists of the MC68SC302 Passive ISDN Protocol Engine User's Manual, and the MC68SC302/D, MC68SC302 Passive ISDN Protocol Engine Product Brief.

The MC68SC302 Passive ISDN Protocol Engine User's Manual describes the programming, capabilities, registers, and operation of the MC68SC302; and the MC68SC302 Passive ISDN Protocol Engine Product Brief provides a brief description of the MC68SC302 capabilities.

This user's manual is organized as follows:

| Section 1 | Introduction                             |

|-----------|------------------------------------------|

| Section 2 | Signal Description                       |

| Section 3 | Interrupts and Timer                     |

| Section 4 | Communications Processor (CP)            |

| Section 5 | ISA Plug And Play Interface              |

| Section 6 | PCMCIA Interface                         |

| Section 7 | Electrical Characteristics               |

| Section 8 | Mechanical Data And Ordering Information |

# **ELECTRONIC SUPPORT:**

Internet access is provided through the World Wide Web at http://www.mot.com/netcomm.

# - Sales Offices -

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

### **UNITED STATES**

| ALABAMA, Huntsville ARIZONA, Tempe CALIFORNIA, Agoura Hills CALIFORNIA, Los Angeles CALIFORNIA, Irvine CALIFORNIA, RosevIlle CALIFORNIA, San Diego CALIFORNIA, Sunnyvale COLORADO, Colorado Springs COLORADO, Denver CONNECTICUT, Wallingford FLORIDA, Maitland FLORIDA, Pompano Beach/ Fort Lauderdal FLORIDA, Clearwater GEORGIA, Atlanta IDAHO, Boise ILLINOIS, Chicago/Hoffman Estates INDIANA, Fort Wayne INDIANA, Indianapolis INDIANA, Kokomo IOWA, Cedar Rapids KANSAS, Kansas City/Mission MARYLAND, Columbia | (305) 486-9776<br>(813) 538-7750<br>(404) 729-7100<br>(208) 323-9413<br>(708) 490-9500<br>(219) 436-5818<br>(317) 571-0400<br>(317) 457-6634 | MASSACHUSETTS, Marborough MASSACHUSETTS, Woburn MICHIGAN, Detroit MINNESOTA, Minnetonka MISSOURI, St. Louis NEW JERSEY, Fairfield NEW YORK, Fairport NEW YORK, Fairport NEW YORK, Poughkeepsie/Fishkill NORTH CAROLINA, Raleigh OHIO, Cleveland OHIO, Columbus Worthington OHIO, Dayton OKLAHOMA, Tulsa OREGON, Portland PENNSYLVANIA, Colmar Philadelphia/Horsham TENNESSEE, Knoxville TEXAS, Austin TEXAS, Houston TEXAS, Plano VIRGINIA, Richmond WASHINGTON, Bellevue Seattle Access WISCONSIN, Milwaukee/Brookfield | (215) 957-1020<br>(215) 957-4100<br>(615) 690-5593<br>(512) 873-2000<br>(800) 343-2692<br>(214) 516-5100<br>(804) 285-2100<br>(206) 454-4160<br>(206) 622-9960 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CANADA BRITISH COLUMBIA, Vancouver ONTARIO, Toronto ONTARIO, Ottawa QUEBEC, Montreal                                                                                                                                                                                                                                                                                                                                                                                                                                   | (604) 293-7605<br>(416) 497-8181<br>(613) 226-3491<br>(514) 731-6881                                                                         | MALAYSIA, Penang MEXICO, Mexico City MEXICO, Guadalajara Marketing Customer Service NETHERLANDS, Best PUERTO RICO, San Juan SINGAPORE SPAIN, Madrid or                                                                                                                                                                                                                                                                                                                                                                   | 60(4)374514<br>52(5)282-2864<br>52(36)21-8977<br>52(36)21-9023<br>52(36)669-9160<br>(31)40088-612-14                                                           |

| INTERNATIONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              | NETHERLANDS, Best                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (31)49988 612 11                                                                                                                                               |

| INTERNATIONAL AUSTRALIA, Melbourne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (61-3)887-0711                                                                                                                               | SINGAPORF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (65)2945438                                                                                                                                                    |

| AUSTRALIA, Sydney                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (61(2)906-3855                                                                                                                               | SPAIN, Madrid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34(1)457-8204                                                                                                                                                  |

| BRAZIL, Sao Paulo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55(11)815-4200                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34(1)457-8254                                                                                                                                                  |

| CHINA, Beijing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86 505-2180                                                                                                                                  | SWEDEN, Solna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46(8)734-8800                                                                                                                                                  |

| FINLAND, Helsinki<br>Car Phone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 358-0-35161191                                                                                                                               | SWITZERLAND, Geneva                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41(22)7991111<br>41(1)730 4074                                                                                                                                 |

| FRANCE, Paris/Vanves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 358(49)211501<br>33(1)40 955 900                                                                                                             | SWITZERLAND, Geneva<br>SWITZERLAND, Zurich<br>TAIWAN, Taipei<br>THAILAND, Bangkok<br>UNITED KINGDOM, Aylesbury                                                                                                                                                                                                                                                                                                                                                                                                           | 886(2)717-7089                                                                                                                                                 |

| GERMANY, Langenhagen/ Hanover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49(511)789911                                                                                                                                | THAILAND, Bangkok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (66-2)254-4910                                                                                                                                                 |

| CEDMANY Munich                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40 90 02402 O                                                                                                                                | UNITED KINGDOM, Aylesbury                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44(296)395-252                                                                                                                                                 |

| GERMANY, Nuremberg GERMANY, Sindelfingen GERMANY, Wiesbaden HONG KONG, Kwai Fong                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49 911 64-3044                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |

| GERMANY Wieshaden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49 7031 69 910<br>49 611 761921                                                                                                              | FULL LINE REPRESENT COLORADO, Grand Junction                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ATIVES                                                                                                                                                         |

| HONG KONG. Kwai Fong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 852-4808333                                                                                                                                  | Cheryl Lee Whitely                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (303) 243-9658                                                                                                                                                 |

| Tai Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 002-000000                                                                                                                                   | KANSAS, Wichita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |

| INDIA, Bangalore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (91-812)627094                                                                                                                               | Melinda Shores/Kelly Greiving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (316) 838 0190                                                                                                                                                 |

| ISRAEL, Tel Aviv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 972(3)753-8222                                                                                                                               | NEVADA, Reno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (702) 746 0642                                                                                                                                                 |

| ITALY, Milan<br>JAPAN, Aizu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39(2)82201<br>81(241)272231                                                                                                                  | Galena Technology Group  NEW MEXICO, Albuquerque                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (102) 140 0042                                                                                                                                                 |

| JAPAN, Atsugi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81(0462)23-0761                                                                                                                              | S&S Technologies, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (505) 298-7177                                                                                                                                                 |

| JAPAN, Kumagaya                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81(0485)26-2600                                                                                                                              | UTAH, Salt Lake City                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ()                                                                                                                                                             |

| JAPAN, Kyushu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81(092)771-4212                                                                                                                              | Utah Component Sales, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (801) 561-5099                                                                                                                                                 |

| JAPAN, Mito                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81(0292)26-2340                                                                                                                              | WASHINGTON, Spokane Doug Kenley                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (509) 924-2322                                                                                                                                                 |

| JAPAN, Nagoya<br>JAPAN, Osaka                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81(052)232-1621<br>81(06)305-1801                                                                                                            | ARGENTINA, Buenos Aires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (000) 324-2022                                                                                                                                                 |

| JAPAN, Sendai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81(22)268-4333                                                                                                                               | Argonics, S.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (541) 343-1787                                                                                                                                                 |

| JAPAN, Tachikawa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81(0425)23-6700                                                                                                                              | HVDDID COMPONENTS ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OF 1 FD0                                                                                                                                                       |

| JAPAN, Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81(03)3440-3311                                                                                                                              | HYBRID COMPONENTS RE Elmo Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (818) 768-7400                                                                                                                                                 |

| JAPAN, Yokohama<br>KOREA, Pusan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81(045)472-2751<br>82(51)4635-035                                                                                                            | Minco Technology Labs Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (512) 834-2022                                                                                                                                                 |

| KOREA, Fusaii<br>KOREA, Seoul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82(2)554-5188                                                                                                                                | Semi Dice Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (310) 594-4631                                                                                                                                                 |

| NOREA, Secul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02(2)334-3100                                                                                                                                | Gerri Dice iric.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (010) 007 7001                                                                                                                                                 |

# **TABLE OF CONTENTS**

| Paragraph<br>Number | Title                                    | Page<br>Number |

|---------------------|------------------------------------------|----------------|

|                     | PREFACE                                  |                |

|                     | ELECTRONIC SUPPORT:                      | iii            |

|                     | — Sales Offices —                        | iii            |

|                     | Section 1 MC68SC302 Overview             |                |

| 1.1                 | MC68SC302 Key Features                   | 1 1            |

| 1.1                 | MC68SC302 Overview                       |                |

| 1.3                 | Reference Designs                        |                |

| 1.4                 | MC68SC302 Application Development System |                |

| 1.5                 | ADS Features                             |                |

|                     | Section 2                                |                |

|                     | Signal Description and Pin Control       |                |

| 2.1                 | Host Interface Pins – ISA Mode           | 2-3            |

| 2.1.1               | Address Bus Pins                         |                |

| 2.1.1.1             | Latched Address Bus Pins (LA23—LA17)     |                |

| 2.1.1.2             | Static Address Bus Pins (SA16—SA0)       |                |

| 2.1.2               | Data Bus Pins (SD15—SD0)                 |                |

| 2.1.2.1             | Low Data Bus Pins (SD7–SD0)              |                |

| 2.1.2.2             | High Data Bus Pins (SD15—SD8)            |                |

| 2.1.3               | Bus Control Pins                         |                |

| 2.1.3.1             | AEN—Address Enable pin                   |                |

| 2.1.3.2             | BALE—Bus Address Latch Enable            |                |

| 2.1.3.3             | SBHE—System Bus High Enable              | 2-4            |

| 2.1.3.4             | MEMR—Memory Read                         |                |

| 2.1.3.5             | MEMW—Memory Write                        | 2-5            |

| 2.1.3.6             | IOR—I/O Read                             | 2-5            |

| 2.1.3.7             | IOW/PC_Mode—I/O Write and PC_Mode        | 2-5            |

| 2.1.3.8             | MEMCS16—Memory Cycle Select is 16 Bit    | 2-5            |

| 2.1.3.9             | IOCS16—I/O Cycle Select is 16 Bi         | 2-5            |

| 2.1.3.10            | IOCHRDY—I/O Channel Ready                | 2-5            |

| 2.1.3.11            | REF—Refresh                              | 2-5            |

| 2.1.3.12            | RESET — Reset                            | 2-5            |

| 2.1.4               | Interrupt Out Pins                       |                |

| 2.1.4.1             | IRQ9, 10, 11, 12, 15 — Dedicated mode    |                |

| 2.1.4.2             | IRQO, IRQSEL3-IRQSEL0 — Encoded Mode     | 2-6            |

| 2.1.5               | Clock Pins                               | 2-6            |

| Paragraph<br>Number | Title                                                           | Page<br>Numbe |

|---------------------|-----------------------------------------------------------------|---------------|

| 2.1.5.1             | EXTAL—External Clock/Crystal Input                              | 2-6           |

| 2.1.5.2             | XTAL— Crystal Output                                            | 2-6           |

| 2.1.5.3             | CLKO— Clock Out                                                 | 2-7           |

| 2.2                 | Host Interface Pins - PCMCIA Mode                               | 2-7           |

| 2.2.1               | Address Bus Pins                                                |               |

| 2.2.1.1             | PC_A[21:17]/IRQIN[5:1]/PA[15:12]—PCMCIA Address Bus             | 2-8           |

| 2.2.1.2             | Address Bus Pins. PC_A[16:0]-PCMCIA Address Bus                 |               |

| 2.2.2               | Data Bus Pins                                                   | 2-8           |

| 2.2.2.1             | PC_D[15:0]—PCMCIA Data Bus                                      | 2-8           |

| 2.2.3               | Bus Control Pins                                                |               |

| 2.2.3.1             | PC_MODE—PCMCIA Mode                                             |               |

| 2.2.3.2             | PC_E2E—PCMCIA Serial EEPROM mode                                |               |

| 2.2.3.3             | PC_CE1 and PC_CE2— PCMCIA Card Enables 1 and 2                  |               |

| 2.2.3.4             | PC_OE—PCMCIA Output Enable                                      |               |

| 2.2.3.5             | PC_WE—PCMCIA Write Enable                                       |               |

| 2.2.3.6             | PC_A25—PCMCIA Address Bus bit 25                                |               |

| 2.2.3.7             | PC_CISCS—PCMCIA CIS Chip Select                                 |               |

| 2.2.3.8             | PC_STSCHG—PCMCIA Status Changed (Replace BVD1)                  |               |

| 2.2.3.9             | PC_WAIT—PCMCIA Wait                                             |               |

| 2.2.3.10            | PC_REG—PCMCIA Attribute Memory Select                           |               |

| 2.2.3.11            | RESET— Hard System Reset Input                                  |               |

| 2.2.3.11            | IRQ3/PC_READY/IREQ— Ready or Interrupt Request Out Pin          |               |

| 2.2.4               | Clock Pins                                                      |               |

| 2.2.4.1             | EXTAL—External Clock/Crystal Input                              |               |

| 2.2.4.1             | XTAL—Crystal Output                                             |               |

| 2.2.4.2             | CLKO— Clock Out                                                 |               |

| 2.2.4.3             | Peripheral Pins                                                 |               |

| 2.3.1               | •                                                               |               |

| 2.3.1.1             | ISDN Pins                                                       |               |

| _                   | L1RXD—Layer-1 Receive Data                                      |               |

| 2.3.1.2             | L1TXD—Layer-1 Transmit Data                                     |               |

| 2.3.1.3             | L1CLK—Layer-1 Clock                                             |               |

| 2.3.1.4             | L1SYNC—Layer-1 Sync                                             |               |

| 2.3.1.5             | L1GRNT / PSYNC —Layer-1 Grant / PCM SYNC                        |               |

| 2.3.1.6             | L1RQ / GCIDCL—Layer-1 Request / GCI Clock Out                   |               |

| 2.3.2               | NMSI Pins                                                       |               |

| 2.3.2.1             | RXD—SCC Receive Data Pin                                        |               |

| 2.3.2.2             | TXD—SCC Transmit Data Pin                                       |               |

| 2.3.2.3             | TCLK / MCLK —SCC Transmit Clock Pin / Codec Main Clock          |               |

| 2.3.2.4             | RCLK / SCLK / IRQIN1 —SCC2 Receive Clock / Codec Serial Cloc    |               |

|                     | Interrupt Request In 1 Pin                                      |               |

| 2.3.2.5             | SDS1 / FSYN / IRQIN2—Serial Data Strobe 1 / Codec Frame Sync    | :/            |

|                     | Interrupt Request In 2 Pin                                      |               |

| 2.3.2.6             | SDS2 / IRQIN3—Serial Data Strobe 2 / Interrupt Request In 3 Pin |               |

| 2.3.2.7             | NMSICS—NMSI Chip Select Pin                                     |               |

| 2328                | RI / IROIN4—Ring Indicate / Interrupt Request In 4 Pin          | 2-12          |

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 2.3.3               | SCP Pins                                          | 2-12           |

| 2.3.3.1             | SPRXD—SCP Receive Serial Data Pin                 | 2-12           |

| 2.3.3.2             | SPTXD—SCP Transmit Serial Data Pin                | 2-12           |

| 2.3.3.3             | SPCLK—SCP Clock Pin                               | 2-12           |

| 2.3.3.4             | E2EN—EEPROM Enable Pin                            |                |

| 2.3.3.5             | SCPEN1-3 —SCP Slave Enable 1-3 Pins               |                |

| 2.3.4               | Multi-Function I/O Pins                           |                |

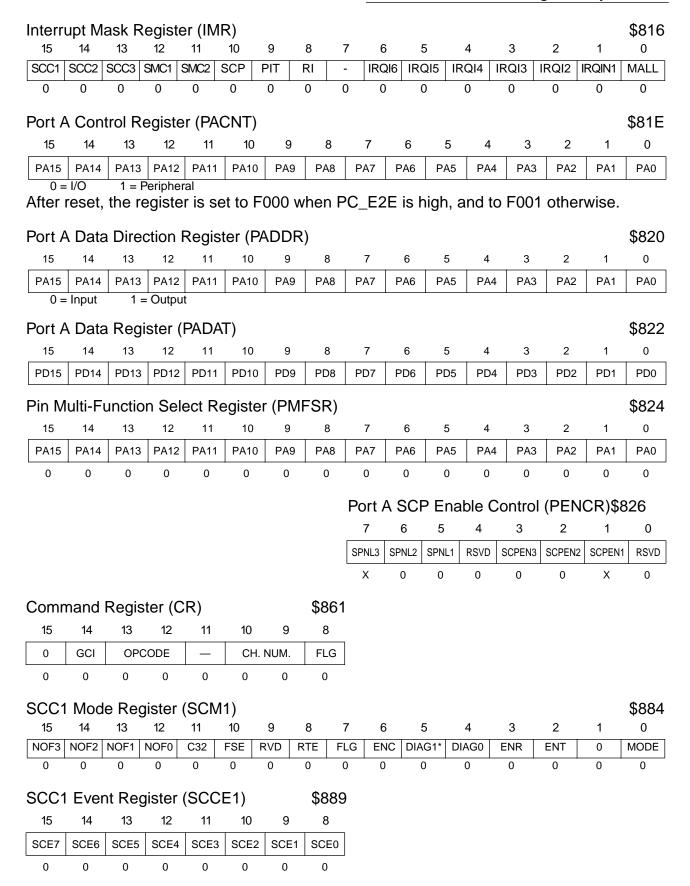

| 2.3.4.1             | PORT A                                            |                |

| 2.3.4.2             | Port A Registers                                  |                |

| 2.3.4.3             | Port A SCP Enable Control                         |                |

| 2.3.4.4             | Multi-Function Pins                               |                |

| 2.3.4.5             | Pin Multi-Function Select Register (PMFSR)        |                |

| 2.3.4.6             | Special Pin Function in 8-Bit Mode                | 2-16           |

|                     | Section 3                                         |                |

| 3.1                 | Interrupt, Timer, and Power Control               | 2.1            |

| 3.1.1               | Interrupt ControllerInterrupt Controller Overview |                |

| 3.1.2               | Masking Interrupt Sources and Events              |                |

| 3.1.3               | Interrupt Handling Procedure                      |                |

| 3.1.4               | Wake Up On Interrupt                              |                |

| 3.1.5               | Global Interrupt Mode Register (GIMR)             |                |

| 3.1.6               | Interrupt Pending Register (IPR)                  |                |

| 3.1.7               | Interrupt Mask Register (IMR)                     |                |

| 3.1.8               | Periodic Interrupt Timer                          |                |

| 3.1.8.1             | Overview                                          |                |

| 3.1.8.2             | Periodic Timer Period Calculation                 |                |

| 3.1.8.3             | Periodic Interrupt Timer Register (PITR)          |                |

| 3.2                 | ISA Power Control Registers                       |                |

|                     | ŭ                                                 |                |

|                     | Section 4 Communications Processor (CP)           |                |

| 4.1                 | Main Controller                                   | 4-1            |

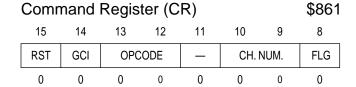

| 4.2                 | Command Set                                       | 4-2            |

| 4.2.1               | Command Execution Latency                         | 4-4            |

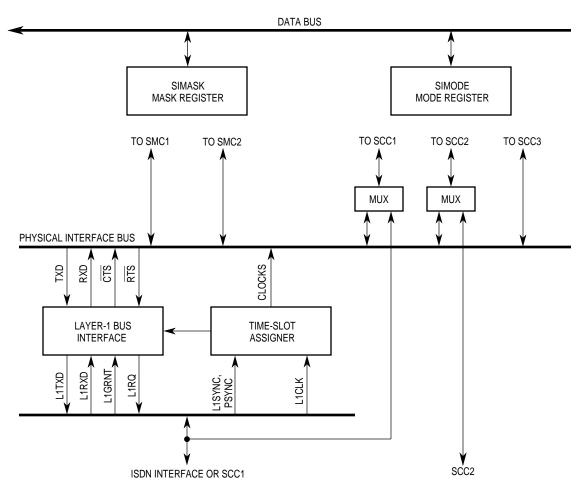

| 4.3                 | Serial Channels Physical Interface                | 4-4            |

| 4.3.1               | IDL Interface                                     | 4-5            |

| 4.3.2               | GCI Interface                                     | 4-7            |

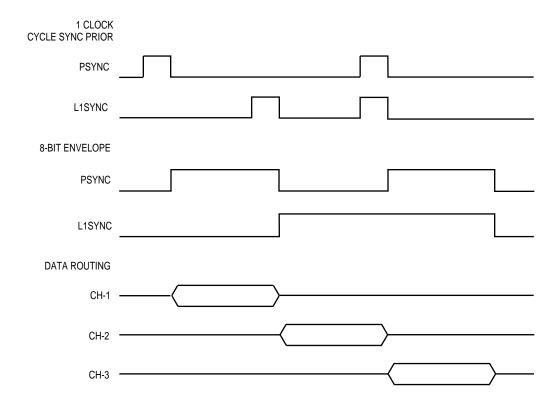

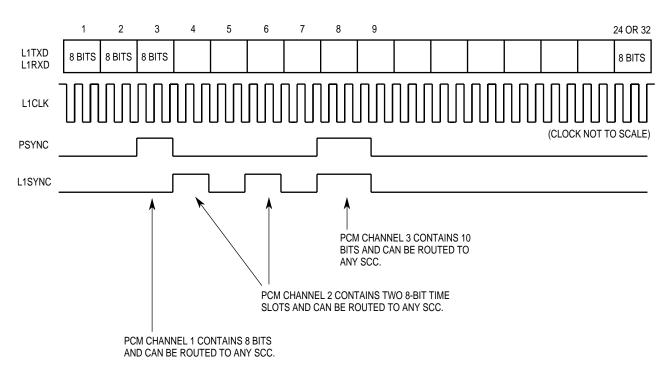

| 4.3.3               | PCM Highway Mode                                  | 4-9            |

| 4.3.4               | Nonmultiplexed Serial Interface (NMSI)            | 4-12           |

| 4.4                 | Serial Interface Registers                        |                |

| 4.4.1               | Serial Interface Mode Register (SIMODE)           | 4-12           |

| 4.4.2               | Serial Interface Mask Register (SIMASK)           |                |

| 4.5                 | Serial Communication Controllers (SCC)            | 4-15           |

| 4.5.1               | SCC Features                                      |                |

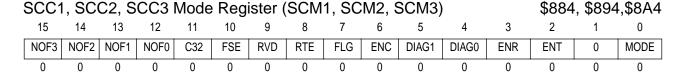

| 4.5.2               | SCC Mode Register (SCM)                           | 4-16           |

|                     |                                                   |                |

| Paragraph<br>Number | Title                                                         | Page<br>Number |

|---------------------|---------------------------------------------------------------|----------------|

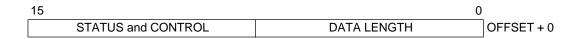

| 4.5.3               | SCC Transmit Buffer Descriptors                               |                |

| 4.5.4               | SCC Transmit Buffer DescriptorsSCC Receive Buffer Descriptors |                |

| 4.5.4               | SCC Receive Bullet Descriptors                                |                |

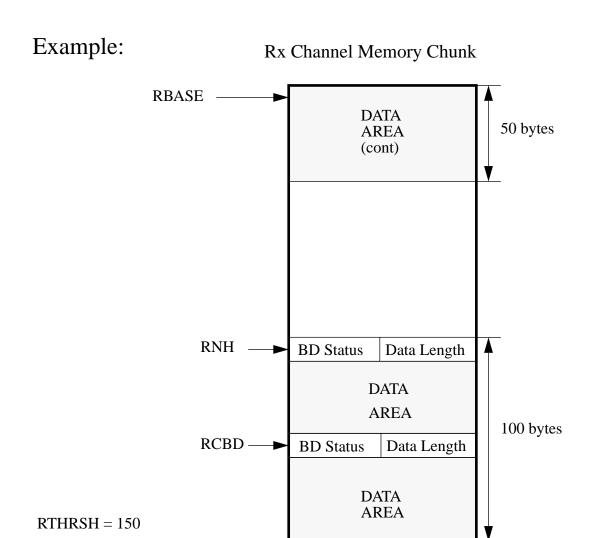

| 4.5.5.1             | RX BD Table Pointer (RBASE)                                   |                |

| 4.5.5.1             | · · · · · · · · · · · · · · · · · · ·                         |                |

| 4.5.5.2             | RX Chunk Length (RLEN)RX Interrupt Threshold (RTHRSH)         |                |

| 4.5.5.4             |                                                               |                |

| 4.5.5.5             | CPU First Not Handled BD (RNH)RX Time-OUT(RTO)                |                |

| 4.5.5.6             | Maximum Receive Buffer Length Register (MRBLR)                |                |

| 4.5.5.7             |                                                               |                |

| 4.5.5.7             | RX Current BD (RCBD)TX BD Table Pointer (TBASE)               | 4-24           |

| 4.5.5.6             |                                                               |                |

| 4.5.5.9             | Transmitter Buffer Descriptor Pointer (TBPTR)                 |                |

|                     | SCC Event Register (SCCE)                                     |                |

| 4.5.7<br>4.5.8      | SCC Mask Register (SCCM)                                      |                |

|                     | SCC Status Register (SCCS)                                    |                |

| 4.5.9               | Disabling the SCCs                                            |                |

| 4.5.10              | HDLC Controller                                               |                |

| 4.5.10.1            | HDLC Channel Frame Transmission Processing                    |                |

| 4.5.10.2            | HDLC Channel Frame Reception Processing                       |                |

| 4.5.10.3            | HDLC Memory Map                                               |                |

| 4.5.10.4            | HDLC Programming Model                                        |                |

| 4.5.10.5            | HDLC Command Set                                              |                |

| 4.5.10.6            | HDLC Address Recognition                                      |                |

| 4.5.10.7            | HDLC Error-Handling Procedure                                 |                |

| 4.5.10.8            | HDLC Receive Buffer Descriptor (Rx BD)                        |                |

| 4.5.10.9            | HDLC Transmit Buffer Descriptor (TxBD)                        |                |

| 4.5.10.10           | HDLC Event Register                                           |                |

| 4.5.10.11           | HDLC Mask Register                                            |                |

| 4.5.11              | Transparent Controller                                        |                |

| 4.5.11.1            | Transparent Channel Buffer Transmission Processing            |                |

| 4.5.11.2            | Transparent Channel Buffer Reception Processing               |                |

| 4.5.11.3            | Transparent Memory Map                                        |                |

| 4.5.11.4            | Transparent Commands                                          |                |

| 4.5.11.5            | Transparent Synchronization                                   | 4-39           |

| 4.5.11.6            | Transparent Error-Handling Procedure                          |                |

| 4.5.11.7            | Transparent Receive Buffer Descriptor (RxBD)                  |                |

| 4.5.11.8            | Transparent Transmit Buffer Descriptor (TxBD)                 |                |

| 4.5.11.9            | Transparent Event Register                                    |                |

| 4.5.11.10           | Transparent Mask Register                                     |                |

| 4.5.12              | SCC2/3 Clocking in NMSI mode                                  |                |

| 4.5.12.1            | SCC2/3 NMSI Interface                                         |                |

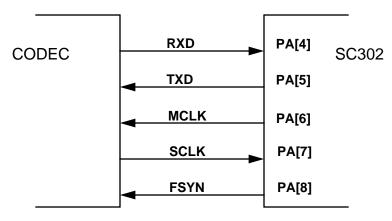

| 4.5.12.2            | SCC2/3 CODEC Interface                                        |                |

| 4.5.12.3            | Configuration Register (SCON)                                 |                |

| 4.6                 | Serial Communication Port (SCP)                               |                |

| 4.6.1               | SCP Programming Model                                         | 4-47           |

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

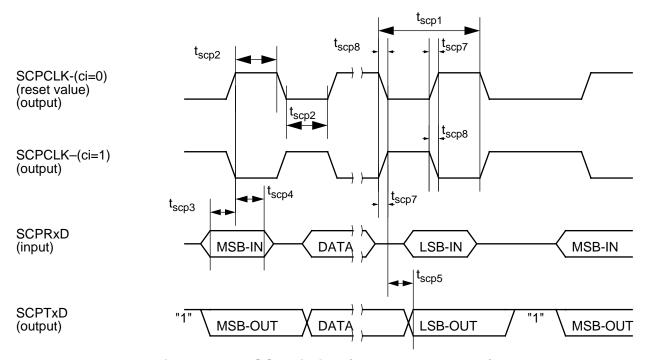

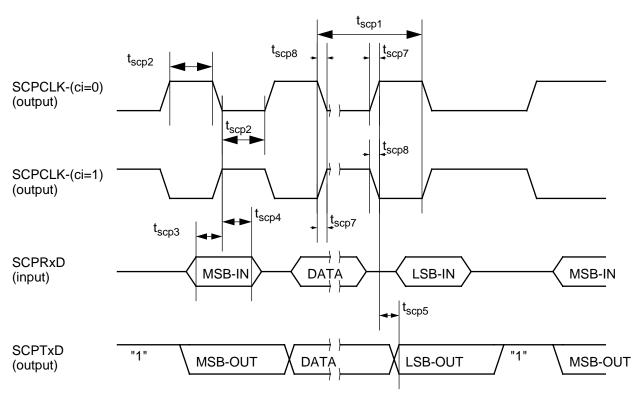

| 4.6.2               | SCP Clock and Data Relationship              | 4-49           |

| 4.6.3               | SCP Transmit/Receive Buffer Descriptor       | 4-49           |

| 4.6.3.1             | SCP Data Transmit/Receive Processing         | 4-50           |

| 4.6.3.2             | SCP - Serial EEPROM interface                | 4-50           |

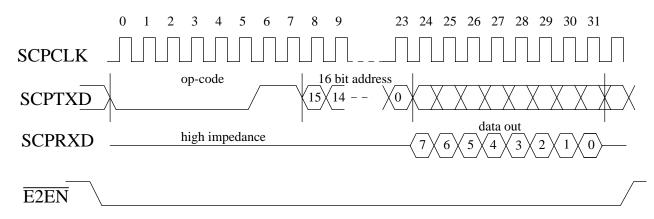

| 4.6.3.2.1           | 16- Bit Address EEPROM                       | 4-50           |

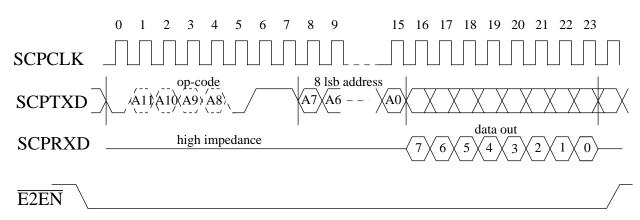

| 4.6.3.2.2           | 8-Bit Address EEPROM                         | 4-51           |

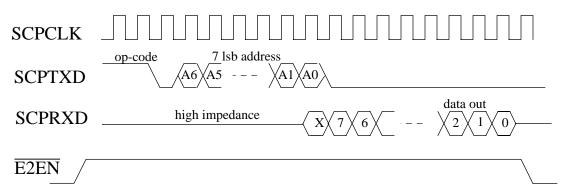

| 4.6.3.2.3           | Mixed Address EEPROM                         | 4-52           |

| 4.7                 | Serial Management Controllers (SMCs)         | 4-52           |

| 4.7.1               | SMC Overview                                 |                |

| 4.7.1.1             | Using GCI with the SMCs                      | 4-52           |

| 4.7.2               | SMC Programming Model                        | 4-54           |

| 4.7.3               | SMC Commands                                 |                |

| 4.7.4               | SMC Memory Structure and Buffers Descriptors | 4-54           |

| 4.7.4.1             | SMC1 Receive Buffer Descriptor               |                |

| 4.7.4.2             | SMC1 Transmit Buffer Descriptor              | 4-56           |

| 4.7.4.3             | SMC2 Receive Buffer Descriptor               | 4-56           |

| 4.7.4.4             | SMC2 Transmit Buffer Descriptor              | 4-57           |

| 4.7.5               | SMC Interrupt Requests                       | 4-57           |

| 4.8                 | Revision Number                              | 4-58           |

|                     | Section 5 ISA Plug and Play Interface        |                |

| 5.1                 | Introduction                                 | 5-1            |

| 5.2                 | Main Features                                | 5-1            |

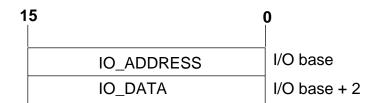

| 5.3                 | ISA Memory Map                               |                |

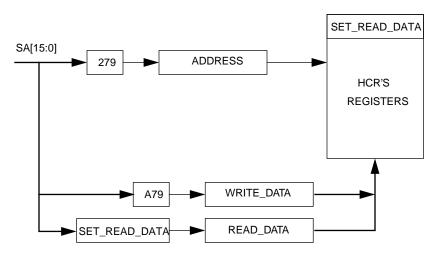

| 5.3.1               | ISA I/O Address Space                        | 5-2            |

| 5.3.1.1             | DPR Addressing                               |                |

| 5.3.1.2             | CCR Addressing                               | 5-4            |

| 5.3.2               | ISA Memory Address Space                     |                |

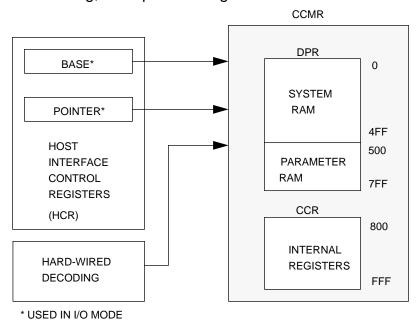

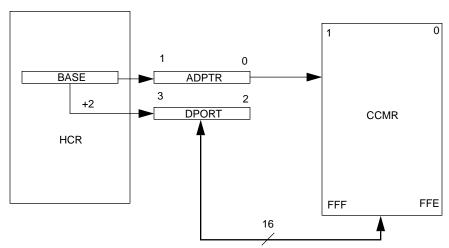

| 5.3.3               | CCMR Structure                               | 5-4            |

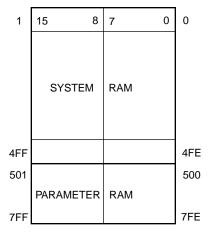

| 5.3.3.1             | DPR                                          |                |

| 5.3.3.2             | Parameter RAM                                |                |

| 5.3.3.3             | CCR Register Map                             |                |

| 5.4                 | ISA-PNP Configuration Programming            |                |

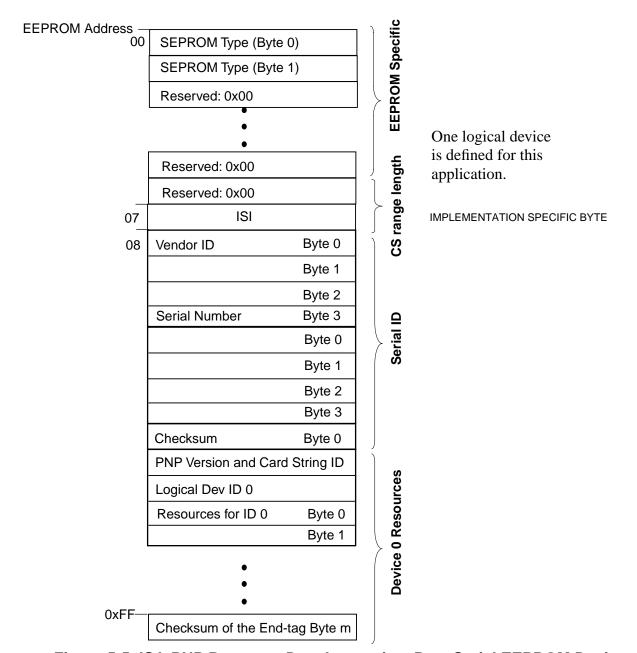

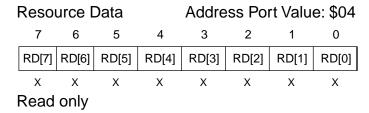

| 5.4.1               | Resource Data Layout in a Byte Serial Device |                |

| 5.4.2               | Reading Resource Data                        |                |

| 5.4.3               | I/O Configuration                            |                |

| 5.4.4               | Memory Configuration                         |                |

| 5.4.5               | IRQ Configuration                            | 5-12           |

| 5.4.6               | Resource Management                          |                |

| 5.4.7               | Logical Device ID                            |                |

| 5.4.8               | Unsupported Resources                        |                |

| 5.5                 | ISA-PNP Card Level Control Registers         | 5-13           |

| 5.6                 | Logical Device Control Registers             |                |

| 5.7                 | ISA-PNP Configuration Registers              |                |

| 5.7.1               | Access to Inactive Registers                 | 5-25           |

| Paragraph<br>Number | Title                                                            | Page<br>Number |

|---------------------|------------------------------------------------------------------|----------------|

| 5.8                 | ISA-PNP Control Registers Summary                                | 5-26           |

| 5.9                 | ISA-PNP Configuration Registers Summary                          | 5-28           |

| 5.10                | Card Configuration and Control Register Map (CCR)                | 5-30           |

| 5.11                | Host Interface Control Register Map (HCR)                        |                |

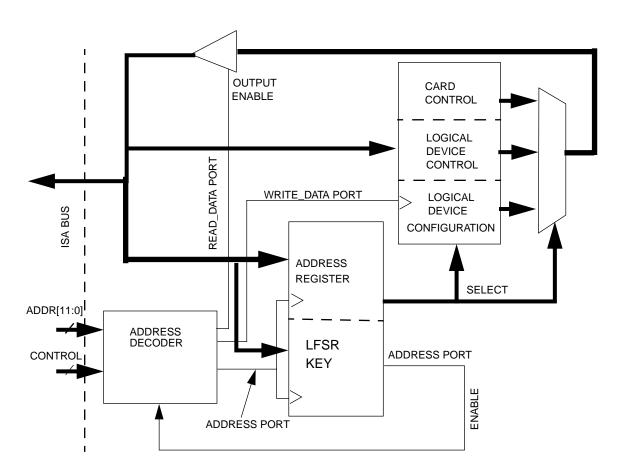

| 5.12                | ISA-PNP Physical Interface BAckground                            | 5-37           |

| 5.13                | Initiation Key                                                   | 5-38           |

| 5.14                | Isolation Protocol                                               | 5-38           |

| 5.14.1              | General                                                          | 5-38           |

| 5.14.2              | The Protocol                                                     | 5-39           |

| 5.14.3              | Timing Issues Related to Serial Isolation                        | 5-40           |

| 5.15                | Run-Time Access to ISA-PNP                                       | 5-41           |

|                     | Section 6 PCMCIA Interface                                       |                |

| 6.1                 | Introduction                                                     | 6-1            |

| 6.2                 | PCMCIA Controller Key Features                                   | 6-1            |

| 6.3                 | PCMCIA Interface Functional Overview                             |                |

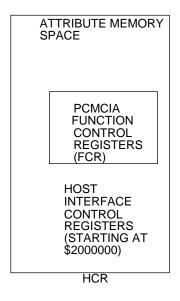

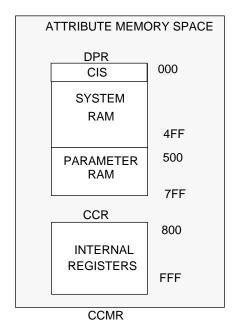

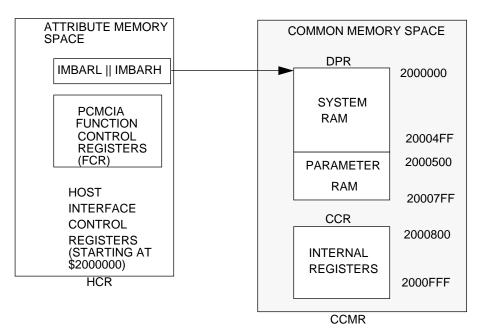

| 6.4                 | PCMCIA Memory Map                                                | 6-3            |

| 6.4.1               | Accessing the HCR Region (Both Serial and Parallel Cis EEPR Mode |                |

| 6.4.2               | Accessing the CCMR Region in Serial CIS EEPROM Mode              |                |

| 6.4.3               | Accessing the CCMR in Parallel CIS EEPROM mode                   |                |

| 6.4.4               | Accessing the External Chip Select Space                         |                |

| 6.4.5               | Accessing Host Interface Control Registers (HCR)                 |                |

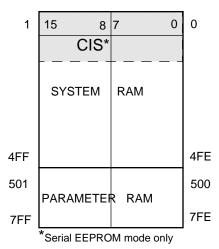

| 6.5                 | CCMR Memory Space                                                |                |

| 6.5.1               | Dual Ported RAM (DPR)                                            |                |

| 6.5.1.1             | System RAM                                                       |                |

| 6.5.1.2             | Parameter RAM                                                    |                |

| 6.5.2               | CCR Register Map                                                 |                |

| 6.6                 | Host Interface Control registers (HCR)                           |                |

| 6.6.1               | PCMCIA Function Configuration Registers (FCR)                    |                |

| 6.6.2               | 68SC302 Specific HCR Registers                                   |                |

| 6.7                 | PCMCIA bus Accesses.                                             |                |

| 6.7.1               | SC302 Power Management                                           |                |

| 6.7.1.1             | Enter Low Power                                                  |                |

| 6.7.1.2             | Wake Up                                                          |                |

| 6.7.1.3             | READY                                                            |                |

| 6.7.1.3             | PCMCIA Host Interrupts                                           |                |

| 6.7.3               | Unimplemented PCMCIA Signals                                     |                |

| 6.7.4               | PCMCIA EEPROM Format                                             |                |

|                     | Section 7                                                        |                |

| 7.4                 | Electrical Characteristics                                       | <del>-7</del>  |

| 7.1                 | Maximum Ratings                                                  | /-1            |

| 7.2                 | Thermal Characteristics                                          |                |

| 7.3                 | Power Considerations                                             | /-2            |

| Table of C | ontents |

|------------|---------|

|------------|---------|

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 7.4                 | Power Dissipation                            | 7-2            |

| 7.5                 | DC Electrical Characteristics                |                |

| 7.6                 | AC Electrical Specifications                 | 7-4            |

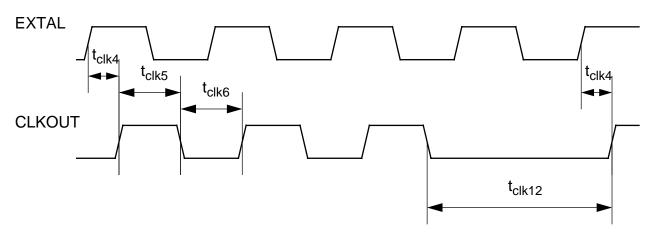

| 7.6.1               | CLKOUT Timing Specifications                 | 7-4            |

| 7.6.2               | ISA Host Interface Timing Specifications     |                |

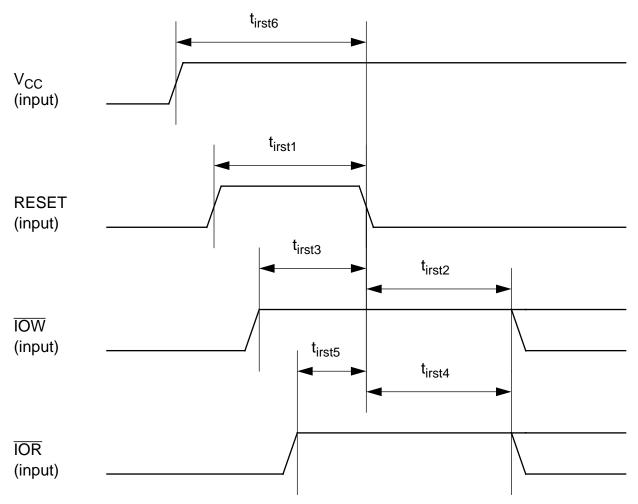

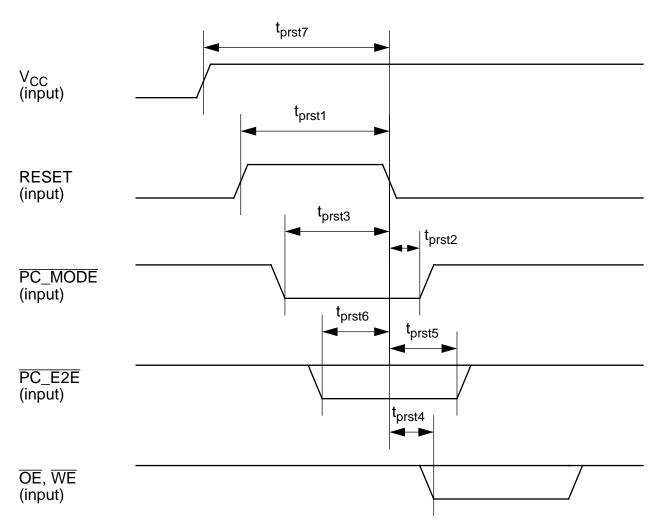

| 7.6.2.1             | ISA Reset Timing Specifications              | 7-6            |

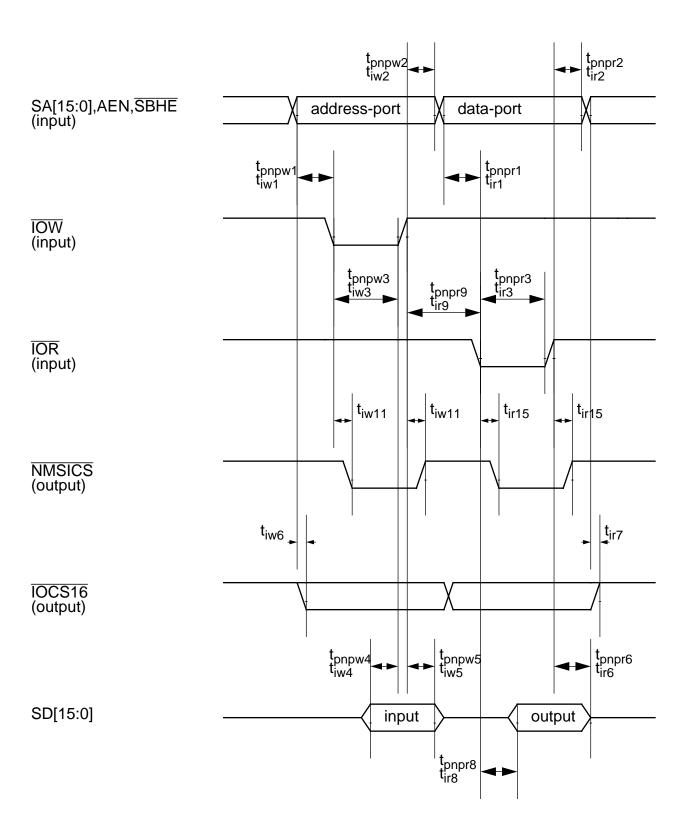

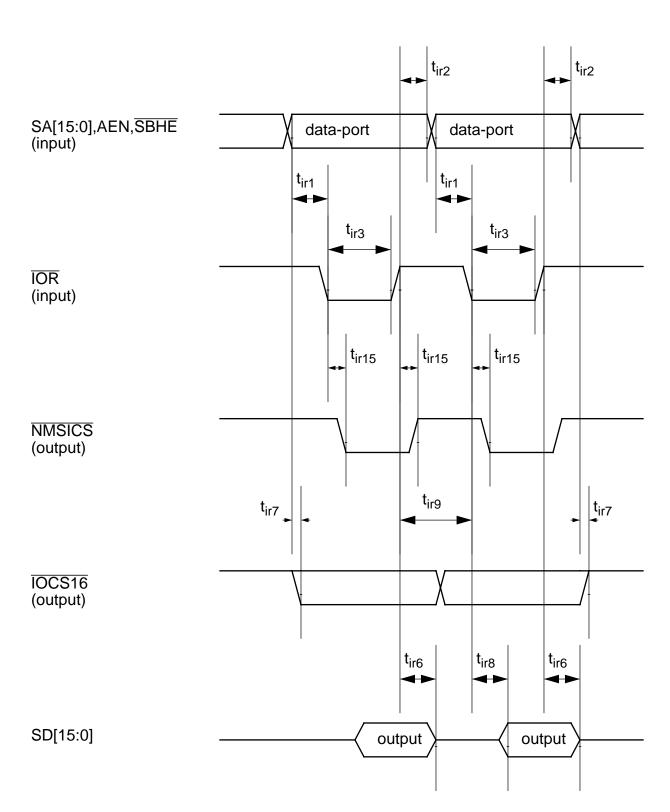

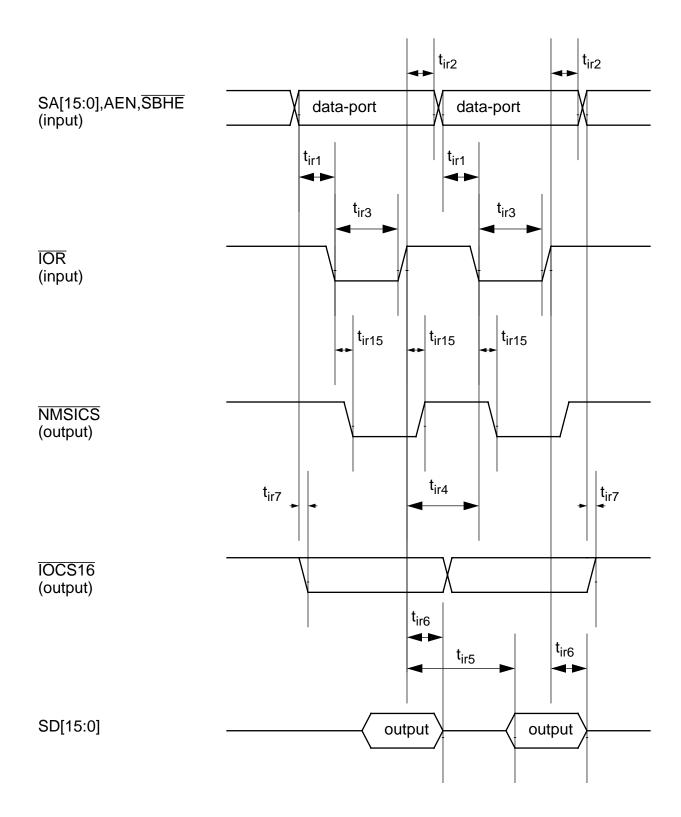

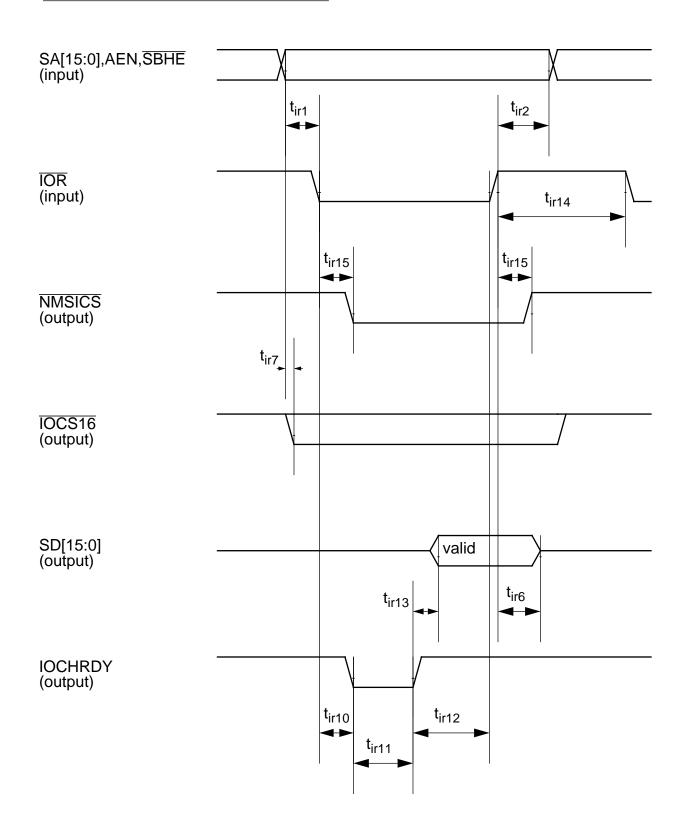

| 7.6.2.2             | ISA IO Space Read Access                     |                |

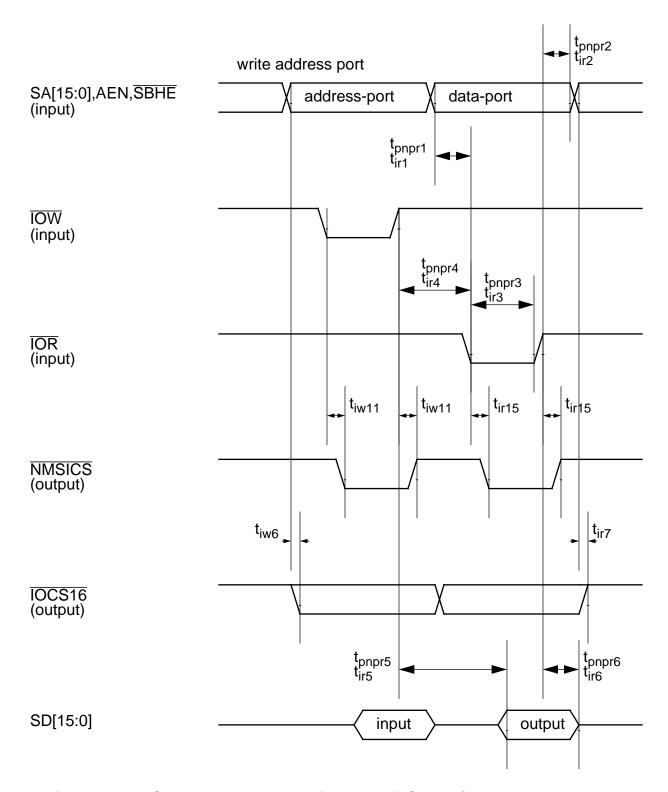

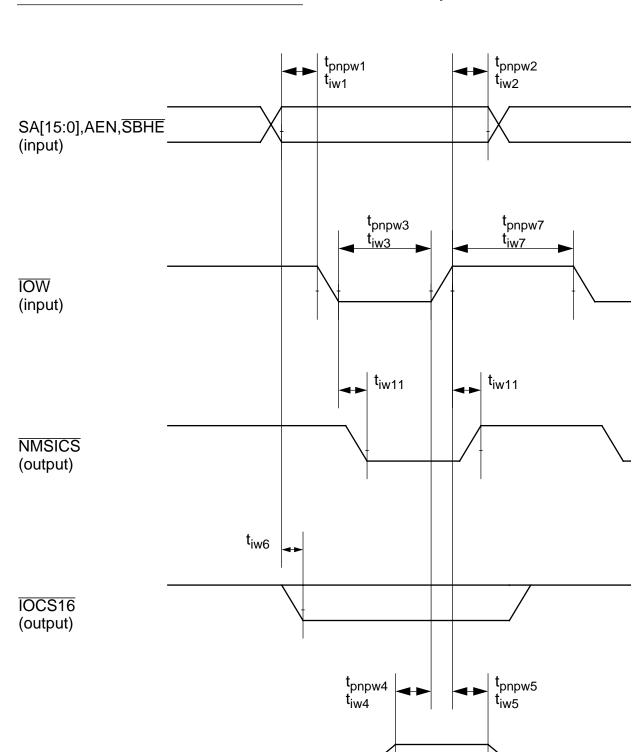

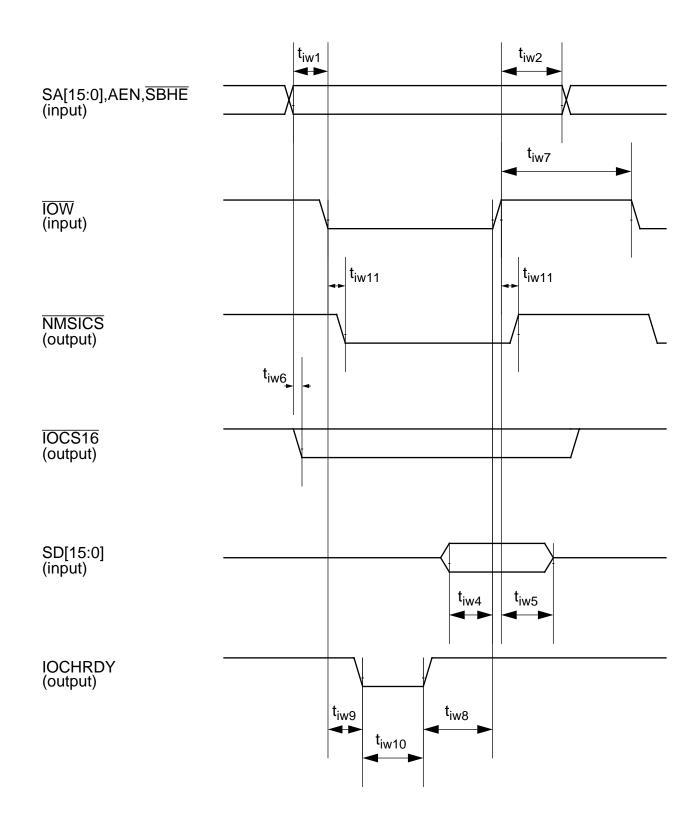

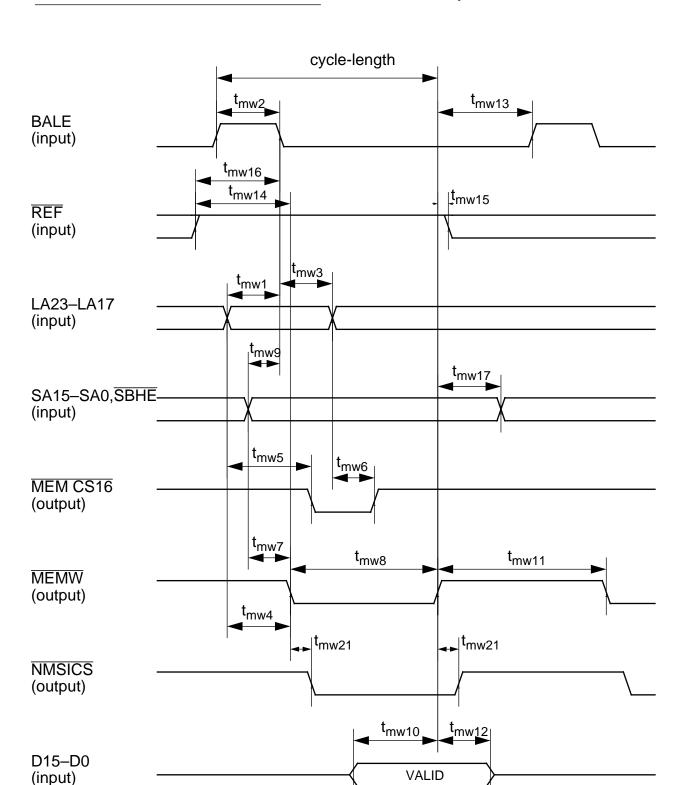

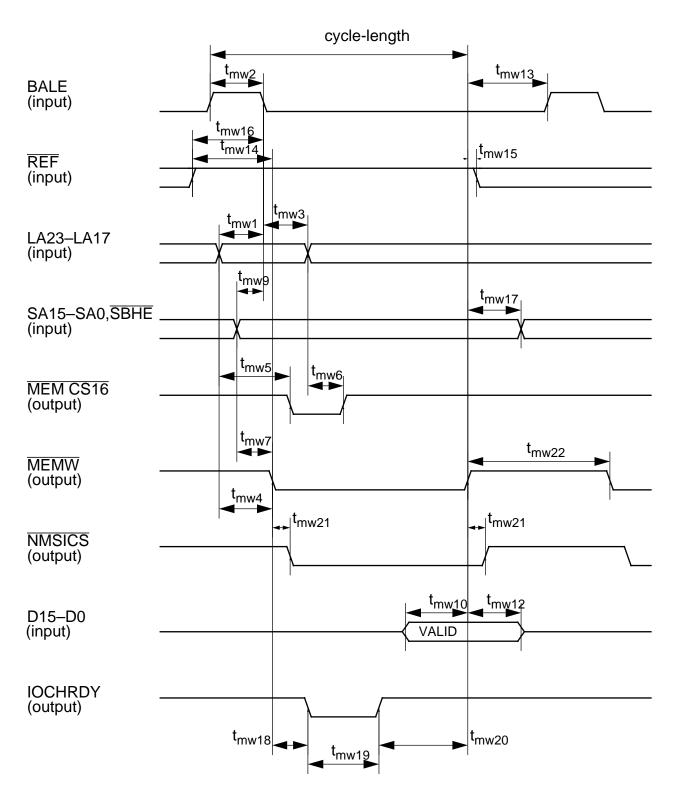

| 7.6.2.3             | IO Space Write Access                        | 7-13           |

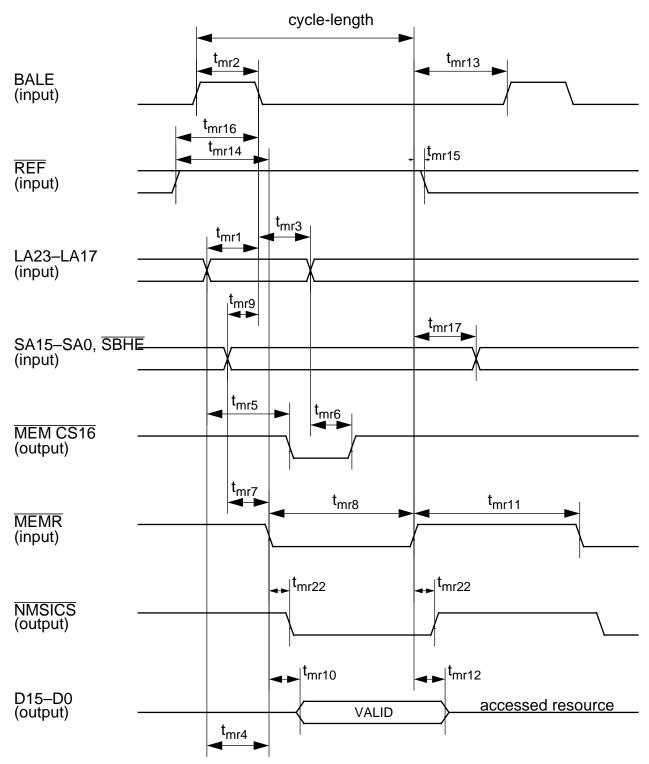

| 7.6.2.4             | Memory Space Read Access                     | 7-16           |

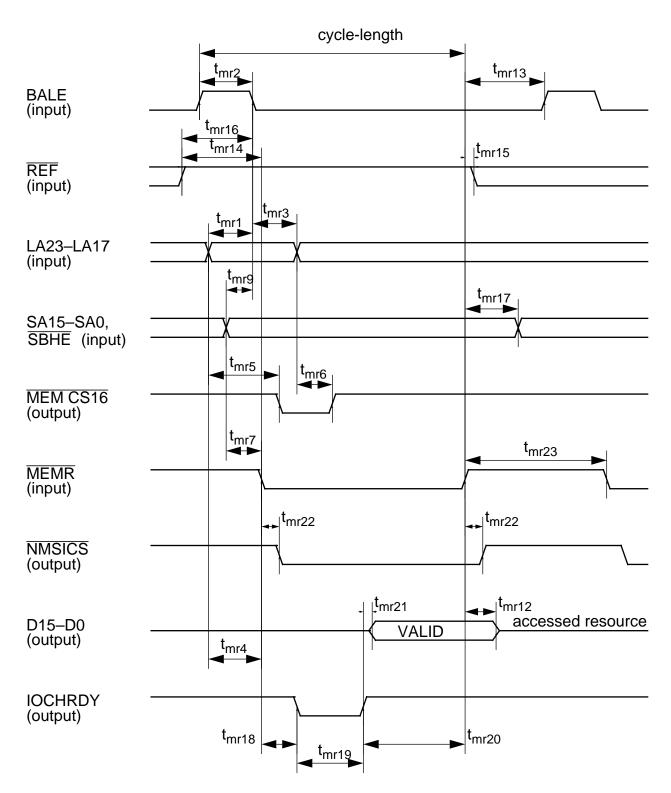

| 7.6.2.5             | Memory Space Write Access                    | 7-19           |

| 7.6.3               | PCMCIA Host Interface Timing Specifications  | 7-22           |

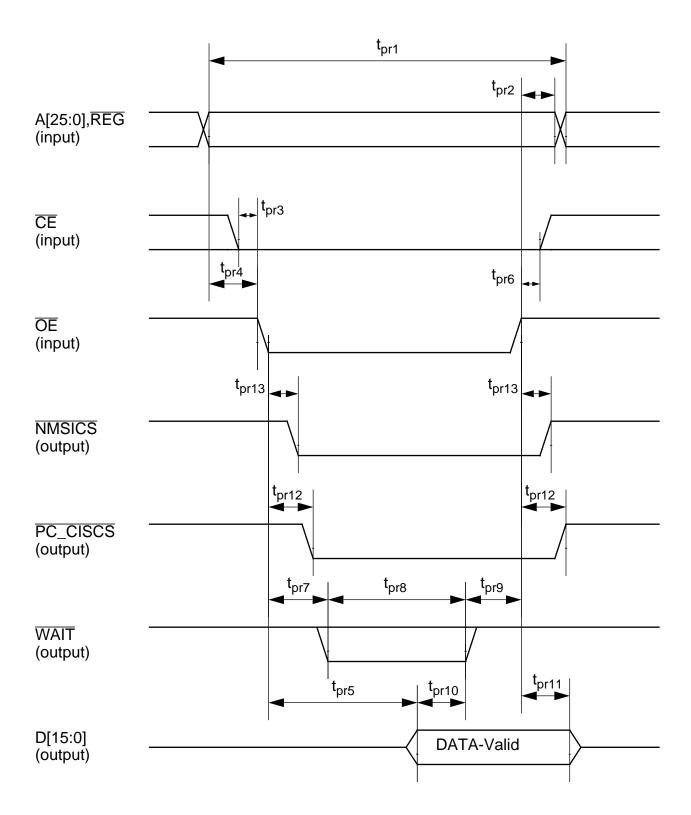

| 7.6.3.1             | PCMCIA Read Access with/without Wait States  | 7-22           |

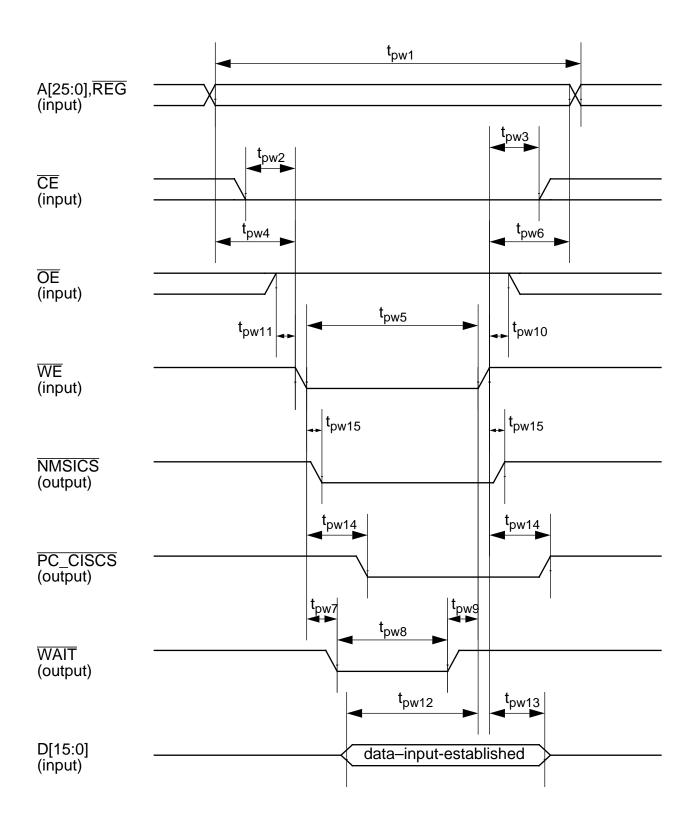

| 7.6.3.2             | PCMCIA Write Access with/without Wait States | 7-24           |

| 7.6.3.3             | PCMCIA Reset Timing Specifications           | 7-26           |

| 7.6.4               | Serial Interface Timing Specifications       | 7-27           |

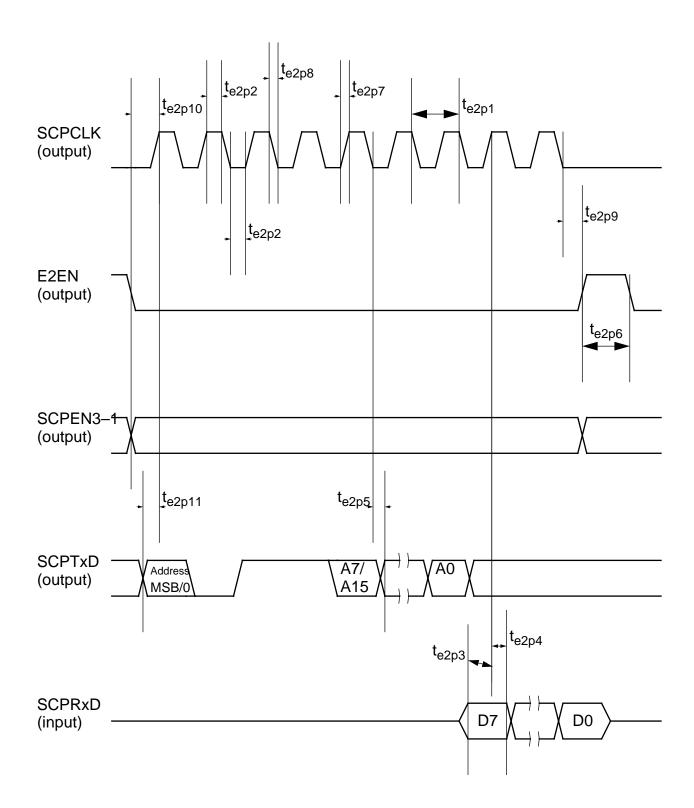

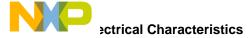

| 7.6.4.1             | SCP Timing Specifications                    |                |

| 7.6.4.2             | SERIAL EEPROM Timing Specifications          | 7-28           |

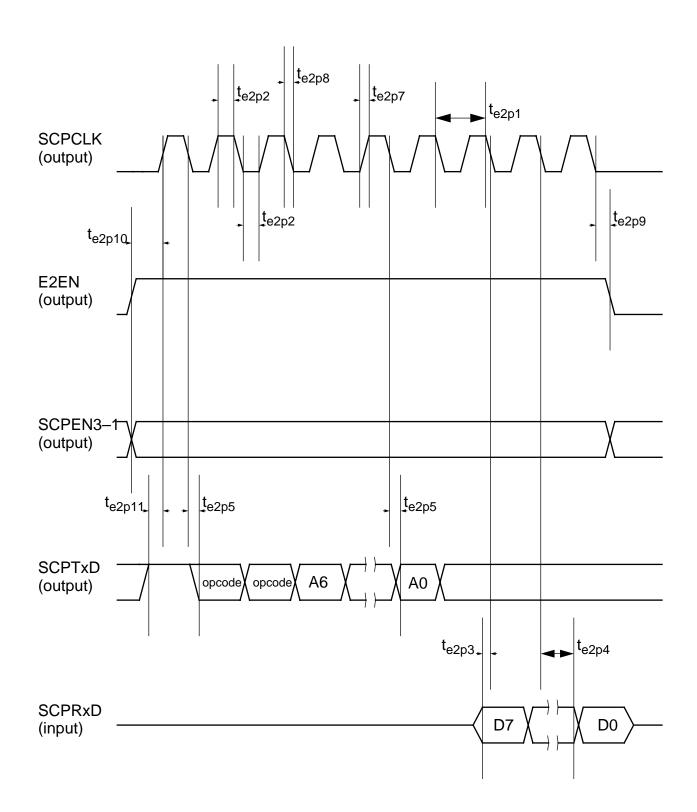

| 7.6.4.3             | IDL Timing Specifications                    | 7-31           |

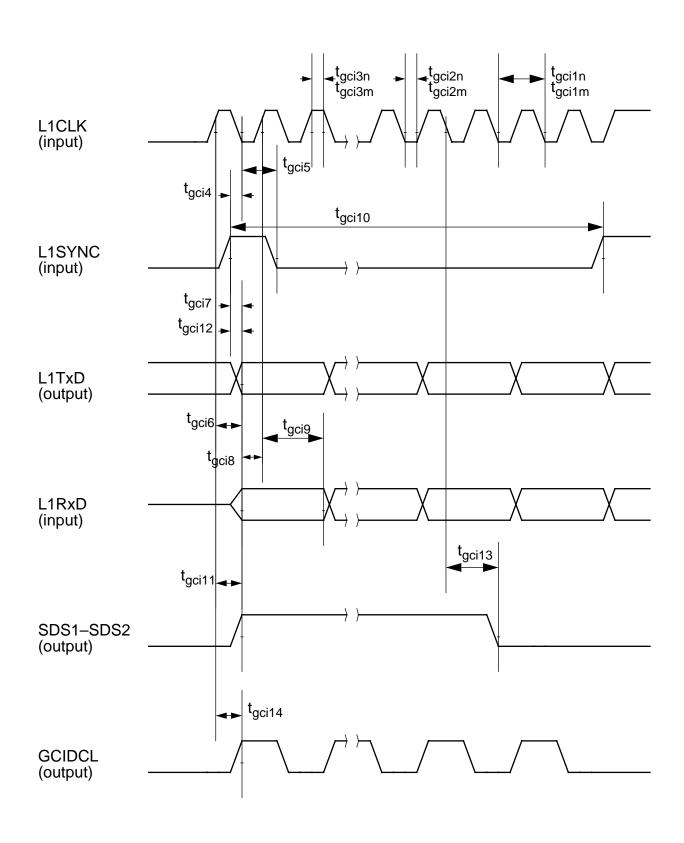

| 7.6.4.4             | GCI Timing Specifications                    | 7-33           |

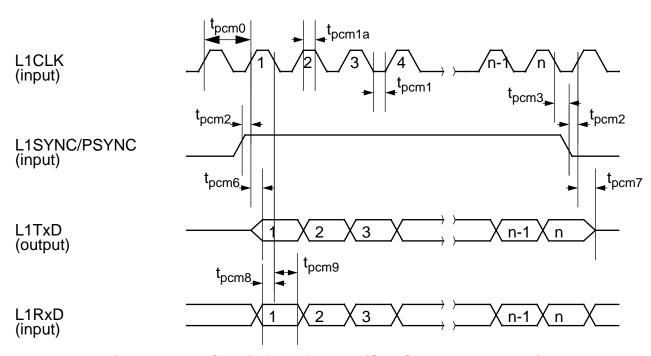

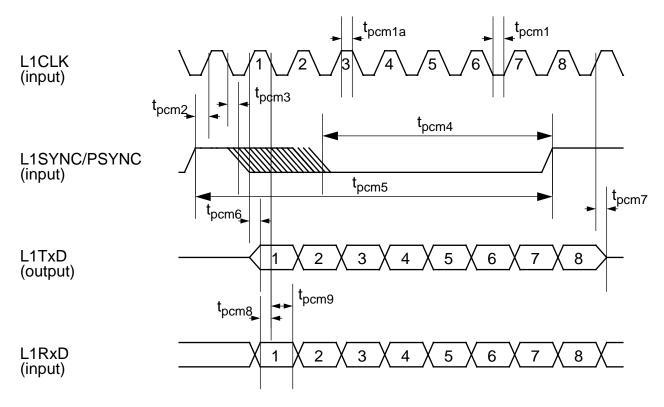

| 7.6.4.5             | PCM Timing Specifications                    |                |

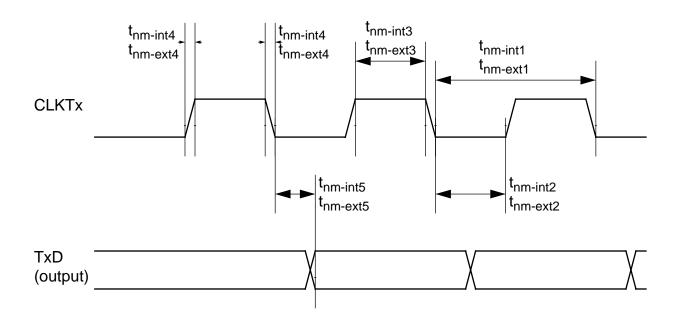

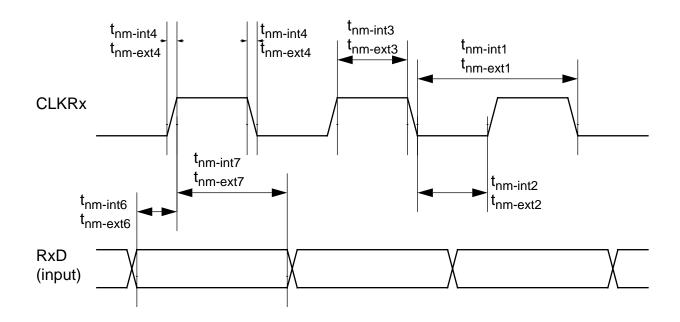

| 7.6.4.6             | NMSI Timing Specifications                   | 7-37           |

|                     | Section 8                                    |                |

|                     | Mechanical Data and Ordering Information     |                |

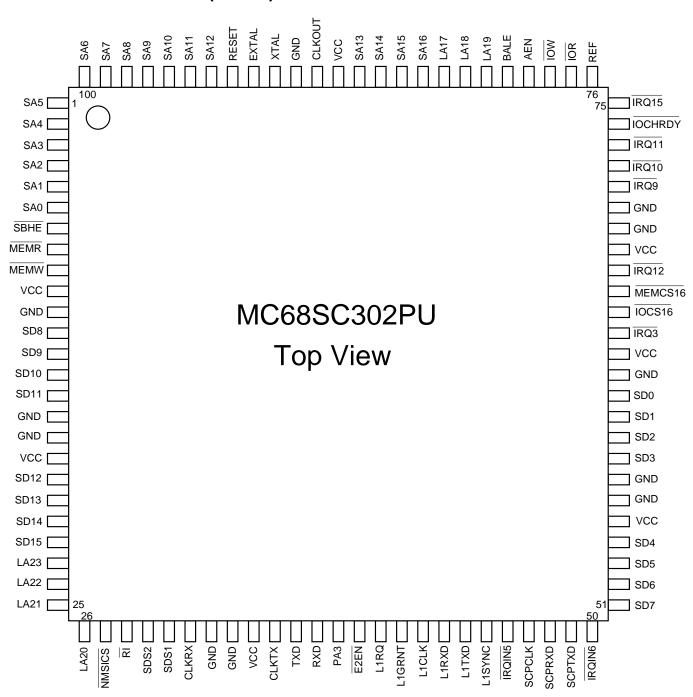

| 8.1                 | Pin Assignments                              | 8-1            |

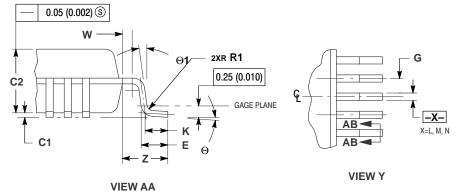

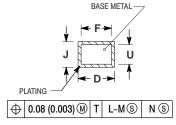

| 8.1.1               | Surface Mount (TQFP)                         | 8-1            |

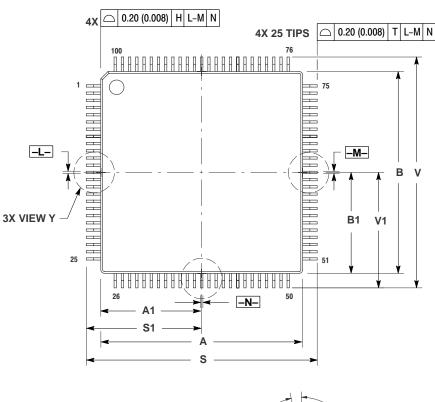

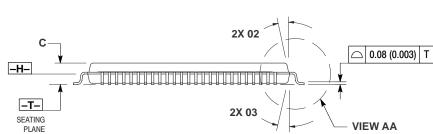

| 8.2                 | Package Dimensions                           | 8-2            |

| 8.2.1               | Surface Mount (TQFP)                         | 8 <b>-</b> 2   |

| 8.3                 | Ordering Information                         | 8-3            |

# **LIST OF FIGURES**

| Figure<br>Number | Title                                                 | Page<br>Number      |

|------------------|-------------------------------------------------------|---------------------|

|                  | Section 1                                             |                     |

|                  | MC68SC302 Overview                                    |                     |

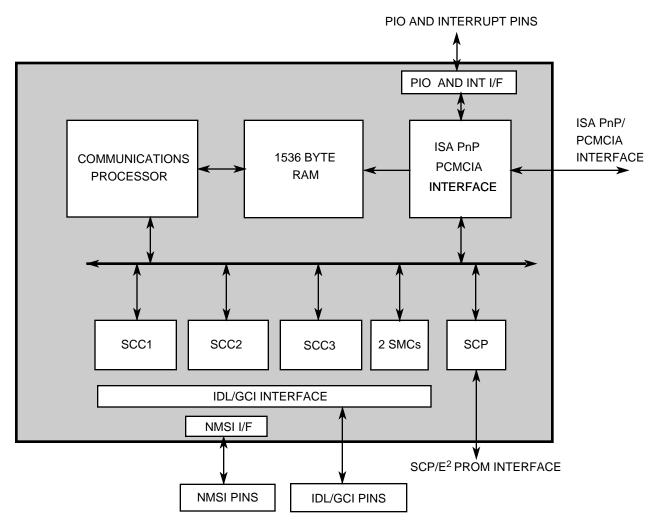

| _                | MC68SC302 Block Diagram                               |                     |

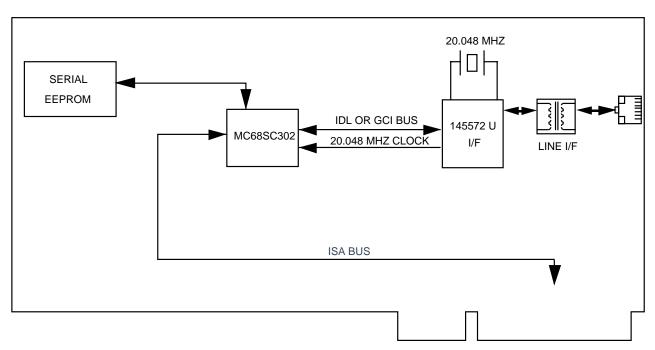

|                  | Passive NT1 TA Block Diagram                          |                     |

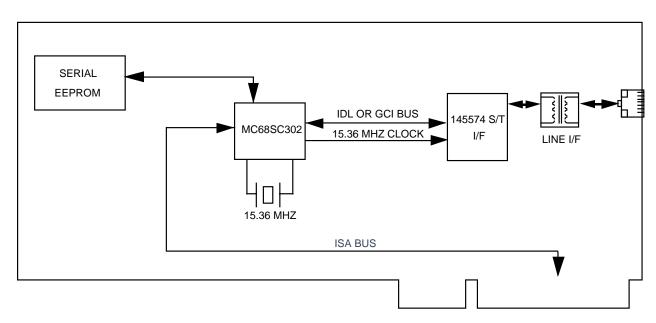

| -                | Passive NT1 TA Block Diagram with S/T Interface       |                     |

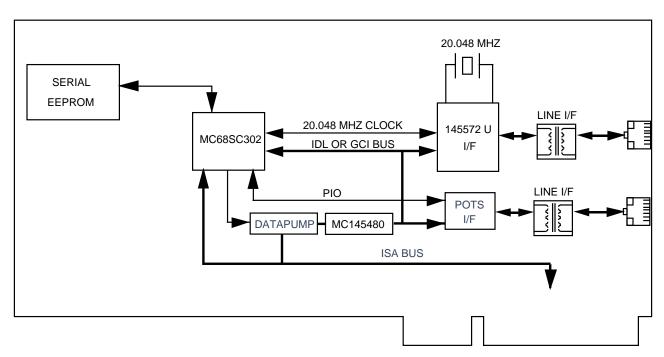

|                  | NT1 TA Block Diagram with POTS Interface and Datapump |                     |

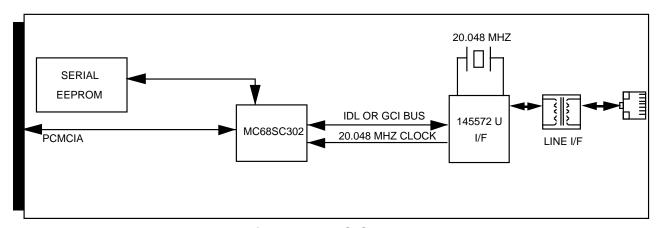

| _                | PC Card TA                                            |                     |

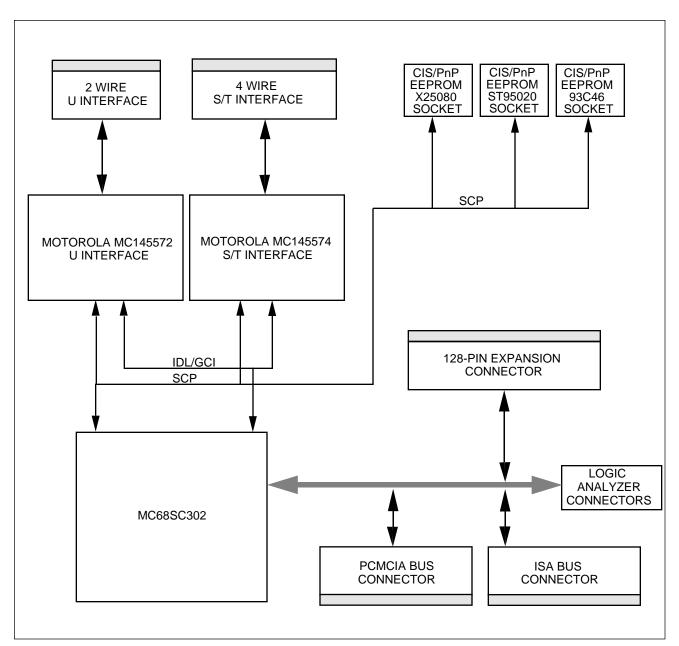

| Figure 1-6.      | ADS Block Diagram                                     | 1-8                 |

|                  | Section 2                                             |                     |

|                  | Signal Description and Pin Control                    |                     |

| Figure 2-1.      | Functional Signal Groups Description (82 Pin)         | 2-2                 |

|                  | Parallel I/O Port A Registers                         |                     |

|                  | O a strange                                           |                     |

|                  | Section 3                                             |                     |

|                  | Interrupt, Timer, and Power Control                   |                     |

|                  | Section 4                                             |                     |

|                  | Communications Processor (CP)                         |                     |

|                  | Serial Channels Physical Interface Block Diagram      |                     |

| •                | Two PCM Sync Methods                                  |                     |

|                  | PCM Channel Assignment on a T1/CEPT Line              |                     |

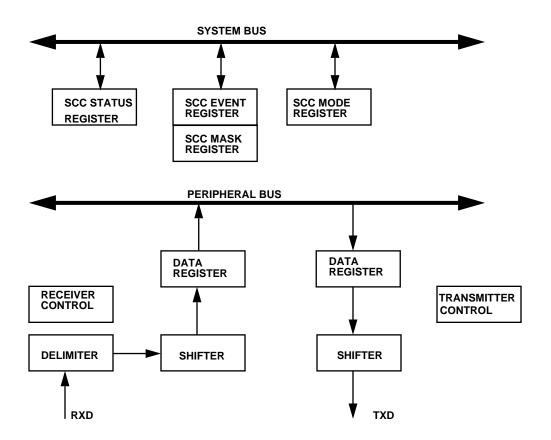

| _                | SCC Block Diagram                                     |                     |

| _                | Transmit BD                                           |                     |

| •                | Receive BD                                            |                     |

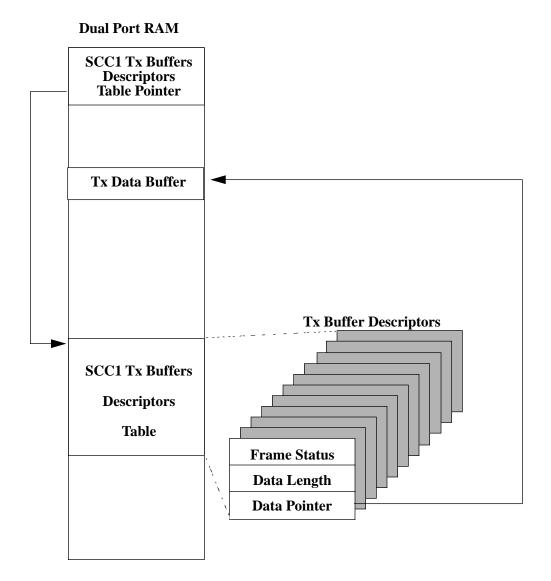

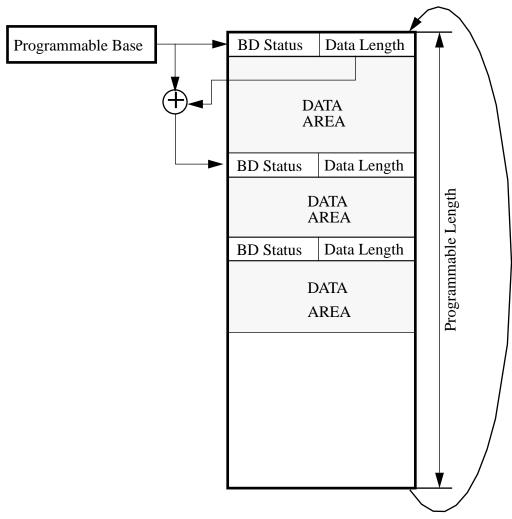

| •                | SCC Transmit Memory Structure                         |                     |

|                  | Rx Channel Memory Chunk                               |                     |

|                  | Typical HDLC Frame                                    |                     |

|                  | . HDLC Address Recognition Examples                   |                     |

| 0                | . HDLC Receive Buffer Descriptor                      |                     |

|                  | . HDLC Transmit Buffer Descriptor                     |                     |

| -                | Transparent Receive Buffer Descriptor                 |                     |

|                  | . Transparent Transmit Buffer Descriptor              |                     |

| -                | Codec Interface                                       |                     |

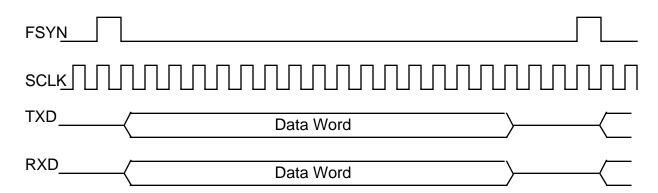

|                  | SESYN TimingSCC Baud Rate Generator                   |                     |

|                  | SCP Clock and Data Relationship                       |                     |

| 1 1441 C T-10    | . OOI - Olook alla Dala RolaliolioliiD                | <del>T - T</del> IJ |

| Figure<br>Number | Title<br>N                                                           | Page<br>Number |

|------------------|----------------------------------------------------------------------|----------------|

| Figure 4-19      | .16-Bit EEPROM Addressing                                            | 4-51           |

|                  | .8-Bit EEPROM Addressing                                             |                |

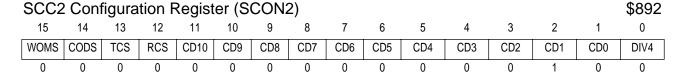

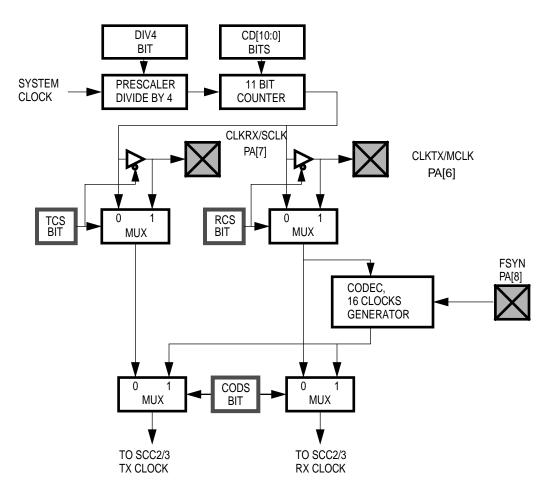

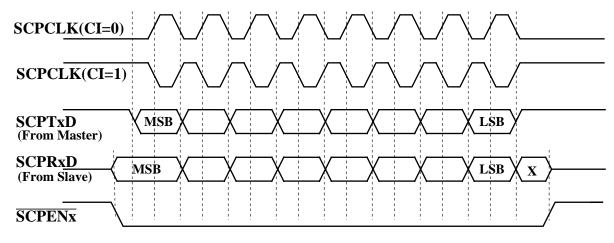

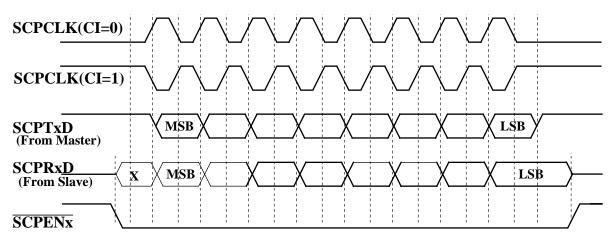

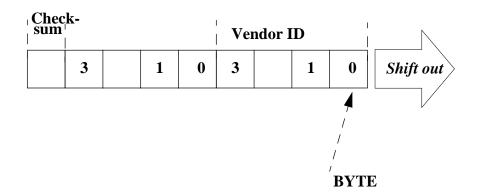

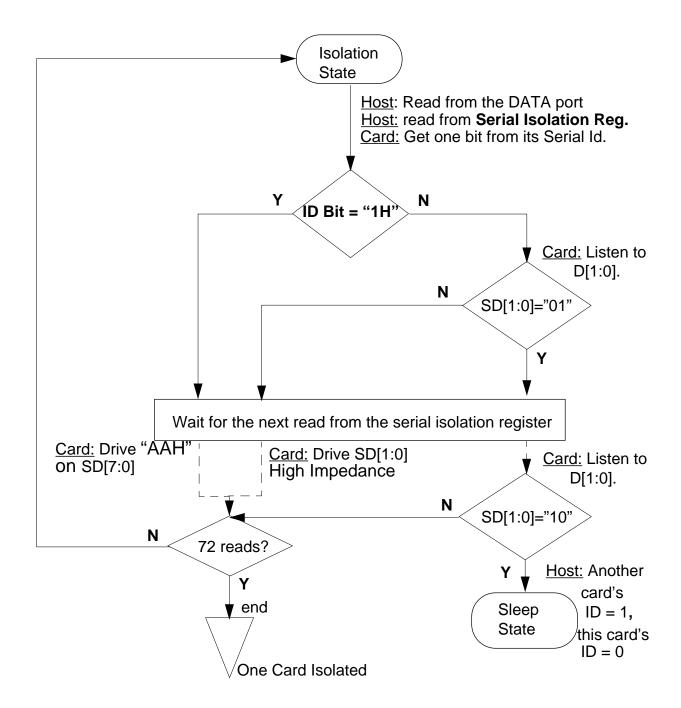

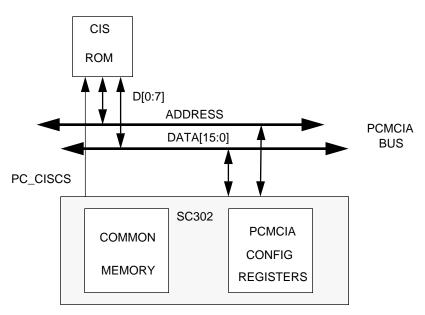

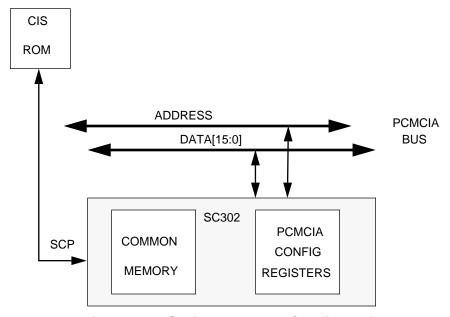

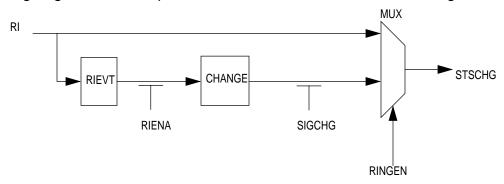

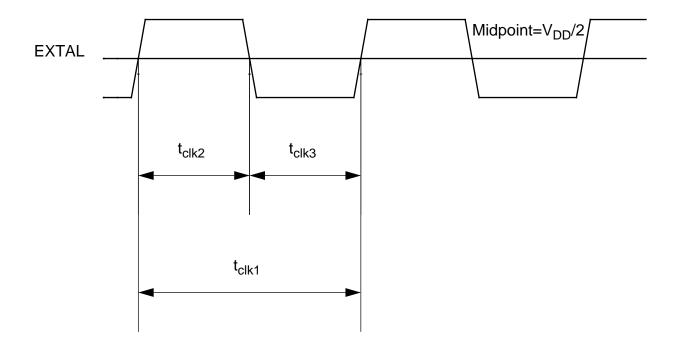

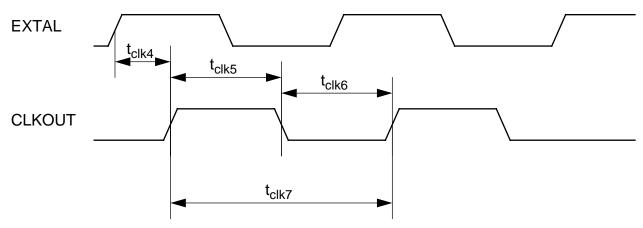

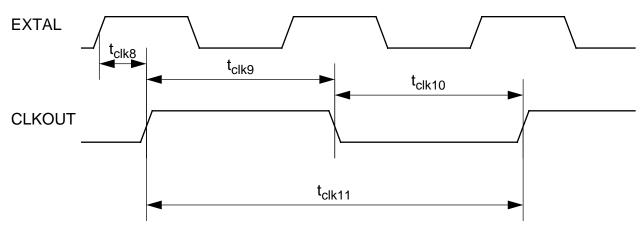

|                  | .Mixed Address EEPROM Addressing                                     |                |