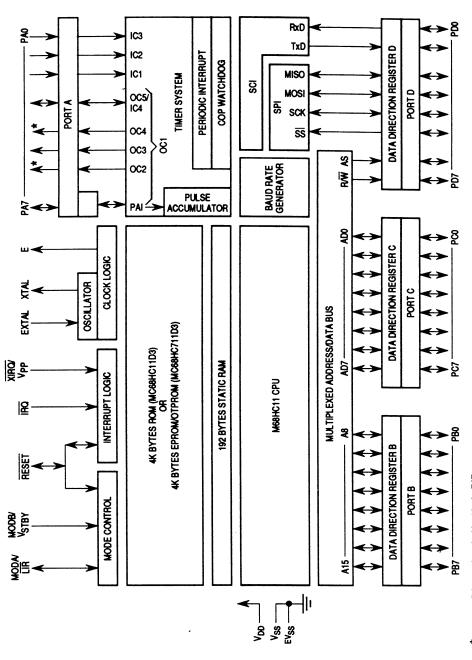

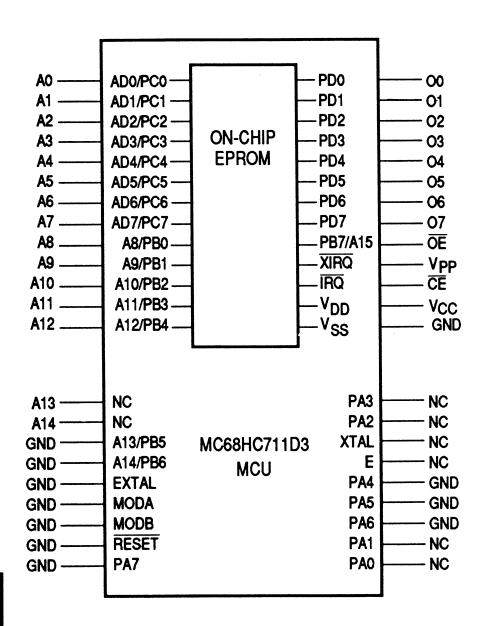

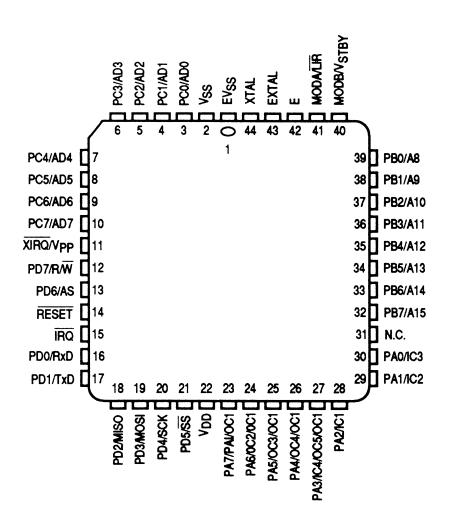

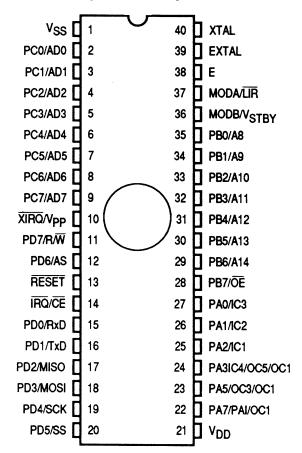

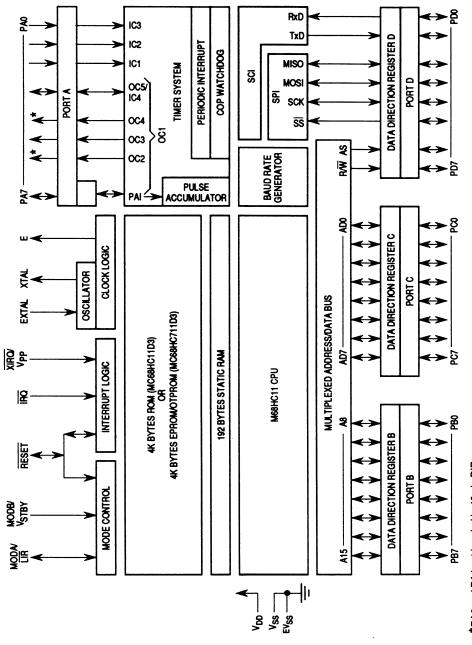

MC68HC11D3 MC68HC711D3

PROGRAMMING REFERENCE GUIDE

\*PA6 and PA4 not bonded in 40 pin DIP

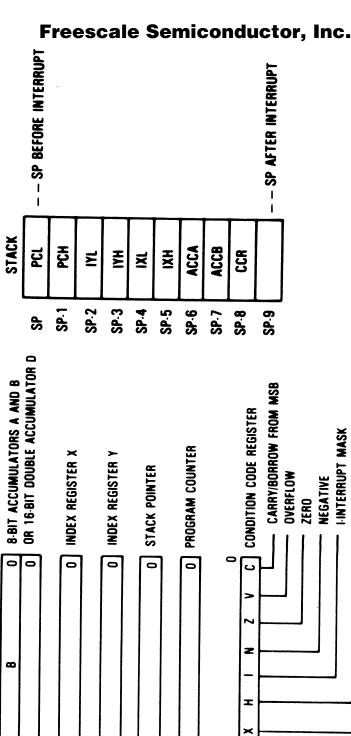

# PROGRAMMING MODEL CRYSTAL DEPENDENT TIMING INTERRUPTS

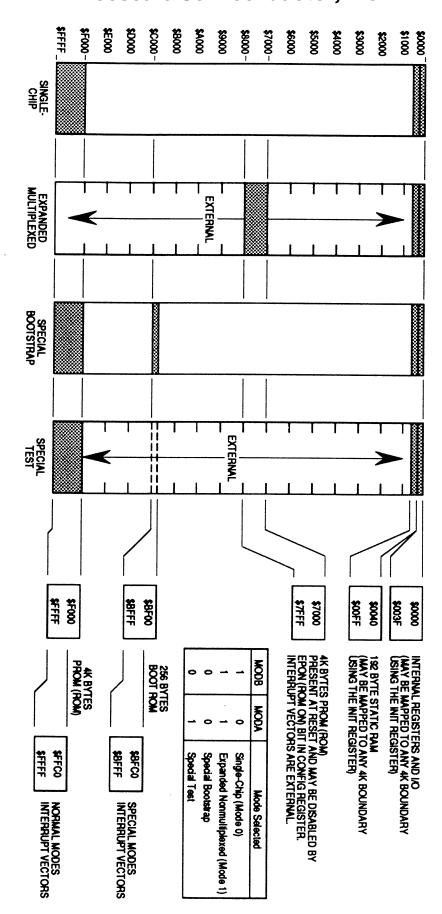

MEMORY MAP OPCODE MAPS

INSTRUCTIONS

ADDRESSING MODES

EXECUTION TIMES

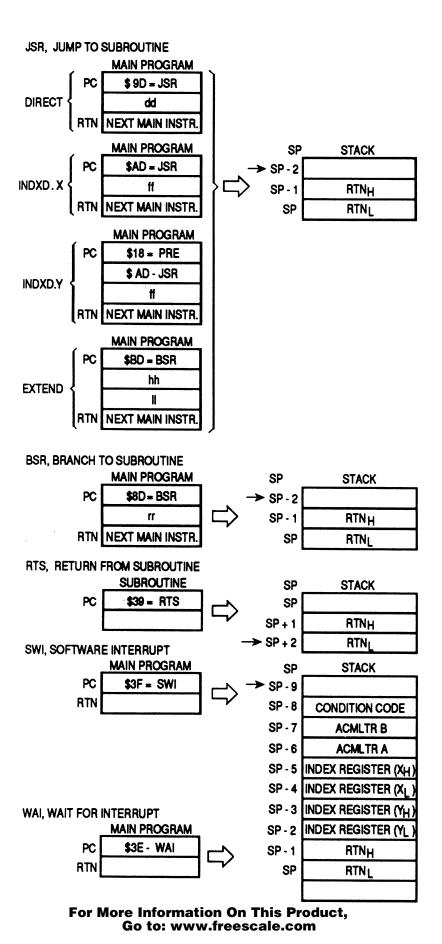

SPECIAL OPERATIONS

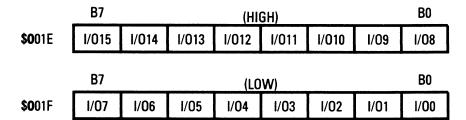

REGISTER AND CONTROL BIT ASSIGNMENTS

MECHANICAL DATA HEX/DEC CONVERSION ASCII CHART

© MOTOROLA, INC 1991

PROGRAMMING MODEL CRYSTAL DEPENDENT TIMING INTERRUPTS

MEMORY MAP OPCODE MAPS

INSTRUCTIONS

ADDRESSING MODES

EXECUTION TIMES

SPECIAL OPERATIONS

REGISTER AND CONTROL BIT ASSIGNMENTS

MECHANICAL DATA HEX/DEC CONVERSION ASCII CHART **PROGRAMMING MODEL**

HALF CARRY (FROM BIT 3)

I.INTERRUPT MASK

X-INTERRUPT MASK

For More Information On This Product, Go to: www.freescale.com

15

ည

S

≚

5

2

5

15

S

# CRYSTAL DEPENDENT TIMING SUMMARY

|                                |                  | Common Xtal F                   | Common Xtal Frequencies (others could be used) | could be used) |

|--------------------------------|------------------|---------------------------------|------------------------------------------------|----------------|

|                                | Selected Crystal | 2 <sup>23</sup> Hz<br>8.389 MHz | 8.0 MHz                                        | 4.0 MHz        |

| CPU Clock                      | (E)              | 2.1 MHz                         | 2.0 MHz                                        | 1.0 MHz        |

| Cycle Time                     | (1/E)            | 477 ns                          | 500 ns                                         | 1000 ns        |

| Periodic (RTI) Interrupt Rates | RTR_ 1 0         |                                 |                                                |                |

| (E/213)                        | 0 0              | 3.91 ms                         | 4.10 ms                                        | 8.19 ms        |

| (E/2 <sup>14</sup> )           | 0 1              | 7.81 ms                         | 8.19 ms                                        | 16.38 ms       |

| (E/215)                        | 1 0              | 15.62 ms                        | 16.38 ms                                       | 32.77 ms       |

| (E/2 <sup>16</sup> )           | -                | 31.25 ms                        | 32.77 ms                                       | 65.54 ms       |

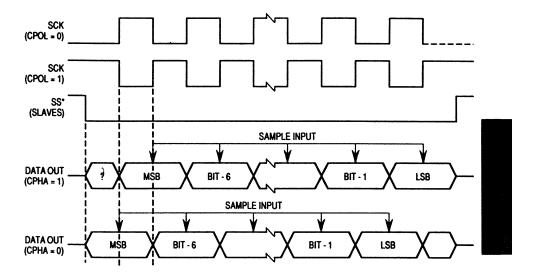

| SPI Bit Rates (baud)           | SPR_ 1 0         |                                 |                                                | , -            |

| (E/2)                          | 0 0              | 1.05 MHz                        | 1.0 MHz                                        | 200 K          |

| (E/4)                          | 0 1              | 524 K                           | 500 K                                          | 250 K          |

| (E/16)                         | 1 0              | 131 K                           | 125 K                                          | 62.5 K         |

| (E/32)                         | 1 1              | 65.5 K                          | 62.5 K                                         | 31.25 K        |

|                                |                  |                                 |                                                |                |

| is table                                                | eesc<br>le mole                                                                  | ale Sen<br>∠ "                          | icondu<br>× ~                           | <del>etor, In</del><br>× –              | uo ( (                                   |

|---------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|

| shown in th                                             | tes are simp                                                                     | —<br>62.40 K<br>488.3                   | <br>20.8 K<br>162.8                     | —<br>15.6 K<br>122.1                    | common<br>4800<br>37.56                  |

| Only the max and min baud rates are shown in this table | (SCR2-0=000 or 111). Additional rates are simple multiples of 2 from min to max. | —<br>124.80 K<br>976.6                  | —<br>41.6 K<br>325.5                    | —<br>31.2 K<br>244.1                    | common<br>9600<br>75                     |

| Only the max and                                        | (SCR2-0 = 000 or 111). Additibles of 2 from min to max.                          | custom<br>131.07 K<br>1024              | —<br>43.691 K<br>341.3                  | custom<br>32.768 K<br>256               | —<br>10.082 K<br>78.77                   |

|                                                         | 0                                                                                | 0 -                                     | 0                                       | 0                                       | 0                                        |

| 6                                                       | SCR_                                                                             | 0 -                                     | 0 -                                     | 0                                       | 0                                        |

| itrol Bits                                              | 2                                                                                | 0                                       | 0                                       | 0                                       | 0                                        |

| Cont                                                    | 0                                                                                | 0                                       | -                                       | 0                                       | 1                                        |

|                                                         | SCP_1                                                                            | 0                                       | 0                                       | 1                                       | 1                                        |

|                                                         | SCI Baud Rates                                                                   | (E/1)<br>(pre out/16)<br>(pre out/2048) | (E/3)<br>(pre out/16)<br>(pre out/2048) | (E/4)<br>(pre out/16)<br>(pre out/2048) | (E/13)<br>(pre out/16)<br>(pre out/2048) |

| M |   |  |

|---|---|--|

|   |   |  |

|   | _ |  |

|                                             |                                   | Common Xtal F                   | Common Xtal Frequencies (others could be used) | could be used)    |

|---------------------------------------------|-----------------------------------|---------------------------------|------------------------------------------------|-------------------|

|                                             | Selected Crystal                  | 2 <sup>23</sup> Hz<br>8.389 MHz | 8.0 MHz                                        | 4.0 MHz           |

| CPU Clock                                   | (E)                               | 2.1 MHz                         | 2.0 MHz                                        | 1.0 MHz           |

| Cycle Time                                  | (1/E)                             | 477 ns                          | 500 ns                                         | 1000 ns           |

| COP Watchdog Timeout Rates                  | CR_ 1 0                           |                                 |                                                |                   |

| (E/215)                                     | 0 0                               | 15.625 ms                       | 16.384 ms                                      | 32.768 ms         |

| (E/2 <sup>17</sup> )                        | 0 1                               | 62.5 ms                         | 65.536 ms                                      | 131.07 ms         |

| (E/2 <sup>19</sup> )                        | 1 0                               | 250 ms                          | 262.14 ms                                      | 524.29 ms         |

| $(E/2^{21})$                                | 1 1                               | 1.s                             | 1.049 s                                        | 2.1 s             |

| (E/215)                                     | Timeout Tolerance<br>( – 0 ms/ +) | 15.6 ms                         | 16.4 ms                                        | 32.8 ms           |

| Pulse Accum                                 | Pulse Accumulator (in gated mode) |                                 |                                                |                   |

| (E/2 <sup>6</sup> )<br>(E/2 <sup>14</sup> ) | 1 count –<br>overflow –           | 30.52 µs<br>7.80 ms             | 32 µs<br>8.19 ms                               | 64 μs<br>16.38 ms |

| <u>eesc</u>            | aie 5  | <u>CII</u> | 110 | onat                          | 101 | or, ir                        | IC. |                                |           |

|------------------------|--------|------------|-----|-------------------------------|-----|-------------------------------|-----|--------------------------------|-----------|

|                        | 1.0 µs | 65.54 ms   |     | 4.0 µs<br>262.1 ms            |     | 8.0 µs<br>524.3 ms            |     | 16.0 µs                        | 0.040.1   |

|                        | 500 ns | 32.77 ms   |     | 2.0 µs<br>131.1 ms            |     | 4.0 µs<br>262.1 ms            |     | 8.0 µs                         | 61110.420 |

|                        | 477 ns | 31.25 ms   |     | 1.91 µs<br>125 ms             |     | 3.81 µs<br>250 ms             |     | 7.63 µs                        | 5 0.0     |

| 0                      | 0      |            | -   |                               | 0   |                               | -   |                                |           |

| -                      | 0      |            | 0   |                               | _   |                               | -   |                                |           |

| PR                     |        |            |     |                               |     |                               |     |                                |           |

|                        |        | overflow – |     | 1 count –<br>overflow –       |     | 1 count –<br>overflow –       |     | 1 count –<br>overflow –        |           |

| Main Timer Count Rates | (E/1)  | (E/210)    |     | (E/4)<br>(E/2 <sup>18</sup> ) |     | (E/8)<br>(E/2 <sup>19</sup> ) |     | (E/16)<br>(E/2 <sup>20</sup> ) |           |

### **Interrupt Vector Assignments**

|                                              |                                                                                                                      |                                  |                               | 1         |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------|-----------|

| Vector<br>Address                            | Interrupt Source                                                                                                     | CC<br>Register<br>Mask           | Local<br>Mask                 |           |

| FFC0, C1                                     | Reserved                                                                                                             | _                                | _                             |           |

| FFD4, D5<br>FFD6, D7                         | Reserved SCI Serial System                                                                                           | —<br>I Bit                       | —<br>See Table                |           |

| FFDA, DB                                     | Pulse Accumulator Input Edge<br>Pulse Accumulator Overflow                                                           | I Bit<br>I Bit<br>I Bit<br>I Bit | SPIE<br>PAII<br>PAOVI<br>TOI  | EQUIATO : |

| FFE0, E1<br>FFE2, E3<br>FFE4, E5<br>FFE6, E7 | Timer Input Capture 4/Output Compare 5<br>Timer Output Compare 4<br>Timer Output Compare 3<br>Timer Output Compare 2 | I Bit<br>I Bit<br>I Bit<br>I Bit | 14051<br>OC41<br>OC31<br>OC21 | , i       |

|                                              | Timer Input Capture 3<br>Timer Input Capture 2                                                                       | l Bit<br>l Bit<br>l Bit<br>l Bit | OC1I<br>IC3I<br>IC2I<br>IC1I  |           |

| FFF2, F3                                     | Real-Time Interrupt IRO (External Pin) SEE HPRIO REGISTER FOR HIGHEST PRIORITY                                       | Bit<br>  Bit<br> -BIT SOU        | RTII<br>None<br>RCE           |           |

| FFF4, F5<br>FFF6, F7                         | XIRQ Pin (Pseudo Nonmaskable Interrupt)<br>SWI                                                                       | X Bit<br>None                    | None<br>None                  |           |

| FFF8, F9<br>FFFA, FB<br>FFFC, FD<br>FFFE, FF |                                                                                                                      | None<br>None<br>None<br>None     | None<br>NOCOP<br>CME<br>None  | ,         |

### **SCI Serial System Interrupts**

| Interrupt Cause              | Local Mask |

|------------------------------|------------|

| Receive Data Register Full   | RIE        |

| Receiver Overrun             | RIE        |

| Idle Line Detected           | ILIE       |

| Transmit Data Register Empty | TIE        |

| Transmit Complete            | TCIE       |

| 1000 8<br>1001 9<br>1010 A<br>1101 B<br>1110 C<br>1111 F |   |       |       |       |          |       | $\dashv$ | $\dashv$ |       | 0111 7 | 0110  | 0101   | 0100   | 0011   | 0010   | 0001  | 0000   | LSB | MSB    |       |                     |                                                                                             |

|----------------------------------------------------------|---|-------|-------|-------|----------|-------|----------|----------|-------|--------|-------|--------|--------|--------|--------|-------|--------|-----|--------|-------|---------------------|---------------------------------------------------------------------------------------------|

|                                                          | 0 | F SEI | E CLI | D SEC | C CLC    | B SEV | A CLV    | 9 DEX    | 8 INX | 7 TPA  | 6 TAP | 5 ASLD | 4 LSRD | 3 FDIV | 2 IDIV | 1 NOP | 0 TEST | 0   | B 0000 | Ī     |                     |                                                                                             |

|                                                          | 1 | BRCLR | BRSET | BCLR  | BSET     | ABA   | PG 3     | DAA      | PG 2  | TBA    | TAB   | BCLR   | BSET   | BRCLR  | BRSET  | CBA   | SBA    | 1   | 0001   | Ž     |                     |                                                                                             |

|                                                          | 2 | BLE   | BGT   | BLT   | BGE      | вмі   | BPL      | BVS      | BVC   | BEQ    | BNE   | BCS    | ВСС    | BLS    | вні    | BRN   | BRA.   | 2   | 0010   | REL   |                     | ב כ                                                                                         |

|                                                          | 3 | SWI   | WAI   | MUL   | PSHX     | RTI   | ABX      | RTS      | PULX  | PSHB   | PSHA  | TXS    | DES    | PULB   | PULA   | SNI   | XST    | 3   | 0011   | Ī     | OPCC                |                                                                                             |

|                                                          | 4 |       |       |       |          |       |          |          |       |        |       |        |        |        |        |       |        | 4   | 0100   | ACCA  | OPCODE WAP (PAGE I) |                                                                                             |

|                                                          | 5 | CLR   |       | TST   | INC      |       | DEC      | ROL      | ASL   | ASR    | ROR   |        | LSR    | сом    |        |       | NEG    | 5   | 0101   | АССВ  | Ar (r               | \<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\ |

|                                                          | 6 | .R    | JMP   | 15    | С        |       | C.       | )L       | 3L    | iR     | )R    |        | R      | M      |        |       | G      | 6   | 0110   | IND,X | AGE                 | 200                                                                                         |

|                                                          | 7 |       | ΛP    |       |          |       |          |          |       |        |       |        |        |        |        |       |        | 7   | 0111   | EXT   | 1)                  | 2                                                                                           |

|                                                          | 8 | XGDX  |       | BSR   |          |       |          |          |       |        |       |        |        |        |        |       |        | 8   | 1000   | MM    |                     |                                                                                             |

|                                                          | 9 |       | LDS   |       | СРХ      |       |          |          |       |        |       |        |        | SUBD   |        |       |        | 9   | 1001   | DIR   | ACCA                |                                                                                             |

|                                                          | Α | STS   | S     | JSR   | ×        |       |          |          |       | STA    |       |        |        | BD     |        |       |        | Α   | 1010   | IND,X | CA                  |                                                                                             |

|                                                          | В |       |       |       |          | ADD   | ORA      | ADC      | EOR   |        | LDA   | ВІТ    | AND    |        | SBC    | CMP   | SUB    | В   | 1011   | ЕХТ   |                     |                                                                                             |

|                                                          | С | STOP  |       | PG 4  |          | Ď     | A<br>A   | )C       | )R    |        | A     | T      | D      |        | 3C     | ΛP    | JB     | С   | 1100   | IMM   | ,                   |                                                                                             |

|                                                          | D |       | רנ    |       | רנ       |       |          |          |       |        |       |        |        | ADDD   |        |       |        | D   | 1101   | DIR   | АССВ                |                                                                                             |

|                                                          | Е | STX   | LDX   | STD   | LDD      |       |          |          |       | STA    |       |        |        | DD     |        |       |        | E   | 1110   | IND,X | СВ                  |                                                                                             |

|                                                          | F |       |       |       |          |       |          |          |       |        |       |        |        |        |        |       |        | F   | 1111   | EXT   |                     |                                                                                             |

|                                                          |   | 1     | 1     |       | <u> </u> | 1     |          |          |       | 1      |       | 1      | 1      | 1      |        | _     | 1      | _   |        |       |                     |                                                                                             |

| NP |

|----|

|----|

|                   |       |      |     | 0    | ŀ    |      | 2   | 3    | 4    | 5    | 9    | 7    | 8    | 6    | ⋖    | В    | C    | ć    | u           | , 4   | 1 |

|-------------------|-------|------|-----|------|------|------|-----|------|------|------|------|------|------|------|------|------|------|------|-------------|-------|---|

|                   | EXT   | 1111 | L   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | щ |

| gg                | IND,Y | 1110 | ы   | SUB  | CMP  |      | SBC | ADDD | AND  | BIT  | LDA  | STA  | EOR  | ADC  | ORA  | ADD  | QQT  | STD  |             | STY   | E |

| ACCB              | DIR   | 1101 | ٥   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      | \<br>\<br>! | 3     | D |

|                   | MM    | 1100 | ပ   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | ၁ |

|                   | EXT   | 1011 | 8   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | В |

| Ą                 | ND,Y  | 1010 | ∢   | SUB  | CMP  |      | SBC | SUBD | AND  | ВІТ  | PDA  | STA  | EOR  | ADC  | ORA  | ADD  |      | JSR  | SOI         | STS   | Ą |

| ACCA              | DIR   | 1001 | 6   |      |      |      |     |      |      |      |      |      |      |      |      |      | CPY  |      |             |       | 6 |

|                   | MMI   | 1000 | 8   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             | XGDX  | 8 |

|                   |       | 0111 | 7   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | 7 |

| E 2/ (10 XX)      | ND,Y  | 0110 | 9   | NEG  |      |      |     | COM  | LSR  |      | ROR  | ASR  | ASL  | ROL  | DEC  |      | INC  | TST  | JMP         | CLR   | 9 |

|                   |       | 0101 | 2   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | 5 |

| T L               |       | 0100 | 4   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | 4 |

| Z Z               | HNI   | 0011 | 3   | TSY  |      |      |     |      |      | TYS  |      |      | PULY |      | ABY  |      | PSHY |      |             |       | 3 |

| OF CODE INAT (FAG |       | 0010 | 2   |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |             |       | 2 |

| 5                 |       | 0001 | -   |      |      |      |     |      |      |      |      |      |      |      |      |      | BSET | BCLR | BRSET       | BRCLR | - |

|                   | Ξ     | 0000 | 0   |      |      |      |     |      |      |      |      |      | N≺   | DEY  |      |      |      |      |             |       | 0 |

| L                 | 7     | MSB  | 7   | 0    | -    | 6    | 1 ( | γ    | 4    | 5    | 9    | 7    | 8    | 6    | ۷    | В    | C    | D    | E           | Ŧ     |   |

|                   |       |      | LSB | 0000 | 0001 | 0010 |     | 1100 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110        | 1111  |   |

For More Information On This Product, Go to: www.freescale.com Y, QNI

|      |             |             | F    | re  | 0    | <b>56</b> | 2<br>2 | <del>او</del> | 4    | <u>و</u> | 9    | ,<br>e | Ðľ<br>∞ | 6    | ₩    | B    | O<br>O | <u>_</u> | E    | ь<br>Б |   |

|------|-------------|-------------|------|-----|------|-----------|--------|---------------|------|----------|------|--------|---------|------|------|------|--------|----------|------|--------|---|

|      |             |             | 1111 | ч   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | F |

|      | ACCB        | X'QNI       | 1110 | Ε   |      |           |        |               |      |          |      |        |         |      |      |      |        |          | LDY  | STY    | Е |

|      | AC          |             | 1101 | D   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | Q |

|      |             |             | 1100 | ပ   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | ၁ |

|      |             | EXT         | 1011 | В   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | В |

|      | ACCA        | IND,X       | 1010 | A   |      |           |        | СРD           |      |          |      |        |         |      |      |      | СРҮ    |          |      |        | A |

|      | AC          | DIR         | 1001 | 6   |      |           |        | IJ            |      |          |      |        |         |      |      |      |        |          |      |        | 6 |

|      |             | Σ<br>N<br>N | 1000 | 8   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 8 |

| 7    | <b>X</b>    |             | 0111 | 7   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 7 |

| ~~~! | E 3/ (IMAX) |             | 0110 | 9   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 9 |

| いこして | つ山りた        |             | 0101 | 5   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 5 |

|      |             |             | 0100 | 4   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 4 |

|      | 7<br>2<br>3 |             | 1100 | 3   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 3 |

|      |             |             | 0010 | 2   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 2 |

| •    |             |             | 1000 | 1   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 1 |

|      |             |             | 0000 | 0   |      |           |        |               |      |          |      |        |         |      |      |      |        |          |      |        | 0 |

|      |             |             | MSB  |     | 0    | 1         | 2      | 3             | 4    | 2        | 9    | 7      | 8       | 6    | ٧    | В    | ე      | a        | Ш    | ш      |   |

|      |             |             |      | LSB | 0000 | 0001      | 0010   | 0011          | 0100 | 0101     | 0110 | 0111   | 1000    | 1001 | 1010 | 1011 | 1100   | 1101     | 1110 | 1111   |   |

|                         | F    | re   | es  | Ç    | 티    | <b>e</b> 2 | Se   | ĒΪ   | S<br>I | <b>G</b> 9 | Δú   | d    | C<br>C | ₹    | B    | ပ    |      | L L  | ш    | 1 |

|-------------------------|------|------|-----|------|------|------------|------|------|--------|------------|------|------|--------|------|------|------|------|------|------|---|

|                         |      | 1111 | u.  |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | F |

| ACCB                    | ND,Y | 1110 | Э   |      |      |            |      |      |        |            |      |      |        |      |      |      |      | XQ1  | STX  | E |

| AC                      |      | 1101 | ۵   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | D |

|                         |      | 1100 | ၁   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | Э |

|                         |      | 1011 | 8   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | В |

| ACCA                    | ND,Y | 1010 | ٧   |      |      |            | CPD  |      |        |            |      |      |        |      |      | CPX  |      |      |      | А |

| AC                      |      | 1001 | 6   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 6 |

|                         |      | 1000 | 8   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 8 |

|                         |      | 0111 | 7   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 7 |

| 4)(CDxx)                |      | 0110 | 9   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 9 |

| GE 4)                   |      | 0101 | 2   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 9 |

| <b>OPCODE MAP (PAGE</b> |      | 0100 | 4   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 4 |

| E MA                    |      | 0011 | 3   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 3 |

| PCOD                    |      | 0010 | 2   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 2 |

| 0                       |      | 1000 | -   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 1 |

|                         |      | 0000 | 0   |      |      |            |      |      |        |            |      |      |        |      |      |      |      |      |      | 0 |

|                         |      | MSB  |     | 0    | 1    | 2          | 3    | 4    | 2      | 9          | 7    | 8    | 6      | А    | В    | 2    | a    | Е    | H.   |   |

|                         |      | _    | LSB | 0000 | 0001 | 0010       | 0011 | 0100 | 0101   | 0110       | 0111 | 1000 | 1001   | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |   |

### Freescalle//SlefmilBANGUESor, Inc.

| Mnemonic | Opcode | Cycles |

|----------|--------|--------|

| BRA      | 20     | 3      |

| BRN      | 21     | 3      |

| BSR      | 8D     | 7      |

### SIMPLE CONDITIONAL BRANCHES

| Test  | True | Opcode | False | Opcode |

|-------|------|--------|-------|--------|

| N = 1 | вмі  | 2B     | BPL   | 2A     |

| Z = 1 | BEQ  | 27     | BNE   | 26     |

| V = 1 | BVS  | 29     | BVC   | 28     |

| C = 1 | BCS  | 25     | BCC   | 24     |

### **SIGNED CONDITIONAL BRANCHES**

| Test                                                            | True | Opcode | False | Opcode |

|-----------------------------------------------------------------|------|--------|-------|--------|

| r>m                                                             | BGT  | 2E     | BLE   | 2F     |

| r≥m                                                             | BGE  | 2C     | BLT   | 2D     |

| r=m                                                             | BEQ  | 27     | BNE   | 26     |

| r≤m                                                             | BLE  | 2F     | BGT   | 2E     |

| r <m< th=""><th>BLT</th><th>2D</th><th>BGE</th><th>2C</th></m<> | BLT  | 2D     | BGE   | 2C     |

### **UNSIGNED CONDITIONAL BRANCHES**

| Test                                                                    | True    | Opcode | False   | Opcode |

|-------------------------------------------------------------------------|---------|--------|---------|--------|

| r>m                                                                     | ВНІ     | 22     | BLS     | 23     |

| r≥m                                                                     | BHS/BCC | 24     | BLO/BCS | 25     |

| r = m                                                                   | BEQ     | 27     | BNE     | 26     |

| r≤m                                                                     | BLS     | 23     | BHI     | 22     |

| r <m< th=""><th>BLO/BCS</th><th>25</th><th>BHS/BCC</th><th>24</th></m<> | BLO/BCS | 25     | BHS/BCC | 24     |

### **BIT MANIPULATION BRANCHES**

BRCLR — Branch if all selected bits are clear (opcode) (operand addr) (mask) (rel offset).

M•mm = 0? M = operand in memory; mm — mask

BRSET — Branch if all selected bits are set (opcode) (operand addr) (mask) (rel offset).

$(\overline{M})$ •mm = 0? M = operand in memory; mm mask

# Opcode vs instruction Cross Reference

|                      | - Posta to motifaction cross freference |                                           |                          |                  |  |

|----------------------|-----------------------------------------|-------------------------------------------|--------------------------|------------------|--|

| Opcode               | Operands                                | Instruction                               | ADDR<br>Mode             | Cycle            |  |

| 00<br>01<br>02<br>03 |                                         | TEST<br>NOP<br>IDIV<br>FDIV               | INH<br>INH<br>INH<br>INH |                  |  |

| 04<br>05<br>06<br>07 |                                         | LSRD<br>ASLD/LSLD<br>TAP<br>TPA           | INH<br>INH<br>INH<br>INH | 3<br>3<br>2<br>2 |  |

| 08<br>09<br>0A<br>0B |                                         | INX<br>DEX<br>CLV<br>SEV                  | INH<br>INH<br>INH<br>INH | 3<br>3<br>2<br>2 |  |

| 0C<br>0D<br>0E<br>0F |                                         | CLC<br>SEC<br>CLI<br>SEI                  | INH<br>INH<br>INH<br>INH | 2<br>2<br>2<br>2 |  |

| 10<br>11<br>12       | dd mm rr                                | SBA<br>CBA<br>BRSET (opr)<br>(msk)        | INH<br>INH<br>DIR        | 2<br>2<br>6      |  |

| 13                   | dd mm rr                                | (rel)<br>BRCLR (opr)<br>(msk)<br>(rel)    | DIR                      | 6                |  |

| 14                   | dd mm                                   | BSET (opr)                                | DIR                      | 6                |  |

| 15                   | dd mm                                   | (msk)<br>BCLR (opr)<br>(msk)              | DIR                      | 6                |  |

| 16<br>17             |                                         | TAB<br>TBA                                | INH<br>INH               | 2<br>2           |  |

| 18<br>19<br>1A       |                                         | (Page 2 Switch)<br>DAA<br>(Page 3 Switch) | INH                      | 2                |  |

| 1B                   |                                         | ABA                                       | INH                      | 2                |  |

| 1C                   | ff mm                                   | BSET (opr)<br>(msk)                       | IND,X                    | 7                |  |

| 1D                   | ff mm                                   | BCLR (opr)                                | IND,X                    | 7                |  |

| 1E                   | ff mm rr                                | (msk)<br>BRSET (opr)<br>(msk)             | IND,X                    | 7                |  |

| 1F                   | ff mm rr                                | (rel)<br>BRCLR (opr)<br>(msk)<br>(rel)    | IND,X                    | 7                |  |

# Opcode vs instruction Cross Reference

| Opcode               | Operands       | Instruction                                      | ADDR<br>Mode             | Cycle            |

|----------------------|----------------|--------------------------------------------------|--------------------------|------------------|

| 20                   | rr             | BRA (rel)                                        | REL                      | 3                |

| 21                   | rr             | BRN (rel)                                        | REL                      | 3                |

| 22                   | rr             | BHI (rel)                                        | REL                      | 3                |

| 23                   | rr             | BLS (rel)                                        | REL                      | 3                |

| 24                   | rr             | BCC/BHS (rel)                                    | REL                      | 3                |

| 25                   | rr             | BCS/BLO (rel)                                    | REL                      | 3                |

| 26                   | rr             | BNE (rel)                                        | REL                      | 3                |

| 27                   | rr             | BEQ (rel)                                        | REL                      | 3                |

| 28                   | rr             | BVC (rel)                                        | REL                      | 3                |

| 29                   | rr             | BVS (rel)                                        | REL                      | 3                |

| 2A                   | rr             | BPL (rel)                                        | REL                      | 3                |

| 2B                   | rr             | BMI (rel)                                        | REL                      | 3                |

| 2C<br>2D<br>2E<br>2F | rr<br>rr<br>rr | BGE (rel)<br>BLT (rel)<br>BGT (rel)<br>BLE (rel) | REL<br>REL<br>REL<br>REL | 3<br>3<br>3<br>3 |

| 30                   |                | TSX                                              | INH                      | 3                |

| 31                   |                | INS                                              | INH                      | 3                |

| 32                   |                | PULA                                             | INH                      | 4                |

| 33                   |                | PULB                                             | INH                      | 4                |

| 34                   |                | DES                                              | INH                      | 3                |

| 35                   |                | TXS                                              | INH                      | 3                |

| 36                   |                | PSHA                                             | INH                      | 3                |

| 37                   |                | PSHB                                             | INH                      | 3                |

| 38                   |                | PULX                                             | INH                      | 5                |

| 39                   |                | RTS                                              | INH                      | 5                |

| 3A                   |                | ABX                                              | INH                      | 3                |

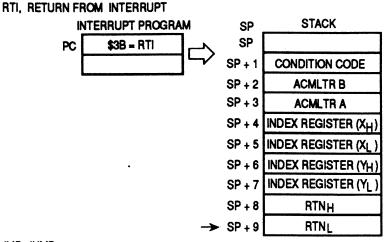

| 3B                   |                | RTI                                              | INH                      | 12               |

| 3C                   |                | PSHX                                             | INH                      | 4                |

| 3D                   |                | MUL                                              | INH                      | 10               |

| 3E                   |                | WAI                                              | INH                      | 14               |

| 3F                   |                | SWI                                              | INH                      | 14               |

| 40                   |                | NEGA                                             | INH                      | 2                |

| 43                   |                | COMA                                             | INH                      | 2                |

| 44                   |                | LSRA                                             | INH                      | 2                |

| 46                   |                | RORA                                             | INH                      | 2                |

| 47                   |                | ASRA                                             | INH                      | 2                |

| 48                   |                | ASLA/LSLA                                        | INH                      | 2                |

| 49                   |                | ROLA                                             | INH                      | 2                |

| 4A                   |                | DECA                                             | INH                      | 2                |

| 4C                   |                | INCA                                             | INH                      | 2                |

| 4D                   |                | TSTA                                             | INH                      | 2                |

| 4F                   |                | CLRA                                             | INH                      | 2                |

| 50                   |                | NEGB                                             | INH                      | 2                |

# Freescale Semiconductor, Inc. Opcode vs Instruction Cross Reference

| Opcode               | Operands             | Instruction                                          | ADDR<br>Mode                 | Cycle            |

|----------------------|----------------------|------------------------------------------------------|------------------------------|------------------|

| 53                   |                      | COMB                                                 | INH                          | 2                |

| 54                   |                      | LSRB                                                 | INH                          | 2                |

| 56                   |                      | RORB                                                 | INH                          | 2                |

| 57                   |                      | ASRB/ASLB                                            | INH                          | 2                |

| 58                   |                      | LSLB                                                 | 17 H                         | 2                |

| 59                   |                      | ROLB                                                 | 17 H                         | 2                |

| 5A                   |                      | DECB                                                 | 17 H                         | 2                |

| 5C                   |                      | iNCB                                                 | 17 H                         | 2                |

| 5D<br>5F<br>60<br>63 | ff<br>ff             | TSTB<br>CLRB<br>NEG (opr)<br>COM (opr)               | INH<br>INH<br>IND,X<br>IND,X | 2<br>2<br>6<br>6 |

| 64                   | ff                   | LSR (opr)                                            | IND,X                        | 6666             |

| 66                   | ff                   | ROR (opr)                                            | IND,X                        |                  |

| 67                   | ff                   | ASR (opr)                                            | IND,X                        |                  |

| 68                   | ff                   | ASL/LSL (opr)                                        | IND,X                        |                  |

| 69                   | ff                   | ROL (opr)                                            | IND,X                        | 6666             |

| 6A                   | ff                   | DEC (opr)                                            | IND,X                        |                  |

| 6C                   | ff                   | INC (opr)                                            | IND,X                        |                  |

| 6D                   | ff                   | TST (opr)                                            | IND,X                        |                  |

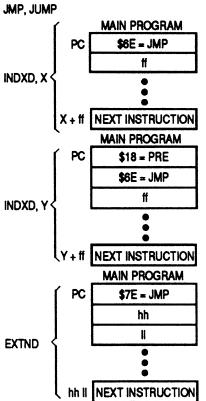

| 6E                   | ff                   | JMP (opr)                                            | IND,X                        | 3                |

| 6F                   | ff                   | CLR (opr)                                            | IND,X                        | 6                |

| 70                   | hh II                | NEG (opr)                                            | EXT                          | 6                |

| 73                   | hh II                | COM (opr)                                            | EXT                          | 6                |

| 74                   | hh II                | LSR (opr)                                            | EXT                          | 6666             |

| 76                   | hh II                | ROR (opr)                                            | EXT                          |                  |

| 77                   | hh II                | ASR (opr)                                            | EXT                          |                  |

| 78                   | hh II                | ASL/LSL (opr)                                        | EXT                          |                  |

| 79                   | hh II                | ROL (opr)                                            | EXT                          | 6666             |

| 7A                   | hh II                | DEC (opr)                                            | EXT                          |                  |

| 7C                   | hh II                | INC (opr)                                            | EXT                          |                  |

| 7D                   | hh II                | TST (opr)                                            | EXT                          |                  |

| 7E                   | hh II                | JMP (opr)                                            | EXT                          | 3                |

| 7F                   | hh II                | CLR (opr)                                            | EXT                          | 6                |

| 80                   | ii                   | SUBA (opr)                                           | IMM                          | 2                |

| 81                   | ii                   | CMPA (opr)                                           | IMM                          | 2                |

| 82                   | ii                   | SBCA (opr)                                           | IMM                          | 2                |

| 83                   | jj kk                | SUBD (opr)                                           | IMM                          | 4                |

| 84                   | ii                   | ANDA (opr)                                           | IMM                          | 2                |

| 85                   | ii                   | BITA (opr)                                           | IMM                          | 2                |

| 86<br>88<br>89<br>8A | ii<br>ii<br>ii<br>ii | LDAA (opr)<br>EORA (opr)<br>ADCA (opr)<br>ORAA (opr) | IMM<br>IMM<br>IMM            | 2<br>2<br>2<br>2 |

# Freescale Semiconductor, Inc. Opcode vs Instruction Cross Reference

| Opcode               | Operands       | Instruction                                    | ADDR<br>Mode             | Cycle            |

|----------------------|----------------|------------------------------------------------|--------------------------|------------------|

| 8B                   | ii             | ADDA (opr)                                     | IMM                      | 2                |

| 8C                   | jj kk          | CPX (opr)                                      | IMM                      | 4                |

| 8D                   | rr             | BSR (rel)                                      | REL                      | 6                |

| 8E                   | jj kk          | LDS (opr)                                      | IMM                      | 3                |

| 8F<br>90<br>91<br>92 | dd<br>dd<br>dd | XGDX<br>SUBA (opr)<br>CMPA (opr)<br>SBCA (opr) | INH<br>DIR<br>DIR<br>DIR | 3<br>3<br>3<br>3 |

| 93                   | dd             | SUBD (opr)                                     | DIR                      | 5                |

| 94                   | dd             | ANDA (opr)                                     | DIR                      | 3                |

| 95                   | dd             | BITA (opr)                                     | DIR                      | 3                |

| 96                   | dd             | LDAA (opr)                                     | DIR                      | 3                |

| 97                   | dd             | STAA (opr)                                     | DIR                      | 3                |

| 98                   | dd             | EORA (opr)                                     | DIR                      | 3                |

| 99                   | dd             | ADCA (opr)                                     | DIR                      | 3                |

| 9A                   | dd             | ORAA (opr)                                     | DIR                      | 3                |

| 9B                   | dd             | ADDA (opr)                                     | DIR                      | 3                |

| 9C                   | dd             | CPX (opr)                                      | DIR                      | 5                |

| 9D                   | dd             | JSR (opr)                                      | DIR                      | 5                |

| 9E                   | dd             | LDS (opr)                                      | DIR                      | 4                |

| 9F                   | dd             | STS (opr)                                      | DIR                      | 4                |

| A0                   | ff             | SUBA (opr)                                     | IND,X                    | 4                |

| A1                   | ff             | CMPA (opr)                                     | IND,X                    | 4                |

| A2                   | ff             | SBCA (opr)                                     | IND,X                    | 4                |

| A3                   | ff             | SUBD (opr)                                     | IND,X                    | 6                |

| A4                   | ff             | ANDA (opr)                                     | IND,X                    | 4                |

| A5                   | ff             | BITA (opr)                                     | IND,X                    | 4                |

| A6                   | ff             | LDAA (opr)                                     | IND,X                    | 4                |

| A7                   | ff             | STAA (opr)                                     | IND,X                    | 4                |

| A8                   | ff             | EORA (opr)                                     | IND,X                    | 4                |

| A9                   | ff             | ADCA (opr)                                     | IND,X                    | 4                |

| AA                   | ff             | ORAA (opr)                                     | IND,X                    | 4                |

| AB                   | ff             | ADDA (opr)                                     | IND,X                    | 4                |

| AC                   | ff             | CPX (opr)                                      | IND,X                    | 6                |

| AD                   | ff             | JSR (opr)                                      | IND,X                    | 6                |

| AE                   | ff             | LDS (opr)                                      | IND,X                    | 5                |

| AF                   | ff             | STS (opr)                                      | IND,X                    | 5                |

| B0                   | hh II          | SUBA (opr)                                     | EXT                      | 4                |

| B1                   | hh II          | CMPA (opr)                                     | EXT                      | 4                |

| B2                   | hh II          | SBCA (opr)                                     | EXT                      | 4                |

| B3                   | hh II          | SUBD (opr)                                     | EXT                      | 6                |

| B4                   | hh II          | ANDA (opr)                                     | EXT                      | 4                |

| B5                   | hh II          | BITA (opr)                                     | EXT                      | 4                |

| B6                   | hh II          | LDAA (opr)                                     | EXT                      | 4                |

# Freescale Semiconductor, Inc. Opcode vs Instruction Cross Reference

| Opcode               | Operands             | Instruction                                          | ADDR<br>Mode      | Cycle            |

|----------------------|----------------------|------------------------------------------------------|-------------------|------------------|

| B7                   | hh II                | STAA (opr)                                           | EXT               | 4                |

| B8                   | hh II                | EORA (opr)                                           | EXT               | 4                |

| B9                   | hh II                | ADCA (opr)                                           | EXT               | 4                |

| BA                   | hh II                | ORAA (opr)                                           | EXT               | 4                |

| BB                   | hh II                | ADDA (opr)                                           | EXT               | 4                |

| BC                   | hh II                | CPX (opr)                                            | EXT               | 6                |

| BD                   | hh II                | JSR (opr)                                            | EXT               | 6                |

| BE                   | hh II                | LDS (opr)                                            | EXT               | 5                |

| BF                   | hh II                | STS (opr)                                            | EXT               | 5                |

| C0                   | ii                   | SUBB (opr)                                           | IMM               | 2                |

| C1                   | ii                   | CMPB (opr)                                           | IMM               | 2                |

| C2                   | ii                   | SBCB (opr)                                           | IMM               | 2                |

| C3                   | jj kk                | ADDD (opr)                                           | IMM               | 4                |

| C4                   | ii                   | ANDB (opr)                                           | IMM               | 2                |

| C5                   | ii                   | BITB (opr)                                           | IMM               | 2                |

| C6                   | ii                   | LDAB (opr)                                           | IMM               | 2                |

| C8<br>C9<br>CA<br>CB | ii<br>ii<br>ii<br>ii | EORB (opr)<br>ADCB (opr)<br>ORAB (opr)<br>ADDB (opr) | IMM<br>IMM<br>IMM | 2<br>2<br>2<br>2 |

| CC<br>CD<br>CE<br>CF | jj kk<br>jj kk       | LDD (opr)<br>(Page 4 Switch)<br>LDX (opr)<br>STOP    | IMM<br>IMM<br>INH | 3<br>3<br>2      |

| D0                   | dd                   | SUBB (opr)                                           | DIR               | 3                |

| D1                   | dd                   | CMPB (opr)                                           | DIR               | 3                |

| D2                   | dd                   | SBCB (opr)                                           | DIR               | 3                |

| D3                   | dd                   | ADDD (opr)                                           | DIR               | 5                |

| D4                   | dd                   | ANDB (opr)                                           | DIR               | 3                |

| D5                   | dd                   | BITB (opr)                                           | DIR               | 3                |

| D6                   | dd                   | LDAB (opr)                                           | DIR               | 3                |

| D7                   | dd                   | STAB (opr)                                           | DIR               | 3                |

| D8                   | dd                   | EORB (opr)                                           | DIR               | 3                |

| D9                   | dd                   | ADCB (opr)                                           | DIR               | 3                |

| DA                   | dd                   | ORAB (opr)                                           | DIR               | 3                |

| DB                   | dd                   | ADDB (opr)                                           | DIR               | 3                |

| DC                   | dd                   | LDD (opr)                                            | DIR               | 4                |

| DD                   | dd                   | STD (opr)                                            | DIR               | 4                |

| DE                   | dd                   | LDX (opr)                                            | DIR               | 4                |

| DF                   | dd                   | STX (opr)                                            | DIR               | 4                |

| E0                   | ff                   | SUBB (opr)                                           | IND,X             | 4                |

| E1                   | ff                   | CMPB (opr)                                           | IND,X             | 4                |

| E2                   | ff                   | SBCB (opr)                                           | IND,X             | 4                |

| E3                   | ff                   | ADDD (opr)                                           | IND,X             | 6                |

# Freescale Semiconductor, Inc. Opcode vs Instruction Cross Reference

| Opcode                           | Operands                         | Instruction                                          | ADDR<br>Mode                     | Cycle            |

|----------------------------------|----------------------------------|------------------------------------------------------|----------------------------------|------------------|

| E4<br>E5<br>E6<br>E7             | ff<br>ff<br>ff                   | ANDB (opr)<br>BITB (opr)<br>LDAB (opr)<br>STAB (opr) | IND,X<br>IND,X<br>IND,X<br>IND,X | 4<br>4<br>4      |

| E8<br>E9<br>EA<br>EB             | ff<br>ff<br>ff                   | EORB (opr)<br>ADCB (opr)<br>ORAB (opr)<br>ADDB (opr) | IND,X<br>IND,X<br>IND,X<br>IND,X | 4<br>4<br>4<br>4 |

| EC<br>ED<br>EE<br>EF             | ff<br>ff<br>ff<br>ff             | LDD (opr)<br>STD (opr)<br>LDX (opr)<br>STX (opr)     | IND,X<br>IND,X<br>IND,X<br>IND,X | 5 5 5 5          |

| F0<br>F1<br>F2<br>F3             | hh II<br>hh II<br>hh II<br>hh II | SUBB (opr)<br>CMPB (opr)<br>SBCB (opr)<br>ADDD (opr) | EXT<br>EXT<br>EXT<br>EXT         | 4<br>4<br>6      |

| F4<br>F5<br>F6<br>F7             | hh II<br>hh II<br>hh II<br>hh II | ANDB (opr)<br>BITB (opr)<br>LDAB (opr)<br>STAB (opr) | EXT<br>EXT<br>EXT<br>EXT         | 4<br>4<br>4      |

| F8<br>F9<br>FA<br>FB             | hh II<br>hh II<br>hh II<br>hh II | EORB (opr)<br>ADCB (opr)<br>ORAB (opr)<br>ADDB (opr) | EXT<br>EXT<br>EXT<br>EXT         | 4<br>4<br>4<br>• |

| FC<br>FD<br>FE<br>FF             | hh II<br>hh II<br>hh II<br>hh II | LDD (opr)<br>STD (opr)<br>LDX (opr)<br>STX(opr)      | EXT<br>EXT<br>EXT<br>EXT         | 5 5 5 5          |

| 18 08<br>18 09<br>18 1C          | ff mm                            | INY<br>DEY<br>BSET (opr)<br>(msk)<br>BCLR (opr)      | INH<br>INH<br>IND,Y<br>IND,Y     | 4<br>4<br>8<br>8 |

| 18 1E                            | ff mm rr                         | (msk) BRSET (opr) (msk)                              | IND,Y                            | 8                |

| 18 1F                            | ff mm rr                         | (rel)<br>BRCLR (opr)<br>(msk)<br>(rel)               | IND,Y                            | 8                |

| 18 30<br>18 35<br>18 38<br>18 3A |                                  | TSY<br>TYS<br>PULY<br>ABY                            | INH<br>INH<br>INH<br>INH         | 4<br>4<br>6<br>4 |

## Opcode vs Instruction Cross Reference

| Opcode                           | Operands             | Instruction                                          | ADDR<br>Mode                     | Cycle            |

|----------------------------------|----------------------|------------------------------------------------------|----------------------------------|------------------|

| 18 3C<br>18 60<br>18 63<br>18 64 | ff<br>ff<br>ff       | PSHY<br>NEG (opr)<br>COM (opr)<br>LSR (opr)          | INH<br>IND,Y<br>IND,Y<br>IND,Y   | 5<br>7<br>7<br>7 |

| 18 66                            | ff                   | ROR (opr)                                            | IND,Y                            | 7                |

| 18 67                            | ff                   | ASR (opr)                                            | IND,Y                            | 7                |

| 18 68                            | ff                   | ASL/LSL (opr)                                        | IND,Y                            | 7                |

| 18 69                            | ff                   | ROL (opr)                                            | IND,Y                            | 7                |

| 18 6A                            | ff                   | DEC (opr)                                            | IND,Y                            | 7                |

| 18 6C                            | ff                   | INC (opr)                                            | IND,Y                            | 7                |

| 18 6D                            | ff                   | TST (opr)                                            | IND,Y                            | 7                |

| 18 6E                            | ff                   | JMP (opr)                                            | IND,Y                            | 4                |

| 18 6F<br>18 8C<br>18 8F<br>18 9C | ff<br>jj kk<br>dd    | CLR (opr)<br>CPY (opr)<br>XGDY<br>CPY (opr)          | IND,Y<br>IMM<br>INH<br>DIR       | 7<br>5<br>4<br>6 |

| 18 A0<br>18 A1<br>18 A2<br>18 A3 | ff<br>ff<br>ff<br>ff | SUBA (opr)<br>CMPA (opr)<br>SBCA (opr)<br>SUBD (opr) | IND,Y<br>IND,Y<br>IND,Y<br>IND,Y | 5<br>5<br>7      |

| 18 A4                            | ff                   | ANDA (opr)                                           | IND,Y                            | 5 5 5 5          |

| 18 A5                            | ff                   | BITA (opr)                                           | IND,Y                            |                  |

| 18 A6                            | ff                   | LDAA (opr)                                           | IND,Y                            |                  |

| 18 A7                            | ff                   | STAA (opr)                                           | IND,Y                            |                  |

| 18 A8                            | ff                   | EORA (opr)                                           | IND,Y                            | 5 5 5 5          |

| 18 A9                            | ff                   | ADCA (opr)                                           | IND,Y                            |                  |

| 18 AA                            | ff                   | ORAA (opr)                                           | IND,Y                            |                  |

| 18 AB                            | ff                   | ADDA (opr)                                           | IND,Y                            |                  |

| 18 AC<br>18 AD<br>18 AE<br>18 AF | ff<br>ff<br>ff       | CPY (opr)<br>JSR (opr)<br>LDS (opr)<br>STS (opr)     | IND,Y<br>IND,Y<br>IND,Y<br>IND,Y | 7<br>7<br>6<br>6 |

| 18 BC                            | hh II                | CPY (opr)                                            | EXT                              | 7                |

| 18 CE                            | jj kk                | LDY (opr)                                            | IMM                              | 4                |

| 18 DE                            | dd                   | LDY (opr)                                            | DIR                              | 5                |

| 18 DF                            | dd                   | STY (opr)                                            | DIR                              | 5                |

| 18 E0                            | ff                   | SUBB (opr)                                           | IND,Y                            | 5                |

| 18 E1                            | ff                   | CMPB (opr)                                           | IND,Y                            | 5                |

| 18 E2                            | ff                   | SBCB (opr)                                           | IND,Y                            | 5                |

| 18 E3                            | ff                   | ADDD (opr)                                           | IND,Y                            | 5                |

| 18 E4                            | ff                   | ANDB (opr)                                           | IND,Y                            | 5                |

| 18 E5                            | ff                   | BITB (opr)                                           | IND,Y                            | 5                |

| 18 E6                            | ff                   | LDAB (opr)                                           | IND,Y                            | 5                |

| 18 E7                            | ff                   | STAB (opr)                                           | IND,Y                            | 5                |

# Opcode vs Instruction Cross Reference

| Opcode                           | Operands             | Instruction                                      | ADDR<br>Mode                     | Cycle       |

|----------------------------------|----------------------|--------------------------------------------------|----------------------------------|-------------|

| 18 E8                            | ff                   | EORB (opr)                                       | IND,Y                            | 5           |

| 18 E9                            | ff                   | ADCB (opr)                                       | IND,Y                            | 5           |

| 18 EA                            | ff                   | ORAB (opr)                                       | IND,Y                            | 5           |

| 18 EB                            | ff                   | ADDB (opr)                                       | IND,Y                            | 5           |

| 18 EC<br>18 ED<br>18 EE<br>18 EF | ff<br>ff<br>ff<br>ff | LDD (opr)<br>STD (opr)<br>LDY (opr)<br>STY (opr) | IND,Y<br>IND,Y<br>IND,Y<br>IND,Y | 6<br>6<br>6 |

| 18 FE                            | hh II                | LDY (opr)                                        | EXT                              | 6           |

| 18 FF                            | hh II                | STY (opr)                                        | EXT                              | 6           |

| 1A 83                            | jj kk                | CPD (opr)                                        | IMM                              | 5           |

| 1A 93                            | dd                   | CPD (opr)                                        | DIR                              | 6           |

| 1A A3                            | ff                   | CPD (opr)                                        | IND,X                            | 7           |

| 1A AC                            | ff                   | CPY (opr)                                        | IND,X                            | 7           |

| 1A B3                            | hh II                | CPD (opr)                                        | EXT                              | 7           |

| 1A EE                            | ff                   | LDY (opr)                                        | IND,X                            | 6           |

| 1A EF                            | ff                   | STY (opr)                                        | IND,X                            | 6           |

| CD A3                            | ff                   | CPD (opr)                                        | IND,Y                            | 7           |

| CD AC                            | ff                   | CPX (opr)                                        | IND,Y                            | 7           |

| CD EE                            | ff                   | LDX (opr)                                        | IND,Y                            | 6           |

| CD EF                            | ff                   | STX (opr)                                        | IND,Y                            | 6           |

### NOTES:

Operands:

11

dd = 8-bit direct address \$0000-\$00FF. (High byte as-

sumed to be \$00).

ff = 8-bit positive offset \$00 (0) to \$FF (255) added to

index.

hh = High-order byte of 16-bit extended address

ii = One byte of immediate data.

jj = High-order byte of 16-bit immediate data.

kk = Low-order byte of 16-bit immediate data.

= Low-order by te of 16-bit extended address.

mm = 8-bit mask (set bits to be effective).

rr = Signed relative offset \$80 ( 128) to \$7F ( 127).

Offset relative to the address following the ma-

chine code offset byte.

INSTRUCTIONS, ADDRESSING MODES, AND EXECUTION TIMES

| Source<br>Form(s) | Operation           | Boolean        | Addressing<br>Mode for | Mach<br>(Hex | Machine Coding<br>(Hexadecimal) | ytes | Acjes | Condition Codes                       |

|-------------------|---------------------|----------------|------------------------|--------------|---------------------------------|------|-------|---------------------------------------|

|                   |                     |                | Operand                | Opcode       | Operand(s)                      | 8    | ၁     | SXHINZVC                              |

| ABA               | Add Accumulators    | A+B D          | HNI                    | 18           |                                 | -    | 2     | 44                                    |

| ABX               | Add B to X          | IX + 00:B ♦ IX | INI                    | 3A           |                                 | -    | 3     |                                       |

| ABY               | Add B to Y          | IY + 00:B ♦ IY | Ī                      | 18 3A        |                                 | 2    | 4     |                                       |

| ADCA (opr)        | Add with Carry to A | A+M+C.AA       | A IMM                  | 88           | :=                              | 2    | 2     | 41<br>41<br>41<br>                    |

|                   |                     |                | A DIR                  | 66           | pp                              | 2    | က     | • • • • • • • • • • • • • • • • • • • |

|                   |                     |                | A EXT                  | B3           | <del>-</del>                    | က    | 4     |                                       |

|                   |                     |                | A IND,X                | A9           | Ħ                               | 2    | 4     | GI                                    |

|                   |                     |                | A IND,Y                | 18 A9        | #                               | က    | ည     | <del>. O .</del>                      |

| ADCB (opr)        | Add with Carry to B | B+M+C → B      | B IMM                  | သ            | :=                              | 2    | 2     | 41<br>41<br>41<br>41                  |

|                   |                     |                | B DIR                  | 60           | pp                              | 2    | က     | )<br>)<br>)                           |

|                   |                     |                | B EXT                  | 6            | н<br>=                          | က    | 4     |                                       |

|                   |                     |                |                        | 63           | Ħ                               | 2    | 4     |                                       |

|                   |                     |                | B IND,Y                | 18 E9        | · ·                             | က    | 2     |                                       |

|                   |                     |                |                        |              |                                 | 1    |       |                                       |

|                                 | F          | eescale S                           | emicondu                            | ctor, Inc.                          |

|---------------------------------|------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Ş                               | >          | 4+                                  | **                                  | 44                                  |

| Condition Codes                 |            | <b>*</b> *                          | <b>**</b>                           | <b>4+</b>                           |