### AN11878 TEA19362T GreenChip SMPS control IC Rev. 1 – 5 October 2017

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | TEA19362T, Discontinuous Conduction Mode (DCM) flyback converter, high efficiency, burst mode operation, Fixed Frequency DCM (FF DCM) operation, low Common-Mode Noise (CMN), low power consumption, multiple-output voltage applications, touchscreen applications                                                                                                                                                                                                                                                                                 |

| Abstract    | The TEA19362T is a high-featured low-cost DCM flyback converter controller.<br>It switches at a fixed frequency over the whole power range, including burst<br>mode. Fixed-frequency operation minimizes CMN and optimizes spectral<br>purity toward (mobile) touchscreens.<br>The TEA19362T is designed to support multiple-output-voltage applications<br>like USB PD (Type C) power supplies. Typical applications include<br>applications with touchscreens, like notebooks and tablet adapters, fast<br>charging and direct charging adapters. |

| Table 1. Revision history |          |             |  |  |

|---------------------------|----------|-------------|--|--|

| Rev                       | Date     | Description |  |  |

| v.1                       | 20171005 | first issue |  |  |

### **1** Introduction

This application note describes the implementation of TEA19362T functions in practical applications. Information is provided on a practical converter design.

The TEA19362T only operates in Fixed Frequency (FF) DCM mode. It is intended for mobile applications using touch screens requiring high spectral purity from the supply to prevent disturbance of the touchscreen operation.

Additional family members are TEA19361T, TEA19363T, TEA19363LT, and TEA1938T.

The TEA19361T operates in DCM mode and QR mode with valley switching for optimal efficiency. The burst mode is optimized for minimal audible noise. It is suited for applications using touch screens with standard Common Mode Noise requirements.

The TEA19363 operation can be compared with the TEA19361T operation, but it also includes active X-capacitor discharge. Furthermore, the TEA19363 comes in a latched (TEA19363LT) and a non-latched version (TEA19363T). When an OVP or OTP exception occurs, the latched version halts operation. The non-latched version initially halts and then resumes operation via a safe restart strategy. The higher Common Mode Noise due to the X-capacitor discharge function makes it less suitable for applications with touchscreen.

The TEA1938T is comparable to the TEA19361T. It contains a different burst mode, which is optimized for minimum ripple. The HV pin and VCCH pin have an ESD rating of 2 kV (for the TEA1936x, the level is 1 kV). It is suited for applications using touchscreens with standard Common Mode Noise requirements.

Each section can be read as a standalone description with few cross-references to other parts of the application note or the data sheet. Unless stated otherwise, typical values are given to enhance the readability.

### 2 Features and applications

#### 2.1 General features

- Switched-Mode Power Supply (SMPS) controller IC supporting smart-charging applications and multiple-output-voltage applications

- Wide output range (5 V to 20 V in Constant Voltage (CV) mode, 3 V to 20 V in Constant Current (CC) mode, and 3 V to 6.5 V for direct charging)

- FF DCM mode operation at all power levels, including burst mode. Suited for mobile charger applications that require low CMN and high spectral purity (touchscreens)

- Small SO10 package

- Adaptive dual supply for highest efficiency over the entire output voltage range

- Integrated high-voltage start-up

- Continuous VCC regulation during start-up and protection via the HV pin, allowing minimum values for the buffer capacitors that are connected to the VCCL and VCCH pins

- Reduced optocoupler current enabling low no-load power (20 mW at 5 V output)

- · Fast transient response from zero to full load

- Minimal output voltage ripple in all operating modes

- Integrated soft start

#### 2.2 Green features

Enables high efficiency operation over a wide power range via:

- Low supply current during normal operation (0.6 mA without load)

- Low supply current during non-switching state in burst mode (0.2 mA)

- Demagnetization switching to minimize switching losses

- DCM controller can be used in combination with NXP Semiconductors Synchronous Rectification (SR) controllers for optimal efficiency performance

#### 2.3 Protection features

- Mains voltage compensated OverPower Protection (OPP)

- OverTemperature Protection (OTP)

- Integrated overpower timeout

- · Integrated restart timer for system fault conditions

- Continuous mode protection using demagnetization detection

- Accurate OverVoltage Protection (OVP)

- General-purpose input for safe restart protection; used with system OverTemperature Protection (OTP)

- Driver maximum on-time protection

- Brownin and brownout protection

- The TEA19362T OVP and OTP protections are safe restart protections

#### 2.4 Applications

- · Supports multiple-output-voltage applications

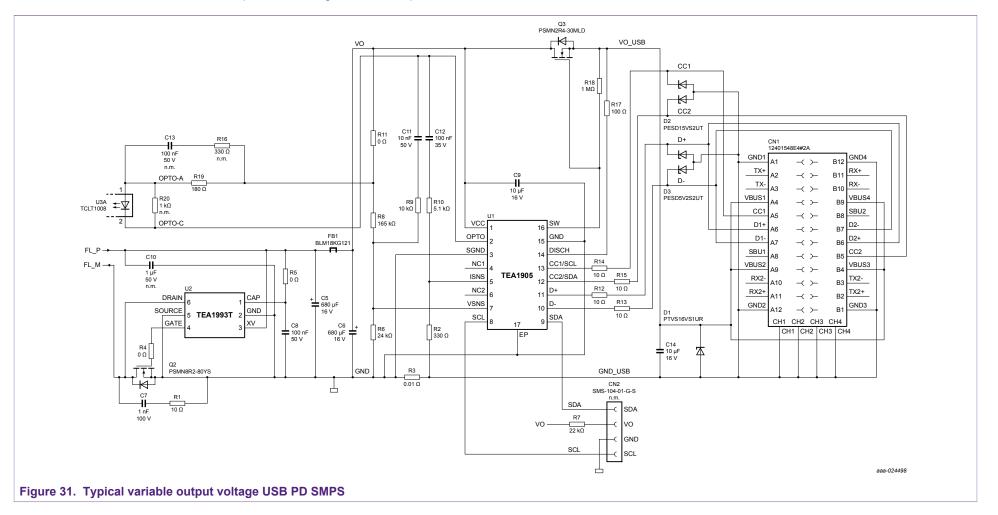

- Easy implementation of a USB-PD (type C) application together with the NXP Semiconductors TEA1903 or TEA1905 secondary side controllers

- Allows easy implementation of a direct charge application using Constant Voltage (CV) and Constant Current (CC) mode

- Touchscreen applications, like mobile phones, tablets, netbooks, and notebook adapters and chargers.

### **3** Functional description

This section describes the functional behavior of the TEA19362T IC on the primary side of an SMPS application. The TEA19362T can operate with various implementations of the secondary side of the SMPS:

- Single fixed voltage SMPS, e.g. a single 19.5 V output voltage (for notebooks)

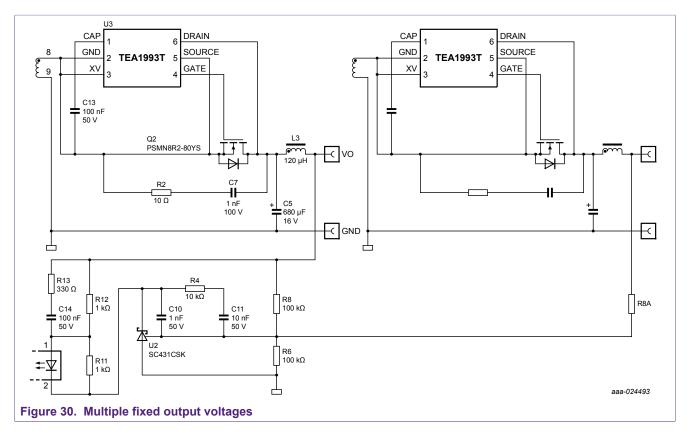

- Multiple fixed voltages SMPS, e.g. simultaneous 12 V and 5 V output voltages

- Single variable voltages SMPS, e.g. 5 V, 9 V, 12 V, or 19.5 V switchable or autoswitchable output voltage (for USB-PD) that typically uses a TEA1903 or TEA1905 secondary controller

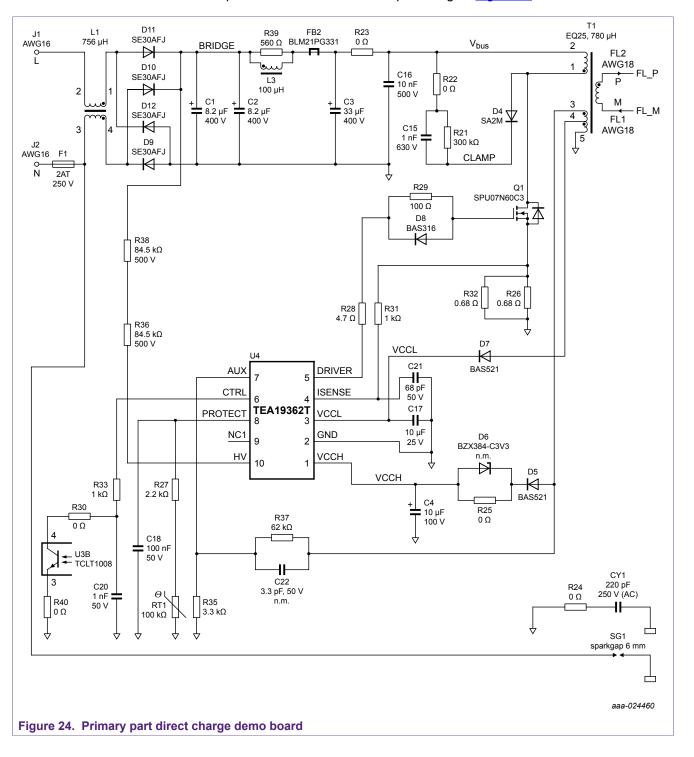

#### 3.1 Application - primary side

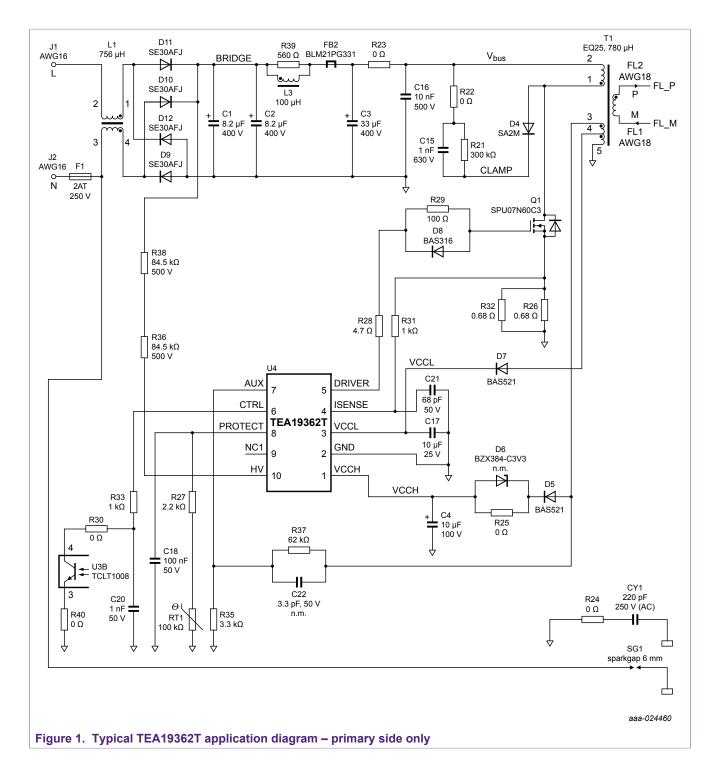

The general behavior of the primary side of the applications that use the TEA19362T is explained using the elementary circuit diagram shown in <u>Figure 1</u>.

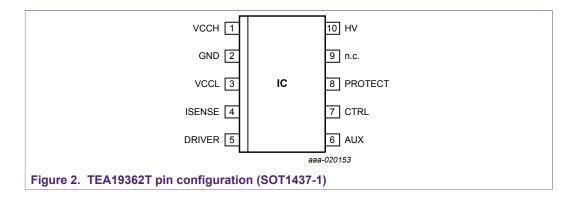

### 3.2 Pinning

### 3.2.1 Pin configuration

### 3.2.2 Pin descriptions

| Pin | Pin name | Functional description summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCCH     | <ul> <li>High IC supply voltage input</li> <li>When used, the VCCH pin is supplied from an auxiliary winding of the flyback transformer with a higher voltage than the auxiliary winding uses for the VCCL pin.</li> <li>When the voltage on pin VCCL is lower than 12.5 V, the (higher) voltage on the VCCH pin provides the supply current via an internal regulator to the VCCL pin. It makes the TEA19362T operate on the VCCH voltage.</li> <li>When the voltage on pin VCCL exceeds 12.5 V, the internal regulator between VCCH and VCCL is switched off. The supply current is taken from the VCCL voltage The combination of the VCCH and the VCCL pins ensures that for the supply the lowest voltage exceeding 12.5 V is selected for the IC supply. It enables building supplies with a wide output voltage range without supplying the IC from an excessively high voltage. The latter causes unnecessary power loss.</li> </ul>                                                                                                                                                                                                                                                          |

| 2   | GND      | Ground connection; reference for other pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3   | VCCL     | <ul> <li>Low IC supply voltage input and source for the internal HV start-up output<br/>All internal circuits, except the high-voltage circuit, are supplied from this pin.</li> <li>The buffer capacitor on the VCCL pin can be charged in several ways:</li> <li>Internal High-Voltage (HV) start-up source (start-up and protection). The<br/>capacitance on the VCCH pin is also charged via an internal diode between the<br/>VCCH and VCCL pins. It can be used as energy reservoir during start-up before<br/>the auxiliary supply takes over.</li> <li>Auxiliary winding from the flyback transformer (when switching)</li> <li>External DC supply</li> <li>When the voltage on the VCCL pin reaches 14.9 V, IC operation is enabled. In burst<br/>mode, when the voltage on the VCCL drops to below 11 V, additional switching<br/>cycles are generated. The switching cycles prevent that the VCCL voltage drops<br/>to below the stop operation level. This voltage drop can occur when no energy is<br/>required on the secondary side for a prolonged time after a load step from maximum<br/>to no load. When the voltage on the VCCL pin drops to below 9.9 V, the IC halts</li> </ul> |

| Pin | Pin name | Functional description summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | ISENSE   | <ul> <li>Current sense input</li> <li>This pin senses the primary current through the MOSFET switch via an external resistor.</li> <li>Soft start <ul> <li>A soft-start procedure is used to limit stress and audible noise during start-up. The l<sub>pk</sub> level, measured over the sense resistor, is gradually increased to the regulated level in 15 steps. The soft-start time constant is 4 ms.</li> <li>Burst mode</li> <li>In this mode, the peak current is kept constant. When a fixed level of 145 mV is reached on the ISENSE pin, the drive switches off. Controlling the number of strokes per burst cycle regulates the output voltage and output power. The switching frequency in the burst cycle is fixed. It is the same as in DCM mode.</li> <li>DCM mode</li> <li>In this mode, the switching frequency is kept constant. The increase or decrease of the peak current regulates the output voltage and output power. The voltage level for switch-off is regulated from 145 mV upward to 510 mV</li> <li>Leading-edge blanking</li> <li>During the first 325 ns of each switching cycle, the ISENSE input is internally blanked. The blanking of the ISENSE input prevents that the spike caused by parasitic capacitance triggers the peak current comparator prematurely.</li> <li>Propagation delay</li> <li>There is a delay between the moment the ISENSE comparator is triggered and the MOSFET is switched off. During this time, the primary current continues to increase. How much it increases, depends on the dl/dt slope, and so, on the mains voltage.</li> <li>Overpower protection counter</li> <li>When the voltage on the ISENSE pin exceeds the overpower protection level (510 mV), the overpower counter is started. When the overpower timer reaches 200 ms (40 ms during start-up), a safe restart is initiated.</li> <li>Overpower compensation for mains voltage by AUX sensing current</li> <li>To compensate the output power level for dependency on the input voltage, an overpower compensation circuit regulates protection level based on the input voltage enot the AUX pin.</li></ul></li></ul> |

| 5   | DRIVER   | MOSFET gate driver output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin | Pin name | Functional description summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | AUX      | <ul> <li>Auxiliary winding input</li> <li>A resistor divider on the AUX pin applies the voltage from an auxiliary winding of the flyback transformer. The voltage on this pin is used for three functions in three different time slots:</li> <li>Demagnetization detection When the AUX voltage drops to below 40 mV, demagnetization is detected. Only when demagnetization is detected, the driver can be switched on to start the next power conversion cycle. So, switch-on is only allowed in the lower half of the ringing. Depending on the operating condition, the MOSFET switches on the first lower half of the ringing or in one of the lower halfs of the subsequent ringing cycles.</li> <li>Input voltage sensing for OPP compensation When the external MOSFET is switched on, the voltage at the auxiliary winding reflects the input voltage. During this period, the AUX pin is clamped to -0.7 V. The measured input current is used to calculate the maximum allowed voltage on the ISENSE pin. Changing the value of the series resistor between the auxiliary winding and the AUX pin adjusts the measured current.</li> <li>Output voltage sensing for OVP The resistor for input voltage sensing and a resistor from the AUX pin to ground make up a voltage divider. During secondary stroke, the divider voltage reflects the output voltage.</li></ul> |

| 7   | CTRL     | Control input<br>In DCM, the control current flowing out of the CTRL pin is regulated to an 80 $\mu$ A fixed<br>value for all modes. The regulation of the control current is achieved by generating<br>an internal offset which regulates the power level via the internal control curve.<br>In burst mode, the control current level varies between 100 $\mu$ A and 200 $\mu$ A.<br>The internal voltage of the CTRL pin is 3 V with a 1.5 k $\Omega$ series resistance to the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8   | PROTECT  | Protection<br>When the voltage level on the PROTECT pin drops to below 0.5 V, a safe restart is<br>initiated after 2 ms to 4 ms.<br>When the pin voltage is lower than 1.45 V, an internal current source delivers -74 μA<br>out of the pin. When the pin voltage reaches 1.45 V, the internal current source is<br>automatically pinched off. Connecting a suitable NTC from the PROTECT pin to GND<br>can realize an external OTP for the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | n.c.     | Not connected<br>This pin has no internal connection. It is used as high-voltage spacer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin | Pin name | Functional description summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | HV       | <ul> <li>High-voltage start-up</li> <li>The HV pin combines two functions:</li> <li>High-voltage current source</li> <li>At start-up, the 1.1 mA HV current source is used to charge the VCCL capacitor (and via a diode also the VCCH capacitor). In this way, IC operation can start. Until VCCL reaches the start-up level (14.9 V), the IC current consumption is limited to 40 µA. When all conditions (VCCL start-up level, PROTECT pin level, and CTRL pin level) are met, start-up commences.</li> <li>Mains voltage sensing</li> <li>Sampling the HV input current value every 1 ms senses the mains voltage during operation. Pulling the HV input to 2.9 V for 20 µs measures the HV input current. The series resistance of the HV pin to the bulk electrolytic capacitor determines this current value. It reflects the mains voltage value. The value of the external series resistors between bulk electrolytic capacitor and HV pin can set the start and stop levels. When the current exceeds 663 µA, start-up is enabled (brownin). When the current drops to below 587 µA for more than 30 ms, the operation is stopped (brownout). The 30 ms period is required to avoid that the system stops switching due to the zero crossings of the mains or during a short mains interruption. During operation, conditional sensing control reduces the sampling frequency. When a mains voltage is detected, mains voltage sensing is halted for 6.7 ms (101 ms during burst mode) to improve efficiency.</li> </ul> |

#### 3.3 Operating modes

This chapter describes the flyback converter operation modes that are implemented in the TEA19362T. In all operating modes, the TEA19362T works in Discontinuous Conduction Mode (DCM). In short, the flyback transformer in the TEA19362T application is fully demagnetized at the end of every power conversion cycle. One benefit for DCM operation is that it easily cooperates with Synchronous Rectification (SR) controllers on the secondary side of the SMPS. This cooperation enables optimal efficiency.

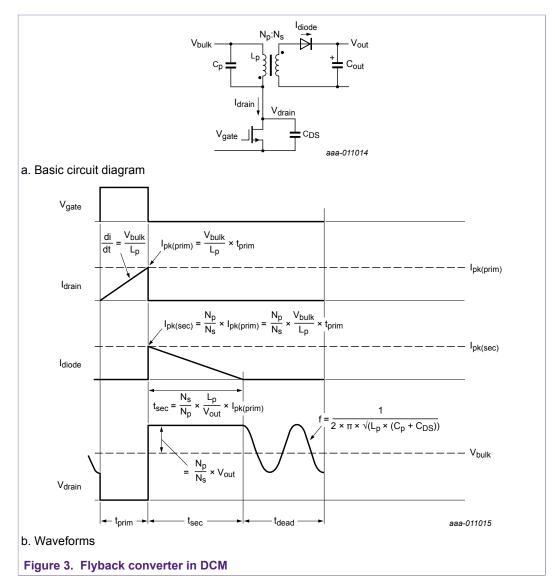

<u>Figure 3</u> shows the elementary circuit diagram of a flyback converter. It also shows the typical voltage and current waveforms when the converter operates in DCM.

#### TEA19362T GreenChip SMPS control IC

During  $t_{prim}$ , the MOSFET is switched on. The current flows through the primary winding of the transformer and the MOSFET. The transformer is magnetized. When the MOSFET is switched off, the drain voltage increases to the sum of the input voltage and the reflected output voltage (output voltage multiplied by the transformer turns ratio). The voltage at the secondary winding increases and the output diode conducts current to the output. The transformer is demagnetized during  $t_{sec}$ . After demagnetization, the voltage on the drain initiates a resonance in the primary inductance and the total capacitance at the MOSFET drain node during  $t_{dead}$ . The next cycle can then start.

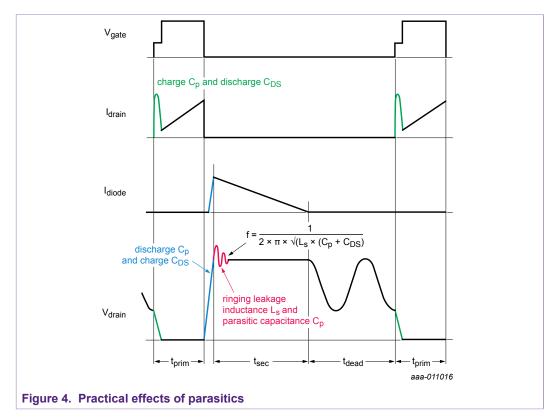

There is some deviation from the basic waveforms because of parasitic elements in the components. Figure 4 shows the main deviations. A very important design aspect of the flyback transformer is to keep the leakage inductance and parasitic capacitances as low as possible. The remaining leakage leads to unwanted effects that do not contribute to the basic power conversion.

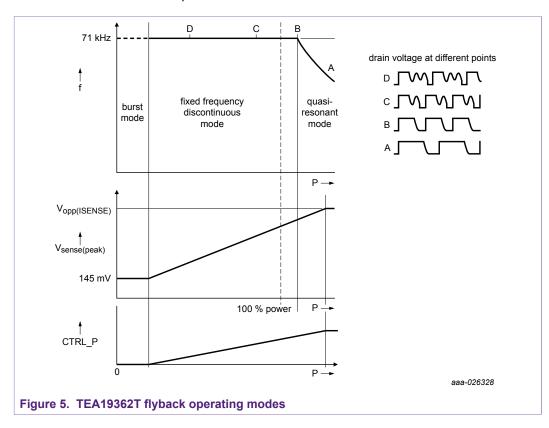

Within DCM operation, two operating modes can be discriminated:

- Discontinuous Conduction Mode (DCM) with fixed frequency (medium and high power level)

- Burst mode (low power level)

Depending on the required output power, the system switches between operating modes. For spectral purity (touchscreens), the switching frequency is kept constant in DCM and in burst mode.

To maintain the spectral purity, the flyback converter must operate in DCM for all powers, including maximum power.

When the power is increased to exceed the level where DCM with fixed switching frequency is possible, the system enters Quasi-Resonant (QR) Mode. The switching

#### TEA19362T GreenChip SMPS control IC

frequency is not fixed anymore then. It drops with the increased output power. To prevent spoiling the spectral purity and CMN performance, decreasing of the switching frequency must be avoided in normal operation.

#### 3.3.1 Flyback operating modes control

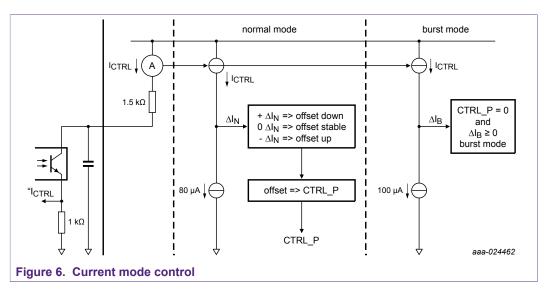

The operating modes are controlled via the CTRL pin. The TEA19362T incorporates a current mode control. Figure 6 shows the principle.

#### 3.3.1.1 CTRL pin during FF DCM

In FF DCM, the current flowing out of the CTRL pin is kept at constant 80  $\mu$ A. The current I<sub>CTRL</sub>, pulled from the CTRL pin by the optocoupler is mirrored for the FF DCM mode and for burst mode. In FF DCM, I<sub>CTRL</sub> is compared with an 80  $\mu$ A reference current. If I<sub>CTRL</sub> is not 80  $\mu$ A, the difference is integrated using a slow time constant. The integrated difference increases or decreases an internal offset. This offset is converted to a proportional signal CTRL\_P, which directly controls the power the IC converts (see Figure 5, flyback operating modes). For  $\Delta$ I<sub>N</sub> > 0, CTRL\_P is decreased, which lowers the converted power. As a consequence, V<sub>out</sub> decreases and so the optocoupler current drops until I<sub>CTRL</sub> becomes 80  $\mu$ A again. For  $\Delta$ I<sub>N</sub> < 0, CTRL\_P is increased. So, V<sub>out</sub> increases and so the optocoupler current increases until I<sub>CTRL</sub> becomes 80  $\mu$ A again. So, I<sub>CTRL</sub> is always regulated to 80  $\mu$ A. The regulation does not depend on the converted power, which ensures stable operation at all output power levels.

#### 3.3.1.2 CTRL pin during burst mode

When  $I_{CTRL} > 80 \ \mu$ A for a longer period and CTRL\_P is lowered to zero (IC is switching at 71 kHz at minimal  $I_{pk}$ , see Figure 5), CTRL\_P cannot be lowered anymore. As a consequence,  $I_{CTRL}$  increases to exceed 80  $\mu$ A. When it reaches 100  $\mu$ A, the IC enters burst mode. The burst mode and related  $I_{CTRL}$  waveforms are discussed in Section 3.3.3. In burst mode, when  $I_{CTRL} < 80 \ \mu$ A for a longer period, the IC enters normal mode again.

#### 3.3.1.3 CTRL pin provisions load steps

To achieve minimum undershoot and overshoot for load steps, various additional provisions are built in. These additional provisions shorten the reaction time for fast changing load conditions:

- When the burst-on time is longer than 1.5 times the minimum burst period (150 μs) during a burst period, the IC changes to normal mode immediately.

- In burst mode, when I<sub>CTRL</sub> remains below 100 μA due to increased load, the IC keeps on switching at 71 kHz with a minimum I<sub>pk</sub> level (145 mV).

- When I<sub>CTRL</sub> drops to below 60 µA due to increased load, the gain is increased and the time constant is reduced. To counteract the voltage drop at the output, the IC moves quickly to maximum power.

- When the load suddenly decreases to very low values and  $I_{CTRL}$  increases to exceed 200  $\mu$ A, switching stops immediately to prevent a high output voltage overshoot.

#### 3.3.2 Fixed-Frequency Discontinuous Conduction Mode (FF DCM)

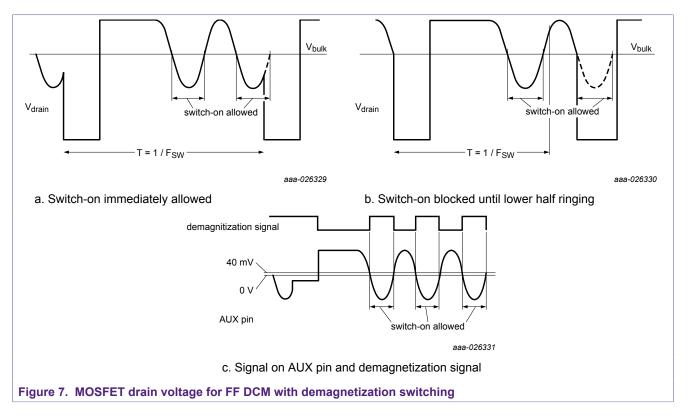

In DCM, a certain dead time always exists between the ending of the secondary stroke and the next switch-on moment of the MOSFET. The dead time enables control of the switching frequency. The system is only allowed to switch on the MOSFET in the bottom half of the ringing (demagnetizing switching), balancing the switching frequency deviation against switch-on losses. Figure 7 shows the switching behavior.

AN11878

When the secondary stroke has ended, the drain voltage starts ringing. When the fixed frequency switch-on timing occurs during the bottom half of the ringing, the MOSFET is switched on immediately (Figure 7a). When the switch-on timing occurs during the upper half of the ringing, the switch-on is delayed until the lower half of the ringing is reached (Figure 7b). The time slots where switch-on is allowed are derived from the demagnetization signal generated on the AUX pin (Figure 7c). Via a resistive divider the signal of the AUX supply winding is fed to the AUX pin. Each time the signal drops below 40 mV, the demagnetization signal becomes high and switch-on is enabled. The demagnetization signal is also used to prevent switch-on during secondary stroke.

The switch-on losses are related to the voltage on the drain at switch-on and are equal to:

Switching loss per cycle =

$$0.5 \times (C_p + C_{DS}) \times (V_{DRAIN})^2$$

(1)

Where:

- C<sub>p</sub> the parasitic transformer capacitance

- C<sub>DS</sub> the drain-source capacitance of the MOSFET (see Figure 7a)

The efficiency gain at higher input voltages by not switching in the top of the ringing is around 1 %.

The switch-on timing deviation, caused by only allowing switching during the bottom half of the ringing, is maximally equal to half the period time of the ringing. With a typical ringing frequency of 750 kHz, the timing deviation becomes 0.67  $\mu$ s. The frequency deviation at 71 kHz is 4.8 %. This deviation is small enough to safeguard the spectral purity.

During DCM, the current flowing out of the CTRL pin is regulated to a fixed value of 80  $\mu$ A. To regulate that current, an offset is generated internally, which controls the operation mode curve (see <u>Section 3.3.1</u>). The internal offset regulates the output power. It increases I<sub>pk</sub> by controlling the level of the ISENSE pin for switch-off from 145 mV to 510 mV.

To maintain the spectral purity, the flyback converter must operate in DCM for all powers, including maximum power. When the power is increased to exceed the level where DCM with fixed switching frequency is possible, the system enters the Quasi-Resonant (QR) mode. The switching frequency is not fixed anymore then. It drops with the increased output power. To prevent spoiling the spectral purity and CMN performance, the switching frequency decreasing must be avoided in normal operation.

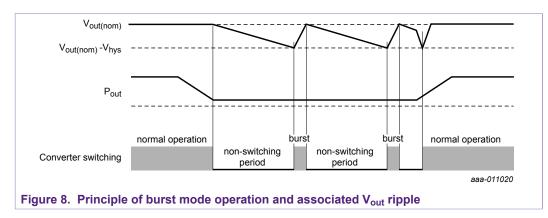

#### 3.3.3 Burst mode

Burst mode operation is used to minimize power loss during low output power conditions. The goal is to generate the required output power with bursts of variable lengths, while switching operation is turned off for shorter or longer periods. When the converter is not switching, conversion losses are zero.

During the intervals that switching is off, it is also important to minimize the current flowing into various circuits of the power converter. Minimizing this current reduces the power consumption. In modern control ICs like the TEA19362T, several internal circuits are switched off during the non-switching period. It minimizes the supply current to less than half the nominal supply current during switching.

#### TEA19362T GreenChip SMPS control IC

Burst mode operation usually results in a higher output voltage ripple than in normal (DCM) mode (see Figure 8).

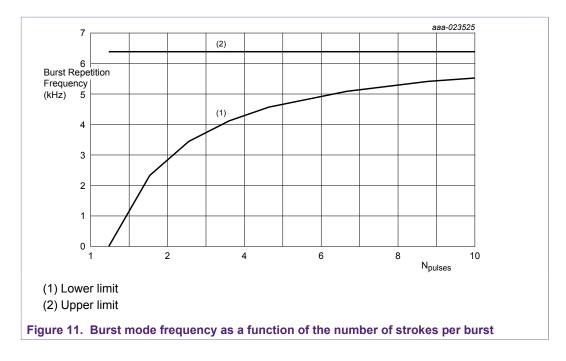

To maintain the spectral purity in burst mode, the switching frequency is kept the same as during normal operation. To limit the ripple in burst mode at the high fixed switching frequency (71 kHz), the burst period is set to a minimum of 150  $\mu$ s (maximum 6.7 kHz).

To prevent audible nose, the peak current in burst mode is chosen as low as possible (145 mV).

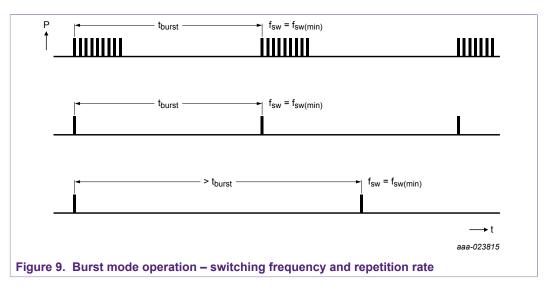

Figure 9 shows the switching behavior during burst mode for different loads.

The minimum number of switching cycles within a burst is 1. At ultra-low load, the number of switching cycles is indeed 1. The repetition rate is regulated to well above 150  $\mu$ s (see Figure 9).

The requested output power determines the number of pulses in each burst period. The digital circuit calculates the number of switching cycles so that the burst repetition timing does not exceed 150  $\mu$ s. At higher output powers, the number of switching pulses increases. At low load, the number of pulses decreases (to a minimum of 1). Simultaneously, the switching frequency within the burst is 71 kHz. In this way, spectral purity is maintained.

AN11878 Application note In FF DCM mode, the internal offset, which keeps  $I_{CTRL}$  regulated at 80  $\mu$ A, regulates the power. When the required output power is reduced in FF DCM mode at 71 kHz, the internal offset cannot be lowered further. The  $I_{pk}$  sense voltage is already at its lowest value (145 mV). In that case,  $I_{CTRL}$  increases to 100  $\mu$ A and the IC enters burst mode.

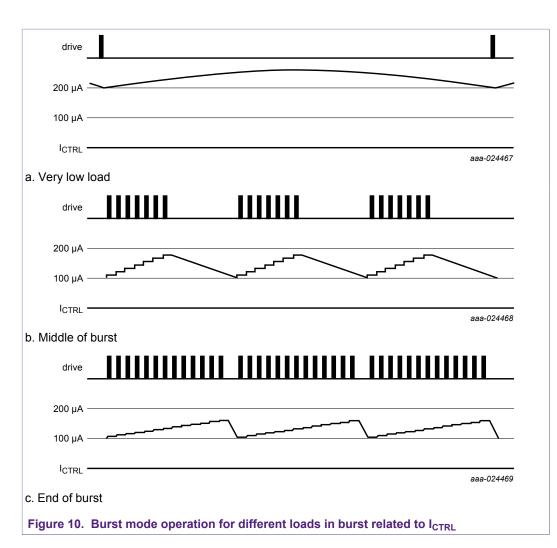

The behavior of the CTRL pin in burst mode differs from its behavior in FF DCM mode. In burst mode, switching always starts when the current drawn from the CTRL pin drops to below 100  $\mu$ A. Figure 10 shows the behavior of I<sub>CTRL</sub> in burst mode at a very low load and in the middle and at the end of the burst.

**Note:** The simplest way to measure  $I_{CTRL}$  is to add a 1 k $\Omega$  resistor from the emitter output of the optocoupler to ground. The sensitivity for oscilloscope measurement is 100 mV/100  $\mu$ A.

#### **NXP Semiconductors**

## AN11878

TEA19362T GreenChip SMPS control IC

At very low loads, only one switching cycle is required to make  $I_{CTRL}$  increase to exceed 100 µA. Only when the  $I_{CTRL}$  drops again to below 100 µA, the next stroke is made. Depending on the winding ratio of the transformer and the output voltage, it is possible that two or three strokes are required to bring ICTRL above 100 µA. Except for the number of strokes per burst cycle, the behavior remains the same.

In the middle of the burst trajectory, the system is switching half the time and half the time it is off. With each stroke  $I_{CTRL}$  increases. This condition generates the highest peak value for  $I_{CTRL}$ .

When the load increases further, the number of strokes per burst increases also until only one stroke per burst is missing. A minor load increase causes the IC to switch continuously to FF DCM at 71 kHz. When FF DCM is entered, I<sub>CTRL</sub> drops from 100  $\mu$ A to 80  $\mu$ A. The internal offset takes over the regulation.

#### TEA19362T GreenChip SMPS control IC

#### 3.3.4 Loop gain and burst period

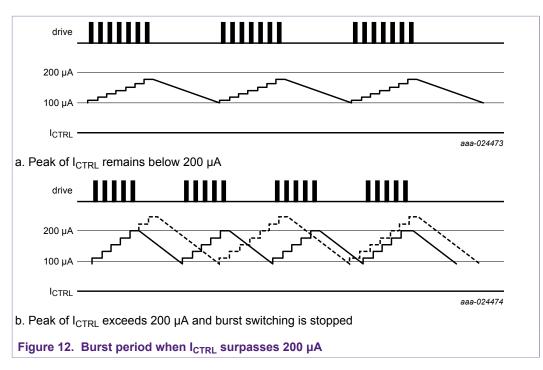

System control is programmed such that switching always stops when  $I_{CTRL} > 200 \ \mu A$  in burst mode and FF DCM. When the input voltage is at its maximum (264 Vac) and operation is at 50 % burst (in middle of the burst trajectory), the maximum  $I_{CTRL}$  peak level is reached. The loop gain determines the peak level. The gain of the optocoupler and the pull-up resistor on secondary side of the optocoupler diode influence the peak level.

When the switching stops earlier than the calculated burst-on time because of a high gain, the system remains working in burst mode. However, the burst period becomes shorter (burst frequency increases). The hysteresis of  $I_{CTRL}$  (between 100 µA and 200 µA) determines the switching behavior (see Figure 12).

AN11878 Application note

#### TEA19362T GreenChip SMPS control IC

<u>Figure 12(b)</u> shows that the burst period reduces when  $I_{CTRL}$  exceeds the 200 µA level. The dashed  $I_{CTRL}$  line indicates the intended (precalculated) behavior.

The loop gain can be optimized to balance load step behavior and burst mode behavior. Select the value of the pull-up resistor of the optodiode on the secondary side such that the current, drawn from the CTRL pin ( $I_{CTRL}$ ) is close to 200 µA at 50 % burst and at 264 V (AC).

#### 3.4 TEA19362 start-up and supply

When the mains voltage is applied, the capacitors at the VCCH and VCCL pins are charged via the HV pin. When the voltage level at the VCCL pin reaches 14.9 V and all conditions are met (brownin, PROTECT pin), the IC starts switching. When the IC is switching, the auxiliary winding takes over the supply of the VCCH and VCCL pins.

#### 3.4.1 Start-up with the HV current source

The HV pin provides two functions:

- High-voltage current source for charging the capacitors at the VCCH and VCCL pins before start-up

- · Mains voltage sensing input for detecting brownin and brownout

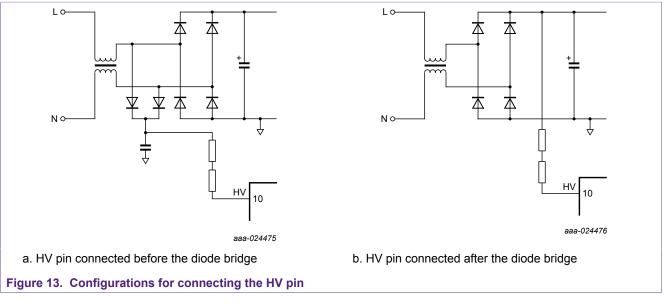

The HV pin can be connected to the high voltage in two ways:

- With a diode/capacitor/resistor network before the mains rectifier bridge

- · With a resistor network after the mains rectifier bridge

Figure 13 shows both configurations.

#### **NXP Semiconductors**

## AN11878

#### TEA19362T GreenChip SMPS control IC

The start-up behavior of the two configurations is alike. However, the brownout behavior after the mains is unplugged is different.

Connecting before the diode bridge has the disadvantage that three additional components are required (two high-voltage diodes and a high-voltage capacitor). When the mains is unplugged, this configuration has the advantage that the voltage across the small capacitor drops quickly to below brownout level and halts switching operation. Only very limited power on the secondary side remains available after the mains is unplugged. To prevent EMI disturbance from the brownin/brownout measuring pulses of the HV pin, the capacitor located after the diodes in this configuration is a requirement.

Connecting the HV pin after the diode bridge saves components. However, when the mains is unplugged, the IC keeps switching. It delivers power to the secondary side until the voltage on the mains electrolytic capacitors drops to below the brownout level (approximately 70 V (DC)). For low load and high input voltages, it can take quite some time. During the time it takes, the output voltage remains regulated.

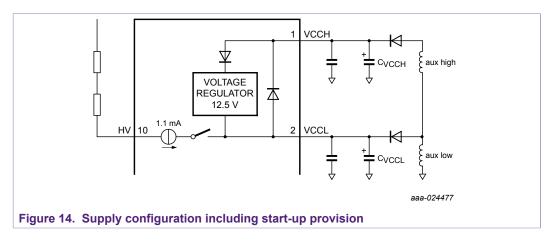

Figure 14 shows the supply configuration.

The main supply pin, which is directly connected to the internal IC supply is the VCCL pin. The VCCH pin is connected to the VCCL pin via an internal regulator. If the supply voltage via the AUX low is lower than 12.5 V, the internal regulator regulates the VCCL to 12.5 V. When the supply voltage via the AUX low pin exceeds 12.5 V, the regulator is turned off. The supply is taken from the VCCL pin. In this way, the lowest voltage that is high enough to supply the IC is always selected to save power. The IC consumes power from the supply as a current source. So, the supply dissipation increases almost linearly with the IC supply voltage.

To charge the capacitors on the VCCL pin and, via the diode, also the capacitors on the VCCH pin, an internal 1.1 mA current source is enabled at start-up. The internal current source is taken from the high-voltage mains connected to the HV pin. Charging these capacitors enables the use of the full capacitance available on both pins as an energy reservoir at start-up. If the capacitance value at the VCCH pin is high enough, it offers the possibility to use a lower capacitance value on the VCCL pin than is required for start-up. As long as VCCL is below system start-up level (14.9 V), the current consumption of the internal IC circuits is limited to 40  $\mu$ A.

When the HV pin is connected before the bridge rectifier, the voltage on the pin may become close to 0 V. The current source is then temporarily unable to generate the 1.1 mA (typical) current required. A discontinuous increase of the VCC voltage can be observed. Depending on the applied input voltage, the series resistance between the HV pin and the mains voltage can also limit the current.

When VCCL reaches the start-up level (14.9 V) during charging, the internal circuits are activated. From this moment, the start-up sequence is activated. The IC current consumption increases (600 µA for the internal IC circuits, the current for the MOSFET drive, and the CTRL function). First, all protections are checked. Further start-up is halted until the brownin condition is met and the protect pin voltage exceeds 0.55 V. Then, switching is enabled. Switching commences with a soft start. During the soft start, the peak current increases to its maximum level in 15 steps. This current increase is achieved by increasing the voltage level for switch-off of the ISENSE pin from 0 mV to 510 mV. The current source of the HV pin remains active. However, it cannot provide all the energy required. So, the VCC voltage decreases until the auxiliary high or auxiliary low winding take over the supply. When the output voltage reaches the regulation level, the HV current source is switched off. The CTRL pin detects when the output voltage has reached the regulation level.

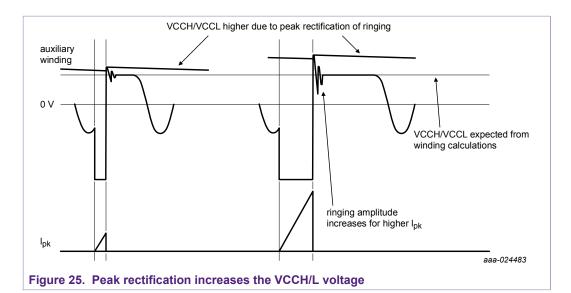

For a reliable implementation of a VCC supply at start-up and during burst operation under all conditions, use a 10  $\mu$ F VCC capacitor. When space and/or cost are critical, it is possible to apply 10  $\mu$ F on the VCCH pin and 1  $\mu$ F on the VCCL pin. The only drawback to this configuration is that there is a slightly higher no-load power consumption. The higher power consumption occurs when a higher output voltage can be generated with the IC operating on the auxiliary low winding during normal (medium or high power level) operation. However, it must switch to auxiliary high during long non-switching periods (e.g. low power or no load).

The value of the capacitor chosen for the VCCH pin must be equal or higher than the value of the capacitor on the VCCL pin. The reason is that during burst the VCC capacitors are only charged at a very low repetition rate during a very short time. The peak charging current can easily surpass 1 A. When the auxiliary high provides the supply under this condition, the series impedance of the series regulator is too high to allow proper charging of a high-value capacitor on the VCCL pin.

#### 3.4.2 Supply protection

Under varying load conditions, it can happen that the switching is stopped for longer periods. An example is when the load changes suddenly from full load to no load. When this sudden change occurs, switching on the primary side does not stop immediately. So, the output voltage increases slightly and exceeds the regulation level. The CTRL pin is pulled low and the IC stops switching via the optocoupler. Because there is no load, the output voltage only drops slowly to its regulation level. When no switching occurs for a longer time, the IC supply can drop to below the UVLO level. The IC then performs a safe restart.

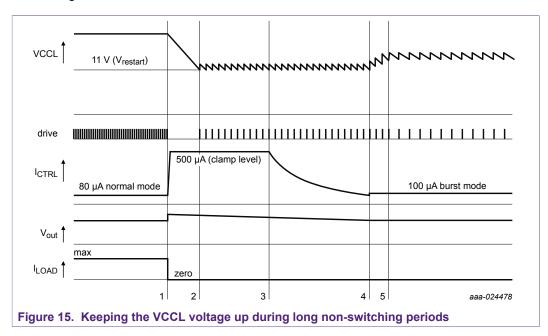

To prevent a restart, the IC starts switching at minimal  $I_{pk}$  when the VCCL voltage drops to below 11 V (V<sub>restart</sub>). The IC keeps switching until the VCCL voltage has increased to at least 100 mV above 11 V. The switching frequency is 71 kHz. When the VCCL voltage drops to 11 V again, the sequence is repeated. The sequence is repeated until V<sub>out</sub> has dropped to the regulation level and the loop is in regulation again. Figure 15 shows the various signals.

The sequence of events is explained using the numbers indicated next to the vertical dashed lines.

1. Load drops from maximum to zero

Switching continues for a short while before stopping, causing V<sub>out</sub> to exceed the regulation level. (For better understanding, the increase of V<sub>out</sub> is exaggerated in Figure 15). Due to the V<sub>out</sub> increase, I<sub>CTRL</sub> also increases from the normal mode level (80  $\mu$ A) to the clamp level (500  $\mu$ A). The VCCL voltage starts to drop because switching stops.

The VCCL voltage has decreased to the V<sub>restart</sub> level (11 V) To keep the VCCL voltage above 11 V, strokes are inserted at minimal I<sub>pk</sub>. When the VCCL voltage has increased by more than 100 mV, switching stops. The VCCL voltage drops again. When it reaches 11 V again, the sequence is repeated.

- V<sub>out</sub> decreases slowly over time, causing I<sub>CTRL</sub> to decrease also.

When the optocurrent drops to below 500 µA on the primary side, I<sub>CTRL</sub> starts to drop to below the saturation level. As long as V<sub>out</sub> keeps decreasing, I<sub>CTRL</sub> keeps dropping.

- 4. When  $I_{CTRL}$  has dropped to 100  $\mu$ A, normal burst switching is resumed. The VCCL voltage increases to the normal level in burst mode.

- 5. The system is in normal burst mode again. All voltages and currents are at the normal level.

Although this mechanism also works when the VCCL voltage becomes too low in burst mode, design the supply such that the VCCL voltage is kept above 11 V during normal burst mode. The drawback of the mechanism is that it regulates the VCCL voltage and not  $V_{out}$ . It causes  $V_{out}$  to exceed the regulation level. The increased  $V_{out}$  increases the optocurrent and  $I_{CTRL}$  current. These additional currents increase the no-load power with several mW.

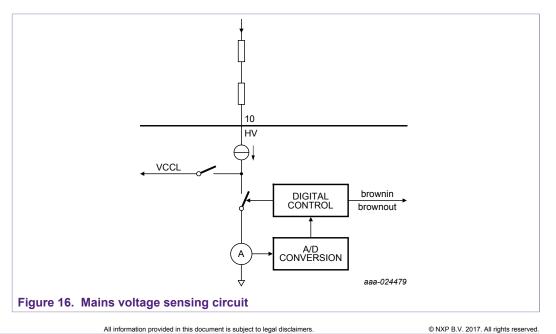

#### 3.5 Mains voltage detection

Mains voltage sensing is performed via sampling of the voltage on the HV pin. To minimize power consumption due to current load on the mains, each measurement takes only a short period (20  $\mu$ s). The measurement interval is 1 ms. However, when a mains voltage that exceeds the brownin level is detected, the measurement interval is increased to 6.7 ms in normal mode and to 101 ms in burst mode. The reason for the increase is saving power.

Measurements are taken during the sampling period. The HV pin is switched to the ground level. The current that flows from the mains through the series resistor at the end of the 20  $\mu$ s period is measured. The internal circuit that connects the HV pin to ground and measures the current introduces a voltage drop of approximately 2.9 V. So, during the sampling period, a voltage of 2.9 V can be observed on the HV pin.

The two possible configurations for connecting the HV pin to the mains are already discussed in <u>Section 3.4.1</u>. In both configurations, the sensing voltage is a DC with some ripple.

Figure 16 shows the measuring setup of the mains sensing.

When the mains sense switch closes, the current is measured. The value of the resistors between the HV pin and the rectified mains determine the current for lower input voltages. For higher input voltages, the current source in series limits the current to 1.1 mA.

#### 3.5.1 Brownin

When the VCCL pin is charged to the start level, mains sensing is activated to generate one of the required conditions for starting the converter. The rectified mains voltage is sensed in the normal sequence of three pulses and a wait time of 6.7 ms. When one pulse shows a value that exceeds the brownin value (663  $\mu$ A), converter start-up is enabled (as far as meeting the brownin requirements is concerned). Sensing continues after start-up.

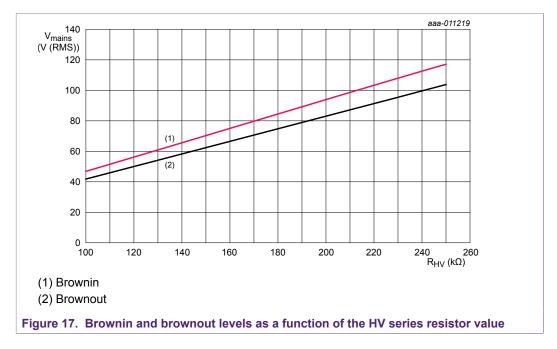

The brownin level can be calculated with Equation 2:

$$R_{HV} = \frac{\sqrt{2} \times V_{mains(RMS)} - V_{meas(HV)}}{I_{bi(HV)}}$$

Example:

- I<sub>bi(HV)</sub> = 663 μA

- V<sub>meas(HV)</sub> = 2.9 V

- V<sub>mains(RMS)</sub> = 86.0 V; The required brownin level

$$R_{HV} = \frac{\sqrt{2} \times 86.0 - 2.9}{663 \times 10^6} \approx 180 \ k\Omega$$

If the brownin level is not met when the VCCL voltage has reached  $V_{start}$ , the HV current source regulates the VCCL voltage on 14.9 V. In this way, when the brownin level is reached, the IC can start immediately.

#### 3.5.2 Brownout

If the mains voltage remains below the brownout level for at least 30 ms, a brownout is detected. The system stops switching. This delay period is built in to ensure that the system does not stop switching during a short mains interruption.

The brownout level can be calculated with Equation 3:

$$R_{HV} = \frac{\sqrt{2} \times V_{mains(HV)} - V_{meas(HV)}}{I_{bo(HV)}}$$

Example:

- I<sub>bo(HV)</sub> = 587 μA

- V<sub>meas(HV)</sub> = 2.9 V

- V<sub>mains(RMS)</sub> = 76.5 V; The required brownout level

$$R_{HV} = \frac{\sqrt{2} \times 76.5 - 2.9}{587 \times 10^6} \approx 180 \ k\Omega$$

AN11878 Application note (2)

(3)

TEA19362T GreenChip SMPS control IC

The selection of a value for the HV pin series resistance determines the brownin and the brownout value.

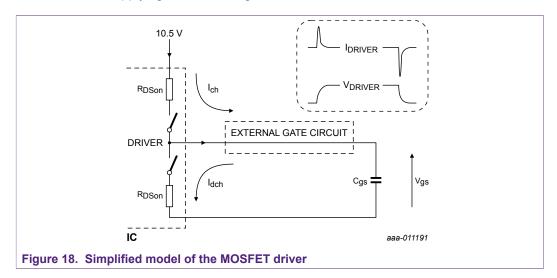

#### 3.6 TEA1936T MOSFET driver

The TEA19362T has a powerful output stage. It directly drives the external power MOSFET. The maximum output voltage is limited to 10.5 V which is the voltage of the internal source supplying the driver stage.

The model in <u>Figure 18</u> shows that current is taken from the internal 10.5 V source when the external MOSFET is switched on by charging the gate to a high voltage.

The shape of the current flowing in and out of the DRIVER pin is related to:

- The supply voltage for the internal driver (10.5 V) at switch-on

- The characteristics of the internal driver MOSFETs (R<sub>DSon</sub>)

- · The value of the gate capacitance of the external MOSFET

- The switch-on/switch-off gate threshold voltage of the external MOSFET

The TEA1936x data sheets provide the characteristics of the internal drivers.

| Symbol                    | Parameter                               | Conditions                 | Min | Тур  | Max | Unit |

|---------------------------|-----------------------------------------|----------------------------|-----|------|-----|------|

| Isource(DRIVER)           | source current on pin<br>DRIVER         | V <sub>DRIVER</sub> = 2 V  | -   | -0.3 | -   | A    |

| I <sub>sink(DRIVER)</sub> | sink current on pin DRIVER              | V <sub>DRIVER</sub> = 2 V  | -   | 0.3  | -   | A    |

|                           |                                         | V <sub>DRIVER</sub> = 10 V | -   | 0.75 | -   | А    |

| V <sub>O(DRIVER)max</sub> | maximum output voltage on<br>pin DRIVER |                            | 9   | 10.5 | 12  | V    |

#### Table 3. MOSFET driver characteristics

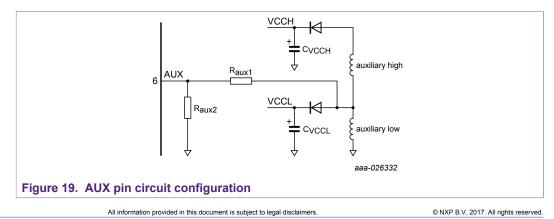

#### 3.7 Auxiliary windings

In the basic application, one or more auxiliary windings on the flyback transformer are used for two main functions:

- Supply voltage for the TEA19362T on the VCCL and the VCCH pins

- Sensing signal on the AUX pin

In a transformer with separate auxiliary windings for the VCCL and VCCH pins, one of the two windings must be used to feed a signal to the AUX pin. In practice, it is the easiest to use the VCCL auxiliary winding because its voltage is lower and it saves some dissipation.

The signal from the auxiliary winding is used to sense several variables that are used for control and protection:

- Demagnetization detection

- · Input voltage sensing for maximum output power compensations

- Output voltage sensing for indirect OVP

The voltage from an auxiliary winding of the flyback transformer is connected to the AUX pin using a resistive divider.

Figure 19 shows the circuit.

As indicated, the resistive divider can also be connected to the auxiliary high winding, provided the values of the resistors are adapted for the higher voltages.

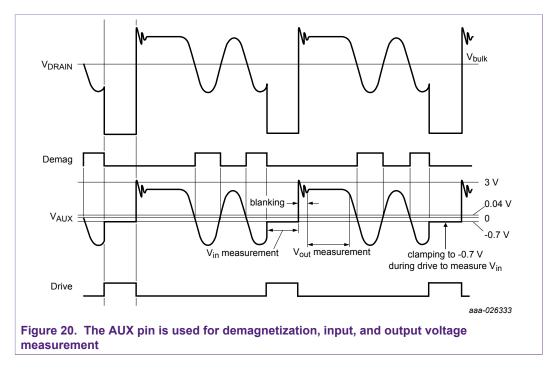

Each detection function has its own time slot in the repetitive AUX signal.

#### 3.7.1 Demagnetization detection

When the signal on the AUX pin drops to below 40 mV, demagnetization is detected. This detection is essential for the DCM switching system. It shows that the transformer is demagnetized because the energy is transferred to the output and the current from the transformer to the output has become zero.

Demagnetization is also used to allow switch-on of the driver, so switching on in the top of the ringing is prevented. Switching on in the top of the ringing increases the switch-on losses.

#### 3.7.2 Input voltage sensing for compensation

When the external MOSFET is switched on, the voltage at the auxiliary winding reflects the input voltage. During this period, an internal circuit clamps the voltage on the AUX pin to -0.7 V. The current from the auxiliary pin to the auxiliary winding via a series resistor is measured. This information is used to compensate for the overpower functions on the ISENSE pin.

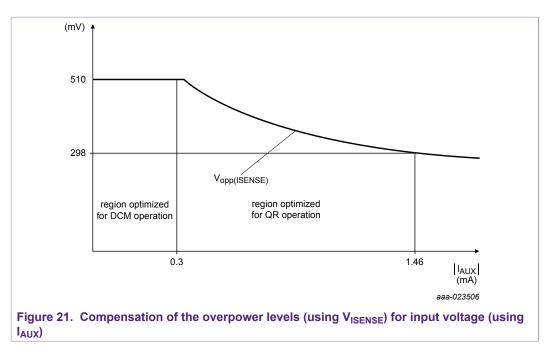

The value of the resistor between the auxiliary winding and the AUX pin ( $R_{aux1}$ ) and the winding voltage value during the primary stroke determine the current that flows. To achieve the required input voltage compensation level, the  $R_{aux1}$  value must match the voltage on the auxiliary winding. Figure 21 shows the relationship between the ISENSE switch-off voltage compensation and the current, measured through  $R_{aux1}$  during primary stroke.

#### TEA19362T GreenChip SMPS control IC

The compensation is optimized for use in QR mode. Though the IC can operate in QR mode, for spectral purity the TEA19362T must operate in DCM for all powers.

In DCM mode, the output power can be written as:

$$\frac{1}{2} \times L_p \times I_{pk}^2 \times f_{sw} \times \eta$$

Where:

- L<sub>p</sub> is the primary inductance

- Ipk is the peak current value

- fsw is the switching frequency

- η is the converter efficiency

In DCM mode, the maximum output power is only dependent on the maximum  $I_{pk}$  level. The maximum switch-off voltage level on the ISENSE pin, which triggers the OPP counter, determines the maximum  $I_{pk}$  level. This level is 510 mV. In practice, however, some  $I_{pk}$  overshoot exists for high input voltages, which is caused by the propagation delay time of the ISENSE comparator. This overshoot can be compensated by increasing the measured current on the AUX pin to slightly above 0.3 mA for high input voltages (e.g. exceeding 200 V (AC)). In this way, the maximum voltage level on the ISENSE pin can be reduced from 510 mV to e.g. 450 mV.

The main relationship between the input voltage for the flyback converter and the current measured at the AUX pin can be calculated with Equation 5:

$$I_{AUX} = \frac{V_{auxiliary\_winding} - V_{AUX}}{R_{aux1}} = \frac{V_{in} \times \frac{N_{aux}}{N_{prim}} - 0.7}{R_{aux1}}$$

(5)

(4)

Because the AUX input combines the input voltage compensation with the OVP protection, a resistor  $R_{aux2}$  to GND is also connected. An additional small current flows to GND through the  $R_{aux2}$  resistor. At low mains voltage, a significant amount of current is added to the total current from the AUX pin (depending on the circuit values; e.g. 10 %).

$$I_{AUX(Raux2)} = \frac{0.7}{R_{aux2}}$$

(6)

$$I_{AUX(tot)} = \frac{V_{in} \times \frac{N_{aux}}{N_{prim}} - 0.7}{R_{aux1}} + \frac{0.7}{R_{aux2}}$$

(7)

The overpower functions use the compensation from the measured AUX current (see <u>Section 3.8.1</u>).

#### 3.7.3 Output voltage sensing for OverVoltage Protection (OVP)

During the secondary stroke, the voltage on the AUX pin is proportional to the output voltage, which is used for an OVP protection for the secondary voltage.

To avoid a wrong level detection due to voltage ringing effects, output voltage sensing is enabled 2.4  $\mu$ s after the primary MOSFET is switched off (see Figure 19 and Figure 20).

Together with the resistor for input voltage sensing ( $R_{aux1}$ ), a voltage divider can be made using a resistor from the AUX pin to ground ( $R_{aux2}$ ). The value of this resistor provides a conditioned signal at which an OVP can be detected. The preset internal level for OVP is 3 V. For a reliable protection function, the voltage on the AUX pin must reflect the output voltage accurately.

The basic relationship (neglecting the output voltage drop via the output rectifier and output cable) between the auxiliary voltage and the output voltage is the transformer turns ratio:

$$\frac{V_{auxiliary\_winding}}{V_O} = \frac{N_{aux}}{N_O}$$

(8)

The value of  $R_{aux1}$  must be determined for the overpower function. The value for  $R_{aux2}$  can be chosen to provide the correct protection level for the OVP.

$$V_{auxiliary\_winding} = \frac{N_{aux}}{N_O} \times V_O$$

<sup>(9)</sup>

$$V_{AUX} = \frac{R_{aux2}}{R_{aux1} + R_{aux2}} \times V_{auxiliary\_winding} = \frac{R_{aux2}}{R_{aux1} + R_{aux2}} \times \frac{N_{aux}}{N_0} \times V_0$$

(10)

Example:

- $N_{aux} = N_O$

- R<sub>aux1</sub> = 47 kΩ

- V<sub>O(ovp)</sub> = 25 V

- V<sub>AUX(ovp)</sub> = 3 V

Solving the equation above for R<sub>aux2</sub>:

$$R_{aux2} = \frac{V_{AUX} \times R_{aux1}}{\frac{N_{aux}}{N_0} \times V_0 - V_{AUX}} = \frac{3 \times 47 \times 10^3}{(1 \times 25) - 3} \approx 6.4 \ k\Omega$$

#### 3.8 Primary current sensing

The voltage across series resistor  $R_{sense}$  measures the primary current through the MOSFET switch. The ISENSE pin senses this voltage. In general, the peak level measured provides information about the power level.

The information about the input voltage (sensed by the AUX pin) and the current (sensed by the ISENSE pin) determines the maximum power level.

The converter power levels are set using the  $R_{\text{sense}}$  resistor value. During start-up and operation, the voltage on the ISENSE pin is used to decide when to switch off the MOSFET. It is also used to detect the various states of conversion.

#### 3.8.1 Soft start

During soft start, the switch-off level on the ISENSE pin increases from zero to 510 mV (in 15 steps) in 3.6 sec. This increase minimizes stress and audible noise during supply turn-on.

soft start: voltage over R<sub>sense</sub>

Figure 22 shows an example of the  $I_{pk}$  behavior during start-up.

The signal on the input of ISENSE is shown. It reflects the current, flowing through the  $R_{sense}$  resistor. It clearly shows the step-wise increase of  $I_{pk}$  until it reaches the maximum level.

#### 3.8.2 OverPower Protection (OPP) counter

When the voltage on the ISENSE pin exceeds the overpower protection level (510 mV), the overpower counter is started. Depending on the input voltage compensation set on the AUX pin (see <u>Section 3.7.2</u>), the protection level can be lower for higher voltages. When the counter has finished, a safe restart is performed after 1000 ms. The counter delay time is 40 ms during start-up and 200 ms during operation. The shorter OPP counter timing during start-up reduces the input power during the output short circuit and repetitive restarts.

When  $V_{\mbox{\scriptsize ISENSE}}$  is lower than the protection level during one cycle, the overpower counter is reset.

When the reference voltage on the ISENSE pin is close to the protection level, the generated continuous average output power can be higher than the expected power. Due to variations of the ISENSE voltage over time, the counter can sometimes be reset.

#### 3.8.3 OPP and UnderVoltage LockOut (UVLO) on the VCC pin

When the load increases to exceed the OPP level, the output voltage decreases. As a result, the voltage on the VCC pin drops as well. The UVLO protection can be triggered before the OPP counter has reached 200 ms (or 40 ms during start-up). To obtain the same behavior in an overpower situation (whether UVLO is triggered or not), the system enters the safe restart mode when overpower and UVLO is detected. The OPP counter value is ignored.

#### 3.8.4 ISENSE pin accuracy

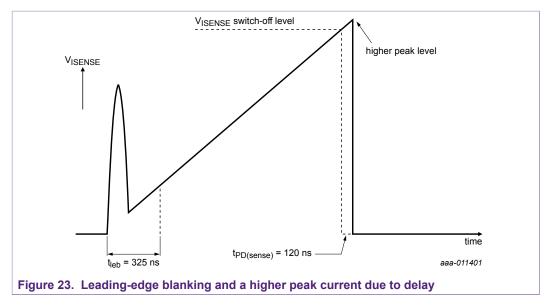

To ensure good quality information measured on the ISENSE pin, a leading-edge blanking is included. Parasitic capacitance can cause spikes, which trigger the peak current comparator prematurely. The ISENSE input is internally blanked the first 325 ns of each switch-on cycle.

A time delay exists between when the voltage level on the ISENSE pin reaches the MOSFET switch-off value and when the MOSFET is switched off  $(t_{PD(sense)} = 120 \text{ ns})$ . During that time, the primary current increases. The primary current increase during the delay period depends on the di/dt slope. The di/dt slope depends on the mains voltage. So, the resulting peak current in the converter partly depends on the mains voltage as well.

#### TEA19362T GreenChip SMPS control IC

Under extreme conditions, di/dt can also rapidly increase because the transformer starts to saturate. The di/dt slope depends on the transformer and converter design. These saturation conditions must be avoided because the converter operation is unpredictable.

#### 3.8.5 ISENSE pin reference levels modulated by input voltage

During high output power conditions, the voltage ripple on the input voltage of the flyback converter has an impact on the compensation function of the AUX and ISENSE pins. Because the rectified mains voltage generates the input voltage, the bulk capacitor shows a ripple voltage when the output power is high. The result is that the average overpower levels are slightly lower at the lowest mains voltage or when a smaller value of the bulk capacitor is used.

#### 3.9 Protections

If a protection is triggered, the controller stops switching. To ensure maximum up-time of the circuit when errors occur, every protection triggers a safe restart sequence.

To avoid false triggering, some protections have a built-in delay.

When the system stops switching, the VCCH and VCCL pins are not supplied via the auxiliary windings anymore. To perform a safe restart in a controlled way, the internal current source on the HV pin keeps the VCCL level above the critical level.

| Protection          | Delay        | Action                                               | V <sub>CC</sub> regulated |

|---------------------|--------------|------------------------------------------------------|---------------------------|

| AUX open            | no           | wait until the AUX pin is connected                  | no                        |

| brownout            | 30 ms        | wait until V <sub>mains</sub> > V <sub>brownin</sub> | yes                       |

| maximum on-time     | no           | safe restart 1000 ms                                 | yes                       |

| OTP internal        | no           | safe restart 1000 ms                                 | yes                       |

| OTP via PROTECT pin | 2 ms to 4 ms | safe restart 1000 ms                                 | yes                       |

#### Table 4. Protections overview

© NXP B.V. 2017. All rights reserved

#### TEA19362T GreenChip SMPS control IC

| Protection                | Delay            | Action                                            | V <sub>CC</sub> regulated |

|---------------------------|------------------|---------------------------------------------------|---------------------------|

| OVP VCCL pin              | 4 cycles         | safe restart 1000 ms                              | yes                       |

| OVP via AUX pin           | 4 cycles         | safe restart 1000 ms                              | yes                       |

| overpower<br>compensation | no               | via AUX pin; cycle-by-cycle                       | -                         |

| overpower timeout         | 40 ms (start-up) | safe restart 1000 ms                              | yes                       |

|                           | 200 ms (normal)  |                                                   |                           |

| overpower and<br>UVLO     | no               | safe restart 1000 ms                              | yes                       |

| OCP                       | blanking time    | cycle-by-cycle                                    | no                        |

| UVLO                      | no               | Wait until VCCL<br>voltage > V <sub>startup</sub> | yes                       |

#### 3.9.1 Safe restart sequence

If a protection is triggered and the system enters the safe restart mode, the system stops switching and restarts after an internally fixed period of 1000 ms. When the converter is not switching, the HV current source supplies the VCCL pin to 14.9 V. At restart, the system continues as in the normal start-up sequence.

#### 3.9.2 Brownout

Brownout is discussed in <u>Section 3.5.2</u>.

#### 3.9.3 Maximum on-time

To prevent extreme power under fault conditions, the controller limits the driver ontime for the external MOSFET to 55  $\mu$ s. When the on-time exceeds 55  $\mu$ s, the IC stops switching and enters a safe restart cycle. Normally, the on-time is never reached unless there is a fault condition.

#### 3.9.4 OverTemperature Protection (OTP)

#### 3.9.4.1 Internal OTP

When the internal temperature of the IC exceeds 140 °C, a safe restart is initiated. The temperature has to drop at least 10 °C before a restart is allowed.

#### 3.9.4.2 OTP via the PROTECT pin

To provide overtemperature protection, an external temperature sensor can be connected to the PROTECT pin. Normally, an NTC resistor with a large value is used for good accuracy. During normal operation, the PROTECT pin delivers a current of 74  $\mu$ A flowing out of the pin. When the voltage on the pin drops below 0.50 V, the protection is triggered. It forces a safe restart. To allow a restart, the voltage level on the PROTECT pin must exceed 0.55 V.

When the voltage on the PROTECT pin exceeds 1.45 V, the internal current source is pinched off. When not used, connecting a capacitor on the PROTECT pin ensures that the capacitor is charged to 1.45 V. It is kept on that voltage, which disables the protection. A value of 10 nF works fine for this purpose.

#### 3.9.5 OverVoltage Protection (OVP)

#### 3.9.5.1 OVP on the VCCL pin

The VCCL pin can withstand a continuous 45 V. When the voltage on the VCCL pin exceeds 48 V, switching is stopped to protect the pin. To prevent erroneous triggering of the protection, the overvoltage must be present for 4 switching cycles.

#### 3.9.5.2 OVP via the AUX pin

The OVP via the AUX pin is described in Section 3.7.3.

#### **3.9.6** OverPower Protection (OPP)

OPP is described in <u>Section 3.8.2</u> and <u>Section 3.8.3</u>. The OPP input voltage compensation is described in <u>Section 3.7.3</u>.

### 4 Circuit design aspects