# Q-5 TRAFFIC MANAGEMENT COPROCESSOR

## **Features**

- Support for ATM Traffic Management 4.1, IP DiffServ, IntServ, and MPLS QoS

- Up to 12 million enqueuedequeue operations per second

- Protocol-independent per-flow and per-VC queuing with up to 128k queues

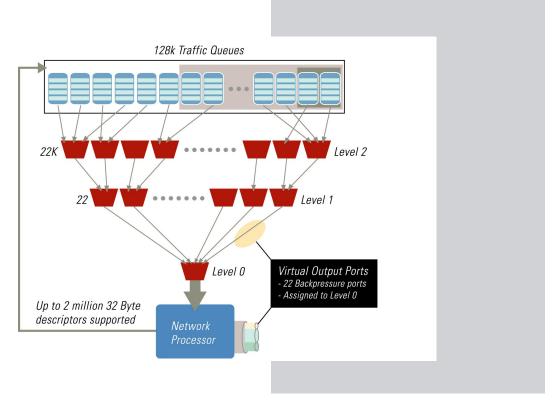

- Flexible three-level scheduling hierarchy supporting a wide array of services and virtual interfaces

- Fully configurable active queue management supporting RED, WRED, EPD, PPD and multiple thresholds

- Up to 2 million 32 Byte descriptors supported

- Integrated multicast enqueue elaboration support.

- Support for per-flow statistics

- API support for dynamic bandwidth provisioning

Quality of Service (QoS) is a growing necessity throughout the network as voice and other services that require reliability and guaranteed bandwidth become more predominant on the Internet. In addition, service providers are increasingly asked to tailor services to meet the needs of their end users, such as minimum bandwidth guarantees, overall Virtual Private Network (VPN) bandwidth guarantees, and more timely and reliable service. To enable these types of services, QoS policies must be enforced from the users' entry point to the network, through the various levels of aggregation, into the core network — and back out again.

Motorola's traffic management solution provides comprehensive QoS management for the forwarding plane with the **Q-5 Traffic Management Coprocessor** (TMC). This multi-protocol TMC provides QoS for up to 128k flows or connections. The following traffic management services are supported:

- ATM TM 4.1

- IP Diffserv compliant

- Intserv compliant

- Multi-protocol Label Switching (MPLS)

The Q-5 TMC also supports up to 22K bandwidth limited channels, each supporting multiple classes of traffic simultaneously (ATM/Diffserv/MPLS). This type of a capability is desirable for access equipment, such as a Digital Subscriber Line Access Multiplexer (DSLAM), supporting multiple classes per customer on a rate-limited channel.

The Q-5 TMC can be implemented in a wide range of networking systems such as:

- Multiservice access platforms

- VPN access devices

- Broadband aggregation devices

- Wireless infrastructure devices

- Internet access routers

The Q-5 TMC is configured using a higher-level QoS API, which provides for ease of programmability, dynamic bandwidth provisioning, and real-time QoS modification.

## Freescale Semiconductor, Inc.

Flexible, look-aside TMC provides unprecedented traffic monitoring, policing and shaping at data rates up to 5Gbps

## FLEXIBLE, LOOK-ASIDE TRAFFIC MANAGER

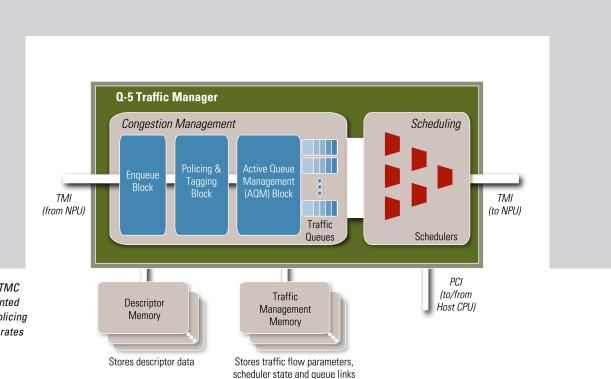

The Q-5 TMC is designed as look-aside traffic manager, which enables you to provide both ingress and egress traffic management with only one TMC in your design. Instead of buffering the payload twice, once at the network processor and then at the TMC as in pipelined architectures, the Freescale solution allows you to buffer the packet only once in the system, thereby minimizing memory requirements.

The Q-5 TMC connects into a network processor or ASIC via its Traffic Management Interface (TMI), a 58 bit wide, 160 MHz, straight-forward connection.

### **ROBUST CONGESTION CONTROLS**

The Q-5 TMC Active Queue Management (AQM) policy, with flexible buffer sharing at flow, class, and interface levels, enables an extensive range of operating conditions in the face of congestion, without degrading the QoS of the flow and of the connections.

Packets and cells can be either tagged or discarded based on the congestion schemes configured in the Freescale TMC.

The Q-5 TMC supports these AQM features:

- 128k Traffic Queues

- Descriptor storage for queueing up to 2 million packets/cells

- Dual leaky bucket policing on up to 128K traffic queues with up to 1K policing profiles supported

- RED, WRED, EPD, PPD and Thresholding supported on up to 128K traffic queues with up to 1K different configurations (shared with policing parameters)

- Two levels of hierarchical buffer sharing (Local and Global) providing greater buffer elasticity to accommodate large bursts of traffic and maintain Service Level Agreements (SLAs) by discarding/tagging data from connections that exceed their contracted rates:

- Up to 4K Local buffer pools available, each of which can be configured to buffer data from multiple traffic queues

- Up to 512 Global buffer pools available, each of which can be configured to buffer data from multiple Local pools

# Freescale Semiconductor, Inc.

#### EFFICIENT BANDWIDTH MANAGEMENT

Efficient bandwidth management ensures that the SLAs for priority, fairness, and data rate are met. The Q-5 TMC implements bandwidth management through its flexible scheduling hierarchy. The traffic queue is the conduit to the Q-5 TMC's scheduling hierarchy. Traffic queues can represent individual connections, a collection of connections, or a flow. The traffic queues can aggregate through up to three scheduling levels. The scheduling hierarchy supports priority and multi-protocol (IP, ATM, Frame Relay, MPLS, or mixture) fair scheduling and shaping algorithms,

The Q-5 TMC bandwidth management features include:

- Per flow and per class bandwidth management

- Fair bandwidth allocation between flows, classes and ports

- Up to 22K rate limited channels with up to four classes of traffic per channel

- Single and dual leaky bucket shaping supported on a large number of flows

- · Spatial multicast support

# REAL-TIME SERVICE PROVISIONING AND REPROVISIONING

QoS configurations, such as active queue management, policing and shaping, and scheduling of flows, can be configured using QoS APIs. These APIs also make it possible to modify QoS configurations for real-time service provisioning and reprovisioning.

When the Q-5 TMC is used with one of Motorola's network processors (such as the C-3e NP or the C-5e NP), the QoS APIs are integrated seamlessly with the C-Port Family C-language based programming model and C-Ware APIs, making your TMC configuration simple and fast. The QoS APIs can also be used for configuring the TMCs when they are used as stand-alone traffic managers.

## **FLOW MANAGEMENT**

The Q-5 TMC can collect statistics to manage the traffic flows and to help support billing and accounting services. These statistics include:

- Number of bytes or packets transmitted on a flow

- Number of bytes or packets dropped

- Number of conforming bytes or packets

- Number of bytes or packets that have been marked as a result of a policing action

Efficient scheduling hierarchy supports multi-protocol fair scheduling and shaping algorithms

For More Information On This Product, Go to: www.freescale.com

# Freescale Semiconductor, Inc.

For more information about Freescale's network processing solutions, please contact your local Freescale sales representative or call (800) 521-6274. You can also visit Freescale's Smart Networks Web site at:

www.freescale.com

#### **Q-5 TMC PRODUCT HIGHLIGHTS**

| Throughput                               | Bandwidth                                                                                                                                              | 5Gbps                                                                                                                                         |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Traffic Management<br>Services Supported | ATM TM 4.1 (CBR, VBR rt and nrt, UBR) IP Diffserv compliant (RFC 2475, 2597, 2598, 2697, 2698) Intserv compliant Multi-protocol Label Switching (MPLS) |                                                                                                                                               |

| Queuing                                  | Independent traffic queues                                                                                                                             | 128k                                                                                                                                          |

| Scheduling                               | Scheduling Hierarchy                                                                                                                                   | 3 levels                                                                                                                                      |

|                                          | Number of schedulers per level                                                                                                                         | Level 2 – 22K<br>Level 1– 22<br>Level 0 – 1                                                                                                   |

|                                          | Programmable scheduling algorithms (per scheduler)                                                                                                     | <ul> <li>Work conserving and non work<br/>conserving Weighted Fair<br/>Queuing (WFQ)</li> <li>Strict Priority</li> <li>Round Robin</li> </ul> |

| Policing                                 | Individually police-able traffic queues                                                                                                                | 128k                                                                                                                                          |

|                                          | Number of policing profiles                                                                                                                            | 1K                                                                                                                                            |

|                                          | Policing algorithms                                                                                                                                    | GCRA, Dual Leaky Bucket, TCM                                                                                                                  |

| Congestion Control                       | Congestion control algorithms                                                                                                                          | EPD, PPD, RED, WRED                                                                                                                           |

|                                          | Active Queue Management                                                                                                                                | 2-level hierarchical buffer sharing                                                                                                           |

| Virtual Output Ports                     | Backpressure-able virtual output ports                                                                                                                 | 22                                                                                                                                            |

|                                          | Virtual output port assignments                                                                                                                        | Level 0 scheduler inputs                                                                                                                      |

| Forwarding Path Interface                | Traffic Management Interface (TMI)                                                                                                                     | 58 bit, 160MHz                                                                                                                                |

| Management Interface                     | PCI Interface                                                                                                                                          | 32 bit, 33MHz                                                                                                                                 |

| Memory Interfaces                        | Descriptor Memory                                                                                                                                      | 76 bit SDRAM, 133MHz                                                                                                                          |

|                                          | Traffic Management Memory                                                                                                                              | 36 bit QDR SRAM, 150MHz                                                                                                                       |

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.