**Freescale Semiconductor Application Note**

AN3655 Rev. 1, 5/2011

# MSC815x and MSC825x DSP Family **Design Checklist**

This application note identifies resources and provides guidance for developing applications using the MSC815x and MSC825x DSP devices. It includes a check list for design phases of projects that incorporate the DSPs, including:

- Definition phase. This document highlights design • requirements, such as pin multiplexing, reset timing, and other design considerations.

- Design implementation phase. This document reviews relevant issues for schematic development and testing.

### NOTE

The MSC815x family includes the MSC8151, MSC8152, MSC8154, MSC8154E, MSC8156, and MSC8156E DSP devices. The MSC825x family includes the MSC8251, MSC8252, MSC8254, and MSC8256 DSP devices.

— Revision 2.1 mask 0M52Y (orderable part number ends in B, for example MSC8156VT100B)

#### Contents

| 1.  | Background 2                                     |

|-----|--------------------------------------------------|

| 2.  | Supporting Documentation 3                       |

| 3.  | Power Supply Requirements 4                      |

| 4.  | Power-Up Sequence and Start-Up Timing 7          |

| 5.  | System Clocking 7                                |

| 6.  | Reset 11                                         |

| 7.  | Boot                                             |

| 8.  | I/O Multiplexing 12                              |

| 9.  | Identifying the Device ID and Revision Number 15 |

| 10. | DDR External Memory Use 16                       |

| 11. | Interface Connections 19                         |

| 12. | Open Drain Pins                                  |

| 13. | Disposition of Unused Signal Lines 30            |

| 14. | Signals Connection Summary 30                    |

# 1 Background

Developing a project that integrates one or more MSC815x/MSC825x devices requires planning that identifies:

- The specific interfaces required for the design.

- How the interfaces are used including whether the interfaces use dedicated signal lines or must share signal lines during device initialization and/or operation (signal multiplexing).

- How the device is initialized/booted during normal operation.

After identifying the high-level system requirements, the designer must define the following hardware requirements:

- Basic power system.

- Clocking system.

- Reset/initialization system.

- Power-up/start-up sequencing system.

- Required memory and memory interface system.

- Interface connections.

- Disposition of unused signal connections to minimize power consumption.

To support the hardware configuration, the designer must also provide software (not discussed in this document) to support device operation, including:

- Device initialization software (reset sequence, booting, and interface setup).

- Interrupt service routines (ISRs) to handle normal DSP core intervention tasks and error interrupts/exceptions.

- Protocol-defined data management and processing software (which may include standard Ethernet frame processing or any of several vocoder implementations, security algorithms for security-enabled devices, and so forth).

- Other software, such as power-management and reporting or overall process management, as required.

The device specific reference manual and core subsystem reference manuals supply the configuration programming information required to develop the application-specific system environment as well as data transfer management and coprocessor execution. The core reference manual provides detailed programming information required to develop the application-specific algorithm core processing software including ISR processing. Support can be provided or recommended by Freescale Semiconductor. Contact your local sales office or representative for additional information.

## 2 Supporting Documentation

The MSC815x/MSC825x devices are supported by the following types of documentation:

- Product brief. Device specific document that includes a high-level description of critical performance metrics, detailed lists of product features, and an overview of available hardware and software development environment tools.

- Data sheet. Device specific document that provides a general description of product features, functional block diagrams, signal/pin assignment for the device packaging, detailed physical and electrical specifications including operating parameter values, general hardware design guidelines, ordering information, and detailed packaging specifications.

- Reference manuals. Each device is supported by four reference manuals:

- Device specific. Includes detailed information about the device for each module/subsystem

with specific programming models to allow configuration, programming, and operation

monitoring. In addition, this document describes device level functionality including interrupt

processing and debugging.

- *SC3850 DSP Core Reference Manual*. Includes a detailed description of core functionality and operation including the core instruction set programming.

- MSC8156 SC3850 DSP Core Subsystem Reference Manual. Includes a detailed description and programming information for the memory management unit (MMU), extended programmable interrupt controller (EPIC), and internal memories (including cache memories) supported in each subsystem.

- QUICC Engine Block Reference Manual with Protocol Interworking. Includes a detailed description and programming information for the QUICC Engine subsystem including the dual RISC processors, internal memory, communication controllers and interfaces, baud rate generators and counters, and lists which components in this subsystem are used by the MSC815x/MSC825x DSPs.

- Application notes. Individual documents that provide specific recommendations and guidelines for configuration and operation of the device for specific applications or for specific interface enablement and optimization.

### NOTE

Before starting an application design, refer to the latest device errata document for the corresponding device. Contact your local sales office or representative for details.

**Power Supply Requirements**

# **3 Power Supply Requirements**

The following sections discuss the various aspects to consider for power supply selection and design.

## 3.1 **Power Supply and Ground Inputs**

Each MSC815x/MSC825x device requires the power supplies and grounds listed in **Table 1**. Refer to the device specific technical data sheet for minimum and maximum voltage levels.

| Signal Name                   | Symbol                | Description                                                                                                   | Required Voltage             |  |  |  |

|-------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|

| POWER                         |                       |                                                                                                               |                              |  |  |  |

| VDD                           | V <sub>DD</sub>       | Core and Internal logic power                                                                                 | 1.0 V                        |  |  |  |

| M3VDD                         | V <sub>DDM3</sub>     | M3 memory Power. Only for 1024 KB, the rest 32 KB are powered with $\rm V_{\rm DD}.$                          | 1.0 V                        |  |  |  |

| MVDD                          | V <sub>DDM</sub>      | MAPLE-B Power                                                                                                 | 1.0 V                        |  |  |  |

| GVDD1, GVDD2                  | V <sub>DDDDR</sub>    | DDR Interface Power. Each controller has it's own supply.                                                     | 1.5 V (DDR3)<br>1.8 V (DDR2) |  |  |  |

| M1VREF, M2VREF                | MV <sub>REF</sub>     | DDR Reference Voltage                                                                                         | = V <sub>DDDDR</sub> /2 V    |  |  |  |

| NVDD, QVDD                    | V <sub>DDIO</sub>     | Input/Output Power. MSC815x/MSC825x I/O voltage is 2.5<br>not like the 814x family which has 3.3 I/O voltage. | 2.5 V                        |  |  |  |

| SXPVDD1, SXPVDD2              | V <sub>DDSXP</sub>    | RapidIO Pad Power (also used for SGMII and PCI Express).<br>Each HSSI port has it's own supply.               | 1.0 V                        |  |  |  |

| SXCVDD1, SXCVDD2              | V <sub>DDSXC</sub>    | RapidIO Core Power (also used for SGMII and PCI Express).<br>Each HSSI port has it's own supply.              | 1.0 V                        |  |  |  |

| PLLx_AVDD                     | V <sub>DDPLLx</sub>   | System PLL x Power (x = 0, 1, 2)                                                                              | 1.0 V                        |  |  |  |

| SR1_PLL_AVDD,<br>SR2_PLL_AVDD | V <sub>DDRIOPLL</sub> | RapidIO PLL Power (also used for SGMII and PCI Express)                                                       | 1.0 V                        |  |  |  |

|                               |                       | GROUND                                                                                                        |                              |  |  |  |

| VSS                           | GND                   | Internal logic and I/O Ground                                                                                 | 0 V                          |  |  |  |

| SR1_PLL_AGND,<br>SR2_PLL_AGND | GND <sub>RIOPLL</sub> | RapidIO PLL Ground (also used for SGMII and PCI Express)                                                      | 0 V                          |  |  |  |

| SXCVSS1, SXCVSS2              | GND <sub>SXC</sub>    | RapidIO Transceiver Core Ground (also used for SGMII and PCI Express)                                         | 0 V                          |  |  |  |

| SXPVSS1, SXPVSS2              | GND <sub>SXP</sub>    | RapidIO Transceiver Pad Ground (also used for SGMII and PCI Express)                                          | 0 V                          |  |  |  |

|  | Table 1. | MSC815x/MSC825x Po | wer Inputs |

|--|----------|--------------------|------------|

|--|----------|--------------------|------------|

Actual requirements depend on the specific design implementation. Refer to the product-specific technical data sheet for detailed specifications. The data sheet also lists the required reference voltage source for each signal connection. Some implementations may require different voltage levels for the specified power supplies. For example, DDR3 memories use a nominal 1.5 V whereas DDR2 memories use a nominal 1.8 V. Select the appropriate voltage level to meet your design requirements using the values recommended in the device-specific data sheet.

### 3.2 **Power Consumption**

Use the following guidelines when considering power consumption and dissipation requirements:

- For each power supply rail, select a source that can supply both the average expected current and peak power requirements. Typical and peak requirements are application dependent. See the device specific technical data sheet for device power characteristics and power supply design recommendations.

- Use the thermal characteristics and consideration guidelines provided in the device-specific data sheet to perform thermal analysis when designing board layout.

- Some applications that do not use some of the device modules can reduce power consumption by connecting some of the power signals to GND instead of the active supply. Refer to the application note *MSC8156 DSP Family Lower Power Modes* (AN4184) for details on powering down certain power domains.

- A power calculator tool is available upon request under NDA. Contact your local sales office or representative for details.

### 3.3 Decoupling

When developing a specific board design, include decoupling capacitors to minimize noise propagation and maintain proper power levels. It is very important that particular attention is paid to decoupling for the supplies for the PLL circuits to minimize radiated emissions and promote stable frequency generation and clocking. **Section 3.2** of the data sheet includes decoupling guidelines for the PLL power circuits. As a reference, the user can review the design of the MSC8156ADS, available under NDA from Freescale. This board design include:

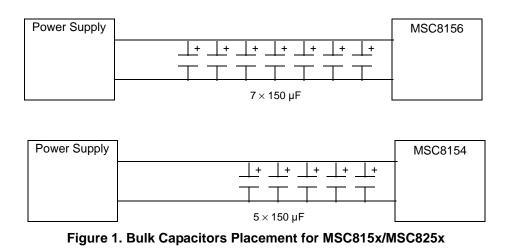

• Bulk capacitors for  $V_{DD}$ . The bulk capacitors decrease low frequency noise. Bulk capacitors should be placed as close as possible to the MSC815x/MSC825x power balls to minimize voltage spikes on the  $V_{DD}$ . In the case of the MSC8156/MSC8156E/MSC8256, a total of seven 150  $\mu$ F capacitors are required. Five of 150  $\mu$ F need to be placed close to the DSP device as shown in Figure 1. For the MSC8151/MSC8152/MSC8154/MSC8154E/MSC8251/MSC8252/MSC8254, a total of five 150  $\mu$ F capacitors are required. Three of the 150  $\mu$ F need to be placed close to the DSP device.

MSC815x and MSC825x Design Checklist, Rev. 1

**Power Supply Requirements**

- Bulk Capacitor for V<sub>DDDDR</sub> on the MSC815x/MSC825x. Two 47 μF bulk capacitors are placed on V<sub>DDDDR</sub> (for each of the two controllers) in the MSC815x/MSC825x to decrease low frequency voltage spikes. Bulk capacitors should be placed as close as possible to the DSP device

- Bulk Capacitor for  $V_{DDM3}$  on the MSC815x/MSC825x. One 47  $\mu$ F bulk capacitor is placed on  $V_{DDM3}$  in the DSP to decrease low frequency voltage spikes. Bulk capacitors should be placed as close as possible to the DSP.

- Bulk Capacitor for V<sub>DDM</sub> on the MSC815x/MSC825x. One 47 μF bulk capacitor is placed on V<sub>DDM</sub> in the DSP device to decrease low frequency voltage spikes. Bulk capacitors should be placed as close as possible to the DSP device.

- Bypass Capacitors for all power supplies on the MSC815x/MSC825x. Should be combined from four types of capacitors. 0.01  $\mu$ F, 0.1  $\mu$ F, 1  $\mu$ F, 4.7  $\mu$ F bypass. Every power ball should be connected to a 0.01  $\mu$ F or 0.1  $\mu$ F or 1  $\mu$ F capacitor, with the total number to include the same number of capacitors of each value. For example, for 60 power balls, there would be 20 capacitors of each size. Spread three to four 4.7  $\mu$ F capacitors among the power balls. The capacitors should be ceramic capacitors with low ESR/ESL and placed on the DSP board for filtering high frequency noise. Ceramic capacitors should be placed on the device ball.

- Refer to the device-specific data sheet for details on PLL decoupling circuits.

- In addition to information about power supply decoupling, *AN3634: Designing a Core Power Supply for MSC8144 DSPs* also includes power plane layout and other design tips to achieve a stable voltage supply for the MSC8144 device. You can apply similar guidelines to the MSC815x/MSC825x board design.

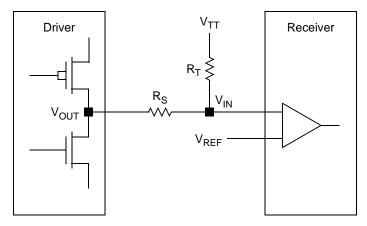

## 3.4 I/O Signal Levels

### NOTE

This section is not relevant to Serial RapidIO and DDR I/O signal levels.

The MSC815x/MSC825x GPIO voltage is 2.5 V. Many industrial standard peripheral devices such as  $I^2C$ , SPI, and UART devices can support a range of I/O voltage between 1.8 V–3.3 V.

### CAUTION

Direction connection of 3.3 V devices can cause damage to the DSP device. Never connect 3.3 V devices directly to the DSP GPIO pins

If the MSC815x/MSC825x device connects to a peripheral device that drives signals with a voltage level that is not 2.5 V (for example, 3.3 V devices that drive the TDM, I<sup>2</sup>C, SPI, UART, CLKIN, or RESET signals), the design must employ a voltage translator on the board to avoid applying voltage levels to the DSP above specified nominal values.

The hardware logic of the CodeWarrior USB TAP has two remote power supplies:

- The main logic (power processor, CPLD, and so on) feeds from the Vbus of the USB cable.

- The output buffers are powered from sense signal on pin number 11 of the 14-pin OnCE cable connected to the target, and should be connected to 2.5 V to provide correct signal level on JTAG port.

I

# 4 Power-Up Sequence and Start-Up Timing

Device start-up requires a synchronization between starting and applying the various device power supplies. Refer to the Section 3 of the device-specific data sheet for guidelines on power supply ramp-up sequence and timing.

# 5 System Clocking

The following sections provides guidelines and descriptions for the various clocking systems used with and in the MSC815x/MSC825x.

## 5.1 Clock Signals

MSC815x/MSC825x devices use clock signals for internal clocking and for synchronous interfaces. Each of the clock signals has its own unique requirements. Clock signals include the following:

- General:

- CLKIN

- CLKOUT

- Serial RapidIO/SGMII/PCI-Express:

- SRx\_REF\_CLK/SRx\_REF\_CLK (differential pair)

- TDM:

- TDMxRCK

- TDMxTCK

- Timers:

- TMRx

- JTAG:

- ТСК

- DDR:

- MxCK[0–2]/MxCK[0–2] (differential pairs)

- Ethernet:

- GEx\_RX\_CLK

- GEx\_TX\_CLK

- GEx\_GTX\_CLK

- GE\_MDC

- SPI:

- SPI\_SCK

- $I^2C$ :

- I2C\_SCL

#### System Clocking

Refer to the device specific technical data sheet in **Section 2.6.1** through **Section 2.6.9** for the individual signals requirements. For each clock signal, make sure that you comply with each of the following specifications:

- Clock frequency limits.

- Clock slope limits.

- Jitter limits.

- Output clock load requirements.

- Clock tree for the DDR-SDRAM balancing with zero delay buffers for large loads.

- Special startup sequencing requirements for clock signals during reset.

As shown in **Chapter 7** *Clocks* of the device-specific reference manual, the MSC815x/MSC825x device has a flexible clocking scheme to deliver the clock frequencies used by the various subsystems and external interfaces. During power-on reset, the user configures a specific clock mode that defines the various clock frequencies and domains in the device. The specific clock mode is selected using the MODCK[5–0] field in the reset configuration word. **Table 7-1** in the device specific reference manual shows the relationships between the input clock (CLKIN) and the mode (MODCK), and the internal clock domains.

**Table 7-2** in the device specific reference manual shows the relationships between the mode (MODCK) and the output clock (CLKOUT), according to the CLKOUT configuration defined during power up sequence.

### NOTE

For each MODCK selected, a specific frequency is selected for each clock domain and a specific CLKIN frequency is required (66.67 Mhz or 100 Mhz). **Table 7-1** in the device specific reference manual has detailed information about the MODCK options. Evaluate each clock and make sure that CLKIN frequency and clock mode (MODCK) yield the desired internal frequencies.

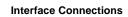

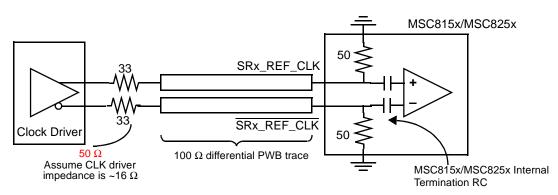

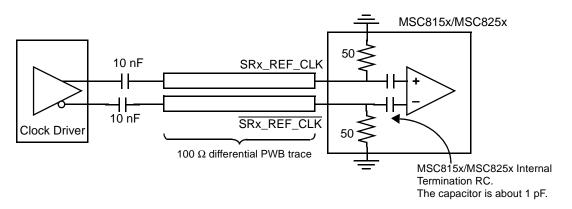

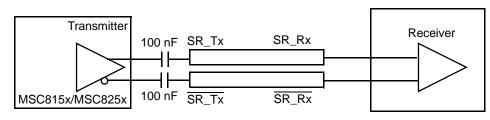

## 5.2 Serial RapidIO Reference Clock

Because the serial RapidIO reference clock is an external signal, the detailed description and requirements are discussed with other interface signal requirements. See the device specific data sheet for details.

## 5.3 QUICC Engine Subsystem Clocks

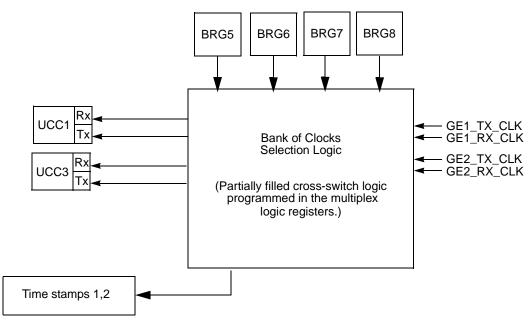

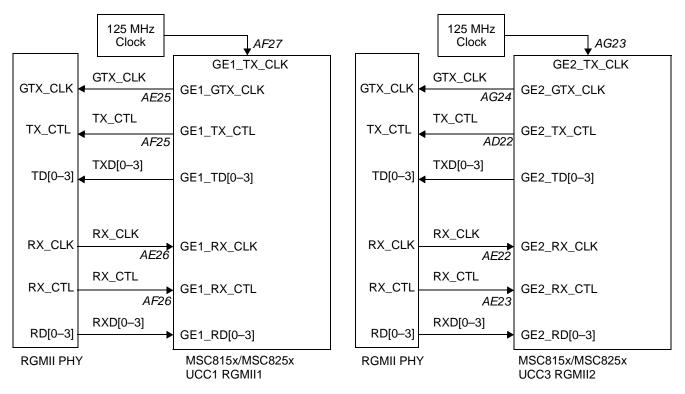

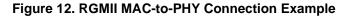

The QUICC Engine subsystem requires input clocks as shown on the right of **Figure 2** to drive the UCC clock signals. The clock signals for each of the UCCs driven by the MSC815x/MSC825x are based on the clock inputs shown in **Figure 2**, For example, the 125 MHz clock source GTX\_CLK125 connects GE1\_TX\_CLK, which is used to drive GE1\_GTX\_CLK as a clock output from the MSC815x/MSC825x to the Ethernet PHY. RX\_CLK of the Ethernet PHY can connect to GE1\_RX\_CLK, which is used to drive UCC1 Rx as clock input from the Ethernet PHY. Refer to the device specific data sheet and reference manual for connection options and details.

Figure 2. Bank of Clocks in the QUICC Engine Subsystem

| Table 2. Clock Source O | ptions Using | I External Clock | Signals   |

|-------------------------|--------------|------------------|-----------|

|                         | phone osing  |                  | Orginalis |

| Clock        | External CLK |            |            |            |  |  |  |  |

|--------------|--------------|------------|------------|------------|--|--|--|--|

| CIOCK        | GE1_RX_CLK   | GE1_TX_CLK | GE2_RX_CLK | GE2_TX_CLK |  |  |  |  |

| UCC1 Rx      | V            |            |            |            |  |  |  |  |

| UCC1 Tx      |              | V          |            |            |  |  |  |  |

| UCC3 Rx      |              |            | V          |            |  |  |  |  |

| UCC3 Tx      |              |            |            | V          |  |  |  |  |

| Time Stamp 1 |              |            | V          | V          |  |  |  |  |

| Time Stamp 2 |              |            | V          | V          |  |  |  |  |

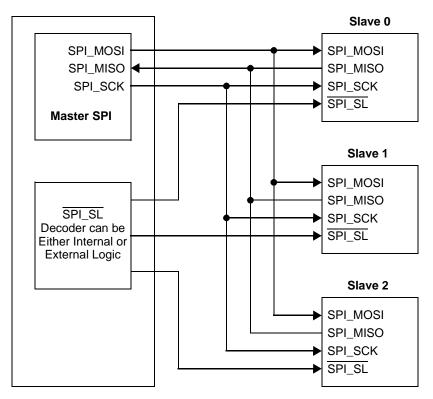

Although SPI is part of the QUICC Engine subsystem, it does not receive its clock signal from the Bank of Clocks. SPI\_SCK is selected by configuring the GPIO17 signal (see **Chapter 24** *GPIO* in the device specific Reference Manual for details). The clock signal operation (clock invert, clock phase, and clock gap) are configured in the SPIMODE register (see **Chapter 20** *Serial Peripheral Interface (SPI)* in the device specific Reference Manual for details).

## 5.4 I<sup>2</sup>C Clock

I2C\_SCL is selected by configuring the GPIO30 signal (see **Chapter 24** *GPIO* in the MSC815x/MSC825x device specific Reference Manual for details). See **Chapter 26**  $I^2C$  in the MSC815x/MSC825x device specific Reference Manual for details on the clock operation.

System Clocking

## 5.5 Clock Mode Tool

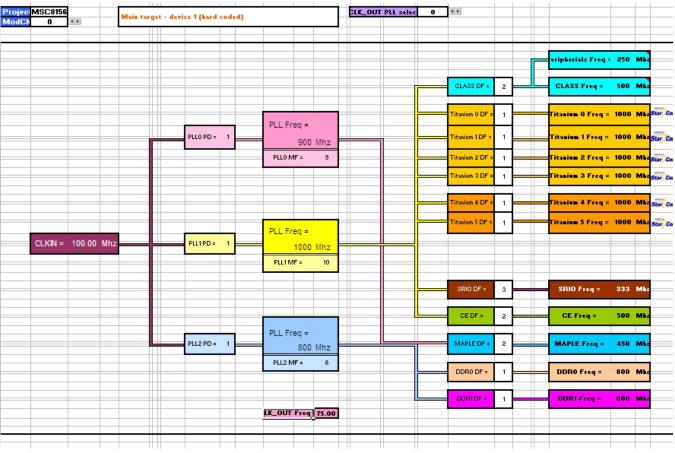

A spreadsheet tool that calculates all component frequencies depending clock mode and clock source for the MSC815x/MSC825x DSPs is available under NDA. This tool also validates configured clock schemes by clock specifications. **Figure 3** shows an example of the tool spreadsheet. Contact your local Freescale sales office or representative for details.

Figure 3. Clock Mode Tool Spreadsheet Example

## 6 Reset

Use the following reset guidelines:

- Ensure that the  $\overline{\text{SRESET}}$  pin is not driven by external logic.

- Connect the HRESET and SRESET pins to 4.7 K $\Omega$  pull-up resistors.

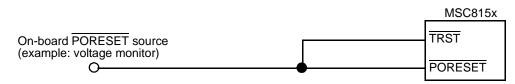

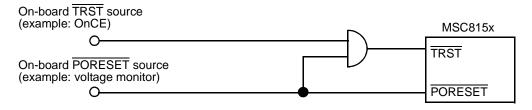

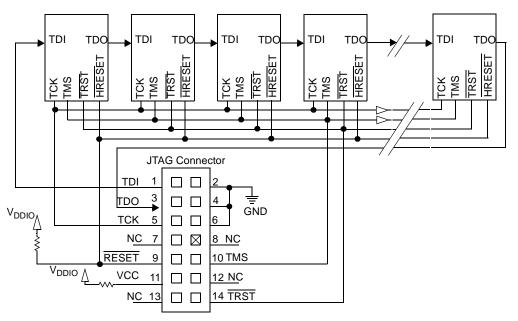

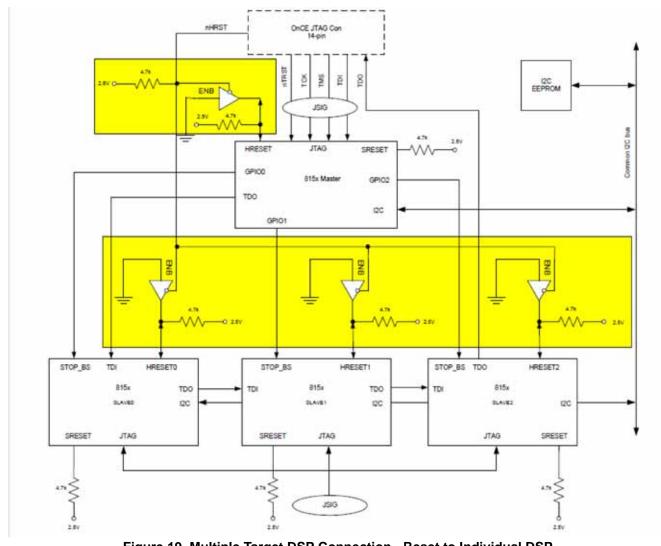

- When a debugger is not used,  $\overline{\text{TRST}}$  must be tied directly to  $\overline{\text{PORESET}}$  as shown in Figure 4.

- When a debugger is used, TRST and PORESET must be connected as shown in Figure 5.

- Refer to the device data sheet for the PORESET, HRESET and SRESET electrical requirements.

- Refer to the device reference manual for the functional description of the reset sequence.

Figure 4. Reset Connection in Functional Application

Figure 5. Reset Connection in Debugger Application

# 7 Boot

**Chapter 6** *Boot Program* of the device specific reference manual describes the functionality and operation of the boot program.

Use the following boot guidelines:

- Implement an I<sup>2</sup>C EEPROM of at least 8 KB in size in the system to support boot patches.

- Contact your local sales office or representative to obtain the boot patch files.

For additional information, see:

- Using an I<sup>2</sup>C EEPROM During MSC8156 Initialization (AN3670)

- Advantages of Using I2C EEPROMs During Reset and Boot Flow for MSC8156 DSPs (EB728)

I/O Multiplexing

# 8 I/O Multiplexing

Use the following I/O multiplexing guidelines:

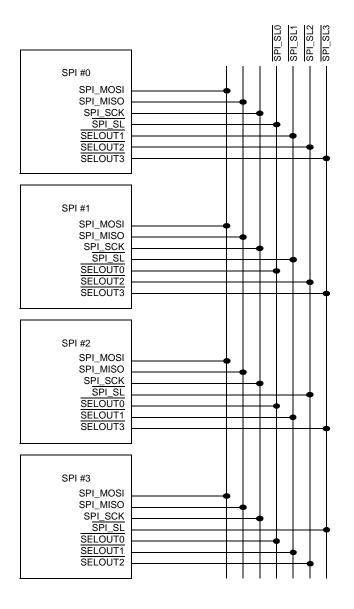

- Based on the system requirements, select the required interfaces using the Pin Mux Tool. The tool spreadsheet confirms all pin availability based on application requirements, such as DDR memory, peripherals, GPIO/IRQ pins, and so on. In addition, this tool validates power supplies and displays all pin mapping based for the application. Contact your local sales office or representative to obtain the Pin Mux Tool. **Figure 6**, **Figure 7** and **Figure 8** show examples of the tool spreadsheet displays.

- Verify that all device interfaces meet the AC specifications listed in the data sheet for the DSP device. Note that the AC specifications are specific with regard to external loads. Also, remember to account for signal propagation delays, clock jitter, and any other factors that can impact signal timing.

| ltem                                                                                                                                                                                                                                                                                    | Configuration Selection                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                         | Mode Selection                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Maple                                                                                                                                                                                                                                                                                   | Used                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| M3 Size                                                                                                                                                                                                                                                                                 | 1056KB                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDM0                                                                                                                                                                                                                                                                                    | Full duplex (RX/TX clock & sync are shared)                                                                | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 links |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDM1                                                                                                                                                                                                                                                                                    | Full duplex (RX/TX clock & sync are shared)                                                                | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 links |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDM2                                                                                                                                                                                                                                                                                    | None                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 link  |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDM2                                                                                                                                                                                                                                                                                    | None                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 link  |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                         |                                                                                                            | INO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TIIDK   |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ethernet1                                                                                                                                                                                                                                                                               | None                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ethernet2                                                                                                                                                                                                                                                                               | SGMII on HSSI port #1                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ethernet Management                                                                                                                                                                                                                                                                     | Yes                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPI                                                                                                                                                                                                                                                                                     | Yes                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RapidIO1                                                                                                                                                                                                                                                                                | None                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RapidIO2                                                                                                                                                                                                                                                                                | 4x 3.125                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PCle                                                                                                                                                                                                                                                                                    | None                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DDR1                                                                                                                                                                                                                                                                                    | DDR2 32bit                                                                                                 | Wit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | h ECC   |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DDR2                                                                                                                                                                                                                                                                                    | DDR2 32bit                                                                                                 | Vit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | h ECC   |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DMA External Request #0                                                                                                                                                                                                                                                                 | Yes                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DMA External Request #1                                                                                                                                                                                                                                                                 | None                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Vart                                                                                                                                                                                                                                                                                    | None                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12C                                                                                                                                                                                                                                                                                     | Yes                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| JTAG                                                                                                                                                                                                                                                                                    | Yes                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| and a second                                                                                                                                                                          | 162                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _       |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                         |                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| The MSC8156                                                                                                                                                                                                                                                                             | 6/4 supports that configuration selection.                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                         | pidlO1 1x lane is active as well as SGMII1 lane<br>t #1 or move BanidlO to nort #1 and use SGM             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                         | pidlO1 1x lane is active as well as SGMII1 lane<br>t #1 or move RapidlO to port #1 and use SGM             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |