## Freescale Semiconductor

**Application Note**

Document Number: AN3424

Rev. 0, 05/2007

# MSC8144 Device Reset Configuration For the MSC8144ADS Board

by Andrew Temple

NCSG DSP Applications

Freescale Semiconductor, Inc.

Austin, TX

This document is a quick configuration reference to help you take advantage of the flexible configuration of the StarCore<sup>TM</sup>-based MSC8144 DSP.

The MSC8144 reset configuration words contain 64 bits to configure 64 clock modes, additional clock sources, peripheral enablement, peripheral and GPIO pin multiplexing, peripheral modes, and boot settings. There are a several ways to configure the device to get the same functionality. For example, there are four ways to boot the device from the I<sup>2</sup>C ROM on the MSC8144ADS board—all of which are described in this application note. Examples illustrate how to configure device reset as well as the SmartDSP OS on the MSC8144 application development system (MSC8144ADS). Related documentation for the MSC8144 device and ADS configuration is referenced in Appendix B.

#### Contents

| 1    | MSC8144ADS Reset Basics                                                              |

|------|--------------------------------------------------------------------------------------|

| 2    | MSC8144 Configuration Sources                                                        |

|      | $2.1 \text{ I}^2\text{C ROM: } (\text{RCW\_SRC}[0:2] = 001 \text{ or } 010) \dots 3$ |

|      | 2.1.1 Programming the I <sup>2</sup> C ROM                                           |

|      | 2.1.2 Altering the Configuration Word Loaded                                         |

|      | into I <sup>2</sup> C ROM                                                            |

|      | 2.2 RC Pins: (RCW_SRC[0:2] = 011)                                                    |

|      | 2.3 Predefined Mode: (RCW_SRC[0:2] = 100,                                            |

|      | 101, 110, 111)5                                                                      |

| 3    | Reading the Reset Configuration Word6                                                |

| 4    | Power-On Reset and Boot Flow                                                         |

| 5    | Example Configurations                                                               |

|      | 5.1 Configure MSC8144ADS to Boot using                                               |

|      | the LEDs Example                                                                     |

|      | 5.1.1 Load the RCW from I <sup>2</sup> C ROM 8                                       |

|      | $5.1.2$ Load the RCW from $I^2$ C ROM (2)                                            |

|      | 5.1.3 Set the RCW using the RC Pins 9                                                |

|      | 5.1.4 Set the RCW using Predefined Settings 10                                       |

|      | 5.2 Configure the MSC8144ADS for SmartDSP OS                                         |

|      | Demonstrations                                                                       |

| 6    | Common MSC8144 Misconceptions                                                        |

| App  | endix ABoot Port Modes and Pin Multiplexing 11                                       |

| Appe | endix B Related Documentation                                                        |

## 1 MSC8144ADS Reset Basics

MSC8144ADS reset terms used throughout this document are as follows:

- Reset configuration word (RCW). The 64 bits used by the MSC8144 to configure clocks, peripherals, booting, and pinning out of reset. For details on the RCW, consult the reset chapter of the MSC8144 reference manual.

- Reset configuration word registers high and low (RCWHR and RCWLR). Two 32-bit registers in the MSC8144 device that contain the reset configuration word.

- Reset configuration word source select pins (RCW\_SRC). Three pins used by an internal multiplexer to select the reset configuration source. The device reads from these pins to fill the contents of the RCW registers. These pins are located on SW4 of the MSC8144ADS board.

- Reset configuration (RC). Pins sampled on reset, which are one of the three configuration sources that can be chosen by RCW\_SRC. These pins are located on SW1, SW3, and SW4 of the MSC8144ADS board.

- *I*<sup>2</sup>*C ROM*. EEPROM on the MSC8144 I<sup>2</sup>C bus for loading the device configuration mode and/or booting executable code.

- *Boot port*. A mode that selects the device boot source if the device is set to run free of the debugger (that is, not in Debug mode) based on bits set in the RCW registers. For quick reference, the table from the MSC8144 reference manual showing the different boot ports is included in Appendix A of this application note.

- *Pin multiplexing*. A mode that determines whether certain GPIO pins are assigned to a peripheral. This mode is required if Ethernet, PCI, or UTOPIA is used. This mode is also selected in the RCW. For quick reference, the table from the MSC8144 reference manual showing the pin multiplexing modes is included in Appendix A.

- Debug mode. Selected by a pin that, on reset, determines whether the device stops and waits for a debugger to connect or begins executing code at the location to which the boot port is pointing. (Not part of the reset configuration word)

# 2 MSC8144 Configuration Sources

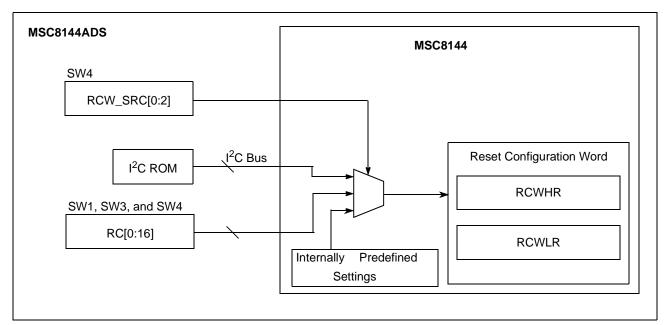

Using the RCW\_SRC multiplexing pins (DIP switch SW4 on the MSC8144ADS), there are three main ways a user can load the contents of the RCW registers (see Figure 1):

- I<sup>2</sup>C ROM

- RC pins

- Predefined mode

Figure 1. Configuration Source Multiplexing

# 2.1 $I^2C$ ROM: (RCW\_SRC[0:2] = 001 or 010)

The only way to gain full access to all bits in RCWLR and RCWHR is to configure the RCW from I<sup>2</sup>C ROM. This configuration gives you access to all 64 clock modes, additional clock options (such as running M3 at the MSC8144 full class speed), and all booting and GPIO multiplexing settings.

# 2.1.1 Programming the I<sup>2</sup>C ROM

There are four ways you can boot the MSC8144 device to run from I<sup>2</sup>C ROM. Remember, booting from I<sup>2</sup>C ROM is different from loading the configuration from I<sup>2</sup>C ROM. The MSC8144 can be configured to load the reset configuration and/or boot from the I<sup>2</sup>C ROM. Programming the I<sup>2</sup>C ROM is currently not supported as a simple GUI feature in CodeWarrior<sup>TM</sup> v3.0 Beta, so you must refer to one of the C projects provided in the example projects folder of the CodeWarrior install directory at:

```

<CodeWarrior Install>\(CodeWarrior Examples)\StarCore Examples\I2CBoot

```

For details on burning, refer to the HOWTO Burn 12C Image.txt.

# 2.1.2 Altering the Configuration Word Loaded into I<sup>2</sup>C ROM

When the I<sup>2</sup>C ROM is programmed, both the boot code and configuration word are burned into I<sup>2</sup>C ROM at the same time, so both are read from data.txt. You can change the configuration word by altering data.txt and rebuilding the burner.mcp project before debugging and executing burner.mcp. The default RCW settings for data.txt are as follows:

```

/* Master Reset Configuration Word Low */

0xFF, 0xFF, 0xFF, 0x00, 0x1F, 0x18, 0x00,

/* Master Reset Configuration Word High */

0xFF, 0xFF, 0xFF, 0x04, 0x6C, 0x18, 0x01,

```

MSC8144 Device Reset Configuration For the MSC8144ADS Board, Rev. 0

#### **MSC8144 Configuration Sources**

There are three bytes of 0xFF padding before the actual contents of the RCW, which is organized from high-order bits to low-order bits. If you refer to the definition of the RCWHR bits in the MSC8144 reference manual, you can see in the preceding lines from data.txt that if RCW\_SRC loads the configuration from  $I^2C$ , the RCW points the boot port back to the  $I^2C$  bus and boots the MSC8144 device from the  $I^2C$  ROM. If you want to boot from the default PCI port, you must alter data.txt as follows:

## 2.2 RC Pins: (RCW\_SRC[0:2] = 011)

For quick switch capability, a subset of the RCW bits can be configured through the RC pins. The settings you can change in this mode are listed in Table 1 and Table 2. In this mode, the following options are hard coded:

- System PLL input to PCI block (PCI block runs at 200 MHz for available clock modes)

- System PLL input to DDR block (DDR block runs at 400 MHz for available clock modes)

- System PLL not input to M3 memory block (M3 block is clocked by PLL2)

- RapidIO<sup>®</sup>/SGMII reference clock is 100 MHz, serializer/deserializer (SerDes) is 1.25 GHz

- RapidIO V<sub>DD</sub> is set to 1.0 V

- PCI and RapidIO host access enabled

- RapidIO prescale timer enable: OCeaN clock is 200 MHz

- SerDes digital filter bandwidth is 200 ppm

- No loopback mode on SerDes

- Watchdog timer is disabled

Table 1. Settings Configurable from DIP Switches (RCW\_SRC[0:2]=011): RCWLR

| RCWLR Bits | RC Pins (DIP Switches) | Usage                                                             |

|------------|------------------------|-------------------------------------------------------------------|

| 19         | RC[16]    RC[3]        | ==0: RapidIO disabled on SerDes<br>==1: RapidIO enabled on SerDes |

| 18         | RC[16]                 | ==0: RapidIO 4x protocol.<br>==1: RapidIO 1x protocol             |

| 17         | RC[16]                 | ==0: Disable SGMII1 on SerDes<br>==1: Enable SGMII1 on SerDes     |

| 16         | RC[16] && RC[3]        | ==0: Disable SGMII2 on SerDes<br>==1: Enable SGMII2 on SerDes     |

| 2–0        | RC[2:0]                | MODCK[2:0],<br><b>Note:</b> MODCK[5:3] = 000                      |

**Note:** Bits are displayed using little-endian format although the device is big-endian. In this mode, the PLL source for PCI and DDR are the system PLL, but M3 remains sourced from PLL2

| RCWHR Bits | RC Pins (DIP Switches) | Usage                                                                                                        |

|------------|------------------------|--------------------------------------------------------------------------------------------------------------|

| 27–26      | RC[15:14]              | Boot port select [4:3]                                                                                       |

| 24–23      | RC[13:12]              | Boot port select [1:0]  Note: Boot Port Select[5] and [2] = 0  Note: For mode definitions, refer to Table 10 |

| 11–10      | RC[11:10]              | Pin Mux[1:0]  Note: See Table 11 in Appendix A                                                               |

| 9–4        | RC[9-4]                | Device ID                                                                                                    |

Table 2. Settings Configurable from DIP Switches SRC[0:2]=011): RCWHR

Note: Bits are displayed using little-endian format although the device is big-endian.

## 2.3 Predefined Mode: (RCW\_SRC[0:2] = 100, 101, 110, 111)

In the predefined modes, RCW is loaded with a fully predefined setting based on only the RCW\_SRC bits. Three predefined modes affect the following:

- Boot port (see Table 10)

- Pin multiplexing (see Table 11)

- · Clock mode

Using these pins is the easiest way to connect a debugger quickly to the device without learning about the full configuration. In the predefined modes, the following options are hardcoded:

- System PLL input to PCI block (PCI block runs at 200 MHz for the available clock modes)

- System PLL input to DDR block (DDR block runs at 400 MHz for the available clock modes)

- System PLL not input to M3 memory block (M3 block is clocked by PLL2)

- RapidIO prescale timer enable: OCeaN clock is 200 MHz

- RapidIO/SGMII reference clock is 100 MHz, SerDes is 1.25 GHz

- RapidIO interface is enabled

- RapidIO uses the 1x protocol

- RapidIO host access enabled

- RapidIO V<sub>DD</sub> is set to 1.0 V

- SGMII1 is enabled on SerDes

- SGMII2 is enabled on SerDes

- PCI host access enabled

- SerDes digital filter BW is 200 ppm

- No loopback mode on SerDes

- Watchdog timer is disabled

#### **Reading the Reset Configuration Word**

For quick reference, the optional settings are provided in Table 8.

**Table 3. Predefined Settings**

| RCW_SRC | MODCK[5:0] (Clock Mode)                                         | PIN MUX[13:10]                        | BOOT PORT[28:23]          |

|---------|-----------------------------------------------------------------|---------------------------------------|---------------------------|

| 100     | 001011<br>(1GHz Core, 333 MHz M3)                               | 0010<br>(PCI Enabled)                 | 000010<br>(Boot from PCI) |

| 101     | 001011<br>(1GHz Core, 333 MHz M3)                               | 0001<br>(Ethernet and UTOPIA Enabled) | 001000<br>(Boot from I2C) |

| 110     | 110101<br>REQUIRES 33.3 MHz CLKIN<br>(800MHz Core, 333 MHz M3)  | 0010<br>(PCI Enabled)                 | 000010<br>(Boot from PCI) |

| 111     | 110101<br>REQUIRES 33.3 MHz CLKIN<br>(800 MHz Core, 333 MHz M3) | 0001<br>(Ethernet and UTOPIA Enabled) | 001000<br>(Boot from I2C) |

Note: Bits here are displayed in little-endian format although the device is big-endian.

# 3 Reading the Reset Configuration Word

Verify that the MSC8144 device is properly configured, as follows:

- 1. connect to the MSC8144ADS using CodeWarrior

- 2. Debug a project.

- Select the View → Registers menu.

The RCW registers (high and low) are located under RESET.

## 4 Power-On Reset and Boot Flow

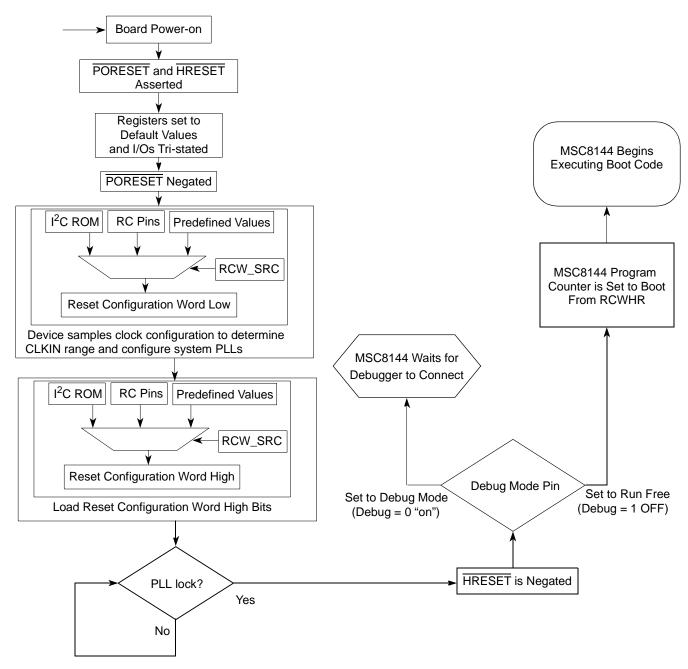

The flow chart in Figure 2 shows how the reset configuration and device boot fit into the main device power-up flow. This flow chart is simplified to show only information necessary to the software programmer testing application code and peripherals on the MSC8144ADS.

# **5** Example Configurations

Because some peripherals—such as the PCI, Ethernet, and UTOPIA—share pins with GPIO, specific configurations are needed to connect to them. This section presents example configurations that are useful to a programmer running applications out of ROM on the MSC8144ADS or working with the SmartDSP OS demonstrations.

Figure 2. MSC8144 Power-on Reset and Boot

# 5.1 Configure MSC8144ADS to Boot using the LEDs Example

If DIP switches malfunction while you are showing a demonstration on a board, the MSC8144ADS has many ways around this kind of configuration problem that do not require board reprogramming. Consider the case of bootloading from the I<sup>2</sup>C ROM on the MSC8144ADS. With the standard 66.667 MHz crystal oscillator on the MSC8144ADS board, there are four different ways to boot out of I<sup>2</sup>C ROM. The differences lie in how the MSC8144 DSP reads the reset configuration word into the RCWHR and RCWLR.

MSC8144 Device Reset Configuration For the MSC8144ADS Board, Rev. 0

#### **Example Configurations**

## 5.1.1 Load the RCW from I<sup>2</sup>C ROM

Because the bootloader and LED example must be loaded into the  $I^2C$  ROM, we start with loading the configuration from  $I^2C$  ROM as well:

- 1. As noted in Section 2.1.1, "Programming the I<sup>2</sup>C ROM, refer to the CodeWarrior examples for the steps in programming the I<sup>2</sup>C ROM, but stop before Step 5.

- 2. Before loading burner.mcp, you must alter the RCW being programmed to I<sup>2</sup>C ROM, so open data.txt.

- 3. Alter the data.txt RCWHR so that the boot port points to I<sup>2</sup>C ROM. Refer to Table 10 to see which boot port mode is required. The configuration should look like this:

- 4. Save data.txt.

- 5. Re-build burner.mcp in CodeWarrior data.txt is an include file to burner.mcp.

- 6. Verify that the MSC8144ADS DIP switches are in a known configuration. Table 4 shows an example default configuration:

|     | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----|---|---|---|---|---|---|---|---|

| SW1 | х | х | х | х | х | х | х | х |

| SW2 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| SW3 | х | х | х | х | 0 | 1 | 1 | 1 |

| SW4 | 0 | 1 | 0 | Х | Х | Х | Х | Х |

Table 4. Default DIP Switch Settings Configured from I<sup>2</sup>C ROM

**Note:** Logic 1 = OFF on the MSC8144ADS

- 7. Power on the MSC8144ADS board and run burner.mcp until it completes.

- 8. Power off the board.

- 9. Now that the  $I^2C$  ROM is set to load RCWHR with boot port = I2C ROM as shown in the flowchart in Section 4, "Power-On Reset and Boot Flow, you must use the DIP switches to ensure the following if the device is to boot from  $I^2C$  ROM:

- RCW\_SRC loads the configuration from  $I^2C$  ROM (see Section 2.1, " $I^2C$  ROM: (RCW\_SRC[0:2] = 001 or 010))

- The MSC8144 runs the boot code (not in debug mode), as highlighted in bold on SW2 in Table 5.

|     | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----|---|---|---|---|---|---|---|---|

| SW1 | х | х | х | х | х | х | х | х |

| SW2 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| SW3 | х | х | х | х | 0 | 1 | 1 | 1 |

| SW4 | 0 | 1 | 0 | х | х | х | х | х |

Table 5. DIP Switch Setting: Configure and Boot from I<sup>2</sup>C ROM

**Note:** Logic 1 = OFF on the MSC8144ADS.

- 10. Power on the board.

- 11. The LEDs should begin flashing.

# 5.1.2 Load the RCW from $I^2C$ ROM (2)

There are two RCW\_SRC settings to load the RCW from  $I^2C$  ROM, RCW\_SRC[0:2] = 001 or 010. The difference between them is the minimum and maximum CLKIN frequency. If the crystal oscillator on the ADS (CLKIN) is between 25 and 100 MHz, RCW\_SRC = 001 mode is expected to work. RCW\_SRC is expected to work with a CLKIN value between 44 and 133 MHz. Because the MSC8144ADS uses a 66 MHz crystal, you can use both load settings. Also, because you have already programmed the  $I^2C$  ROM, the only remaining step is to change the RCW\_SRC DIP switches to test this load option, as shown in Table 6. Re-power the board and verify that the LED program still boots and flashes LEDs.

Table 6. DIP Switch Setting: Configure and Boot from I<sup>2</sup>C ROM (2)

|     | 1        | 2        | 3 | 4 | 5 | 6 | 7 | 8 |

|-----|----------|----------|---|---|---|---|---|---|

| SW1 | х        | х        | х | х | х | х | х | х |

| SW2 | 0        | 1        | 1 | 1 | 1 | 1 | 1 | 1 |

| SW3 | х        | х        | х | х | 0 | 1 | 1 | 1 |

| SW4 | <u>0</u> | <u>0</u> | 1 | х | х | х | х | х |

Note: Logical 1 = OFF on the MSC8144ADS

## 5.1.3 Set the RCW using the RC Pins

Because the  $I^2C$  ROM already has a bootloader and example program in it, you need only verify the following to ensure that the MSC8144 can load and run from  $I^2C$  ROM:

- RCW SRC[0:2] = 011 points the MSC8144 to load the RCW from the RC pins.

- RC[14] = 1, RC[15,13,12] = 0 so that the boot port points to  $I^2C$  ROM

- Debug mode is OFF (logic 1)

Referring to Table 1 and Table 2, configure the DIP switches as shown in Table 7.

Table 7. DIP Switch Settings Configured from the RC Pins, With Boot from the I<sup>2</sup>C ROM

|     | 1        | 2 | 3        | 4 | 5 | 6 | 7 | 8        |

|-----|----------|---|----------|---|---|---|---|----------|

| SW1 | 0        | 0 | 0        | 0 | 0 | 1 | 1 | <u>0</u> |

| SW2 | 0        | 1 | 1        | 1 | 1 | 1 | 1 | 1        |

| SW3 | <u>0</u> | 1 | <u>0</u> | 1 | 0 | 1 | 1 | 1        |

| SW4 | <u>0</u> | 1 | 1        | 0 | 0 | 0 | 1 | 0        |

Note: Logic 1 = OFF on the MSC8144ADS

After the DIP switch settings match those in Table 7, cycle power on the MSC8144ADS board and boot the LED demonstration again through this new avenue.

## 5.1.4 Set the RCW using Predefined Settings

As Table 3 shows, using predefined mode RCW\_SRC = 101 sets the RCW to point the boot port to  $I^2C$  ROM. Therefore, with the  $I^2C$  ROM already loaded with code, you need only complete the following steps:

- 1. Verify that RCW\_SRC is configured to a value of 0b101.

- 2. Verify that the device is set to run free (Debug mode = OFF, which is a logic 1).

Table 8. DIP Switch Settings Configured from Predefined Settings, with Boot from I<sup>2</sup>C ROM

|     | 1 | 2        | 3 | 4 | 5 | 6 | 7 | 8 |

|-----|---|----------|---|---|---|---|---|---|

| SW1 | х | х        | х | х | х | х | х | х |

| SW2 | 0 | 1        | 1 | 1 | 1 | 1 | 1 | 1 |

| SW3 | х | х        | х | х | 0 | 1 | 1 | 1 |

| SW4 | 1 | <u>0</u> | 1 | Х | Х | Х | х | х |

**Note:** Logic 1 = OFF on the MSC8144ADS

There is a fifth setting for RCW\_SRC to make the MSC8144 boot from I<sup>2</sup>C ROM, but it requires a different board oscillator, so it is not discussed here.

## 5.2 Configure the MSC8144ADS for SmartDSP OS Demonstrations

The SmartDSP OS and example MSC8144ADS demonstrations are optionally installed along with CodeWarrior. To select this option, click YES to Install SmartDSP OS during CodeWarrior installation. The demonstrations of Ethernet (UEC, NET, and NET\_PATTERN) require additional hardware configuration for pin multiplexing. That is, in the SmartDSP OS documentation, all of these demonstrations request the user to alter the RCW to pin multiplexing mode 6.

As described in Section 5.1.1, "Load the RCW from I<sup>2</sup>C ROM, the I<sup>2</sup>C ROM must be re-programmed because pin multiplexing mode 6 is not available to the other configurations. Repeat the procedure in Section 5.1.1, but this time ensure that the configuration portion of data.txt matches the following:

/\* Master Reset Configuration Word Low \*/

0xFF, 0xFF, 0xFF, 0x00, 0x1F, 0x18, 0x00,

MSC8144 Device Reset Configuration For the MSC8144ADS Board, Rev. 0

```

/* Master Reset Configuration Word High */

0xFF, 0xFF, 0xFF, 0x04, 0x6C, 0x18, 0x01,

```

After the I<sup>2</sup>C ROM is programmed, the RCW\_SRC DIP switches should be set to load the RCW from the I<sup>2</sup>C ROM, and the board should be left in Debug mode. Therefore, the DIP switches are configured as shown in Table 9.

1 2 5 7 8 SW<sub>1</sub> Х Х Х Х Х Х Х Х SW<sub>2</sub> 0 1 1 0 1 1 1 1 SW3 0 1 1 1 Х Х SW4 0 1 0 Х Х Х

Table 9. DIP Switch Settings: SmartDSP OS Demonstrations for Ethernet

Note: Logic 1 = OFF on the MSC8144ADS.

At this point, the MSC8144 is configured to run with the SmartDSP OS demonstrations.

# 6 Common MSC8144 Misconceptions

Aspects of the MSC8144 that may cause confusion when the MSC8144ADS is configured are as follows:

- The MSC8144 DSP and most Freescale devices are big-endian devices, meaning that the bits are organized from low-order to high. For example, a 32-bit register is organized from bit 0 to 31 rather than from bit 31 to 0. For purposes of clarity, this document states the bit order each time a variable is listed. For example: "RCW\_SRC[0:2] lists bits from low order to high."

- On the MSC8144ADS, a DIP switch turned to OFF = logic 1.

- Booting and configuring from I<sup>2</sup>C ROM should not be confused with each other. They are two different procedures. *Booting* from I<sup>2</sup>C ROM can be done without *configuring* from I<sup>2</sup>C ROM and *vice versa*, as illustrated in the examples presented in this document.

# Appendix A Boot Port Modes and Pin Multiplexing

In this appendix, Table 10 presents the boot port modes and Table 11 presents the pin multiplexing configurations.

| Boot Port | Description             | BPRT[5:0] |

|-----------|-------------------------|-----------|

| PCI       | No DDR                  | 000000    |

|           | Single 32MB DDR         | 000001    |

|           | 256 Mbyte DDR (Default) | 000010    |

|           | Single 64 Mbyte DDR     | 000011    |

|           | Single 128 Mbyte DDR    | 000100    |

|           | 512 Mbyte DDR           | 000101    |

**Table 10. Boot Port Modes**

MSC8144 Device Reset Configuration For the MSC8144ADS Board, Rev. 0

## **Boot Port Modes and Pin Multiplexing**

**Table 10. Boot Port Modes**

| Boot Port                      | Description                    | BPRT[5:0] |

|--------------------------------|--------------------------------|-----------|

| I <sup>2</sup> C               | Boot over I <sup>2</sup> C bus | 001000    |

| SRIO                           | No I <sup>2</sup> C            | 001001    |

|                                | with I <sup>2</sup> C          | 001010    |

| Ethernet1 without              | SMII                           | 001111    |

| I <sup>2</sup> C               | RMII                           | 010000    |

|                                | RGMII                          | 010001    |

|                                | MII                            | 010010    |

|                                | SGMII                          | 010011    |

| Ethernet1 and I <sup>2</sup> C | SMII                           | 010100    |

|                                | RMII                           | 010101    |

|                                | RGMII                          | 010110    |

|                                | MII                            | 010111    |

|                                | SGMII                          | 011000    |

**Table 11. GPIO Pin Multiplexing Configurations**

|      |                  |                  | I/O Mo           | de (PIN_MUX      | field lowest fo  | ur bits)         |                  |                  |  |  |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|--|

| GPIO | Mode 0<br>(0000) | Mode 1<br>(0001) | Mode 2<br>(0010) | Mode 3<br>(0011) | Mode 4<br>(0100) | Mode 5<br>(0101) | Mode 6<br>(0110) | Mode 7<br>(0111) |  |  |

| 0    | GPIO             |                  |                  |                  |                  |                  |                  |                  |  |  |

| 1    |                  |                  |                  | GI               | PIO              |                  |                  |                  |  |  |

| 2    |                  |                  |                  | GI               | PIO              |                  |                  |                  |  |  |

| 3    |                  |                  |                  | GI               | PIO              |                  |                  |                  |  |  |

| 4    |                  | GPIO             |                  | PCI GP           |                  |                  | GPIO             | GPIO             |  |  |

| 5    |                  | GPIO             |                  | Р                | CI               | GPIO             |                  |                  |  |  |

| 6    |                  | GPIO             |                  | Р                | CI               | GPIO             |                  |                  |  |  |

| 7    |                  | GPIO             |                  | Р                | PCI GPIO         |                  |                  | PIO              |  |  |

| 8    |                  | GPIO PCI GPIO    |                  |                  |                  |                  |                  |                  |  |  |

| 9    |                  | GPIO             |                  | Р                | CI               |                  | GPIO             |                  |  |  |

| 10   |                  | GPIO             |                  | Р                | CI               |                  | GPIO             |                  |  |  |

| 11   |                  | GPIO             |                  | PCI GPIO         |                  |                  | GPIO             | PIO              |  |  |

| 12   | GPIO PCI GPIO    |                  |                  |                  |                  |                  |                  |                  |  |  |

| 13   |                  |                  |                  | GI               | PIO              |                  |                  |                  |  |  |

| 14   |                  |                  |                  | GI               | PIO              |                  |                  |                  |  |  |

MSC8144 Device Reset Configuration For the MSC8144ADS Board, Rev. 0

Table 11. GPIO Pin Multiplexing Configurations (continued) (continued)

| GPIO | I/O Mode (PIN_MUX field lowest four bits) |                  |                  |                  |                  |                  |                  |                  |

|------|-------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|      | Mode 0<br>(0000)                          | Mode 1<br>(0001) | Mode 2<br>(0010) | Mode 3<br>(0011) | Mode 4<br>(0100) | Mode 5<br>(0101) | Mode 6<br>(0110) | Mode 7<br>(0111) |

| 15   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 16   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 17   | UTC                                       | PIA              | GPIO             | UTOPIA           | PCI              | UTOPIA           |                  |                  |

| 18   | GPIO                                      |                  |                  |                  | PCI              | GPIO U1          |                  | UTOPIA           |

| 19   | GPIO                                      |                  |                  |                  | PCI              | GPIO             |                  | UTOPIA           |

| 20   | GPIO                                      |                  |                  |                  | PCI              | GPIO UTOPIA      |                  | UTOPIA           |

| 21   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 22   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 23   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 24   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 25   | GPIO                                      | GPIO Ethernet    |                  | PCI              |                  | GPIO             | Ethernet         | GPIO             |

| 26   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 27   | GPIO                                      |                  |                  |                  |                  |                  |                  |                  |

| 28   | GPIO                                      |                  |                  | PCI              |                  | GPIO             |                  |                  |

| 29   | GPIO                                      |                  | PCI              |                  | GPIO             |                  |                  |                  |

| 30   | GPIO                                      |                  |                  | PCI              |                  | GPIO             |                  |                  |

| 31   | GPIO                                      |                  |                  | PCI              |                  | GPIO             |                  |                  |

**Note:** GPIO includes any signal configured by the GPIO configuration registers, including GPI, GPO,  $\overline{IRQ}$ , and other dedicated functions.

# Appendix B Further Reading

Related documentation for the MSC8144 device and the MSC8144ADS currently available on the Freescale web site and through the Literature Distribution Center is as follows:

- MSC8144ADS Processor Board Reference Manual (MSC8144ADSRM)

- MSC8144ADS Hardware Getting Started Guide

- MSC8144 Reference Manual: Quad Core Media Signal Processor (MSC8144RM)

- Using an I<sup>2</sup>C EEPROM During MSC814x Initialization (AN3421)

**Further Reading**

## THIS PAGE INTENTIONALLY LEFT BLANK

## THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>TM</sup>, the Freescale logo, and StarCore are trademarks of Freescale Semiconductor, Inc. CodeWarrior is a trademark or registered trademark of Freescale Semiconductor, Inc. in the United States and/or other countries. RapidIO is a registered trademark of the RapidIO Trade Association. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

Document Number: AN3424

Rev. 0 05/2007