# Freescale Semiconductor

**Application Note**

Document Number: AN2680

Rev. 1, 10/2005

# **EIM Asynchronous Timing Parameters**

MC9328MX1, MC9328MXL, and MC9328MXS

By Michael Kjar

# 1 Abstract

This document provides a detailed overview of the i.MX applications processor's External Interface Module (EIM), specifically analyzing the asynchronous timing parameter bit settings of the EIM chip-select control register. This analysis provides the user a better understanding of how these bits are used and how they affect the timing parameters of several of the EIM's control signals, to better enable the system design in interfacing the i.MX processor's EIM to external memories and peripherals. An overview of the EIM and its chip-select control registers is provided, followed by several example waveforms to illustrate how changing these bit settings affects the asynchronous timing parameters of the external control signals. The aim of this document is to supplement the EIM information provided in the i.MX reference manuals and data sheets.

This document applies to the following i.MX devices, collectively called i.MX throughout:

- MC9328MX1

- MC9328MXL

- MC9328MXS

### **Contents**

| 1 | Abstract                               |

|---|----------------------------------------|

| 2 | Overview of the i.MX EIM               |

| 3 | EIM External Bus Asynchronous Waveform |

|   | Examples                               |

| 4 | References29                           |

| 5 | Revision History29                     |

# 2 Overview of the i.MX EIM

The i.MX is an application processor targeted for low power, portable applications. Part of the rich feature set of the i.MX includes the on-chip External Interface Module (EIM). The EIM may be used to interfacing the i.MX to external memory such as SRAM and NOR Flash (asynchronous, synchronous/burst, and page mode styles), as well as interfacing to external peripheral devices such as the ST16C2552 Dual UART chip. The i.MX EIM includes these distinctive features:

- Six chip selects for external devices:  $\overline{CS}[0]$ , covering a range of 32 Mbyte, and  $\overline{CS}[1]$ – $\overline{CS}[5]$ , covering a range of 16 Mbyte each

- Selectable protection for each chip select

- Reset programmable data port size for  $\overline{CS}[0]$

- Programmable data port size for each chip select

- Address suppression during burst mode operations

- Synchronous burst mode support for burst flash devices

- Programmable wait-state generator for each chip select

- Supports big endian and little endian modes of operation

# 2.1 EIM Interface Signals

The EIM interface signals provide communication and control pathways between external devices and the i.MX processor.

The Table 1 summarizes each of these signals and their use. This document covers the following adjustable control signals:  $\overline{CS}[5:0]$ ,  $\overline{EB}[3:0]$ ,  $\overline{OE}$ , and  $R/\overline{W}$ , where the signals BCLK,  $\overline{LBA}$ , and  $\overline{ECB}$  are specific to the burst and page style interfaces and will not be covered here. However, both BCLK and  $\overline{LBA}$  are shown in the example waveforms for illustrative purposes. For more information on these signals please refer to the EIM section of the i.MX reference manual.

Table 1. EIM Interface Signals

| i.MX EIM<br>Pin Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|--|

| D[31:0]              | External 32-bit data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |  |  |  |  |  |  |

| A[24:0]              | External address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |  |  |  |  |  |  |

| CS[5:0]              | Active low external chip selects.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output |  |  |  |  |  |  |

| DTACK                | External input data acknowledge signal for $\overline{\text{CS}}[5]$ .                                                                                                                                                                                                                                                                                                                                                                                                                            | Input  |  |  |  |  |  |  |

| EB[3:0]              | Active low external enable bytes signals. $\overline{EB}[0]$ controls D[31:24], $\overline{EB}[1]$ controls D[23:16], $\overline{EB}[2]$ controls D[15:8], and $\overline{EB}[3]$ controls D[7:0].                                                                                                                                                                                                                                                                                                | Output |  |  |  |  |  |  |

| OE                   | Active low output enable for external data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output |  |  |  |  |  |  |

| R/W                  | Indicates whether external access is a read (high) or write (low) cycle. The assertion timing of this signal for write accesses is not configurable. Though it can be connected to the write enable of memories and other devices, for those devices that require any timing delay of the write enable assertion/de-assertion times, the user may use one the of EB[3:0] signals as their timing may be affected by the WEA and WEN bit settings (see Section 2.2, "i.MX EIM Register Overview.") | Output |  |  |  |  |  |  |

| i.MX EIM<br>Pin Name | Function                                                                                                                   |        |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| BCLK                 | Clock for external synchronous memories (such as burst flash). May be programmed to run continuously as a reference clock. | Output |  |  |  |

| LBA                  | Active low signal sent to flash device causing the external device to latch the address.                                   | Output |  |  |  |

| ECB                  | Input signal identifies when to end an external burst access (as in the case for burst flash).                             | Input  |  |  |  |

In this document, some signals may be denoted differently in text then in the example waveforms. For example, the EIM read/write signal,  $R/\overline{W}$ , is denoted as  $R/\overline{W}$  in the text, but in the waveform examples, it may be denoted simply as RW. In other instances, the EIM enable byte signals,  $\overline{EB}[3:0]$ , may simply be referred to as  $\overline{EB}$ , or in the case of the example waveforms, the enable byte is denoted as EB3 for simplicity.

# 2.2 i.MX EIM Register Overview

The EIM module includes thirteen user-accessible 32-bit registers. There is a common register called the EIM Configuration Register that contains control bits that configure the EIM for certain operation modes. The other twelve registers are pairs of control registers for each chip select. The layout of the control register is slightly different for the  $\overline{CS}[0]$  register output because  $\overline{CS}[0]$  does not support the programmable output function Pin Assert (PA), bit 1. Also, the DSIZ the bits of  $\overline{CS}[0]$  register are configurable upon reset, since  $\overline{CS}[0]$  is a bootable chip select. The settings of these DSIZ bits are determined by the setting of the BOOT[3:0] signals on reset. Refer to the i.MX reference manual for more details. These registers are accessible only in supervisor mode with word (32-bit) reads and writes.

The 64 bits of control are divided into two registers, Chip Select Upper Control Register and Chip Select Lower Control Register.

- Bits [63:32] are located in Chip Select Upper Control Register.

- Bits [31:0] are located in Chip Select Lower Control Register.

Though the reference manual provides these chip select control register bit definitions, this document attempts to provide more detail to these bit settings along with references to the external waveforms given later in the document. This document concentrates solely on the asynchronous bit timings, specifically the following bit settings: CNC (bits 47 and 46), WSC (bits 45 through 40), WWS (bits 38 through 36), EDC (bits 35 through 32), OEA (bits 31 through 28), OEN (bits 27 through 24), WEA (bits 23 through 20), WEN (bits 19 through 16), and CSA (bits 15 through 12). The bit settings not covered in detail in this document are related to the synchronous and page mode timings, specifically the following bits: BCD, BCS, PSZ, PME, SYNC, and DOL, although a description of these bits is provided in Table 1.

#### Overview of the i.MX EIM

| CS0U<br>CS1U<br>CS2U<br>CS3U<br>CS4U<br>CS5U |                                                                                                                                                                                                 |                    |          |            |          | (      | Chip Sel<br>Chip Sel<br>Chip Sel<br>Chip Sel<br>Chip Sel | ect 1 U<br>ect 2 U<br>ect 3 U<br>ect 4 U | pper C<br>pper C<br>pper C<br>pper C | Control<br>Control<br>Control<br>Control | Registe<br>Registe<br>Registe<br>Registe | er<br>er<br>er<br>er |         | 0x002<br>0x002<br>0x002<br>0x002<br>0x002 | 2000<br>2001<br>2001<br>2002 | 8<br>0<br>8<br>0 |        |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------------|----------|--------|----------------------------------------------------------|------------------------------------------|--------------------------------------|------------------------------------------|------------------------------------------|----------------------|---------|-------------------------------------------|------------------------------|------------------|--------|

| BIT                                          |                                                                                                                                                                                                 | 63                 | 62       | 61         | 60       | 59     | 58                                                       | 57                                       | 56                                   | 55                                       | 54                                       | 53                   | 52      | 51                                        | 50                           | 49               | 48     |

|                                              | DTAC                                                                                                                                                                                            | K_SEL <sup>1</sup> |          | ВС         | D        |        | ВС                                                       | S                                        |                                      | PS                                       | SZ                                       | PME                  | SYNC    |                                           |                              | OL               |        |

| TYPE                                         | 1                                                                                                                                                                                               | ſW                 | r        | rw         | rw       | rw     | rw                                                       | rw                                       | rw                                   | rw                                       | rw                                       | rw                   | rw      | rw                                        | rw                           | rw               | rw     |

| CS0U<br>CS1-5U                               |                                                                                                                                                                                                 | 0<br>0             | 0<br>0   | 0<br>0     | 0<br>0   | 0<br>0 | 0<br>0                                                   | 0                                        | 0<br>0                               | 0<br>0                                   | 0<br>0                                   | 0<br>0               | 0       | 0                                         | 0                            | 0                | 0      |

| RESET                                        |                                                                                                                                                                                                 |                    |          |            |          |        |                                                          | 0x000<br>0X0000                          | 00 (CSC<br>0 (CS1-                   |                                          |                                          |                      |         |                                           |                              |                  |        |

| BIT                                          |                                                                                                                                                                                                 | 47                 | 46       | 45         | 44       | 43     | 42                                                       | 41                                       | 40                                   | 39                                       | 38                                       | 37                   | 36      | 35                                        | 34                           | 33               | 32     |

|                                              |                                                                                                                                                                                                 | CNC                |          |            |          | W      | SC                                                       |                                          |                                      |                                          |                                          | wws                  |         |                                           | E                            | DC               |        |

| TYPE                                         | 1                                                                                                                                                                                               | rw                 | rw       | rw         | rw       | rw     | rw                                                       | rw                                       | rw                                   | r                                        | rw                                       | rw                   | rw      | rw                                        | rw                           | rw               | rw     |

| CS0U                                         |                                                                                                                                                                                                 | 0<br>0             | 0<br>0   | 1<br>0     | 1<br>0   | 1<br>0 | 1<br>0                                                   | 1<br>0                                   | 0<br>0                               | 0<br>0                                   | 0<br>0                                   | 0<br>0               | 0<br>0  | 0<br>0                                    | 0                            | 0                | 0<br>0 |

| CS1-5U                                       |                                                                                                                                                                                                 | U                  | U        | U          | U        | U      | U                                                        |                                          | 0<br>00 (CS0                         |                                          | U                                        | U                    | U       | U                                         | U                            | U                | U      |

| RESET                                        |                                                                                                                                                                                                 |                    |          |            |          |        |                                                          |                                          | ) (CS1-                              |                                          |                                          |                      |         |                                           |                              |                  |        |

|                                              | <sup>1</sup> —Bit (                                                                                                                                                                             | 63 of CS           | 5U regis | ster is de | efined a | s DTAC | K_SEL.                                                   | Bit 63 is                                | reserve                              | ed for C                                 | S0U, C                                   | S1U, CS2             | 2U, CS3 | U, CS4                                    | ·U.                          |                  |        |

| CS0L<br>CS1L<br>CS2L<br>CS3L<br>CS4L<br>CS5L | Chip Select 1 Lower Control Register 0x0022000C Chip Select 2 Lower Control Register 0x00220014 Chip Select 3 Lower Control Register 0x0022001C Chip Select 4 Lower Control Register 0x00220024 |                    |          |            |          |        |                                                          |                                          |                                      |                                          |                                          |                      |         |                                           |                              |                  |        |

| BIT                                          | 31                                                                                                                                                                                              | 30                 | 29       | 28         | 27       | 26     | 25                                                       | 24                                       | 23                                   | 22                                       | 21                                       | 20                   | 19      | 18                                        | 3                            | 17               | 16     |

|                                              |                                                                                                                                                                                                 | OE                 | ΞA       |            |          | C      | DEN                                                      |                                          |                                      | ٧                                        | WEA                                      |                      |         |                                           | WEN                          | l                |        |

| TYPE                                         | rw                                                                                                                                                                                              | rw                 | rw       | rw         | rw       | rw     | rw                                                       | rw                                       | rw                                   | rw                                       | rw                                       | rw                   | rw      | rv                                        | V                            | rw               | rw     |

| CS0L                                         | 0                                                                                                                                                                                               | 0                  | 0        | 0          | 0        | 0      | 0                                                        | 0                                        | 0                                    | 0                                        | 0                                        | 0                    | 0       | C                                         |                              | 0                | 0      |

| CS1-5L                                       | 0                                                                                                                                                                                               | 0                  | 0        | 0          | 0        | 0      | 0                                                        | 0                                        | 0                                    | 0                                        | 0                                        | 0                    | 0       | C                                         | )                            | 0                | 0      |

| RESET                                        | 0x0000 (CS0L)<br>0x0000 (CS1–5L)                                                                                                                                                                |                    |          |            |          |        |                                                          |                                          |                                      |                                          |                                          |                      |         |                                           |                              |                  |        |

| BIT                                          | 15                                                                                                                                                                                              | 14                 | 13       | 12         | 11       | 10     | 9                                                        | 8                                        | 7                                    | 6                                        | 5                                        | 4                    | 3       | 2                                         | !                            | 1                | 0      |

|                                              |                                                                                                                                                                                                 | CS                 | SA       |            | EBC      |        | DSZ                                                      |                                          |                                      | SP                                       |                                          | WP                   |         |                                           |                              | PA <sup>2</sup>  | CSEN   |

| TYPE                                         | rw                                                                                                                                                                                              | rw                 | rw       | rw         | rw       | rw     | rw                                                       | rw                                       | r                                    | rw                                       | r                                        | rw                   | r       | r                                         |                              | rw               | rw     |

| CS0L<br>CS1–5L                               | 0<br>0                                                                                                                                                                                          | 0<br>0             | 0<br>0   | 0<br>0     | 1<br>1   | *<br>0 | *<br>0                                                   | *<br>0                                   | 0<br>0                               | 0<br>0                                   | 0<br>0                                   | 0<br>0               | 0<br>0  | C                                         |                              | 0<br>1           | 1<br>0 |

| RESET                                        | 0x0*01 <sup>1</sup> (CS0L)<br>0x0802 (CS1–5L)                                                                                                                                                   |                    |          |            |          |        |                                                          |                                          |                                      |                                          |                                          |                      |         |                                           |                              |                  |        |

$<sup>^1</sup>$ —The DSIZ bits are configurable upon reset, dependent upon the BOOT[3:0] signal settings.  $^2$ —PA for  $\overline{\text{CS}}[1]$  to  $\overline{\text{CS}}[5]$  only, and "rw". Reserved for  $\overline{\text{CS}}[0]$  (read only).

### EIM Asynchronous Timing Parameters Application Note, Rev. 1

### **Table 2. Chip Select Control Registers Description**

| Name                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Settings                                                                                                     |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Reserved/<br>DTACK_<br>SEL<br>Bit 63 | Reserved—This bit is reserved and should read 0 for CS0–CS4.  DTACK_SEL—This bit is used to select the functionality of the DTACK input signal for CS[5]. To select the DTACK functionality on CS[5], the WSC bits for CS[5] must be set to 1111111.  Note: Due to current chip errata, DTACK_SEL can only be set to 1 for Compact Flash/PCMCIA functionality and requires the use of an external D flip-flop or other mechanism to extend the OE negation (assertion) time until the CS[5] cycle is completed. Refer to the latest chip errata found at www.freescale.com/imx | Reserved for CS0–CS4  CS5: 0 = Reserved 1 = Compact Flash/PCMCIA wait function                               |  |  |  |

| Reserved<br>Bit 62                   | Reserved—This bit is reserved and should read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |  |  |  |

| BCD<br>Bits 61–60                    | Burst Clock Divisor—Contains the value used to program the burst clock divisor and is used for synchronous (burst) style interfaces. Refer to the i.MX reference manual for more information on the burst clock divisors. When the BCM bit is set (BCM = 1) in the EIM configuration register, BCD is ignored.  BCD is cleared by a hardware reset.                                                                                                                                                                                                                            | 00 = Divisor is 1<br>01 = Divisor is 2<br>10 = Divisor is 3<br>11 = Divisor is 4                             |  |  |  |

| BCS<br>Bits 59–56                    | Burst Clock Start—Determines the number of half cycles after LBA assertion before the first rising edge of BCLK is seen. A value of 0 results in a half clock delay, not an immediate assertion. This is used in conjunction with synchronous (burst) style interfaces. When the BCM bit is set (BCM = 1) in the WEIM configuration register, this overrides the BCS bits.  BCS is cleared by a hardware reset.                                                                                                                                                                | 0000 = 1 half cycle before BCLK<br>0001 = 2 half cycles before BCLK<br><br>1111 = 16 half cycles before BCLK |  |  |  |

| PSZ<br>Bits 55–54                    | Page Size—Indicates the number of words (where "word" is defined by the port size or DSIZ bits) in a page in memory. This ensures that the WEIM does not burst pass a page boundary when the PME bit is set. This is used in conjunction with page-mode style interfaces. PSZ is cleared by a hardware reset.                                                                                                                                                                                                                                                                  | 00 = 4 words in a page<br>01 = 8 words in a page<br>10 = 16 words in a page<br>11 = 32 words in a page       |  |  |  |

| PME<br>Bit 53                        | Page Mode Emulation—Enables/Disables page mode emulation in burst mode. When PME is set, the external address asserts for each piece of data requested. Additionally, the LBA and BCLK signals behave as they do when an asynchronous access is performed. This is used in conjunction with page-mode style interfaces.  PME is cleared by a hardware reset.                                                                                                                                                                                                                   | 0 = Disables page mode emulation<br>1 = Enables page mode emulation                                          |  |  |  |

| SYNC<br>Bit 52                       | Synchronous Burst Mode Enable—Enables/Disables synchronous burst mode. When enabled, the EIM is capable of interfacing to burstable (synchronous) flash devices through additional burst control signals: BCLK, LBA, and ECB. The sequencing of these additional I/Os is controlled by other EIM configuration register bit settings as defined below. This is used in conjunction with synchronous (burst) style interfaces.                                                                                                                                                  | 0 = Disables synchronous burst mode<br>1 = Enables synchronous burst mode                                    |  |  |  |

#### Overview of the i.MX EIM

### Table 2. Chip Select Control Registers Description (continued)

| Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOL<br>Bits 51–48 | Data Output Length—Specifies the expected number of system clock (HCLK) cycles required for burst read data to be valid on the data bus before it is latched by the EIM. The reset value specifies that burst data is held for a minimum of two system clock periods. As system clock frequencies increase, it may become necessary to delay sampling the data for multiple system clock periods in order to meet burst flash max frequency specifications and/or EIM data setup time requirements. DOL has no effect on EIM data latching when SYNC = 0. This is used in conjunction with synchronous (burst) style interfaces.  DOL is cleared by a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000 = 2 system clock delay<br>0001 = 2 system clock delay<br>0010 = 3 system clock delay<br>0011 = 4 system clock delay<br><br>1111 = 16 system clock delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

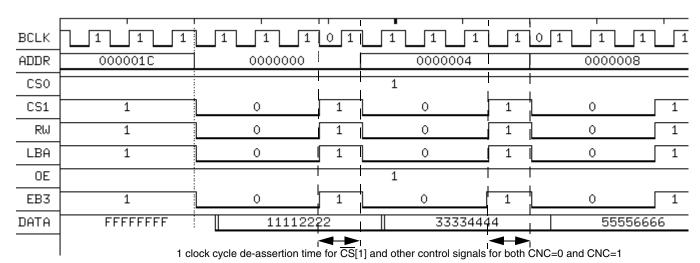

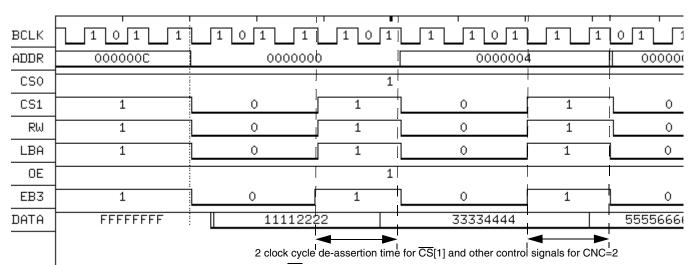

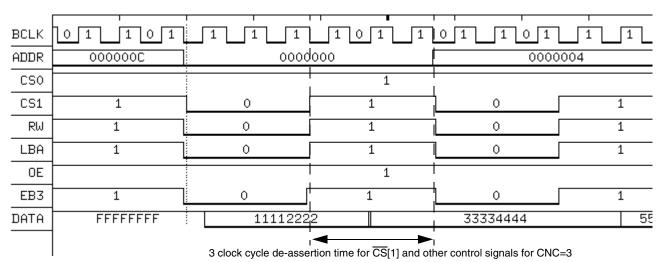

| CNC<br>Bits 47–46 | Chip Select Negation Clock Cycles—Specifies the minimum number of system clock (HCLK) cycles a chip select must remain de-asserted after it is de-asserted. The CNC will only affect the chip select de-assertion once the chip select has de-asserted, in other words, for external back-to-back accesses where the chip select does not de-assert (in instances where it stays asserted), CNC has no affect. An example of how the CNC bit setting affects the chip select de-assertion time can be seen in Figure 16, Figure 17, and Figure 18.  CNC has no effect on write accesses when any CSA bit is set. CNC is cleared by a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00 = Minimum de-assertion is 0 clock cycle<br>01 = Minimum de-assertion is 1 clock cycle<br>10 = Minimum de-assertion is 2 clock cycles<br>11 = Minimum de-assertion is 3 clock cycles                                                                                                                                                                                                                                                                                                                                                                                                                                       |

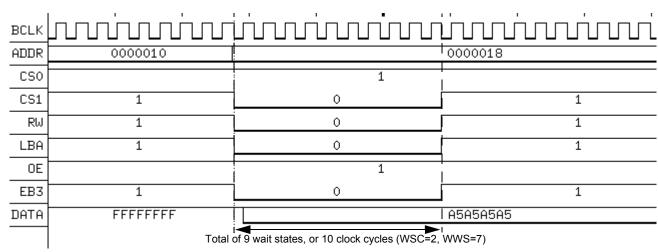

| WSC<br>Bits 45–40 | Wait State Control— For SYNC = 0:  WSC programs the number of wait-states for an access to the external device connected to the chip select. When the WWS (Write Wait State) bit settings are cleared, setting:  WSC = 000000 results in 2 system clock (HCLK) transfers  WSC = 000001 results in 2 system clock (HCLK) transfers  WSC = 001110 results in 15 system clock (HCLK) transfers  WSC = 111110 results in 63 system clock (HCLK) transfers  WSC = 111111 is not available (reserved) for CSO, CS1, CS2, CS3  and CS4, but it is available (the external DTACK) for CS5.  As can also be seen from the external waveform diagrams in Section 3, "EIM External Bus Asynchronous Waveform Examples," the WSC setting also dictates how many system clock (HCLK) cycles an address is held on the external address bus. This is best seen on those waveforms that depict back-to-back accesses, rather than for single external accesses, where the address will normally be held on the address bus after the transaction has completed when there is no immediate external transaction that follows.  For SYNC = 1:  WSC programs the number of system clock cycles required for the initial access of a burst sequence initiated by the EIM to an external burst device. Refer to the i.MX reference manual for more details.  WSC is set to 111110 by a hardware reset for CSO.  WSC is cleared by a hardware reset for CS1-CS5.  Note: WSC bits should be configured to more than one wait states.  The i.MX does not support zero wait state (1 clock cycle) accesses. | 000000 = 1 wait state delay (2 system clock (HCLK) cycle transfers)  000001 = 1 wait state delay (2 system clock (HCLK) cycle transfers)  000002 = 2 wait state delay (3 system clock (HCLK) cycle transfers)  000003 = 3 wait state delay (4 system clock (HCLK) cycle transfers)  111110 = 62 wait state delay (63 system clock (HCLK) cycle transfers)  111111 = not available (reserved) for CSO, CS1, CS2, CS3 and CS4, but it is available (the external DTACK) for CS5  Note: Depending on the WWS setting, more wait states may be added for write cycles. Refer to the WWS bit setting definition for more details. |

### Table 2. Chip Select Control Registers Description (continued)

| Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Reserved<br>Bit 39 | Reserved—This bit is reserved and should read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| WWS<br>Bits 38–36  | Write Wait State—Determines whether additional wait-states are required for write cycles. This is useful for writing to memories that require additional data setup time. This setting basically adds wait states to what is programmed in the WSC setting for write access. An example of how the WWS bit setting affects write cycle timing can be seen in Figure 26, Figure 27, and Figure 28.  WWS is cleared by a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

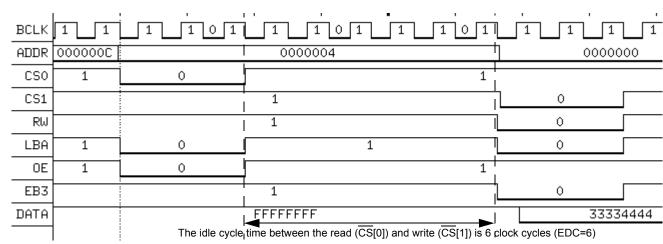

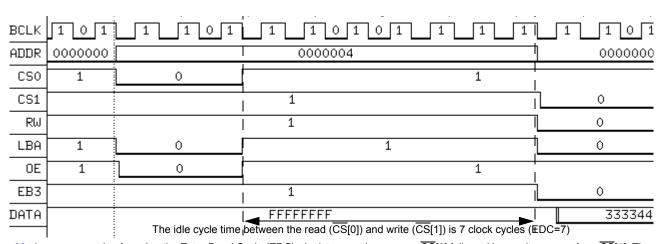

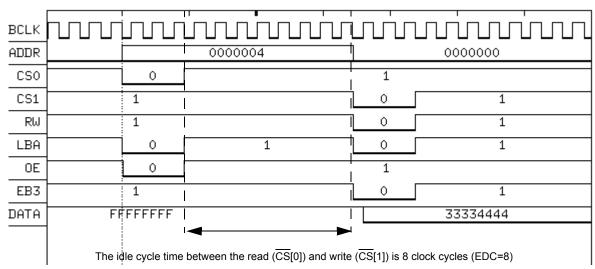

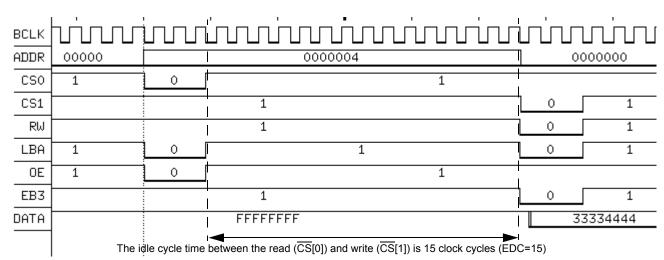

| EDC<br>Bits 35–32  | Extra Dead Cycles—Determines whether idle cycles (HCLK cycles) are inserted after a read cycle for back-to-back external transfers to eliminate data bus contention. This is useful for slow memory and peripherals that use long $\overline{CS}$ or $\overline{OE}$ to output data three-state times. Idle cycles are not inserted for back-to-back external reads from the same chip select. In other words, idle cycles are only inserted for back-to-back transactions from separate chip selects. An example of how the EDC bit setting affects the idle cycle timing between chip select accesses can be seen in Figure 22, Figure 23, Figure 24, and Figure 25.                                                                                                                                                                                                                                                                                                                                                                                      | 0000 = 0 Idle (HCLK) Cycles Inserted between the end of a read from one chip select to the start of an access on another chip select  0001 = 1 Idle (HCLK) Cycle Inserted between the end of a read from one chip select to the start of an access on another chip select  1111 = 15 Idle (HCLK) Cycles Inserted between the end of a read from one chip select to the start of an access on another chip select to the start of an access on another chip select |  |  |  |  |  |  |  |  |  |

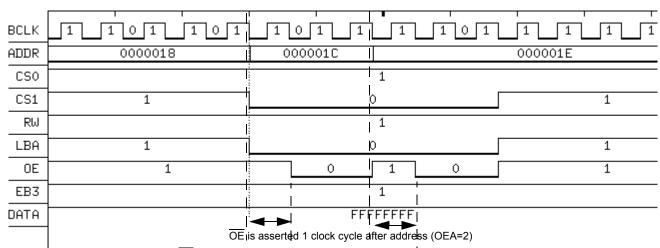

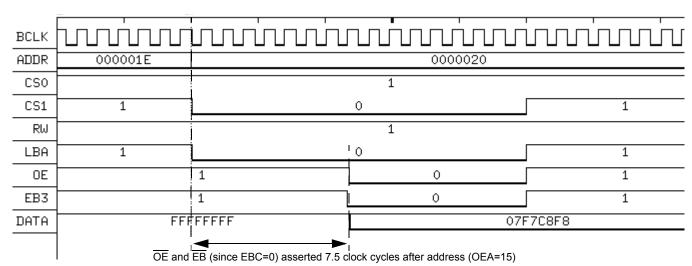

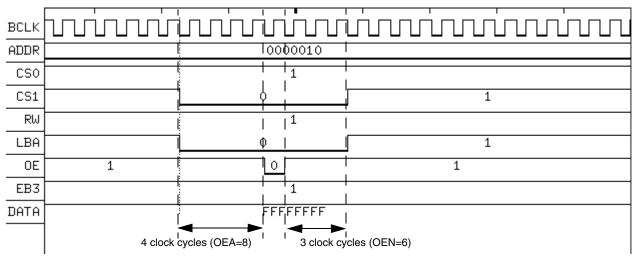

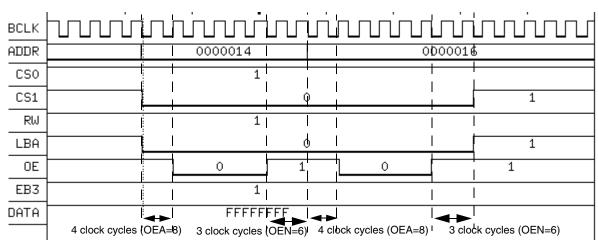

| OEA<br>Bits 31–28  | OE Assert—Determines when OE is asserted during read cycles.         For SYNC = 0:         OEA determines the number of half clocks (half HCLK cycles) before OE asserts during a read cycle. The OE assertion time is referenced from when the read address is placed on the address bus (it can also be referenced from when chip select asserts). See the OEA bit settings for more details. Also, examples of how the OEA bit setting affects the OE assertion time during read accesses can be seen in Figure 4, Figure 5, Figure 6, Figure 31, and Figure 32.         For SYNC = 1:       After the initial burst access, OE is asserted continuously for subsequent burst accesses, and is not affected by OEA (see burst read timing diagrams for more detail). The behavior of OE on the initial burst access is the same as when SYNC = 0.         When the EBC bit in the corresponding register is clear, the EB[3:0] outputs are similarly affected.         OEA does not affect the cycle length.         OEA is cleared by a hardware reset. | 0000 = $\overline{OE}$ is asserted 0 half clocks (HCLK cycles) after the assertion of chip select (or after the address is placed on the bus)  0001 = $\overline{OE}$ is asserted 1 half clock (HCLK cycles) after the assertion of chip select (or after the address is placed on the bus)  1111 = $\overline{OE}$ is asserted 15 half clocks (HCLK cycles) after the assertion of chip select (or after the address is placed on the bus)                       |  |  |  |  |  |  |  |  |  |

#### Overview of the i.MX EIM

Table 2. Chip Select Control Registers Description (continued)

| Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Settings                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

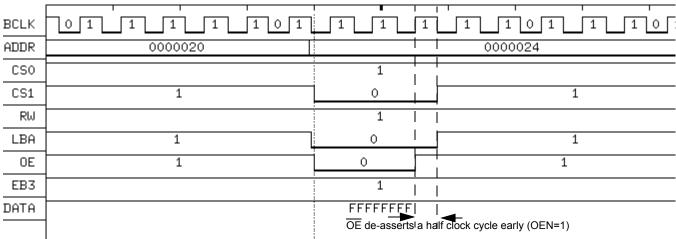

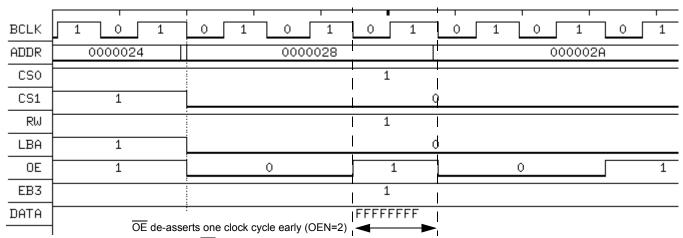

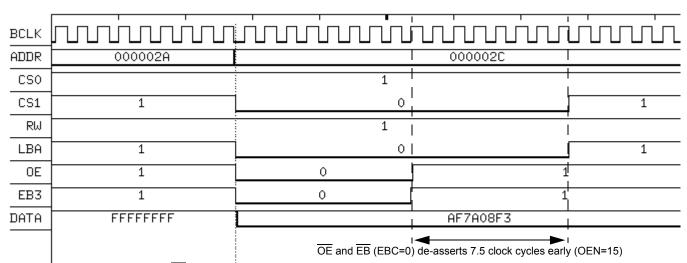

| OEN<br>Bits 27–24 | OE De-assert—Determines when OE is de-asserted during a read cycle. See the OEN bit settings for more details. Also, examples of how the OEN bit setting affects the OE de-assertion time during read accesses can be seen in Figure 7, Figure 8, Figure 9, Figure 31, and Figure 32.  When EBC in the corresponding register is clear, the EB[3:0] outputs are similarly affected.  Setting the SYNC bit (SYNC = 1) overrides OEN and OE negates at the end of a read access and no sooner.  OEN does not affect the cycle length.  OEN is cleared by a hardware reset.  Note: Programming the OEA and OEN bits such that the total assertion time of OE is one half HCLK cycle is not allowed, and will result in no assertion of the OE signal.                                                                                                                                      | 0000 = $\overline{OE}$ is de-asserted 0 half clocks (HCLK cycles) before end of access (before the chip select is de-asserted)  0001 = $\overline{OE}$ is de-asserted 1 half clock (HCLK cycles) before end of access (before the chip select is de-asserted)  1111 = $\overline{OE}$ is de-asserted 15 half clocks (HCLK cycles) before end of access (before the chip select is de-asserted) |

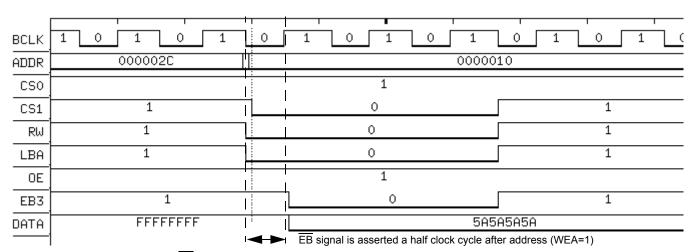

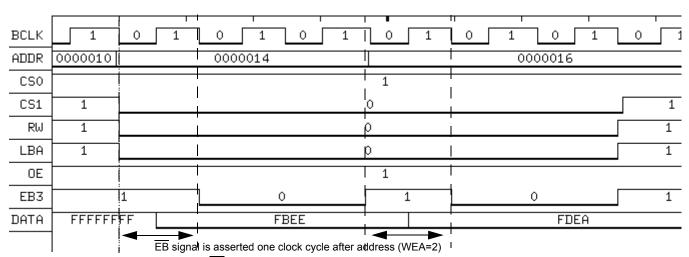

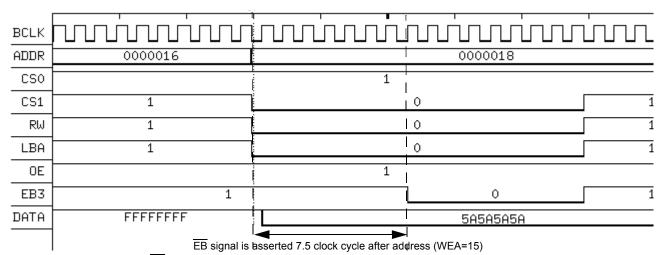

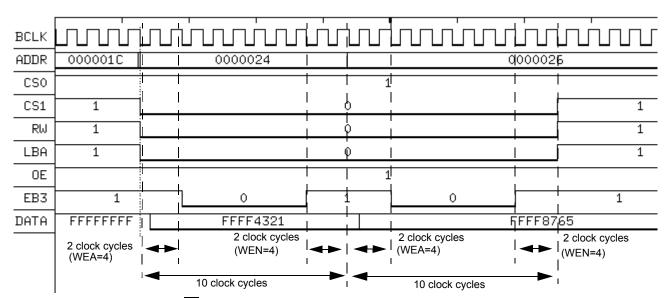

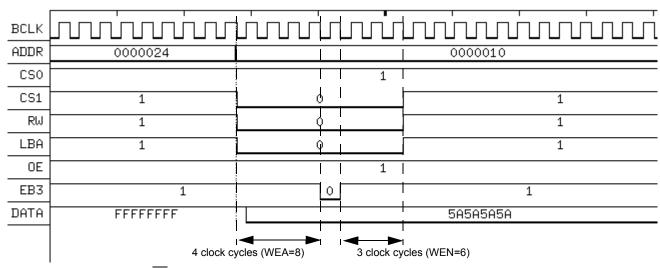

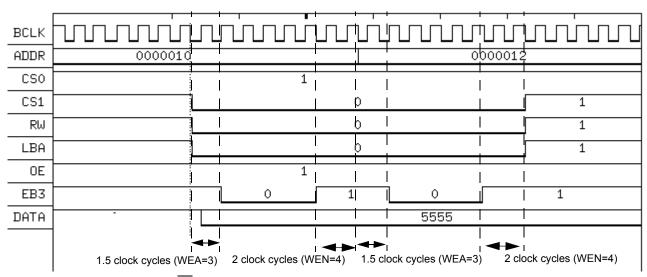

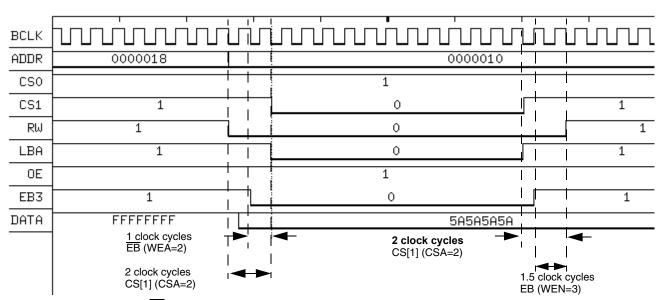

| WEA<br>Bits 23–20 | EB[3:0] Assert—Determines when EB[3:0] is asserted during write cycles. This is useful to meet data setup time requirements for slow memories. WEA determines the number of half clocks (half HCLK cycles) before EB[3:0] asserts during a write cycle. The EB[3:0] assertion time is referenced from when the write address is placed on the address bus or when the R/W signal asserts (it can also be referenced from when chip select asserts, however, in the case of writes, the chip select assertion time may also be affected by the CSA bit setting). See the WEA bit settings for more details. Also, examples of how the WEA bit setting affects the EB[3:0] assertion time during write accesses can be seen in Figure 10, Figure 11, Figure 12, Figure 27, Figure 28, Figure 29, and Figure 30. WEA does not affect the cycle length. WEA is cleared by a hardware reset. | $0000 = \overline{EB}[3:0]$ is asserted 0 half clocks (HCLK cycles) after the address is placed on the bus $0001 = \overline{EB}[3:0]$ is asserted 1 half clock (HCLK cycles) after the address is placed on the bus $1111 = \overline{EB}[3:0]$ is asserted 15 half clocks (HCLK cycles) after the address is placed on the bus                                                               |

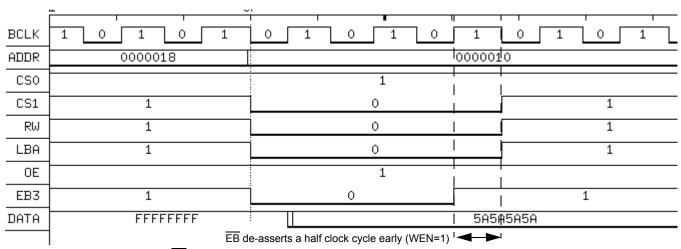

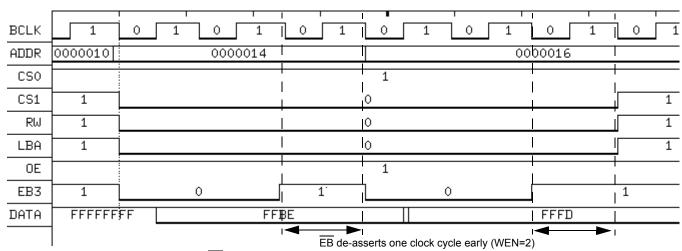

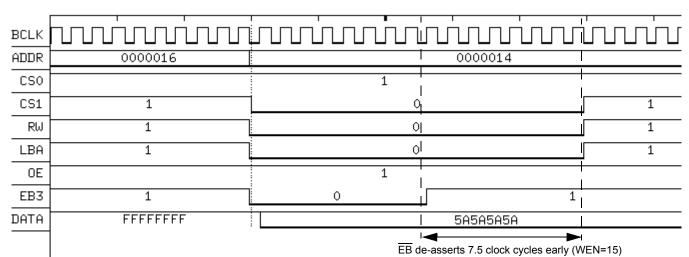

| WEN<br>Bits 19–16 | EB[3:0] De-assertion During Write—Determines when EB[3:0] outputs are de-asserted during a write cycle. This is useful to meet data hold time requirements for slow memories. See the WEN bit settings for more details. Also, examples of how the WEN bit setting affects the EB[3:0] de-assertion time during write accesses can be seen in Figure 13, Figure 14, Figure 15, Figure 28, Figure 29 and Figure 30. WEN does not affect the cycle length. WEN is cleared by a hardware reset. Note: Programming the WEA and WEN bits such that the total assertion time of EB[3:0] is one half HCLK cycle is not allowed, and will result in no assertion of the EB[3:0] signal                                                                                                                                                                                                          | $\begin{array}{l} 0000 = \overline{EB}[3:0] \text{ is de-asserted 0 half clocks} \\ \text{(HCLK cycles) before end of access (or before the de-assertion of R/W)} \\ \\ 0001 = \overline{EB}[3:0] \text{ is de-asserted 1 half clock} \\ \text{(HCLK cycles) before end of access (or before the de-assertion of R/W)} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$               |

Table 2. Chip Select Control Registers Description (continued)

| Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

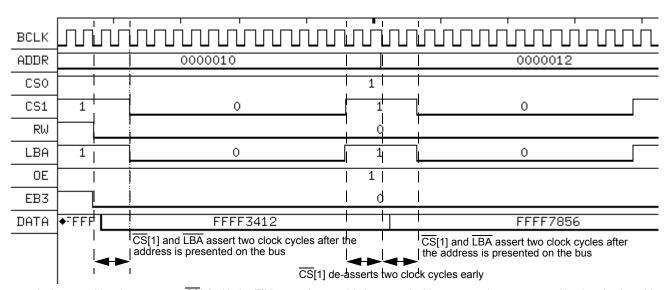

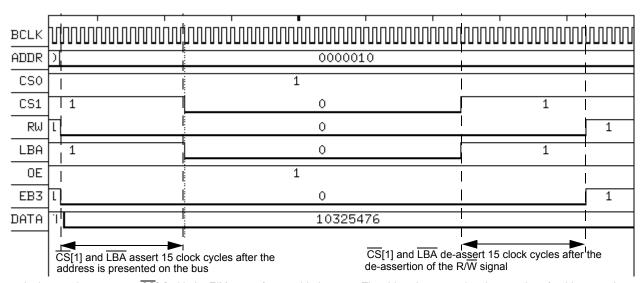

| CSA<br>Bits 15–12 | Chip Select Assert—Determines when the chip select is asserted and de-asserted for devices that require additional address setup time and additional address/data hold times. CSA affects only external writes, and is ignored on external reads. The chip select assertion/de-assertion times may be referenced from the assertion and de-assertion of the R/W signal or for back-to-back external writes, the chip select assertion/de-assertion time may be referenced to when the write address is placed and removed from the external address bus. See the CSA bit settings for more details. Also, examples of how the CSA bit setting affects the chip select assertion and de-assertion time during write accesses can be seen in Figure 19, Figure 20, Figure 21, and Figure 33. CSA pre-empts the CNC bit setting. CSA does not affect the cycle length. CSA is cleared by a hardware reset. | 0000 = Asserts 0 HCLK cycles after address is placed on bus and de-asserts 0 HCLK cycles before end of access (or before address is removed from bus for back-to-back accesses)  0001 = Asserts 1 HCLK cycles after address is placed on bus and de-asserts 1 HCLK cycles before end of access (or before address is removed from bus for back-to-back accesses)  1111 = Asserts 15 HCLK cycles after address is placed on bus and de-asserts 15 HCLK cycles before end of access (or before address is placed on bus and de-asserts 15 HCLK cycles before end of access (or before address is removed from bus for back-to-back accesses) |

| EBC<br>Bit 11     | Enable Byte Control—Indicates the access types that assert the enable byte outputs (EB[3:0]).  EBC is set by a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $0$ = Both read and write accesses assert the $\overline{EB}[3:0]$ outputs, thus configuring the access as byte enables 1 = Only write accesses assert the $\overline{EB}[3:0]$ outputs, thus configuring the access as byte write enables; the $\overline{EB}[3:0]$ outputs are configured as byte write enables for accesses to dual x16 or quad x8 memories                                                                                                                                                                                                                                                                             |

| DSZ<br>Bits 10–8  | <b>Data Port Size</b> —Defines the width of the external device's data port as shown in the table, <b>DSZ</b> Bit Encoding, to the right. At hardware reset, the value of <b>DSZ</b> is 101 for $\overline{CS1}$ — $\overline{CS5}$ . For $\overline{CS0}$ , <b>DSZ</b> is based on the value of the external BOOT[3:0] signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 000 = 8-bit port, resides on D[31:24] pins<br>001 = 8-bit port, resides on D[23:16] pins<br>010 = 8-bit port, resides on D[15:8] pins<br>011 = 8-bit port, resides on D[7:0] pins<br>100 = 16-bit port, resides on D[31:16] pins<br>101 = 16-bit port, resides on D[15:0] pins<br>11x = 32-bit port                                                                                                                                                                                                                                                                                                                                        |

| Reserved<br>Bit 7 | Reserved—This bit is reserved and should read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SP<br>Bit 6       | Supervisor Protect—Prevents accesses to the address range defined by the corresponding chip select when the access is attempted in the User mode of ARM920T core operation.  SP is cleared by a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 = User mode accesses are allowed in the range of chip select 1 = User mode accesses are prohibited; attempts to access an address mapped by this chip select in User mode results in a TEA to the ARM920T core and no assertion of the chip select output                                                                                                                                                                                                                                                                                                                                                                                |

| Reserved<br>Bit 5 | Reserved—This bit is reserved and should read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WP<br>Bit 4       | Write Protect—Prevents writes to the address range defined by the corresponding chip select.  WP is cleared by a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 = Writes are allowed in the range of chip select 1 = Writes are prohibited; attempts to write to an address mapped by this chip select result in a TEA to the ARM920T core and no assertion of the chip select output                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Overview of the i.MX EIM

Table 2. Chip Select Control Registers Description (continued)

| Name                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       | Settings                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

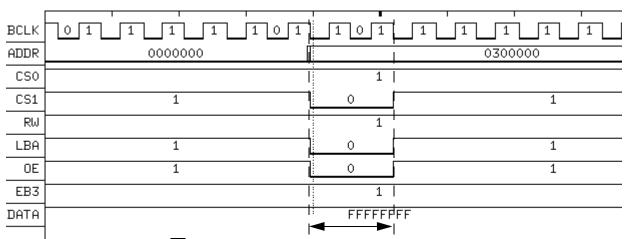

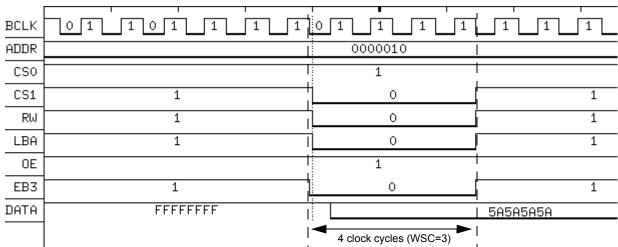

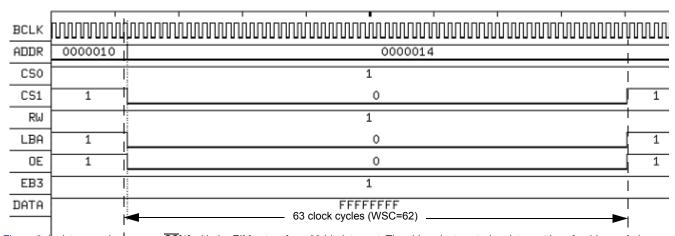

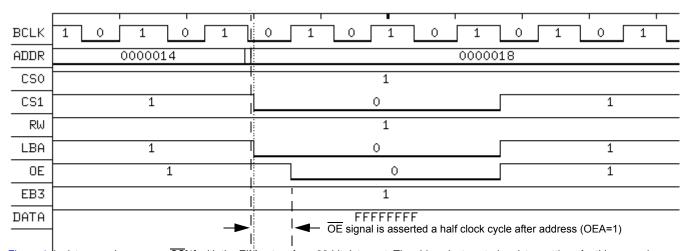

| Reserved<br>Bits 3–2 | Reserved—These bits are reserved and should read 0.                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |