### Application Note

AN2597/D 10/2003

Using the MC9S12E128 to Implement an IrDA Interface

By Steven Torres 8/16 Bit Systems Engineering Austin, Texas

### Introduction

The MC9S12E128 (E128) is designed for the low-cost, general-purpose distribution market with 8K of RAM and 128K FLASH. The E128 is a member of the MC9S12E Family of 16-bit FLASH-based microcontrollers. It is the first of a series of new low-cost, general-purpose products to address the UPS (uninterruptible power supply) and home appliance market.

The E128 has a rich set of modules including three SCIs with 13-bit baud rate selection. These SCIs are further enhanced because they can be operated in a mode that makes them compliant to a subset of the Infrared Data Association (IrDA) physical layer standard. The E128, with its SCI in IrDA mode, is designed to cover IrDA data rates between 2.4 and 115.2 kbps. This application note details the infrared capability of the E128 SCIs and how it fits into the IrDA standard. The discussion details the following:

- Infrared and IrDA

- Overview and Benefits of E128 SCI IrDA

**Freescale Semiconductor, Inc.**

- E128 SCI and IrDA Modulation/Demodulation Capabilities

- E128 Hardware Interfaces to an Integrated IrDA Transceiver

- Software Setup of the SCI to Initiate the IrDA Mode

- Introductory Discussion on IrDA Stacks Software

- **NOTE:** With the exception of mask set errata documents, if any other Motorola document contains information that conflicts with the information in the device guide, the device guide should be considered to have the most current and correct data.

All trademarks belong to their respective companies. This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

For More Information On This Product, Go to: www.freescale.com

$<sup>\</sup>ensuremath{\mathbb{C}}$  Freescale Semiconductor, Inc., 2004. All rights reserved.

Infrared today is synonymous with wireless connectivity. Infrared technology transfers data between nodes using infrared radiation. This point-to-point communication between nodes (or electronic devices) is inherently half duplex. IrDA-enabled products and applications are used in many products in today's market. Some of these products and applications include:

- Computing PCs, PDAs, calculators

- Peripherals Cameras, printers

- Communications Pagers, wireless phones

- Industrial Hand-held data collection devices

- Other Bridges/adapters

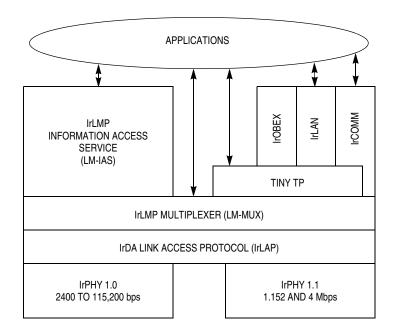

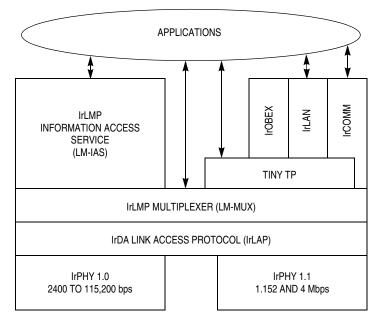

This application note addresses infrared transmission based on the IrDA standard as defined by the IrDA consortium. The IrDA standard provides specifications for physical devices and communication protocol. Each protocol layer in the IrDA standard is illustrated in **Figure 1**.

Figure 1. IrDA Standard Block Diagram

Using the MC9S12E128 to Implement an IrDA Interface

| Mandatory IrDA<br>Protocols | The complete IrDA standard defines each of the blocks in <b>Figure 1</b> . The mandatory blocks are listed below. The protocols not listed are optional.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | <ul> <li>PHY (physical signaling layer) — Provides continuous operation up to at<br/>least 1 meter; it is bidirectional and half duplex, with data transmission<br/>up to 16 Mbps, CRC calculation for data packets, and a data framer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

|                             | <ul> <li>IrLAP (link access protocol) — Provides a point-to-point wireless link for<br/>reliable communication, device discover procedures, and handling of<br/>hidden nodes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                             | <ul> <li>IrLMP (link management protocol) — Provides multiplexing of the IrLAP<br/>layer and protocol and service discovery via the information access<br/>service.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                             | This application note focuses on a subset of the physical signaling layer that includes the data host, modulator, and transceiver (see <b>Overview and Benefits of E128 SCI IrDA</b> ).                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Physical Signaling<br>Layer | Although this discussion focuses primarily on the IrDA standard PHY specification, a brief discussion of the communication protocol will be included in the Introductory Discussion on IrDA Stacks Software section.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             | Devices conforming to the IrDA standards can operate over distances up to 1.0 meter and must not have a bit error ratio (BER) greater than 10 <sup>-8</sup> over the range. The BER is a ratio of the number of incorrectly transferred bits to the number of correctly transferred bits. The maximum level of surrounding illumination for this operation is 10 <sup>3</sup> lux (daylight). The IrDA standard further defines the physical layer implementation based on communication speed. <b>Table 1</b> shows the pulse width requirements and modulation scheme for different IrDA physical layer signaling speeds. |

| Signaling Rate                               | Modulation   | Rate Tolerance<br>% of Rate | Pulse Duration<br>Minimum | Pulse Duration<br>Nominal | Pulse Duration<br>Maximum |  |

|----------------------------------------------|--------------|-----------------------------|---------------------------|---------------------------|---------------------------|--|

| 2.4 kbps                                     | RZI          | ±0.87                       | 1.41 μs                   | 78.13 μs                  | 88.55 μs                  |  |

| 9.6 kbps                                     | RZI          | ±0.87                       | 1.41 μs                   | 19.53 μs                  | 22.13 μs                  |  |

| 19.2 kbps                                    | RZI          | ±0.87                       | 1.41 μs                   | 9.77 μs                   | 11.07 μs                  |  |

| 38.4 kbps                                    | RZI          | ±0.87                       | 1.41 μs                   | 4.88 μs                   | 5.96 μs                   |  |

| 57.6 kbps                                    | RZI          | ±0.87                       | 1.41 μs                   | 3.26 µs                   | 4.34 μs                   |  |

| 115.2 kbps                                   | RZI          | ±0.87                       | 1.41 μs                   | 1.63 μs                   | 2.23 μs                   |  |

| 0.576 Mbps                                   | RZI          | ±0.01                       | 295.2 ns                  | 434.0 ns                  | 520.8 ns                  |  |

| 1.152 Mbps                                   | RZI          | ±0.01                       | 147.6 ns                  | 217.0 ns                  | 260.4 ns                  |  |

| 4.0 Mbps<br>(single pulse)<br>(double pulse) | 4PPM<br>4PPM | ±0.01<br>±0.01              | 115.0 ns<br>240.0 ns      | 125.0 ns<br>250.0 ns      | 135.0 ns<br>260.0 ns      |  |

| 16.0 Mbps                                    | HHH(1.13)    | ±0.01                       | 38.3 ns                   | 41.7 ns                   | 45.0 ns                   |  |

## Table 1. Pulse-Width Requirements

AN2597/D

Table 1 entries can be categorized into four different IrDA implementations

based on modulation and signal speed. These categories include:

- 2400 to 115,200 bps (named serial infrared or SIR)

- 0.576 and 1.152 Mbps (named medium infrared or MIR)

- 4 Mbps (named fast infrared or FIR)

- 16 Mbps (named very fast infrared or VFIR)

Although each of these different IrDA implementations are backwards-compatible with the original low-speed standard and default to a 9600 bps connection, only the SIR IrDA implementation is relevant to this application note. **Table 1** shows that for the slow IrDA connection speed (2400 bps to 115,200 bps), the standard specifies return-to-zero inverted (RZI) modulation. These requirements are easily handled by the E128.

## **Overview and Benefits of E128 SCI IrDA**

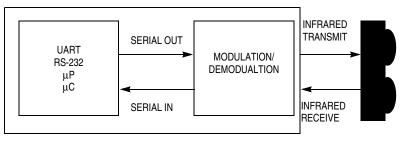

As discussed above, the E128 provides a solution for part of the SIR IrDA physical layer. The list below more clearly identifies components required for a more complete system implementation of an IrDA physical layer. This section also details how the E128 fits in with the IrDA SIR requirements. **Figure 1** shows a high level system view of IrDA system components including:

- Data host

- IrDA modulator/demodulator

- Infrared transceiver, which can be an integrated solution or designed from discrete components (LED, diode, and circuitry)

Figure 2. High Level IrDA Interface (Three Components)

Using the MC9S12E128 to Implement an IrDA Interface

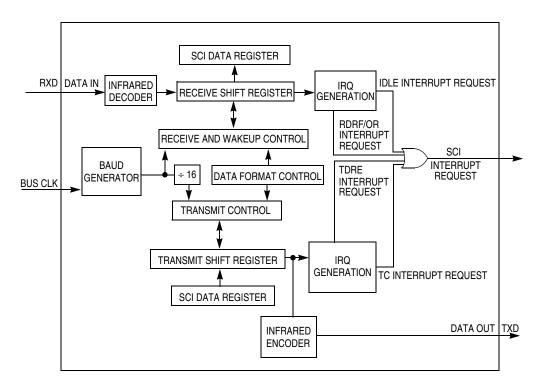

From a system perspective, the E128 integrates a data host and an IrDA modulator within the SCI. This makes each of the E128 SCIs compliant with the IrDA 1.0 physical layer specification when the E128 SCI IrDA mode is enabled. The E128 SCIs can then be directly interfaced to IrDA-compliant IR transceivers as shown in Figure 3.

In **Figure 3**, the modulation/demodulation IrDA submodule is shown as a component of the SCI block diagram for the E128.

Figure 3. E128 SCI with Integrated IrDA Modulator (Two Components)

Because this IrDA submodule is integrated within the SCI module, it provides substantial system benefits. One major point is that IrDA functionality can be added to the system with little additional hardware because no discrete external IrDA modulation components are required. Also, no additional software is required for signal modulation or demodulation. Benefits from a system's perspective include the following:

- Reduced component count

- Reduced PCB foot print

- Reduced system cost

## E128 SCI and IrDA Modulation/Demodulation Capabilities

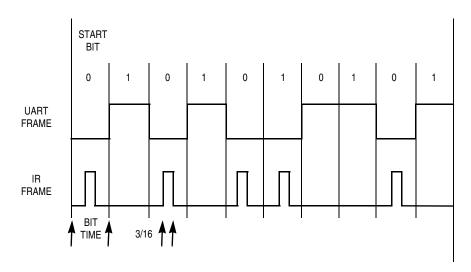

The E128 SCI meets the SIR IrDA physical layer requirements because the standard was based on SCI data formats. The data from the data host is represented as NRZ (non-return to zero) encoded serial bit stream just like the default data representation of a SCI. With NRZ encoding, the output is the same level for the entire bit period. For operation of a compliant IrDA transceiver, however, discrete narrow pulses are required as input. This narrow pulse RZI encoding task is the primary responsibility of the IrDA modulator in the E128 SCI.

When the SCI is transmitting and the SCI IrDA mode is enabled, the IrDA submodule modulates the signal as shown in **Figure 4**. **Figure 4** shows that when the NRZ bit is zero, an IrDA narrow pulse is generated by the modulator such that the output is asserted for a brief period of time. The minimum pulse duration is 3/16th of a SCI bit time running at 115.2 kbps (or  $1.63 \pm 0.87 \mu$ s). Operating with the minimum pulse duration of  $1.63 \mu$ s at a slower baud rate can reduce current requirements. The pulse width maximum for a particular baud rate is defined as 3/16th of the bit time of the given SCI baud rate (with a  $\pm 0.87 \mu$ s tolerance). Table 2 provides pulse width specifications for common SCI baud rates.

Figure 4. IrDA Encoding and Pulse Width Representation

For receiving data from the IrDA transceiver, the IrDA standard requires the modulator to convert the narrow pulse data stream into the NRZ encoded serial bit stream the SCI (the data host) is expecting.

## E128 Hardware Interfaces to an Integrated IrDA Transceiver

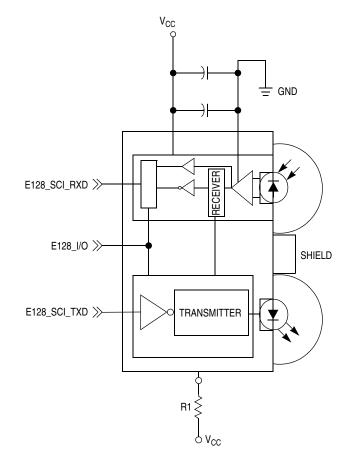

The electrical connection between the E128 and IrDA transceiver module requires no additional external component (except those that will be recommended by the IrDA transceiver manufacturer). See **Figure 5**, a partial and simplified schematic.

**Figure 5** is a typical example for a schematic and should not be used without verifying recommendations from the IrDA transceiver manufacturer. Different IrDA transceiver manufacturers have different requirements on IrDA transceiver hook-ups. IrDA transceiver manufacturers include Vishay, Agilent, Zilog, and others.

Figure 5. Typical IrDA Schematic

**Figure 5** shows several typical pins and components for an IrDA integrated transceiver:

- TXD (transmitter data input) Turns the LED on

- RXD (receiver data output) Signal output is a low pulse response when a light pulse is seen

- SD (shutdown) Completely shuts down TXD, RXD, and PIN diode

- V<sub>CC</sub> (supply voltage) Regulated range depending on transceiver specification

- GND (ground) Connects to system ground

- SHIELD (EMI shield) Typically connects to system ground via a low-inductance trace

Some IrDA transceivers also have mode pins that can be used to adjust optical power output. Adjustable optical power is desirable when the link distance will be shorter than the 1-meter IrDA requirement.

When selecting an IrDA transceiver for the E128, the IrDA transceiver must be operational up to 115.2 kbps. Using an IrDA transceiver that can handle higher IrDA speeds is not required. Also note, though this application uses an integrated IrDA transceiver, this is not the only possible configuration. Instead of the IrDA transceiver, discrete components (LED and photo-diode) can be used.

## Software Setup of the SCI to Initiate the IrDA Mode

To enable the IrDA mode of the SCI, the IREN bit of the SCIBDH register must be asserted and the SCI baud rate must be set. Asserting the IREN bit enables the integrated SCI IrDA submodule. **Figure 6** shows the contents of the SCIBDH register. Note that the SCIBDH register holds the five upper bits, SBR[12:8], of the SCI baud rate bits, SBR[12:0].

| Addr.    | Register Name                  |                 | Bit 7 | 6    | 5    | 4     | 3     | 2     | 1    | Bit 0 |  |

|----------|--------------------------------|-----------------|-------|------|------|-------|-------|-------|------|-------|--|

| \$001C   | SCI Baud Rate<br>Register High | Read:<br>Write: | IREN  | TNP1 | TNP0 | SBR12 | SBR11 | SBR10 | SBR9 | SBR8  |  |

| (SCIBDH) |                                | Reset:          | 0     | 0    | 0    | 0     | 0     | 0     | 0    | 0     |  |

In addition, the transmitter narrow-pulse bits, TNP[1:0], can also be used to configure the operation of the E128 on-board IrDA modulator. The TNP[1:0] bits are used configure the size of the narrow pulse that is generated by the device. Based on the IrDA standard, at 115.2 kbps the minimum pulse width is 3/16th of an NRZ encoded bit period (which is equivalent to the 1.63  $\mu$ s pulse-width minimum size). At slower baud rates, TNP[1:0] settings can be set to narrower pulse width settings as long as the actual pulse-width duration is not smaller than 1.63  $\pm$ 0.87  $\mu$ s minimum as indicated in the standard.

Table 2 itemizes additional TNP[1:0] settings.

| TNP[1:0] | Narrow Pulse Width |

|----------|--------------------|

| 11       | Reserved           |

| 10       | 1/32               |

| 01       | 1/16               |

| 00       | 3/16               |

| Table 2. IRSCI Transmit Pulse Width | Table 2. | IRSCI | Transmit | Pulse | Width |

|-------------------------------------|----------|-------|----------|-------|-------|

|-------------------------------------|----------|-------|----------|-------|-------|

The baud rate calculation, in IrDA mode, is different than when not in IrDA mode. Recall IrDA mode is set by the IREN bit. Below the equations for the baud rate calculation are shown as a function of the IREN bit.

When IREN = 0, SCI baud rate = SCI module clock / (16 × SBR[12:0])

When IREN = 1, SCI baud rate = SCI module clock / (32 × SBR[12:0])

Even with the IREN bit asserted, with SBR[12:1] = 0, the baud rate generator is disabled. SBR[12:1] must be set in order for data transmission to commence. In fact, after reset, the baud rate generator is disabled and not started until the TE bit or the RE bit (in the SCICR2 register) is set for the first time.

## Introductory Discussion on IrDA Stacks Software

Though this application note has focused on setting up an IrDA interface with the E128, this is only a part of a complete IrDA implementation as briefly stated in the **Infrared and IrDA** section. Implementing the upper IrDA protocol stack components is not a goal of this discussion, but an overview of IrDA protocol stack components is provided in this section. (The block diagram of the IrDA protocol layering is also repeated for convenience.)

Figure 7. IrDA Standard Block Diagram (Revisited)

For a review of the functionality of the IrDA stack mandatory protocols, review the section titled **Mandatory IrDA Protocols**. A list of the optional protocols is provided below. More information on the complete standard is found on the IrDA website (http://www.irda.org).

- Tiny TP Provides flow control on IrLMP connections with optional Segmentation and Reassembly.

- IrCOMM Provides COM (serial and parallel) port emulation for legacy COM applications.

- OBEX<sup>™</sup> Provides object exchange services similar to HTTP.

- IrTran-P Provides an image exchange protocol used in digital image capture devices.

- IrMC Provides specifications on how mobile telephony and communication devices (such as phone book, calendar, and message data) can exchange information.

- IrLAN Describes IR wireless access to local area networks.

- IrDA Lite Provides methods of reducing the size of IrDA code while maintaining compatibility with full implementations.

IrDA protocol stack development is not a trivial undertaking. Several IrDA protocol stack developers are available, including Extended Systems, EMBEDnet, and others. Motorola does not recommend or endorse any particular vendor for IrDA stack software.

AN2597/D Introductory Discussion on IrDA Stacks Software

Using the MC9S12E128 to Implement an IrDA Interface

### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

AN2597/D For More Information On This Product, Go to: www.freescale.com