# **INTEGRATED CIRCUITS**

# **APPLICATION NOTE**

# AN255-02 I<sup>2</sup>C / SMBus REPEATERS, HUBS AND EXPANDERS

PCA9511, PCA9512, PCA9513, PCA9514, PCA9515, PCA9516, PCA9518, P82B96, P82B715

Abstract - Philips Semiconductors family of Repeaters, Hubs and Expanders are detailed in this application note that discusses device operation, maximum cable length and frequency calculations and typical applications.

Phil Tracy - Senior Field Applications Engineer

Alma Anderson - Senior Design Engineer

Jean-Marc Irazabal - Technical Marketing Manager

Steve Blozis - International Product Manager

Specialty Logic Product Line Logic Product Group

Purchase of Philips  $I^2C$  components conveys a license under the Philips' patent to use the components in the  $I^2C$  system provided the system conforms to the  $I^2C$  specification defined by Philips.

**Philips Semiconductors**

**December**, 19 2002

# **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                                                                 |    |

|---------------------------------------------------------------------------------------------------|----|

| OVERVIEW                                                                                          |    |

| DESCRIPTION                                                                                       |    |

| APPLICATIONS                                                                                      |    |

| DEVICE FEATURES AND CHARACTERISTICS                                                               | 4  |

| DEVICE PINOUT                                                                                     |    |

| Ordering Information                                                                              |    |

| DATA SHEETS AND IBIS MODELS                                                                       |    |

| PCA9511/12/13/14 TECHNICAL INFORMATION                                                            |    |

| BLOCK DIAGRAM                                                                                     |    |

| PCA9515/16/18 TECHNICAL INFORMATION                                                               |    |

| BLOCK DIAGRAM                                                                                     |    |

| VOLTAGE LEVEL TECHNICAL INFORMATION                                                               |    |

| DESIGN CONSTRAINTS                                                                                | 10 |

| P82B715 TECHNICAL INFORMATION                                                                     | 1  |

| BLOCK DIAGRAM                                                                                     | 1  |

| VOLTAGE LEVEL TECHNICAL INFORMATION                                                               | 1  |

| DESIGN CONSTRAINTS                                                                                | 12 |

| P82B96 TECHNICAL INFORMATION                                                                      | 13 |

| BLOCK DIAGRAM                                                                                     | 13 |

| VOLTAGE LEVEL TECHNICAL INFORMATION                                                               | 14 |

| DESIGN CONSTRAINTS                                                                                |    |

| USE OF MULTIPLE DEVICES IN THE SAME I <sup>2</sup> C SYSTEM                                       | 15 |

| DETERMING PULL-UP RESISTORS VALUE                                                                 | 10 |

| APPLICATIONS                                                                                      | 10 |

| BUS EXPANSION BEYOND THE 400 PF LIMITATION                                                        |    |

| SPLIT BUS 100 KHZ AND 400 KHZ APPLICATION                                                         | 17 |

| VOLTAGE LEVEL SHIFTING                                                                            |    |

| I <sup>2</sup> C MULTIPLEXING                                                                     |    |

| I <sup>2</sup> C MULTI-POINT HOT SWAP APPLICATIONS                                                |    |

| I <sup>2</sup> C Bus Extension Over Long Cables                                                   |    |

| I <sup>2</sup> C Opto-Electrical Isolation                                                        |    |

| MULTIPLE SEGMENT APPLICATION                                                                      |    |

| FREQUENTLY ASKED QUESTIONS                                                                        |    |

| DEVICE USAGE AND DIFFERENCES                                                                      |    |

| LIVE INSERTION                                                                                    |    |

| I <sup>2</sup> C OVER LONG DISTANCES                                                              |    |

| ELECTRICAL PARAMETERS.                                                                            | 30 |

| I <sup>2</sup> C protocol                                                                         |    |

| ARCHITECTURE / APPLICATIONS                                                                       |    |

| ADDITIONAL INFORMATION                                                                            |    |

| APPENDIX 1 – Long Bus Calculations                                                                |    |

| CALCULATION OF MAXIMUM CLOCK FREQUENCY FOR LONG BUSES                                             |    |

| THE 'SHORTCUT' APPROACH TO LONG BUS APPLICATIONS                                                  |    |

| SOME CALCULATION EXAMPLES                                                                         |    |

| APPENDIX 2 – Using P82B715 to increase the total allowable bus capacitance                        |    |

| APPENDIX 3 - Operating P82B715 on lower supply voltages                                           |    |

| APPENDIX 4 - The special logic levels and noise margins of buffer logic                           |    |

| APPENDIX 5 - Using P82B96 to create a multi-drop "distribution" bus using 12 V logic levels       |    |

| APPENDIX 6 - Differences Between the LTC1694 and LTC1694-1                                        |    |

| APPENDIX 7 - Typical response times to 'data valid' on SDA, measured from the falling edge of SCL | 58 |

#### **OVERVIEW**

#### Description

The PCA9511, PCA9512, PCA9513, PCA9514, PCA9515, PCA9516, PCA9518, P82B715 and P82B96 allow a larger or longer I<sup>2</sup>C or SMBus system where the following constraints previously restricted its size:

- a) More I<sup>2</sup>C devices or larger wiring capacitance than the 400 pF maximum allowed in the I<sup>2</sup>C specification.

- b) Long bus wiring or backplanes

- c) Different operating supply voltages or logic voltage levels within one system

- d) Opto-isolation for safety or due to difference in ground plane

- e) Isolating a section of a system that has lost its power supply

- f) Insertion of unpowered cards into an active I<sup>2</sup>C bus

With only one repeater delay between any two segments, the:

- PCA9511/12/13/14 Hot Swappable I<sup>2</sup>C Buffers supports two segments of 400 pF and hot swapping with pin precharge and idle detect features.

- PCA9515 I<sup>2</sup>C Bus Repeater supports two segments of 400 pF with channel enable.

- PCA9516 5-channel I<sup>2</sup>C Hub supports five segments of 400 pF for a total I<sup>2</sup>C or SMBus capacitance of 2000 pF with 4 channel enables.

- PCA9518 Expandable 5-channel I<sup>2</sup>C Hub supports multiple groupings of five segments of 400 pF each for an unlimited I<sup>2</sup>C or SMBus capacitance with 4 channel enables per device.

The PCA9511/12/13/14 are designed to work with clock frequencies up to 400 kHz and are suitable for utilization in a multi-master I<sup>2</sup>C bus or SMBus environment. They are specifically designed for backplane multi-point applications and hot swap. The devices support bus arbitration and contention with bus masters located on any segment. They are multi-directional and require no direction control. Operational voltage supply is 2.7 V to 5.5 V with 5.5 V tolerant I/Os. Operational temperature range is -40 °C to 85 °C. See Philips application note AN10160-01 for more detailed technical information on these devices.

The PCA9515/16/18 are designed to work with clock frequencies up to 400 kHz and are suitable for utilization in a multi-master I²C bus or SMBus environment. They are specifically designed for larger buses on single card applications with the PCA9516 or PCA9518 for star configuration point to point connections. The devices support bus arbitration and contention with bus masters located on any segment. They are multi-directional and require no direction control. Operational voltage supply is 3.0 V to 3.6 V with I/Os that are 6.0 V tolerant allowing easy interfacing of 3.3 V and 5 V devices. Operational temperature range is -40 °C to 85 °C.

The P82B715 allows bi-directional signaling without an external direction control over wiring capacitance loads up to around 3000 pF. At normal I<sup>2</sup>C logic voltage levels, it transforms the impedance of the wiring by a factor 10, so 3000 pF of wiring appears as 300 pF loading on the I<sup>2</sup>C bus. The P82B715 does not afford any isolation or support logic voltage level translation. The P82B96 is recommended for new designs due to its superior features.

The P82B96 allows bi-directional signaling without an external direction control and provides a true buffer functionality supporting logic levels from 2 V to 15 V and bus impedance 10 times lower than  $I^2C$ . It is designed for long distance signaling, multi-point applications and opto-isolation of bus segments in situations like power supplies with different ground planes.

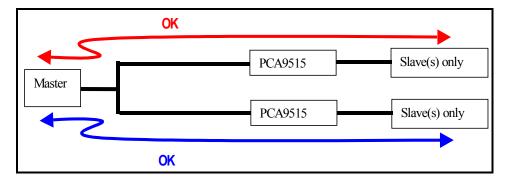

Normally, <u>only one</u> PCA9515 Repeater or PCA9516 Hub should be used per  $I^2C$  or SMBus system due to the way they operate to provide multi-directional signally without an external direction control. The PCA951x series of Hot Swappable Bus Buffers, the PCA9518 Expandable Hub or the P82B715/96 Bus Buffers should be used for any application requiring multiple devices in the same system.

This Application Note covers the use of these devices in a generic multiple master environment.. Information on the permitted interfaces and bus propagation delays between P82B715/96 Buffers and PCA951x/15/16/18 are also included.

## **Applications**

These devices can be used for a wide variety of applications:

I<sup>2</sup>C or SMBus Extension – All devices allow extension of the I<sup>2</sup>C or SMBus on systems requiring capacitance loads larger than the 400 pF max specified by the I<sup>2</sup>C protocol. Designers can extend the use of the I<sup>2</sup>C or SMBus in systems with more devices and / or longer bus lengths with only one repeater delay between any device. The devices are multiple master capable and support arbitration and bus contention on any segment.

- The PCA9511/12/13/14/15 I<sup>2</sup>C Bus Repeater supports two I<sup>2</sup>C or SMBus branches of 400 pF

- The PCA9516 5-channel I<sup>2</sup>C Hub enables separation of the I<sup>2</sup>C or SMBus into five 400 pF segments

- The PCA9518 Expandable 5-channel I<sup>2</sup>C Hub enables separation of the I<sup>2</sup>C or SMBus into multiple groupings of five 400-pF segments for star configurations.

- The P82B715 and P82B96 provide the multi-point bus alternative. Working in the conventional I<sup>2</sup>C 'wired and' mode, but with an impedance level that may be 10 times lower than I<sup>2</sup>C thus allowing up to 4000 pF bus capacitance. P82B96 allows selection of any convenient logic voltage level up to 15 V with no restriction on the number of 'drops'.

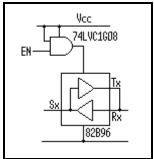

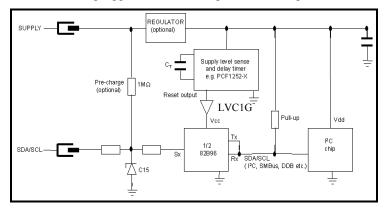

$I^2C$  or SMBus Isolation - Each PCA9511/13/14/15/16/18 individual repeater channel has an enable/disable feature that is used to electrically isolate that segment of the  $I^2C$  or SMBus. In addition, all devices except the P82B715 release their I/O pins should their supply voltage fail. When an enable input is required with P82B96 the Picogate circuit in Figure 1 may be used.

Figure 1. P82B96 Enable Input Configuration

Examples where bus isolation could be useful include:

- 1. Allow mixed operation of 100 and 400 kHz devices on a combined bus by isolating the segment with the 100 kHz devices from the rest of the 400 kHz devices so that the 400 kHz devices can operate at their maximum speed.

- 2. Supporting the PCI management bus with 8 or more PCI slots

- 3. Isolating the I<sup>2</sup>C or SMBus to support hot plug PCI slots

- 4. Allowing the main I<sup>2</sup>C or SMBus to drive multiple system boards

- 5. Addressing selected devices if there are multiple devices in the system with the same I<sup>2</sup>C address.

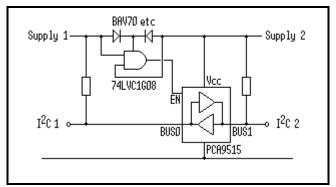

- 6. Sensing multiple power supplies on different bus segments and providing automatic isolation of failed segments or segments suffering 'brown-out' of their power supplies. An example of such sensing using the PCA9515 is shown in Figure 2. In this example a failure of EITHER Supply 1 OR Supply 2 will cause I<sup>2</sup>C 1/Bus0 to be disconnected from I<sup>2</sup>C 2/Bus1. The PCA9512 with its two V<sub>CC</sub> supplies and ACC pin can also be used in this application by tying ACC to V<sub>CC</sub>.

Figure 2. Multiple Voltage Sensing Example

**Voltage Translation** - The PCA9515/16/18 operate on 3.3 V  $V_{CC}$  but since they have 6.0 V tolerant I/Os, they support different  $I^2C$  or SMBus segments at 3.3 V or 5 V, thus extending the life of older 5 V circuit blocks while allowing use of newer 3.3 V devices for improved system performance.

PCA9511/13/14 do **NOT** support logic level translations. The PCA9512 has two  $V_{CC}$  supply inputs specifically designed for voltage translation applications.

P82B715 does **NOT** support logic level translations. Its I/O pins simply track each other within 100mV, independent of the power supply ( $V_{CC}$ ). Its logic levels may not exceed  $V_{CC}$  and will be diode clamped at  $V_{CC}$  + Vdiode.

P82B96 is intended for operation with 5 V logic on its Sx side but can operate down to 3.3 V. The logic threshold on the Sx side is independent of the device's  $V_{CC}$ . The logic levels on the higher drive Rx/Tx side are half-rail CMOS switching levels related to the device's supply ( $V_{CC}$ ) that is specified from 2 V to 15 V. All I/Os are 18 V tolerant.

The GTL2000/02/10 allow I<sup>2</sup>C voltage level translation at any voltage between 1.0 V and 5.0 V. See application note AN10145-01 Bi-Directional Voltage Translators for more information.

Hot Swapping Line Cards - The PCA9511/12 are featured with circuitry that precharges the SDA and SCL pins to prevent glitching data on an active  $I^2C$  bus when the unpowered slave card is inserted into the backplane system. They also feature an idle detect circuit that will not connect the active bus to the line card devices until the bus is idle. The PCA9513/14 do not have the precharge feature since it is not needed or desired in some applications. The PCA9513 has a 92  $\mu$ A current source for PICMG applications.

#### **Device Features and Characteristics**

#### PCA9511/12/13/14:

- Bi-directional buffer for SDA and SCL lines

- Prevents SDA and SCL corruption during live board insertion and removal from backplane

- Idle detect circuit connects board only when bus is idle

- 1 V precharge on all SDA and SCL lines prevents data glitch (PCA9511/12 only)

- Compatible with I<sup>2</sup>C, I<sup>2</sup>C fast mode, and SMBus standards

- DV/Dt rise time accelerators on all SDA and SCL lines

- Rise time accelerator disable (PCA9512 only)

- Low I<sub>CC</sub> device disable: <1 mA (PCA9511/13/14 only)

- READY open-drain output (PCA9511/13/14 only)

- 92 µA current source for PICMG applications (PCA9513 only)

- Operating voltage range is 2.7 V to 5.5 V

- 5.5 V tolerant I<sup>2</sup>C and enable pins

- Split V<sub>CC</sub> for 3.3 V and 5 V level translation (PCA9512 only)

- Operating temperature range is -40 °C to 85 °C

- Accommodate 100 kHz and 400 kHz devices and multiple masters

- ESD protection exceeds:

- 2000 V HBM per JESD22-A114

- 200 V MM per JESD22-A115

- 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- PCA9511/12/13/14 offered in 8-pin SO (D) and TSSOP (DP)

#### PCA9515/16/18:

- •Accommodate more I<sup>2</sup>C devices or a longer bus length, up to 400 pF per segment

- Multi-directional I<sup>2</sup>C drivers that require no directional control isolate the I<sup>2</sup>C bus capacitance of each segment.

- Powered-off high impedance I<sup>2</sup>C pins support hot insertion and tolerant up to 6.0 V.

- Open drain outputs and fail safe (will not inhibit attached devices) operation on loss of power

- Designed for I<sup>2</sup>C-bus operation but compatible with SMBus

- Lock-up free operation

- Multi-master capable repeaters support bus arbitration and clock stretching with only one repeater delay between segments

- Operating voltage range is 3.0 V to 3.6 V

- 6.0 V tolerant I<sup>2</sup>C and enable pins pull-up resistors to either 3.3 V or 5 V voltage levels are allowed on the individual segments since the I<sup>2</sup>C bus and enable pins are over voltage tolerant to 6.0 V.

- Individual channel enables allow segments to be individually isolated. Hardware enable pins operate at LVTTL voltage levels and are over voltage tolerant to 6.0 V.

- Operating frequency range from 0 kHz to 400 kHz

- Operating temperature range is -40 °C to 85 °C

- ESD protection exceeds:

- 2000 V HBM per JESD22-A114

- 200 V MM per JESD22-A115

- 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- PCA9515 offered in 8-pin SO (D) and TSSOP (DP)

- PCA9516 offered in 16-pin SO narrow (D) and TSSOP (PW)

- PCA9518 offered in 20-pin SO (D) and TSSOP (PW)

#### P82B715:

- Accommodate more I<sup>2</sup>C devices or a longer, lower impedance bus wiring. Up to 3000 pF wiring capacitance.

- Bi-directional unity voltage gain buffering with no external directional control required.

- 10x impedance transformation but does not change logic voltage levels.

- Wide supply voltage range of 3.0 V to 12.5 V.

- Logic signal levels independent of device supply and may include (but not exceed) supply and ground.

- I<sup>2</sup>C-bus compatible but not compatible with SMBus.

- Manufactured in rugged bipolar process (includes diodes to V<sub>CC</sub>).

- Operating frequency range from 0 kHz to 100 kHz

- Operating temperature range is -40 °C to 85 °C

- ESD protection exceeds:

- 2500 V HBM per Mil. Std. 883C 3015.7

- Latch-up free (bipolar process with no latching structures).

- P82B715 offered in 8-pin DIP (N) and SO (D)

#### P82B96:

- Can split bi-directional I<sup>2</sup>C signals into two unidirectional Tx and Rx data signals, or recombine these.

- 10x bus impedance transformation option, unlimited bus drive capability with external transistor.

- Multi-drop extension bus configuration supports full I<sup>2</sup>C protocol.

- Open collector outputs and fail safe operation (will not inhibit attached devices) on loss of power.

- Designed for I<sup>2</sup>C-bus operation and compatible with SMBus

- Powered-off high impedance and 18 V rated I/O pins support hot insertion or cable plug-in.

- Low supply current (1 mA)

- Manufactured in rugged bipolar process.

- Operating voltage range is 2.0 V to 15.0 V

- 18 V tolerant I/O pins pull-up resistors to different voltage levels are allowed on each side of the device.

- Usual operating frequency range from 0 kHz to 400 kHz but will clock above 600 kHz

- Operating temperature range is -40 °C to 85 °C

- ESD protection exceeds:

- 3500 V HBM per JESD22-A114

- 1000 V CDM per JESD22-C101

- Latch-up free (bipolar process with no latching structures).

- P82B96 offered in 8-pin DIP (N), SO (D) and TSSOP (DP)

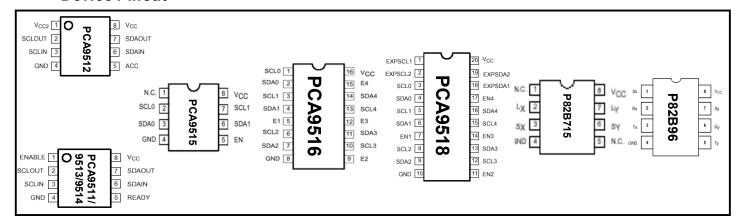

#### **Device Pinout**

Figure 3. Device Pinout

# **Ordering Information**

| Package | Container | PCA9511     | PCA9512     | PCA9513     | PCA9514     |

|---------|-----------|-------------|-------------|-------------|-------------|

| so      | Tube      | PCA9511D    | PCA9512D    | PCA9513D    | PCA9514D    |

|         | T&R       | PCA9511D-T  | PCA9512D-T  | PCA9513D-T  | PCA9514D-T  |

| TSSOP   | T&R       | PCA9511DP-T | PCA9512DP-T | PCA9513DP-T | PCA9514DP-T |

| Package | Container | PCA9515     | PCA9516     | PCA9518     | P82B715     | P82B96     |

|---------|-----------|-------------|-------------|-------------|-------------|------------|

| DIP     | Tube      | -           | -           | -           | P82B715PN   | P82B96PN   |

| SO      | Tube      | PCA9515D    | PCA9516D    | PCA9518D    | P82B715TD   | P82B96TD   |

| 30      | T&R       | PCA9515D-T  | PCA9516D-T  | PCA9518D-T  | P82B715TD-T | P82B96TD-T |

| TSSOP   | Tube      | -           | PCA9516PW   | PCA9518PW   | -           | P82B96DP   |

|         | T&R       | PCA9515DP-T | PCA9516PW-T | PCA9518PW-T | -           | P82B96DP-T |

**Table 1. Ordering Information**

#### Data Sheets and IBIS Models

Data sheets and IBIS models can be downloaded from www.philipslogic.com

#### PCA9511/12/13/14 TECHNICAL INFORMATION

### **Block Diagram**

The PCA9511/12/13/14 are multi-directional translators that require no external directional control and are specifically designed to support a multi-master  $I^2$ C/SMBus environment where masters can be located on both sides of the PCA9511/13/14 is shown in Figure 4A and PCA9512 is shown in Figure 4B.

Figure 4A. PCA9511/13/14 Block Diagram

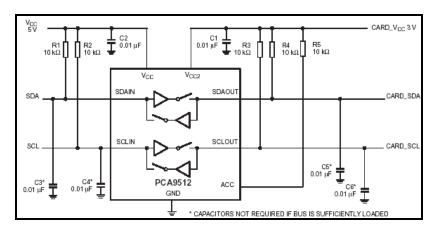

Figure 4B. PCA9512 Block Diagram

There are no external hardware address pins since this device does not have an I<sup>2</sup>C address. It merely buffers the I<sup>2</sup>C signals from segment to segment and does not respond to any I<sup>2</sup>C commands.

The PCA9511/12/13/14 operates at a supply voltage from 2.7 V to 5.5 V with 5.5 V tolerant I/Os. Additional technical information is presented in application note AN10160-01.

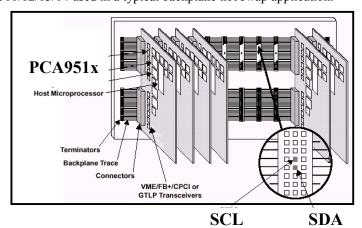

Figure 5 shows the PCA9511/12/13/14 used in a typical backplane hot swap application.

Figure 5. PCA951x Typical Multi-Point Hot Swap Application

#### PCA9515/16/18 TECHNICAL INFORMATION

#### **Block Diagram**

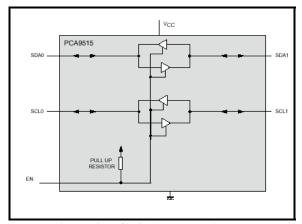

The PCA9515/16/18 are multi-directional translators that require no external directional control. They are specifically designed to support a multi-master I<sup>2</sup>C/SMBus environment where masters can be located on both sides of the PCA9515 as shown in Figure 4 or any or all of the segments of the PCA9516/18 hubs.

Figure 6. PCA9515 Block Diagram

There are no external hardware address pins since these devices do not have an I<sup>2</sup>C address. They merely buffer the I<sup>2</sup>C signals from segment to segment and do not respond to any I<sup>2</sup>C commands.

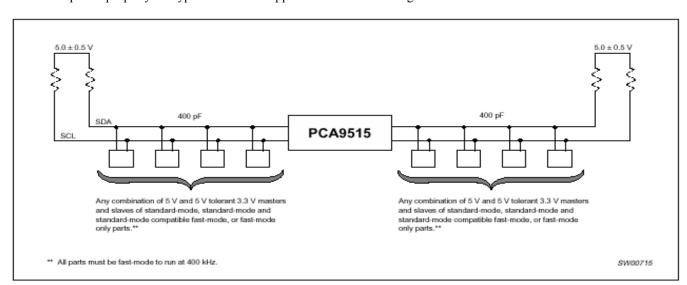

The PCA9515/16/18 devices operate at a supply voltage from 3.0 V to 3.6 V, with SDx/SCx and enable pins all tolerant to voltages up to 6.0 V. The pass gates of these devices are constructed such that the  $V_{DD}$  pin can be used to limit the maximum high voltage, which will be passed by the devices. This allows the use of different bus voltages on each SCx/SDx pair, so that, for example, 3.3 V devices on one segment can communicate with 5 V devices on a different segment without any additional protection. External pull-up resistors pull the bus up to the desired voltage level for this channel.

The repeater hardware enable pin allows the downstream segments to be isolated and includes an internal pull-up resistor. The enable is held low to isolate the downstream segment to communicate with the upstream channel.

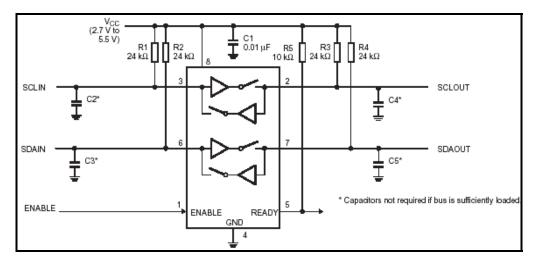

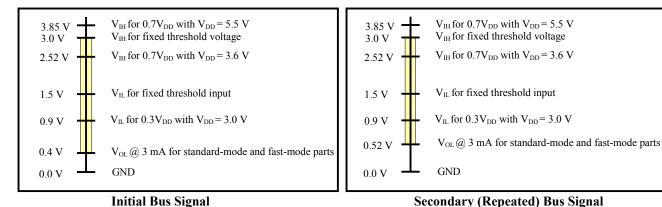

### Voltage Level Technical Information

The low-level input threshold is set just above the  $0.4~V~V_{OL}$  specifications limit for standard-mode devices. This limits the bus operation to a maximum current of 3 mA.

Figure 7. Voltage Level Comparison

Considering a 3.3 V  $\pm$  0.3 V device with power supply referenced input thresholds, the minimum noise margin for 3 mA operation is 500 mV. In order to both drive the bus low and detect a contention condition or clock stretching event, the device  $V_{OL}$  is set at 0.52 V @ 3 mA as shown in Figure 7. Thus a minimum 380 mV noise margin is preserved when the device is driving low. The low-level detector used to recognize contention conditions has a threshold set at about 450 mV and includes an integrator filter for high frequency noise rejection.

#### Design Constraints

**Maximum Current** - The bus can be operated at no more than 3 mA and the bus IR voltage drops must be controlled such that the device sees 0.4 V or less  $V_{IL}$  during a contention condition or clock-stretching event. Normally the bus pull-up resistor would need to be at the opposite end of the bus segment from the device. The device bus pins are over voltage tolerant to 5.5 V so that the  $I^2C$  bus on one or all sides of the device can be operated at 5 V while the device is operated from a 3.3 V supply.

**5** V Bus Operation - The bus pull-up resistors need to be tied to the 5 V supply if any 5 V devices are on the bus to guarantee that the V<sub>IH</sub> of the 5 V device is reached. If no 5 V devices are used, a 3.3 V bus pull-up resistor supply should be used as this will result in a smaller RC time constant for the same 3 mA current.

**Pull-Up Resistor Sizing** - The device edge rate control on the open drain outputs means falling edge rate is almost independent of capacitive loading up to the 400 pF maximum allowed by the I<sup>2</sup>C bus specification. Both standard mode and fast mode allow the same 400 pF maximum bus capacitance. The rise time is determined by the RC product of the bus capacitance and the pull-up resistor; for standard-mode the limit is 1000 ns and for fast-mode the limit is 300 ns.

Consider the  $V_{DD}$  released input threshold of  $V_{IH}$  = 0.7  $V_{DD}$  and  $V_{IL}$  = 0.3  $V_{DD}$  for the purposes of RC time constant calculation. Then  $V_{(t)}$  =  $V_{DD}$  (1-1/e<sup>-t/RC</sup>) where t is the time since the charging started and RC is the time constant.

```

V_{(t1)} = 0.3 \text{ x } V_{DD} = V_{DD} (1-1/e^{-t1/RC}); \text{ then } t1 = 0.3566749 \text{ x RC}

V_{(t2)} = 0.7 \text{ x } V_{DD} = V_{DD} (1-1/e^{-t2/RC}); \text{ then } t2 = 1.2039729 \text{ x RC}

T = t2 - t1 = 0.8473 \text{ x RC}

```

For standard-mode  $I^2C$  bus: t = rise time = 1000 ns so RC = 1180.2 ns.

At a bus load of 400 pF: R max =  $2.95 \text{ k}\Omega$

However, for fast-mode the maximum rise time is 300 ns, so at a bus load of 400 pF, R max = 885  $\Omega$ .

For a 3 mA bus pull-up at  $V_{DD} = 5.0 \pm 0.5 \text{ V}$ ; R min = 1.700 k $\Omega$  and at  $V_{DD} = 3.3 \pm 0.3 \text{ V}$ ; R min = 1.0667 k $\Omega$

**Operation at 400 kHz** – Fast- mode devices can only be operated at 400 kHz clock frequency if no standard-mode devices are on the bus. The maximum acceptable capacitive load for 400 kHz operation with a 3 mA current is 331 pF at V pull-up = 3.3 V  $\pm$  0.3 V, and 208 pF at V pull-up = 5.0 V  $\pm$  0.5 V, in order to satisfy the fast-mode rise time requirement.

**Rise Time** – Rise time must be less than or equal to 1000 ns because the device regenerates the  $I^2C$  signal, the pull-up voltages on either side need not be equal, i.e., one side could be 5 V  $\pm$  0.5 V and the other side could be 3.3 V  $\pm$  0.3 V, see figure 4.

**Device Segment Enable** – Only enable or disable the devices when all buses are in an idle state, to prevent system failures.

Enable = 0: Repeater or Hub is disabled Enable = 1: Repeater or Hub is enabled

#### P82B715 TECHNICAL INFORMATION

#### Block Diagram

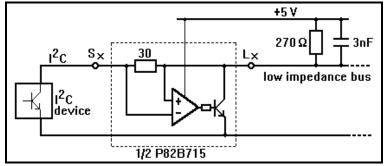

The P82B715 is a bi-directional logic driver that increases the allowable total  $I^2C$  system wiring capacitance and requires no external directional control. It uses unidirectional analog current amplification to increase the current sink capability of  $I^2C$  devices by a factor 10 and the theoretical load capacitance to 4000 pF. Half of the P82B715 block diagram is shown in Figure 8.

Figure 8. P82B715 Block Diagram

The P82B715 device operates with a supply voltage from 3 V to 12.5 V but the logic signal levels at Sx/Lx are independent of the device's supply. They remain at the levels presented to the device by the attached ICs. The P82B715 cannot modify the bus voltage levels but it does contains internal diodes connected to  $V_{CC}$  that will conduct if logic levels exceed the supply voltage by more than 0.5 V. External pull-up resistors pull the connected buses up to the desired voltage level, normally the device supply  $V_{CC}$ .

## Voltage Level Technical Information

The internal current amplifier is activated whenever the input Sx has a lower voltage level than the output pin Lx. It has a small 'input offset voltage' built-in to ensure system stability. In normal application the static voltage difference between Lx and Sx will not exceed 100 mV. The current sunk on the 'buffered' bus Lx is controlled so it does not exceed 10 times the current being sunk at (i.e. flowing out of) the Sx pin and the maximum 3 mA sink current at Sx causes a difference in bus logic 'low' levels (Lx-Sx) of less than 100 mV. This makes P82B715 fully compatible with all logic signal drives, including TTL. The current amplifier also includes slew rate limiting to ensure system stability the selected slew rate makes P82B715 suitable for Standard-mode systems up to 100 kHz. Signals pass from the 'buffered' Lx side back to the Sx ( $I^2C$  bus) side simply via a passive 30  $\Omega$  path. For the specified maximum 3 mA static sink current of  $I^2C$  devices this resistance results in a logic voltage drop (Sx-Lx) of typically 90 mV.

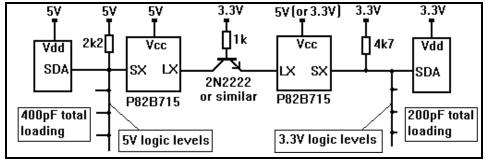

When logic level shifting is required, the impedance transforming action allows a single transistor to be used as shown in Figure 9.

Figure 9. Logic level shifting with P82B715

#### **Design Constraints**

**5** V Bus Operation – The P82B715 was originally designed and specified for 5 V bus operation. The specification deratings that apply when its supply voltage is reduced below the data sheet value of 4.5 V are given in Appendix 3. The absolute minimum supply is 3 V.

**Pull-Up Resistor Sizing** - The pull-down current amplification provided by P82B715 allows reducing the pull-up resistors on its Lx bus side by a factor up to 10 times. Any capacitance connected on the Lx bus side is also "scaled" by a factor 1/10, so 1000 pF of loading at Lx only appears as 100 pF loading of the  $I^2C$  bus at Sx whenever the buffer is active. It is active whenever its Sx pin voltage is lower than its Lx pin voltage. While it is not mandatory to fit pull-up resistors on both sides of P82B715, it is usually best practice to do so. If no pull-up was fitted at Sx, and 200 pF was connected at Sx, then for a rising edge of Lx the amplification will be active and the charging current of the 200 pF will be amplified by a factor 10. This means its 'effective' loading on the bus at Lx is 2000 pF! If a pull-up resistor was fitted at Sx, such that the natural rise-time of Sx becomes faster than the rise-time of the Lx side, then the amplifier in P82B715 will not be activated and there will be no slowing of the bus rise-time at Lx. In fact, there will be a tiny improvement because any pull-up at Sx is always connected via 30  $\Omega$  to Lx.

#### A simple rule saves complex calculations:

Use pull-ups on both sides of P82B715 and ensure that the rise-times calculated for each side meets the I<sup>2</sup>C requirement of 1 µs. This is met whenever their RC product is less than 1.18 µs (see paragraph "Pull-Up Resistor Sizing" page 10)

For the Lx side, all the normal  $I^2C$  impedances may be reduced by a factor up to 10 because its static sink current is 30 mA and the device provides a current gain of 10. The minimum pull-up resistor to 5 V  $\pm$  10% becomes (5.5 V - 0.4 V / 30 mA) = 170 ohms. But that assumes this is the only pull-up in the system. That is allowed, but we recommend using pull-ups on Sx as well. Because P82B715 does not isolate Lx from Sx, the 'effective' pull-up, referenced to any  $I^2C$  bus (i.e., at Sx) must be calculated to ensure it does not exceed 3 mA.

#### Example:

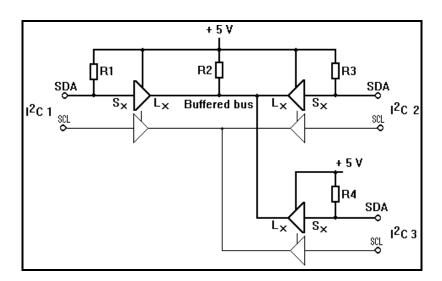

Figure 10. Calculating pull-ups and sink currents (Note: Capacitors & SCL pull-ups omitted for clarity)

Figure 10 shows three P82B715s connected to a common 'buffered' bus. The resistors have been sized to give an RC product of less than 1.18 us so the bus rise time requirement will be satisfied.

An  $I^2C$  device connected at  $I^2C$  1 holding the bus low has to sink the current flowing in its local pull-up R1 PLUS, with assistance from P82B715, the currents in R2, R3 and R4. Because the resistors R3 and R4 act to pull  $I^2C$  2 and  $I^2C$  3 to a voltage higher than the voltage at Lx their buffers will be inactive but these busses will be pulled low via the internal 30  $\Omega$  resistors that link Lx to Sx. So the effective current that must be sunk by the buffer on  $I^2C$  1 is the sum of the currents in R2, R3 and R4. The current that must be sunk at  $I^2C$  1, due to buffer action, is 1/10 of that current.

So the 'effective' pull-up, determining the current to be sunk by an  $I^2C$  device at  $I^2C$  1 is R1 in parallel with resistors 10 times the values of R2, R3 and R4. So, if R1 = R3 = R4 = 10 k $\Omega$ , and R2 = 1 k $\Omega$ , the pull-up load at  $I^2C$  1 is  $10k\Omega$  // $100k\Omega$  // $100k\Omega$  // $100k\Omega$  = 4.55 k $\Omega$

The same calculation applies for  $I^2C$  2 and  $I^2C$  3.

To calculate the current being sunk by the Lx pin of the buffer at  $I^2C$  1, note that the current in R1 is being sunk directly by the  $I^2C$  device at  $I^2C$  1. The buffer therefore sinks the currents flowing in R2, R3, and R4. The effective pull-up equals R2//R3//R4. In this example, it is  $1k\Omega$  // $10k\Omega$  // $10k\Omega$  = 833  $\Omega$ . For a 5.5 V supply and 0.4 V low, that means the buffer is sinking 16.3 mA. Its rated static limit is 30 mA. So the requirement is that the pull-up on the buffered bus, in parallel with all other pull-ups at Sx pins that Lx is pulling low must be a net resistance greater than the allowed minimum of 170  $\Omega$  (for a 5 V system).

#### P82B96 TECHNICAL INFORMATION

#### **Block Diagram**

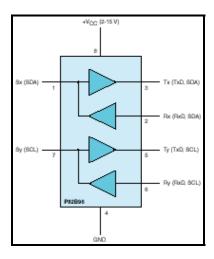

The P82B96 (shown in Figure 11) is a bi-directional buffer device that requires no external directional control and is intended for application in buses such as I<sup>2</sup>C, SMBus, DDB and similar derivatives. It provides full isolation of the buses on its two sides, allowing different voltage levels or impedances to be used.

Figure 11. P82B96 Block Diagram

In normal applications, the Sx side will be connected into a standard I<sup>2</sup>C or SMBus and the logic voltage levels and impedances will conform to the requirements of those systems.

The Tx/Rx side provides the following options:

- a) Normal  $I^2C$  bus, with standard CMOS logic  $0.5V_{DD}$  threshold levels, with  $V_{CC}$  anywhere in the range 2-15 V. In this case, it must comply with bus capacitance limits, rise/fall times, and pull-ups must be selected for  $I_{OL} < 3$  mA. In this option, Tx and Rx pins are externally connected.

- b) Bus with all the special multi-drop, multi-master characteristics of an I<sup>2</sup>C bus yet it need not conform to the bus impedance, capacitance or rise/fall limits. The designer may set these. In this case the I<sub>OL</sub> capability of 30 mA at Tx (10x normal I<sup>2</sup>C) may be used to decrease the bus impedance and allow at least 10 times increase in this bus capacitance (e.g. > 4 nF). The 2 V- 15 V capability may be used to provide improved noise margins when working in a noisy environment. In this option, Tx and Rx pins are externally connected.

- c) The Tx and Rx signals may be used as individual uni-directional logic interfaces to convert the I<sup>2</sup>C signals into any bus hardware format, for example to differential signaling over CAN or RS485 buses. These uni-directional signal transmission paths may include opto-isolators or even radio links. Propagation delays in low speed opto-isolators like 4N36 can limit the bus speed to around 5 10 kHz but higher speed couplers like 6N137 permit full 100 kHz operation and even higher frequencies are possible.

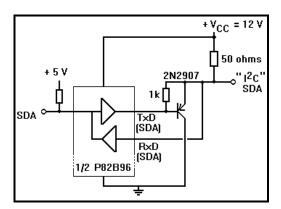

d) The Tx open collector output may be amplified (e.g. by adding a PNP transistor) to further increase the  $I_{OL}$  to 300 mA or more. This allows working over very long buses. See Appendix 1 for more details.

## Voltage Level Technical Information

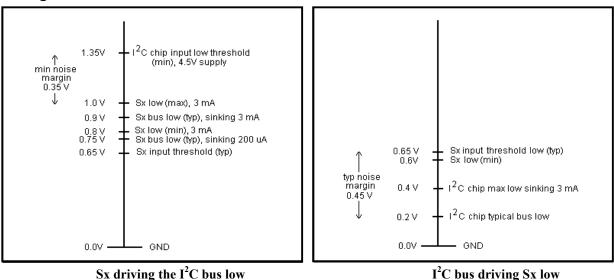

Figure 12. Signal Voltage Levels Compared (at 25 °C)

The low-level input at Sx is set at 0.65 V to give a 0.25 V noise margin above the 0.4 V  $V_{OL}$  specifications limit for standard-mode devices sinking the maximum allowed 3 mA. In order to both drive an  $I^2C$  bus low and detect a contention condition or clock stretching event, the device  $V_{OL}$  at Sx is set at 0.9 V (typical) at 3 mA as shown in Figure 12. This provides a minimum noise margin of 0.35 V below the 0.3V<sub>DD</sub> minimum bus input low specification when working on 5 V  $\pm$  10% supply. The typical noise margin, based on a typical 50% switching threshold, is 2.25 V - 0.9 V = 1.35 V.

Care is needed when connecting a 3.3 V bus at Sx because the typical noise margin with Sx sinking 3 mA is reduced to 1.5~V-0.9~V=0.6~V while the guaranteed margin is 0 V. Where possible, 3.3 V (or lower) devices should be connected on the Tx/Rx side that uses standard CMOS logic levels. If connected to Sx, then the pull-up resistors should be set to the maximum allowed by the rise time, or to provide the Sx minimum of 200  $\mu$ A, whichever needs the lower resistance. Working at 200  $\mu$ A provides a typical noise margin of 1.5~V-0.75~V=0.75~V and even 0.25~V of margin compared to a minimum  $0.3~V_{DD}$  at 1~V.

The temperature coefficient of the bus low created by Sx and the input logic threshold at Sx are equal, so these levels track each for temperature changes. Their coefficient is -2 mV/K.

## Design Constraints

Maximum Current - The  $I^2C$  bus can be operated at no more than 3 mA and the bus IR voltage drops must be controlled such that a Sx I/O sees 0.65 V or less for a valid  $V_{IL}$ . So the Sx input is intended for connection only to devices on the same PCB with relatively low total bus capacitance. Select the pull-up resistor for the lowest pull-up current consistent with bus speed requirements. The minimum pull-up current at Sx is 200  $\mu$ A. The Tx pin can sink a static current of 30 mA for  $V_{OL}=0.4$  V maximum, and typically 100 mA at  $V_{OL}=1$  V. Both Tx and Sx drives are internally current controlled (limited) at about 5 times their static sink ratings.

**Variable Bus Voltage Operation -** The bus pull-up resistors at Sx will normally be tied to the supply for the  $I^2C$  devices connected to it. This I/O has fixed input and output logic levels. The  $V_{IL}$  is 0.65 V and  $V_{OL}$  is 0.9 V, independent of both the device's  $V_{CC}$  and the levels used on the connected bus. Sx may be pulled-up to any required voltage, the limit is 18 V. The logic switching threshold at Rx is related to the devices  $V_{CC}$  as for CMOS logic. It switches at 50% of  $V_{CC}$  but has tighter tolerances than CMOS. Limits are 42% and 58% of  $V_{CC}$ . It is not necessary to use pull-ups to  $V_{CC}$  on the

Tx/Rx interface provided it is recognized that  $V_{CC}$  sets the logic threshold. So operating with  $V_{CC} = 5$  V sets the logic switching level at 2.5 V but it is still allowed to connect to a bus operating with 12 V logic as long as the 1.25 V noise margin (low) is acceptable.

**Pull-Up Resistor Sizing** – The calculations are the same as shown on paragraph "Pull-up Resistor Sizing" page 10 when either side of P82B96 is operated as a standard I<sup>2</sup>C bus. When the 10x drive capability is used then all resistances can be scaled down by a factor 10 and bus capacitance can be at least 10x greater.

**Operation at 400 kHz** – Although P82B96 will clock well above 600 kHz it was designed for operation up to 100 kHz because its propagation delays, and those of connected devices and long buses will rarely permit operation to 400 kHz. If timing calculations for a system indicate 400 kHz is within the necessary limits it can of course be used at the higher speeds.

Rise Times – Bus rise and fall times, and capacitance limits, apply to any bus connected to  $I^2C$  devices. When the Tx/Rx side of P82B96 is being used at non-standard impedance or voltage levels (so only connected to other P82B96 or P82B715 devices) then no such limits apply and the designer is free to set these parameters to suit the application.

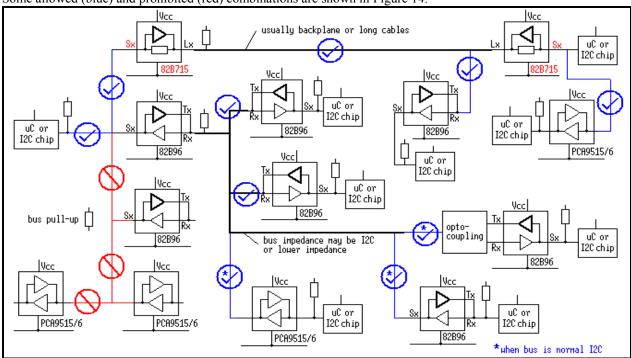

# USE OF MULTIPLE DEVICES IN THE SAME I2C SYSTEM

Series connection of PCA9515 and/or PCA9516 should not be attempted because the output of one device will not be recognized as a low for arbitration purposes by a second device. For the same reason, series connection between two Sx I/O pins of the P82B96, or the interconnection of a Sx I/O of a P82B96 with a PCA9515 or PCA9516 is not permitted. Multiple PCA9511/12/13/14 Hot Swap Buffers can be used in series.

However, it is only the P82B96 Sx pins using special logic voltage levels that should not be interconnected. In the normal application of both P82B96 and P82B715 it is intended that two devices will USUALLY be connected in series. The P82B715 uses normal I<sup>2</sup>C voltage levels, and only one side of P82B96 uses special levels. All sides of the PCA9515/16/18 use special levels.

There are no fundamental restrictions on making series connections between any of the following groups:

- A) The Tx/Rx side of P82B96

- B) Either side of the PCA9511/12/13/14

- C) Either side of P82B715

- D) Either side of just one PCA9515/16, OR just one Sx connection of a single P82B96

The selected system impedance levels, voltages, and propagation delays of course need to be considered.

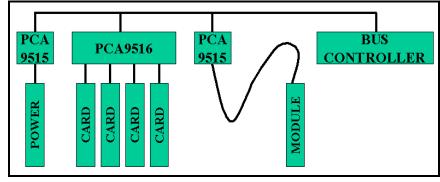

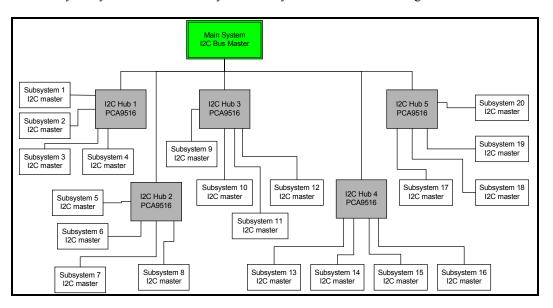

Multiple PCA9515/16 devices are allowed in a system where the devices are not positioned in series and I<sup>2</sup>C components on separate PCA9515/16 devices do not need to talk to each other. In the example in Figure 13, the bus controller can talk to the power supply, cards or module, one at a time or it could talk to all of them at the same time if the power supply, cards and module didn't ever need to talk with each other or hear different device acknowledgements. The power supply, cards and module can never talk to each other since a low will not be transmitted between two PCA9515/16 devices in series. All cards on the PCA9516 can talk to each other and the bus controller since they are on the same hub.

Figure 13. Multiple Parallel PCA9515/16 Devices

The PCA9518 was designed to allow larger systems where all segments need to be able to talk with each other.

Some allowed (blue) and prohibited (red) combinations are shown in Figure 14.

Figure 14. Various Ways to Interconnect Repeaters, Hubs and Extenders

## **APPLICATIONS**

### Bus Expansion beyond the 400 pF Limitation

Adding more I<sup>2</sup>C and SMBus devices on the bus may exceed the 400 pF limitation. The PCA951x/15/16/18 can isolate device and trace capacitance to different segments that are 400 pF or less capacitive loading so that the I<sup>2</sup>C and SMBus devices can operate properly. A typical PCA9515 application is shown in Figure 16.

Figure 16. Typical Bus Expansion Application

#### Split Bus 100 kHz and 400 kHz Application

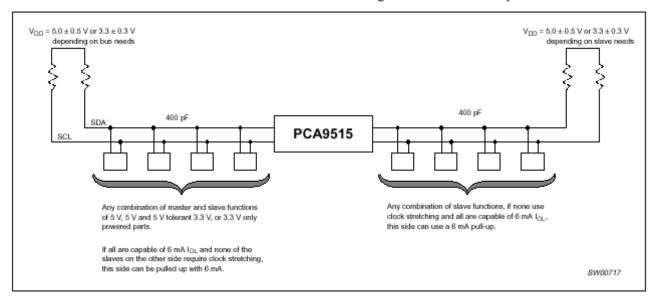

If all masters are on one side of the PCA9515 repeater and none of the slaves on the other side of the repeater use clock stretching and if all of these slaves are capable of 6 mA I<sub>OL</sub>, as shown in Figure 17, then the slave side pull-up can be sized for 6 mA because there will be no contention nor clock stretching to be communicated by the PCA9515.

Figure 17. PCA9515 in Split Bus 100 kHz and 400 kHz Application

If all of the masters and slaves on the master side of the PCA9515 are capable of fast-mode operation, none of the slaves on the opposite side of the repeater require clock stretching and the master(s) are able to generate enable and disable changes during the bus idle time. Then the enable feature of the PCA9515 could be used to isolate the master side to allow the master to run at 400 kHz rather than the standard-mode 100 kHz necessary when any standard-mode slave are present on the slave side of the repeater.

If an individual slave is particularly badly behaved during power-up but performs correctly after power-up, or power-up and system reset on power-up, then the PCA9515 enable function could be used to isolate the offending device until it is well behaved and both sides of the repeater are in an idle state. The enable should never be changed, enabled nor disabled, except when both sides of the repeater are in an idle state. If the device being isolated is a slave that does not use clock stretching, then the isolation technique and the standard bus expansion technique can be combined.

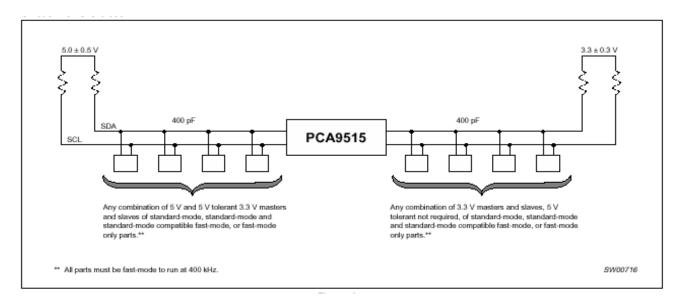

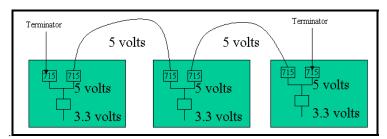

#### Voltage Level Shifting

Many  $I^2C$  and SMBus devices operate at different voltage levels but need to operate on a common bus. The PCA9515/16/18 allows translations between 3.3 V and 5 V. So, for example, a 5 V  $I^2C$  master on one segment can communicate with a 3.3 V (non 5 V tolerant) SMBus device on different segment. The channel pass gates are constructed such that the  $V_{DD}$  pin can be used to limit the maximum high voltage that will be passed by the device. This allows the use of different bus voltages on each pair, so 3.3 V devices can communicate with 5 V devices without any additional protection as shown in Figure 15. All I/O pins are tolerant to 6.0 V. The PCA9512 with two  $V_{CC}$ s can also be used to translate between 3.3 V and 5 V buses. Refer to Philips application note AN10160-01 for more information. The GTL2000/02/10 can also be used to translate between any voltage between 1.0 V and 5.5 V but these devices do not buffer any capacitance. Refer to Philips application note AN10145-01 for more information..P82B96 allows logic level shifting in the range 2V to 15V and can be useful to improve noise immunity on long buses.

Figure 18. Typical Voltage Translation Application

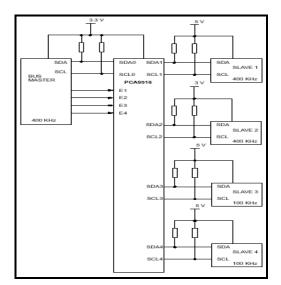

# I<sup>2</sup>C Multiplexing

Some specialized devices only have one I<sup>2</sup>C address and sometimes several identical devices are needed in the same system. The PCA9516 and PCA9518 could be used to both isolate capacitive load and to connect one downstream segment at a time to the bus master, where each downstream segment contains identically addressed devices. This would eliminate address conflicts. The PCA954X family of devices can also be used for multiplexing but **they do not regenerate the I<sup>2</sup>C signal and do not isolate the bus capacitance** to each segment. Refer to Philips application note AN262 for additional information on the Multiplexer and Switch family. In Figure 19, the PCA9516 is used to multiplex between Slaves 1 through 4 where it is assumed that there are identically addressed devices on each slave module.

Figure 19. Typical Multiplexing Application

Multiple PCA9516s can be attached in parallel to a common master bus if only one hub's segments will be active at any one time or the hub segments do not need to talk with each other. PCA9518s should be used if more than one hubs segment must be active at the same time and any hub segment to any other hub segment communications is required.

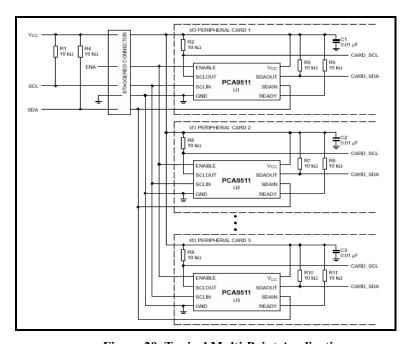

## I<sup>2</sup>C Multi-Point Hot Swap Applications

Use of the I<sup>2</sup>C bus in backplane systems is increasing and either a point to point arrangement with multiple individual buses to each line card from the master or a single multi-point bus to every line card is used. The PCA9511/12/13/14 are designed for this multi-point application. They have:

- A precharge feature for the SDA and SCL pins to prevent glitching the bus (PCA9511/12)

- An idle detect circuit that will not connect the multi-point bus to the slave devices on the line card until the bus is idle (PCA9511/12/13/14).

In Figure 20, the PCA9511 is used in this multi-point application. Refer to Philips application note AN10160-01 for more information on the PCA9511/12/13/14.

Figure 20. Typical Multi-Point Application

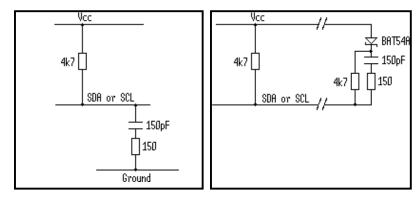

# I<sup>2</sup>C Bus Extension Over Long Cables

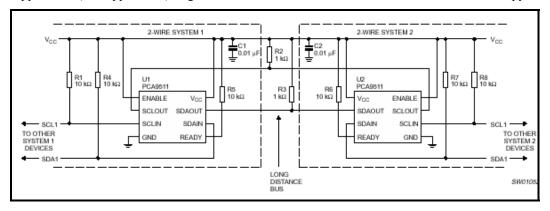

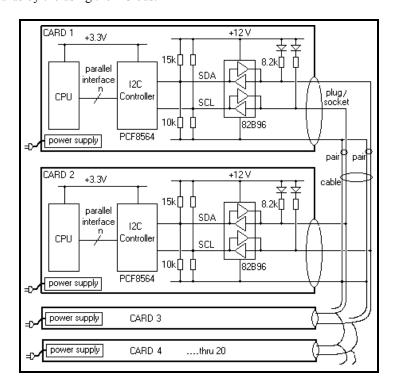

The I<sup>2</sup>C bus is normally used in small localized areas but some applications may require extending the I<sup>2</sup>C bus further. There are several devices that can be used to extend the I<sup>2</sup>C bus over cables for a significant distance. The PCA951x, P82B715 and the P82B96. The PCA9511/12/13/14, P82B715/96 can all be used in series. The P82B96 is recommended for this application (see Appendix 1). Figure 21 shows the PCA9511 which can also be used in this application.

Figure 21. Typical Cable Bus Extension Application using the PCA9511

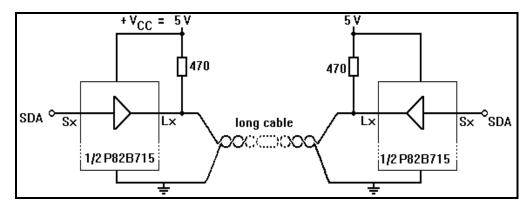

The P82B715 can be used to extend I<sup>2</sup>C over a cable and is shown in Figure 22A.

Figure 22A. Typical Cable Bus Extension Application using the P82B715

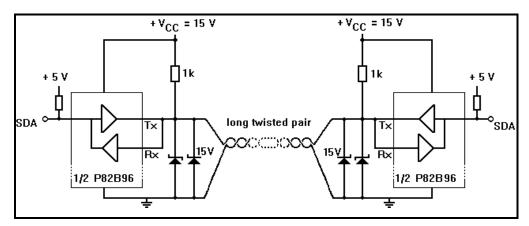

The P82B96 can be used to level shift and extend I<sup>2</sup>C over a cable and is shown in Figure 22B. The Schottky diodes help suppress ringing on cables that are not correctly terminated, see Appendix 5, and the Zeners may be required to protect against excessive voltages coupled into very long wiring.

Figure 22B. Typical Cable Bus Extension Application using the P82B96

There are advantages and disadvantages of each buffer device, some of which are outlined in this selection table:

| CABLE DRIVE APPLICATION                 | PCA9515     | P82B96<br>on Sx on Tx/Rx |            | P82B715<br>on Sx on Lx |            |

|-----------------------------------------|-------------|--------------------------|------------|------------------------|------------|

|                                         |             |                          |            |                        |            |

| Max. cable capacitance<br>3nF approx    | 400 pF      | 400 pF                   | > 4 nF     | 400                    | pF         |

| Bus (cable) logic voltage               | 3.0 - 3.6 V | 3.3 - 15 V               | 2 - 15 V   | 3 - 12                 | 2 V        |

| Bus logic sink current max.             | 3 mA        | 3 mA                     | 30 mA      | 3 mA                   | 30 mA      |

| Max I <sup>2</sup> C clock speed        | 400 kHz     | 400 kHz                  |            | 100 k                  | κHz        |

| Cable length recommended                | very short  | very short               | unlimited  | as I <sup>2</sup> C to | 30 m/100'  |

| Logic 'low' level                       | 0.4 V       | 0.5 V                    | $V_{cc}/2$ | as conne               | cted chips |

| Typ noise margin, input driven 'low'    | 0.2 V       | 0.3V                     | $V_{cc}/2$ | as conne               | cted chips |

| Logic 'low' output voltage max          | 0.6 V       | 1 V                      | 0.4 V      | input leve             | el +0.1V   |

| Typ noise margin output low, 3.3V logic | 1.1 V       | 0.65 V                   | 1.5 V      | 1.4                    | V          |

| Typ noise margin output low, 5V logic   | 2 V         | 1.6 V                    | 2.3 V      | 2.2                    | V          |

| Typ noise margin output low, TTL logic  | 0.8 V       | 0.4 V                    | 1.2 V      | 1.1                    | V          |

| Logic levels to cables can be shifted   | yes         | yes                      |            | no                     |            |

| Typ propagation delay                   | 100 ns      | 300 ns                   | 3          | 400                    | ns         |

Table 2. Cable Bus Extension Selection Guide

# I<sup>2</sup>C Opto-Electrical Isolation

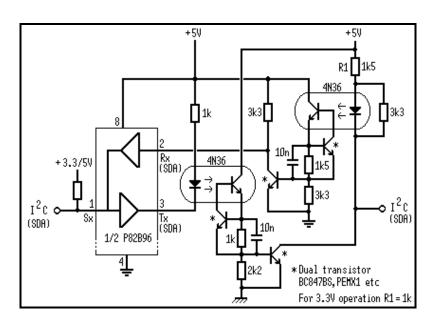

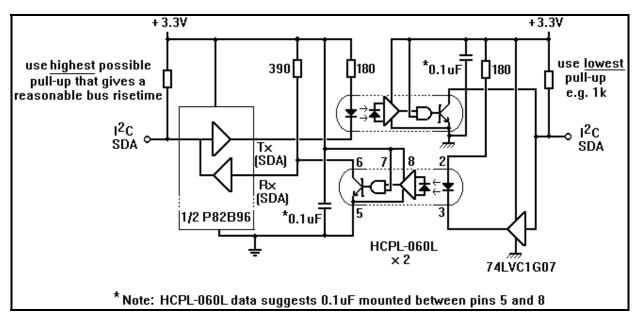

The P82B96 can be used for opto-electrical isolation. In Figure 23, the P82B96 is used in the simplest low speed application. More information can be found in Philips application note AN460. A faster circuit, suitable for approximately 50kHz but still using low cost Optos, is shown in Figure 24. A very high speed circuit is shown in Figure 25.

Figure 23. Simple 5 kHz Opto-Electrical Isolation Application

Figure 24. 50 kHz application with general purpose low speed Optos

Figure 25. Suggest circuit for highest speed Opto-coupling

With the correct choice of master and slave devices this circuit can be toleranced for up to 400 kHz operation.

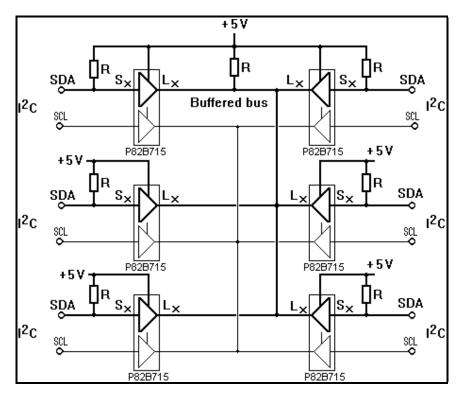

#### **Multiple Segment Application**

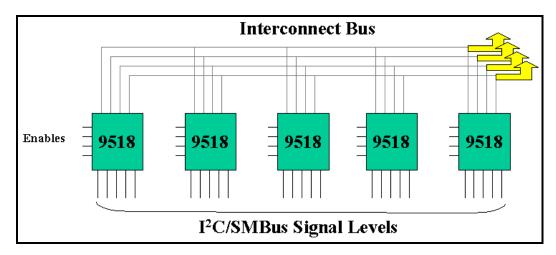

The PCA9518 is similar to the PCA9516 but with four extra open drain signal pins that allow the internal device logic to be interconnected into an unlimited number of segments with only one repeater delay between any two segments as shown in Figure 26. The PCA9518, like the PCA9515/16, is transparent to bus arbitration and contention protocols in a multi-master environment and a master can talk to any other master on any one of the I<sup>2</sup>C segments. The enable pins isolate four of the five PCA9518 segments. A pull-up resistor needs to be placed on unused segments that do not have a hardware disable pin.

Figure 26. PCA9518 Interconnect Bus

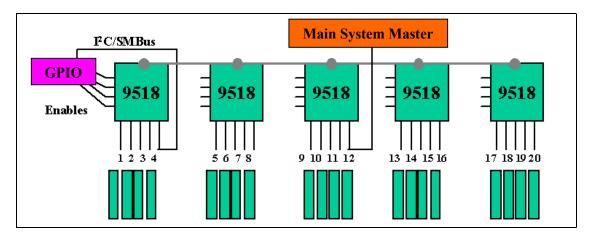

Using the PCA9518 in the 20 card application shown in Figure 27.

- Any submaster can talk to any other submaster on any of the line cards and the main master can talk with any submaster with only one repeater delay.

- An I<sup>2</sup>C General Purpose I/O Expander with the capability of changing its output states at a STOP command only. This allows the master to enable and disable the PCA9518 segments without confusing devices on the segment becoming isolated or being returned to the main bus. If a normal GPIO is used (i.e., I/O' changes state after the command register is sent, during the Acknowledge sequence) then the devices on the bus would not see the stop

prior to being isolated or would only see the stop or a partial sequence of I<sup>2</sup>C commands if returned to the bus. The GPIO is controlled by the main system master and can isolate cards 1 through 4 using the enable pins on the PCA9518. Additional GPIO devices can be used to control I<sup>2</sup>C signals to all the submaster cards

- Another option is for the master to directly control the PCA9518 enable pins but that may require longer trace lengths and multiple GPIO on the microcontroller. This would however ensure that the segments could be individually isolated if for some reason the I<sup>2</sup>C bus locks up and the remote GPIO is no longer operational.

- Pull-up resistors are required for the 4-wire inter-device bus. Value depends upon the number of devices connected together. The RC constant of the node needs to be taken into account. Maximum current is 12 mA. 500  $\Omega$  on each node can then be used.

Note that channel 0 is not used for the card slots. The reason is that if cards are connected to channel 0, they cannot be isolated from the main bus since channel 0 does not have an Enable pin.

Figure 27. PCA9518 in 20 Slot Application

#### FREQUENTLY ASKED QUESTIONS

#### Device usage and differences

1. **Question**: What are the main differences between the PCA9515 and the P82B96? **Answer:** The main 'buffering' differences are related to the logic operating voltage levels and drive current capability. In addition, the P82B96 has a capability to split the bi-directional I<sup>2</sup>C bus into two conventional unidirectional logic signals or to re-combine two such signals to form normal I<sup>2</sup>C signals again.

The P82B96 is intended for use in systems that will typically include significant propagation delays (long cables or opto-couplers) so it will normally be applied in standard-mode systems but can clock up to 600 kHz. PCA9515 offers much shorter propagation delays and will be the usual choice for 400 kHz systems.

PCA9515 is a symmetrical device with standard I<sup>2</sup>C sink-current capability while P82B96 has standard I<sup>2</sup>C drive capability on one side (Sx) but up to 30 mA static sinking (10 times normal level) on the other (Tx) side. The PCA9515 (both sides) and P82B96 (Sx side) use special logic thresholds to prevent bus latch-up. The P82B96 uses perfectly standard half-rail logic levels on its Rx side so that I/O is fully compatible will all logic families and there is no (theoretical) limit to the number of other P82B96 devices allowed to be interconnected in a multi-drop bus configuration.

#### Repeater, Hub and Bus Extender Selection Summary

| FEATURES                                                   | PCA9515                    | PCA9516                    | P82B96                    | P82B715                         |

|------------------------------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------------|

| Data sheet supply voltage range V <sub>CC</sub>            | 3.0 - 3.6 V                | 3.0 - 3.6 V                | 2.0 - 15.0 V              | 4.5 - 12.0 V                    |

| Nominal logic levels supported (range)                     | V <sub>CC</sub> to 5.5 V   | V <sub>CC</sub> to 5.5 V   | V <sub>CC</sub> to 15.0 V | Equal/less than V <sub>CC</sub> |

| Allows I <sup>2</sup> C bus logic level shifting (range)   | 3.0 - 5.5 V                | 3.0 - 5.5 V                | 2.0 - 15.0 V              | no level shifts                 |

| Allows interconnecting I <sup>2</sup> C buses, each 400 pF | yes, 2<br>I <sup>2</sup> C | yes, 5<br>I <sup>2</sup> C | yes, 2                    | no                              |

| On-chip bus sink current capability                        | I <sup>2</sup> C           | I <sup>2</sup> C           | 10x I <sup>2</sup> C      | 10x I <sup>2</sup> C            |

| Drives lower impedance " I <sup>2</sup> C like" buses      | по                         | no                         | yes                       | yes                             |

| Max. (multimaster) bus capacitance supported               | 800 pF                     | 2000 pF                    | unlimited                 | 3000 pF approx                  |

| Allows inter-working of I <sup>2</sup> C and SMBus         | yes                        | yes                        | yes                       | no                              |

| Designed operating I <sup>2</sup> C clock speed            | 400 kHz                    | 400 kHz                    | 400 kHz                   | 100 kHz                         |

| Typ. propagation delay (excluding contention)              | 100 nsec                   | 120 nsec                   | 300 nsec                  | 400 nsec                        |

| (Multimaster) system configuration                         | repeater                   | hub/star                   | multi-drop bus            | multi-drop bus                  |

| Splits I <sup>2</sup> C to Tx/Rx allowing opto-isolation   | no                         | no                         | yes                       | no                              |

| Releases all I/Os if V <sub>CC</sub> supply fails          | yes                        | yes                        | yes                       | no                              |

| I/Os can be pulled above chip's V <sub>CC</sub> level      | yes, to 5.5 V              | yes, to 5.5 V              | yes, to 15.0 V            | no                              |

| Logic "buffer enable" input(s)                             | yes                        | yes, 4                     | no                        | no                              |

| Supply current (typical)                                   | 2 mA                       | 7 mA                       | 1 mA                      | 16 mA                           |

| Packages                                                   | TSSOP/SO8                  | TSSOP/SO16                 | DIL/SO8                   | DIL/SO8                         |

Table 3. Repeater, Hub and Bus Extender Selection Summary

2. **Question:** Can the PCA9515/16 be used in series?

**Answer:** No, two of the PCA9515/16/18 cannot be used in series, or one of these connected to the Sx I/O pin of the P82B96. The reason is because of the way these devices sense whether a low on the line is being driven externally (e.g. by a device on the bus connected to that segment) to the device or internal (e.g. by a device on a bus connected to the opposite side of the device) to the device. A low on one end of the bus will not be seen as a low at the other end of the bus if it must travel through more then one repeater/hub/extender. The Philips PCA9511/12/13/ are being designed to be used in series. Normally two P82B715s can be used in series because they do not use special logic levels. It is allowable to connect the PCA9515/16 to the Tx/Rx side of the P82B96 or to either side of the P82B715.

3. **Question:** We have an application for 30 identically addresses I<sup>2</sup>C slaves, each 2 meters from the bus master and we need a bus wiring solution.

**Answer:** Possible solutions include:

- 1. Use four of the 8-channel PCA9548 switch in parallel and activate only one downstream channel at a time. Some concerns would be the capacitive loading of the 2 meter wiring exceeding the 400 pF limitation, but at 80 pF/m, it should not happen.

- The PCA9548 uses I<sup>2</sup>C commands to activate and deactivate the downstream channels. The channel does not shift until the STOP command is sent by the master and the switch acts only as a wire and does not regenerate the signal.

- 2. Use the P82B715 or P82B96 in a multi-point arrangement that can help extend the bus longer distances (e.g., 30 meters depending on the transmission means). The P82B96 has a split output port bus buffer that can also be used for interfacing to other cable drivers allowing differential transmission of the I<sup>2</sup>C signal, optically isolating the I<sup>2</sup>C bus or just increasing the bus voltage to improve the noise margin.

- 3. Use eight of the 5-channel PCA9516 in parallel. The bus master would connect to the SD0/SC0 segment of all eight PCA9516s and then the master would use its GPIO (30 GPIOs are needed) to enable and disable the required downstream segment one at a time. Each segment isolates capacitance from the other segments so 400 pF is allowed on each 2 meter trace. The PCA9516 uses hardware enable pins to activate and deactivate the downstream channels. More than one segment can be enabled at the same time but the limitations are that although a segment on hub A can talk multi-directionally with any other segment on hub A, it will not be able to send a low signal to downstream segments on hub B, C, D, etc. Since in this application only one segment can be enabled at a time, each segment has slave devices with the same I<sup>2</sup>C address, this will not be a problem. The 4-channel PCA9516 hub does the selection via hardware pins and the bus needs to be idle before adding or removing channels. The hub also allows 400 pF per channel since the signal is regenerate by the hub.

**Bottom Line** - The PCA9516 would be the better solution since all downstream segments can be physically isolated should the bus hang up and it isolates the capacitive loading to each segment. The PCA9548 however has a hardware reset pin that opens all channels if the bus should hang up so the master can regain control. The PCA9548 should be considered if reduced cost is important (only 1/2 as many devices are needed) and it is desired to use I<sup>2</sup>C commands to select channels since 30 extra GPIOs are not available on the bus master. You can't use standard I<sup>2</sup>C GPIO slaves to expand your master I/O to enable and disable the PCA9516 since GPIO changes state on acknowledge, before the slave would see the stop command, and the slave would become confused. A GPIO changing the I/O state at a STOP command is required.

4. **Question:** We are passing signals from a PCA9515 through the PCA9544. On the  $I^2C$  bus lines, they are using a 1.3  $k\Omega$  pull-up to 3.3 V on the PCA9515 side of the pass transistor and a 20  $k\Omega$  pull up to 3.3 V on the other. We see a PCA9515 Vol = 0.5 V to 0.6 V and on the other side of the pass transistor a signal level of 0.7 V to 0.8 V. This makes the combination unsuitable for use with a Linear Tech ® LTC4300-1 (which has a max Vil spec. of 0.6 V and which is used on the other side of the pass transistor). Does Philips have a plot of Vol vs Iol for the PCA9515-if we're at 0.6 V @ 2.7 mA, we will be out of data sheet specification at 6 mA. Using the 20  $k\Omega$  ohm resistors, they appear to be limiting the amount of current through the pass transistor in order to reduce the drop across it. From the calculations, they have about 165  $\mu$ A of pull-up current through the pass transistor. To get a 200 mV delta Ron is quite considerable. Do we see any Ron dependency with through current?

**Answer:** You are suffering from one of the unintended outcomes of using the LTC4300-1 device.

- The PCA9515 uses an output driver that is essentially a voltage source that only sinks current and its level is set at 0.52 V. Thus, from zero to more than 10 mA, the output voltage only changes by a few millivolts. Even with variations over process, temperature, and power supply, the voltage is within a few tens of millivolts of 0.52 V. The output voltage at even 10 mA is less than 0.6 V.

- The maximum Ron for the PCA9544 is 55  $\Omega$ . Assuming 135  $\mu$ A from the 20  $k\Omega$  resistor, the voltage drop across the PCA9544 should be less than 0.01 V. Even at 55  $\Omega$  Ron, which is the maximum limit, to get a 0.2 V drop across the PCA9544 would require 3.6 mA.

Therefore, the LTC4300-1 is the most likely source of the extra current. I believe a check of the system with the LTC4300-1 removed will confirm that the voltage driven at the output of the PCA9544 is less than 0.6 V. The problem is that the "pull-up" current one-shot in the LTC4300-1 is being triggered by noise and is contending with the low level driven by the PCA9515. The pull-up current source in the LTC4300-1 speeds the low to high transition by increasing the total pull-up current and is switched off when the pin is high so as not to contend on the next high to low transition. If the current source of the LTC4300-1 gets turned on when the PCA9515 is driving a low, it will remain on because the pin does not go high. The current supplied by the current source will be high enough to pull the voltage up to 0.7 V - 0.8 V.

Note: The LTC4300-1 is 100% equivalent to the Philips PCA9511 and the LTC4300-2 is 100% equivalent to the Philips PCA9512.

5. **Question:** We are having problems with the PCA9516 and want to replace it with an analog multiplexer solution. Can you share any information to justify the need for these hub devices and discuss in more detail how arbitration is used (beyond what is in the data sheet)?

**Answer:** The PCA9515/16 provide the principal benefit of allowing the system to be increased in size well beyond the 400 pF limit in the I<sup>2</sup>C specification by physically separating the system into branches. Each branch can be loaded up to 400 pF. The enables can be used to isolate faulty branches, or resolve address conflicts, however to prevent system problems the enable pins should only be switched during an idle state. Acknowledge and arbitration is fundamental aspects of I<sup>2</sup>C protocol. Arbitration only applies to multiple master systems however acknowledge is used between master and slave to confirm byte transactions. If you only need to multiplex the lines and loading is not a problem, we offer a family of I<sup>2</sup>C controlled multiplexers and switches under the PCA954X series.

#### Live insertion

1. **Question:** Can the PCA9515 be used in a Hot Insertion application? I'm worried about when the main system power is off and the PCA9515 is not energized. What happens when one of the cards is plugged in? Could the active I<sup>2</sup>C signal voltage damage the device?

**Answer:** When the PCA9515/16/18 are powered off, the SCL and SDA pins are in a high impedance state so a voltage being applied to them will not damage the devices. The PCA9511/12/13/14 are specially designed for hot swap applications.

2. **Question:** Is it possible to pull up some of the hub downstream I<sup>2</sup>C channels to a permanent supply line and some others to a switched supply lines?

**Answer:** When the hub is in operation and the channel is enabled, the channel termination voltage must be on to pull the  $I^2C$  bus high. If the channel is disabled, then the channel termination voltage can be turned off.

3. **Question:** If the PCA9516 is powered up and a channel enabled what will happen if I remove the channel's pull-up voltage?

**Answer:** If the power supply is turned off, it will almost certainly pull low. If the power supply is removed, then the leakage current will determine what happens. If the leakage to ground dominates, it will go low and if the leakage to a high dominates it will stay high. (High is an unlikely outcome especially if no power is present).

4. **Question:** In the theory of operation you refer to a pull-down resistor - if I remove the pull-up voltage will I in fact pull down to GND and lock every channel up?

**Answer:** Most likely, if the channel is enabled and drifts low because the pull up supply is removed it is recognized as a low and will be repeated on all enabled channels for as long as the condition exists or until the channel is disabled, which ever comes first.

5. **Question:** What is the behavior of the PCA9516 hub when the switched supply is switched off?

**Answer:** When power is cut to the PCA9516 hub, the device outputs go to a high impedance state and no communication through the hub is possible. When in a high impedance state, the outputs will not affect operation of the segment and normal I<sup>2</sup>C communications are possible on that segment, however, none of the 5 segments will be able to talk to each other. However care must be taken if segments are conducting independent conversations when reconnecting or restoring power. Discussion of the software routines to cover all the possibilities during power failures or hot-plugging is beyond the scope of this application note and will be covered separately.

6. **Question:** Does the PCA9516 Hub power supply need to be put on the same supply that powers the microcontroller (permanent supply) or a switched supply?

**Answer:** It does not matter to the PCA9516 hub. If it is the permanent power supply then the device is always active and the downstream channel need to be pulled high or disabled. If switched off, all outputs go to a high impedance state and no communication is possible through the hub.

7. **Question:** What about Fault Tolerance? How do the devices fail? Would it be possible to tri-state the I<sup>2</sup>C bus interface in case there is a problem and makes the bus hanging up? This would make our system better and will give them a better Fault Tolerance.

Answer: Modern ICs have extremely low failure rates so failures will almost always be due to overstress.

Overstress can be prevented by applying protection measures where the likelihood of overstress justifies this extra cost. Devices like P82B96 have very high typical breakdown voltages, over 25 V on the Sx and almost 50 V on Tx pins so it is relatively easy to apply protection clamps set at around the data sheet limit voltage (15 V - 18 V) that will not influence normal operation.

The P82B96 is relatively new and has no reported failures. It is closely related in technology to P82B715. In selling that device for 7 years I think the Quality and Failure Analysis lab has only ever seen about 4 defective products returned. All were at the same time and due to an unusual customer application that was not protected in our testing or data. We calculated the chance of other faulty devices at 1 in 10,000 and even that was restricted to production in a short time interval (due to a mask defect) it cannot happen again because we have added factory tests for it. I am not aware of any field returns for any cause in the last 4 years (since that test was added), or in the earlier period.

The PCA9511/12/13/14/15/16/18 and P82B96 are designed to release their I/Os if their power supply fails, so the bus is available for other devices to communicate. The PCA9515 Repeater and PCA9516/18 Hubs also features an Enable pin that provides the tri-state function. So several devices are offered that can be used to isolate failure problems PROVIDED the problems can be software-diagnosed -- for example by isolating sections of the bus in turn and testing for shorts until the faulty section is found.

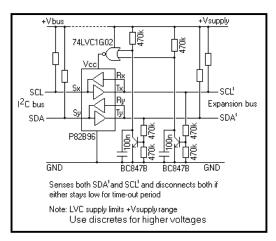

It is also possible to include simple hardware circuits that check the state of the bus lines and cause disconnection of sections if the bus stays low for longer than a designed period. Some SMBus devices integrate this function. An example of such hardware is shown in Figure 28.

Figure 28. Bus "stuck low" sensor schematic

## I<sup>2</sup>C over long distances

- 1. **Question:** The PCA9515 is being used in the network between the server and peripherals.

- Is there any rule for the distance of I<sup>2</sup>C Bus?

- Is there any method to improve signal quality in the I<sup>2</sup>C Bus in the cable length of 1m?

Answer: There is no maximum length specified in the I<sup>2</sup>C specification. The limit of the length is a function of several factors including capacitance (usual maximum limit is 400 pF), the minimum value for Rp, propagation delays along the cables, the type of cable used and the integrity of the logic signals in the presence of noise. There are bus rise and fall times that must be met with limits set by the static and dynamic sink capability of standard I<sup>2</sup>C devices (3 mA sink current etc). There are some ways to improve the rise time by using a switched pull up circuit. At 400 kHz data rates, there is not any problem with transit time for just 1 meter of cabling. This assumes the question refers to cable propagation delay, then there's no 'problem' with PCA9515 (100 ns each way) and no problem with 1 meter (10 ns round trip) and a bus 'low' time of 1.3 μs. Appendix 1 covers these complex calculations.

- 2. Question: There is an old P82B715 App note about a "mile long" I<sup>2</sup>C. Is that practical?

Answer: No, certainly not for P82B715. In real applications it is fine (conservatively and well proven) to about 100 feet at 5 V at 100 kHz. It was explained in the application note that the result was obtained only under perfect lab conditions, and with low clock speeds. Signal propagation delays over a mile are around 17 microseconds meaning the clock speed certainly cannot exceed about 25 kHz. If a mile is really needed then it could be achieved using the P82B96 with the circuit in Appendix 1 provided the necessary protection against things like lightning-induced currents are included.

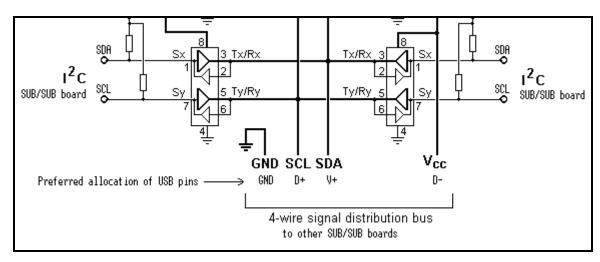

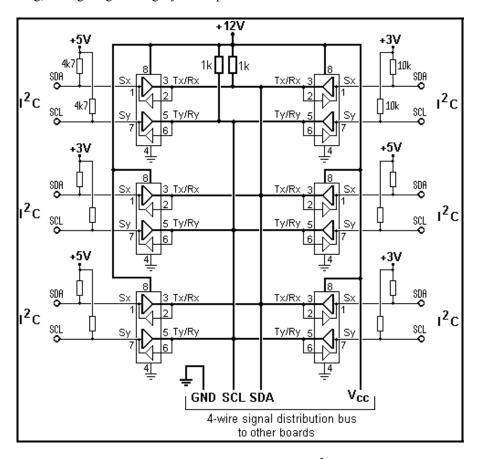

- 3. **Question:** We really want to simplify the board design and wiring by using an I<sup>2</sup>C bus and would rather use the P82B715 than the P82B96 because the number of cables will be reduced from 6 to 4. We want to use USB cables and USB connectors as the physical connectors for the P82B715 because they are easy to obtain and the price is very low.

**Answer:** When distributing I<sup>2</sup>C signals using 'buffer' ICs like P82B96 or P82B715 the signals that are distributed are usually just the same ones as for I<sup>2</sup>C. We just use 4 wires. So we 'buffer' the SCL and the SDA signals, but we still only require one signal wire for each of these signals. It is helpful to send the two logic signals (SDA and SCL) with a return (ground) wire for each. So we would like to send (SCL plus Ground) and (SDA plus Ground). That takes 4 wires to send the I<sup>2</sup>C signals to each sub-sub board. It is also allowed to substitute a voltage supply wire for one of the ground signals, because the supply will also be bypassed to ground.

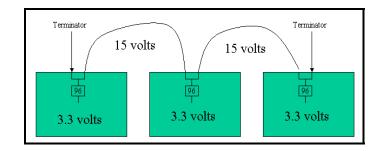

So then you would use two pairs of wires: (SCL with ground) and (SDA with the positive supply wire). That is 4 wires in total. This is usually exactly the same for both P82B96 and P82B715. The pins Tx and Rx will be connected together and pins Ty and Ry will be connected together. Then P82B96 buffer I/O connections become: Input at Sx, output is Tx linked to Rx. Input at Sy, output at Ty linked to Ry.

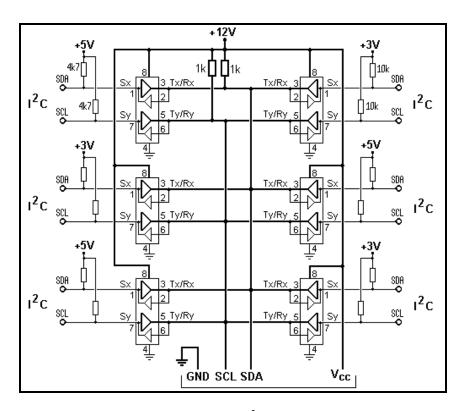

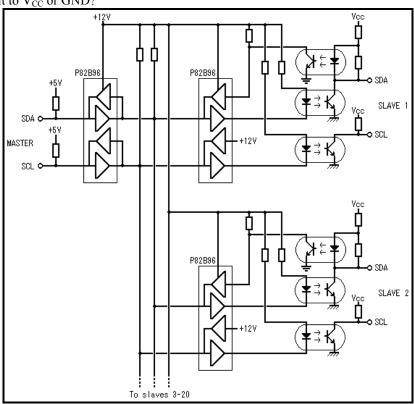

Figure 29 below shows how I<sup>2</sup>C signals would be distributed to all the sub/sub boards with the P82B96. Notice there are only 4 wires in the suggested "expansion bus" that distributes the I<sup>2</sup>C signals. In this example this "distribution bus" is using 12 V logic signals so that it will be very immune to noise. It is not necessary to use 12 V logic, it will also work with 5 V or any other voltage that is convenient to use.

Figure 29. Distribute I<sup>2</sup>C using USB cables (1)