### Freescale Semiconductor

#### Application Note

AN2298/D Rev. 0.1, 2/2003

Nexus Interface Connector Options for MPC56x Devices

Randy Dees TECD Applications The Nexus interface is a new industry standard that crosses CPU boundaries and allows industry-standard tools to support multiple CPU architectures. It allows advanced debug capabilities by providing high-speed access to the microcontroller core. These advanced debug capabilities include trace, without requiring extensive external circuitry to monitor an external address bus. A Nexus-compliant class 2 or greater device allows non-intrusive trace on a microcontroller in single-chip mode or a microcontroller without external data and address buses.

An IEEE-ISTO 5001<sup>™</sup>-1999 <sup>1</sup> Nexus Class 3 interface is included on the MPC56x family of microcontrollers. The Nexus standard, as implemented on the MPC56x, is referred to as the Real-time Embedded Application Development Interface (READI).

This application note addresses connector options for the MPC561, the MPC563, and the MPC565 and replaces *MPC565/MPC566 Nexus Interface Connector Options* (AN2002).

### 1 Nexus Connector Options

The 5001-Nexus standard defines several different standards for different speed accesses to a microcontroller in a target system. These standards have been revised since that release. The new connectors come in both a robust and a non-robust configuration. In addition, each connector has 2 definitions depending upon whether the connection is an Auxiliary only (Auxiliary In and Auxiliary Out) connection or a JTAG IEEE 1149.1 port with an Auxiliary Output port.

#### NOTE

The MPC56x parts do not support the JTAG IEEE 1149.1 configuration.

### 1.1 Non-Robust Connectors

The Nexus connectors are available in several pin counts from the low-end connector A (26 pins) to the high-end connector D (80 pins), which includes a port replacement for the Nexus port microcontroller signals. In addition, the new standard also defines a 40-pin connector B

<sup>&</sup>lt;sup>1</sup>Nexus 5001-1999 (Version 1.0) is the current release of the standard. This application note describes connectors that have been approved by the Nexus Consortium Hardware Technical subcommittee, but have not yet been included in a new released version of the standard.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

For More Information On This Product, Go to: www.freescale.com

and a 50-pin connector C, both of which feature IEEE 1149.1 and Auxiliary port options. See Table 1 for a listing of the possible Nexus connectors.

|                                  | Non-Robust        |                                            |                                  | Rob               |                                  |                                                                                  |

|----------------------------------|-------------------|--------------------------------------------|----------------------------------|-------------------|----------------------------------|----------------------------------------------------------------------------------|

| Connector<br>Option <sup>1</sup> | Number<br>of pins | AMP, System 50<br>Connector Part<br>Number | Connector<br>Option <sup>1</sup> | Number<br>of pins | Glenair Connector<br>Part Number | Comments                                                                         |

| A1                               | 26                | 1-104068-2                                 | A1R                              | 25                | MR7580-25P2 BNU                  | Minimum Combined IEEE<br>1149.1/Auxiliary Out<br>Nexus Configuration JTAG        |

| A2                               | 26                | 1-104068-2                                 | A2R                              | 25                | MR7580-25P2 BNU                  | Minimum Auxiliary Port<br>Nexus Configuration                                    |

| B1                               | 40                | 104549-6                                   | B1R                              | 37                | MR7580-37P2 BNU                  | Combined IEEE<br>1149.1/Auxiliary Out<br>Configuration                           |

| B2                               | 40                | 104549-6                                   | B2R                              | 37                | MR7580-37P2 BNU                  | Auxiliary Port Option<br>Typical Reduced-Port<br>MPC56x Configuration            |

| C1                               | 50                | 104549-7                                   | C1R                              | 51                | MR7580-51P2 BNU                  | Combined IEEE 1149.1<br>and Auxiliary Configuration                              |

| C2                               | 50                | 104549-7                                   | C2R                              | 51                | MR7580-51P2 BNU                  | Auxiliary Port Option<br>Recommended MPC56x<br>Configuration (Full-Port<br>Mode) |

| D <sup>2</sup>                   | TBD               | TBD                                        | TBD                              | TBD               | —                                | Maximum Nexus Port<br>Configuration with Port<br>Replacement <sup>3</sup>        |

| Table <sup>•</sup> | 1 Ne   | SIIX  | Connector | Ontions |

|--------------------|--------|-------|-----------|---------|

| Table              | 1. 140 | , Aus | Connector | options |

<sup>1</sup> The connector option is determined by the combination of the connector and port. For example, connector A1 is the connector A, combined JTAG/Auxiliary Out non-robust option. The robust option is A1R.

$^{2}$  To be determined; connector D pin definitions have not been defined at this time.

<sup>3</sup> Port replacement is not supported on the MPC56x family of devices.

The non-robust connectors are used in evaluation boards and other systems that are not exposed to extreme environments. These are common, low-cost, 2-row connectors that are available from several manufacturers. The AMP System 50 part numbers are listed in Table 1.

## 1.2 Robust Connectors

The lowest pin-count robust connector is a 25-pin Nexus connector A. The high-end robust Nexus connector D has 100 pins. The Nexus connector B has 37 pins, and the Nexus connector C has 51 pins. These connectors are further described in Table 1.

The robust connectors are designed to be used in harsh environments such as under the hood of an automobile. The robust connectors listed in Table 1 are manufactured by Glenair and feature TwistPin connections for highly reliable contact under all conditions in a Micro-D configuration. Figure 1 is an illustration of a typical sub-D configuration and a close-up of the TwistPin.

Figure 1. Details of the Glenair Micro-D TwistPin Connectors (See Section 6, "References" for more details.)

## 2 MPC56x Nexus Connector Options

The MPC56x devices support four of the Nexus connectors: connector B option 2 (B2), connector B option 2 robust (B2R), connector C option 2 (C2), and connector C option 2 robust (C2R). The recommended interface is the 50-pin full-port (and high-speed) C2 configuration. For extreme environments, use the connector C option 2 robust (C2R) connector.

## 2.1 MPC56x Full-Port Configuration

In its maximum configuration, the MPC56x supports eight message data outputs and two message data inputs. This provides a maximum throughput of debug information to and from the Nexus tool. For specific signals used by the MPC565 and the MPC561/MPC563, see Section 3, "MPC56x Nexus Signals." The full-port mode allows transfers from the microcontroller at up to 56 Mbytes (448 Mbits) per second (56-MHz system clock speed x the 8-bit data output port). Messages into the microcontroller can be transmitted at up to 56 Mbits per second (one-half the 56-MHz system clock x the 2-bit data input port). Table 2 shows the MPC56x signals and the Nexus Auxiliary signals for the 50-pin Nexus auxiliary port connector C2 (non-robust). The non-robust connector is a 2-row, 0.1 mil spacing connection. The pinout for the MPC56x is shown in Table 2.

#### MPC56x MPC56x **Nexus Auxiliary** Pin Pin **Nexus Auxiliary** I/O I/O Signal Signal Number Number Signal Signal UBATT OUT OUT UBATT 1 2 \_\_\_\_ VSTBY2.6 VSTBY OUT 3 4 IN or TOOL 100 OUT TOOL IO1 IN or 5 6 IN or TOOL IO2 OUT OUT IN<sup>2</sup> /RESET<sup>1</sup> 7 HRESET OUT VREF 8 **VDD2.6** FVTI $IN^2$ /EVTI 9 10 GND GND \_\_\_\_ $IN^2$ RSTI /RSTI GND GND 11 12 $IN^2$ MSEI 13 /MSEI 14 GND GND $IN^2$ MDI[0] MDI0 15 16 GND GND \_\_\_\_ $IN^2$ MCKI MCKI 17 18 GND GND \_ MDO[0] MDO0 OUT 19 20 GND GND МСКО MCKO OUT 21 22 GND GND \_\_\_\_ OUT LWP[1] /EVTO 23 24 GND GND MSEO /MSEO0 OUT 25 26 IN or VENDOR 100 LWP[0] OUT OUT MDO[1] MDO1 27 28 GND GND \_\_\_\_ 29 MDO[2] MDO2 OUT 30 \_ GND GND MDO[3] MDO3 OUT 31 GND GND 32 $IN^2$ MDI[1] MDI1 33 34 GND GND \_ /MSEO1 OUT 35 36 GND GND \_ OUT MDO4 37 GND GND MDO[4] 38 \_\_\_ MDO[5] MDO5 OUT 39 40 GND GND \_\_\_\_ OUT MDO[6] MDO6 41 42 \_\_\_\_ GND GND MDO7 OUT 43 44 GND GND MDO[7] \_\_\_3 $IN^2$ MDI2 45 46 GND GND \_\_\_\_ \_\_\_3 $IN^2$ MDI3 47 GND 48 GND EPEE & B0EPEE<sup>4</sup> VENDOR IO1 IN or 49 50 GND GND OUT

| Table 2. | MPC56x | Nexus  | 50-Pin          | Definition | (Full-Port M | ode) |

|----------|--------|--------|-----------------|------------|--------------|------|

|          |        | HUCKUS | <b>00</b> I III | Dennaon    |              | ouc, |

<sup>1</sup> The Nexus specification labels active low signals with a forward slash (/) before the signal name.

<sup>2</sup> The Nexus standard recommends that inputs should have 10K  $\Omega$  pull-up resistors to VREF (2.6 volts). Exception: The RSTI input should have a 10K  $\Omega$  pull-down resistor. This is in line with the proposed new standard.

<sup>3</sup> These optional signals are not used in reduced port configuration on the MPC56x devices.

<sup>4</sup> This signal is needed only if control of EPEE or B0EPEE is required by the Nexus tool.

For the MPC56x devices, the robust connector is a 3-row, sub-D type connector. Table 3 shows the signal names for the Nexus Auxiliary Port connector C2R (51-pin).

|            | 19                | 1<br>UBATT    |

|------------|-------------------|---------------|

| 36         | MDO0              | 2             |

| GND        | 20                | UBATT         |

| 37         | GND               | 3             |

| MDO4       | 21                | VSTBY         |

| 38         | 22                | 4             |

| GND        | CND               | TOOL_IO0      |

| 39<br>MDO5 | GND<br>23<br>EVTO | 5<br>TOOL_IO1 |

| 40         | 24                | 6             |

| GND        | GND               | TOOL_IO2      |

| 41         | 25                | 7             |

| MDO6       | MSEO0             | RESET         |

| 42         | 26                | 8             |

| GND        | VEN 100           | VREF          |

| 43         | 27                | 9             |

| MDO7       | MDO1              | EVTI          |

| 44         | 28                | 10            |

| GND        | GND               | GND           |

| 45         | 29                | 11            |

| MDI2       | MDO2              | RSTI          |

| 46         | 30                | 12            |

| GND        | GND               | GND           |

| 47         | 31                | 13            |

| MDI3       | MDO3              | MSEI          |

| 48         | 32                | 14            |

| GND        | GND               | GND           |

| 49         | 33                | 15            |

| VEN_IO1    | MDI1              | MDI0          |

| 50         | 34                | 16            |

| GND        | GND               | GND           |

| 51         | 35                | 17            |

| PORT0      | MSEO1             | MCKI          |

|            |                   | 18<br>GND     |

|            |                   |               |

Table 3. MPC56x Nexus 51-Pin Robust Connector

## 2.2 MPC56x Minimum Configuration

In the reduced-port configuration, the MPC56x supports two message data outputs and one message data input. See Table 4 and Section 3, "MPC56x Nexus Signals," for the mapping of these signals to the MPC565 and the MPC561/MPC563. In the reduced-port configuration, data can be transmitted out of the MPC56x at 112 Mbits per second (14 Mbytes per second) at a 56-MHz system clock. Data from the Nexus tool to the

MPC56x can be transmitted at up to 26 Mbits per second (at a 56-MHz system clock). Table 4 shows the MPC56x signals mapped into the Nexus Auxiliary Port B2. In addition, for the reduced port mode, the 50-pin connector (see Table 2) can be used if the extra signals (MDI[1] and MDO[2:7]) are ignored.

### NOTE

This 40-pin option has a different pinout than the 40-pin connector used on early Freescale/Axiom Manufacturing MPC565 and MPC561/MPC563 Evaluation Boards. See Appendix A, "MPC56x Initial EVB Nexus Connectors."

| MPC56x<br>Signal | Nexus Auxiliary<br>Signal | I/O             | Pin<br>Number | Pin<br>Number | I/O                       | Nexus Auxiliary<br>Signal | MPC56x<br>Signal |

|------------------|---------------------------|-----------------|---------------|---------------|---------------------------|---------------------------|------------------|

|                  | UBATT                     | OUT             | 1             | 2             | OUT                       | UBATT                     |                  |

| VSTBY2.6         | VSTBY                     | OUT             | 3             | 4             | IN or<br>OUT              | TOOL_IO0                  | 2                |

| 2                | TOOL_IO1                  | IN or<br>OUT    | 5             | 6             | IN or<br>OUT              | TOOL_IO2                  | 2                |

| HRESET           | /RESET                    | IN <sup>1</sup> | 7             | 8             |                           | VREF                      | VCC2.6           |

| EVTI             | /EVTI                     | IN <sup>1</sup> | 9             | 10            |                           | GND                       | GND              |

| RSTI             | /RSTI                     | IN <sup>1</sup> | 11            | 12            |                           | GND                       | GND              |

| MSEI             | /MSEI                     | IN <sup>1</sup> | 13            | 14            |                           | GND                       | GND              |

| MDI[0]           | MDI0                      | IN <sup>1</sup> | 15            | 16            | -                         | GND                       | GND              |

| MCKI             | MCKI                      | IN <sup>1</sup> | 17            | 18            |                           | GND                       | GND              |

| MDO[0]           | MDO0                      | OUT             | 19            | 20            | _                         | GND                       | GND              |

| МСКО             | МСКО                      | OUT             | 21            | 22            | IN <sup>1</sup> or<br>OUT | GND                       | GND              |

| LWP[1]           | /EVTO                     | OUT             | 23            | 24            |                           | GND                       | GND              |

| MSEO             | /MSEO0                    | OUT             | 25            | 26            |                           | VENDOR_IO0                | LWP[0]           |

| MDO[1]           | MDO1                      | OUT             | 27            | 28            |                           | GND                       | GND              |

| 2                | MDO2                      | OUT             | 29            | 30            | —                         | GND                       | GND              |

| 2                | MDO3                      | OUT             | 31            | 32            | _                         | GND                       | GND              |

| 2                | MDI1                      | IN <sup>1</sup> | 33            | 34            | _                         | GND                       | GND              |

| 2                | /MSEO1                    | OUT             | 35            | 36            | _                         | GND                       | GND              |

| 2                | MDO4                      | OUT             | 37            | 38            | _                         | GND                       | GND              |

| 2                | MDO5                      | OUT             | 39            | 40            | —                         | GND                       | GND              |

| Table 4. | MPC56x | Nexus | 40-Pin | Definition | (Reduced-Port | Mode) |

|----------|--------|-------|--------|------------|---------------|-------|

|          |        |       |        |            | (             |       |

<sup>1</sup> The Nexus standard recommends that inputs should have 10K  $\Omega$  pull-up resistors to VREF (2.6 volts). Exception: the RSTI input should have a 10K  $\Omega$  pull-down resistor. This is in line with the proposed new standard.

<sup>2</sup> These optional signals are not used in reduced port configuration on the MPC56x devices.

## 3 MPC56x Nexus Signals

On the MPC56x devices, some of the Nexus signals are shared with other pin functions. The shared functions of the MPC565 are different from the MPC561/MPC563. Table 5 shows the Nexus signal versus the MPC565 and MPC561/MPC563 pins. See Table 6 for signal descriptions.

| N            | exus Signal | MPC                    | 565  | MPC561/MF                                  | PC563 |

|--------------|-------------|------------------------|------|--------------------------------------------|-------|

| IN           | exus Signai | Signal                 | Ball | Signal                                     | Ball  |

|              | /RESET      | HRESET                 | AB23 | HRESET                                     | W23   |

|              | /RSTI       | RSTI                   | M3   | JCOMP/RSTI                                 | L1    |

|              | MCKI        | MCKI                   | L4   | TCK/DSCK/MCKI                              | L2    |

|              | /MSEI       | MSEI                   | M4   | VF[2]/MPIO32B[2]/<br>MSEI                  | M24   |

| Aux In Port  | MDI0        | MDI[0]                 | L1   | TDI/DSDI/MDI0                              | M1    |

| ıx In        | MDI1        | MDI[1]                 | L3   | MPWM0/MDI1                                 | F26   |

| AL           | MDI2        | 1                      | _    | _1                                         | —     |

|              | MDI3        | _1                     | _    | _1                                         | —     |

|              | /EVTI       | EVTI                   | M2   | TMS/EVTI                                   | M2    |

|              | МСКО        | МСКО                   | P3   | VF[1]/MPIO32B[1]/<br>MCKO                  | L24   |

|              | /MSEO       | MSEO                   | T2   | VFLS[0]/MPIOB32[3]/<br>MSEO                | M25   |

|              | MDO0        | MDO[0]                 | P4   | TDO/DSDO/MDO[0]                            | M4    |

|              | MDO1        | MDO[1]                 | R1   | VF[0]/MPIO32B[0]/<br>MDO[1]                | L23   |

| ort          | MDO2        | MDO[2]                 | R3   | MPWM[1]/MDO[2]                             | G23   |

| out P        | MDO3        | MDO[3]                 | T1   | MPWM[17]/MDO[3]                            | H23   |

| Aux Out Port | MDO4        | MDO[4]/<br>MPIO32B[10] | N2   | IRQ[0]/SGPIO[0]/<br>MDO[4]                 | P3    |

|              | MDO5        | MDO[5]/<br>MPIO32B[9]  | N4   | MPIO32B[5]/MDO[5]                          | H26   |

|              | MDO6        | MDO[6]/<br>MPIO32B[8]  | N3   | MPIO32B[6]/<br>MPWM[4]/MDO[6] <sup>2</sup> | J23   |

|              | MDO7        | MDO[7]/<br>MPIO32B[7]  | P1   | MPWM[19]/MDO[7]                            | H25   |

|              | /EVTO       | BG/VF[0]/LWP[1]        | AF14 | BG/VF[0]/LWP[1]                            | R3    |

| Port         | PORT0       | 1                      | _    | 1                                          | —     |

### Table 5. MPC56x Signal Sharing

MPC56x Minimum Configuration

|                | exus Signal | MP                          | C565        | MPC561/MPC563               |                       |  |

|----------------|-------------|-----------------------------|-------------|-----------------------------|-----------------------|--|

|                | exus Signai | Signal                      | Ball        | Signal                      | Ball                  |  |

| efined         | VENDOR_IO0  | SGPIOC[7]/<br>IRQOUT/LWP[0] | AC14        | SGPIOC[7]/IRQOUT/<br>LWP[0] | R1                    |  |

| Vendor Defined | VENDOR_IO1  | EPEE & B0EPEE <sup>3</sup>  | AF21 & AD20 | EPEE & B0EPEE <sup>3</sup>  | T23 & T24             |  |

| ned            | TOOL_IO0    | 4                           | _           | —                           | _                     |  |

| Defined        | TOOL_IO1    | 4                           | —           | _                           | _                     |  |

| Tool           | TOOL_IO2    | 4                           | —           | _                           | —                     |  |

|                | VREF        | VDD2.6                      | VDD         | VDD2.6                      | VDD                   |  |

|                | VALTREF     | VSTBY2.6                    | 5           | VSTBY                       | VSTBY2.6 <sup>6</sup> |  |

### Table 5. MPC56x Signal Sharing (continued)

<sup>1</sup> This optional signal is not available on the MPC56x devices.

<sup>2</sup> Pin MPWM[18]/MDO[6] (H24) could also be used, but is not enabled at reset and must be enabled via software. Using the MPWM[18]/MDO[6] for the MDO6 function is not recommended and is not supported by tool vendors.

<sup>3</sup> This signal is needed only if control of EPEE or B0EPEE is required by the Nexus tool.

<sup>4</sup> This optional signal is defined for use by tool vendors and has no defined connection to the MPC56x device.

<sup>5</sup> This signal depends on the following system requirements: KAPWR (Y26), VDDSRAM1 (E3), VDDSRAM2 (D2), or VDDSRAM3 (G4). This pin should be connected to the standby supply used in a particular system.

<sup>6</sup> This should be a 2.6-volt supply and not the IRAMSTBY current source.

#### Table 6. MPC56x Nexus Signal Description

| Sig              | Inal Name                         | Nexus Signal Name & Description                                                                                                                                                                                                                                                 |

|------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPC565           | MPC561/MPC563                     |                                                                                                                                                                                                                                                                                 |

| HRESET           | HRESET                            | Nexus reset (/RESET). Resets the MPC56x microcontroller.                                                                                                                                                                                                                        |

| EVTI             | TMS/EVTI                          | <b>Nexus event in</b> (/EVTI). Level sensitive when configured for breakpoint generation.                                                                                                                                                                                       |

| RSTI             | JCOMP/RSTI                        | <b>Nexus reset input</b> (/RSTI). Resets the READI port<br>and is used to reconfigure the Nexus port. /RSTI<br>should be pulled down by a 10K $\Omega$ resistor (for normal<br>applications) to hold an unused Nexus port in reset<br>and driven high to enable the Nexus port. |

| MSEI             | VF[2]/MPIO32B[2]/MSEI             | <b>Message start/end input</b> (/MSEI). Indicates when a message has started on the MDI pins. /MSEI signals both the end of a packet within a message as well as the end of the message.                                                                                        |

| MCKI             | TCK/DSCK/MCKI <sup>1</sup>        | <b>Message clock input</b> (MCKI). Should be one-half of the system clock frequency and synchronous to the MCKO.                                                                                                                                                                |

| MDI[0]<br>MDI[1] | TDI/DSDI/MDI[0]<br>MPWM[0]/MDI[1] | <b>Message data input</b> (MDI). Provide data input. In the reduced-port configuration, only the MDI[0] signal is used.                                                                                                                                                         |

| Sign                                                                  | al Name                                                                                      | Norma Circal Nama & Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPC565                                                                | MPC561/MPC563                                                                                | Nexus Signal Name & Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BG/VF[0]/LWP[1]                                                       | BG/VF[0]/LWP[1]                                                                              | <b>Nexus event out</b> (/EVTO). Indicates that the processor has halted in response to an /EVTI signal. On the MPC56x, /EVTO can be connected to the MPC56x RCPU L-Bus Watchpoint signal 1 to indicate when the RCPU has reached an L-bus Watchpoint.                                                                                                                                                                                                                                        |

| MSEO                                                                  | VFLS[0]/MPIO32B[1]/MSEO                                                                      | <b>Message start/end output</b> (/MSEO). Indicates when<br>an MDO signal has started and when an MDO packet<br>has ended.                                                                                                                                                                                                                                                                                                                                                                    |

| МСКО                                                                  | VF[1]/MPIO32B[1]/MCKO                                                                        | <b>Nexus message clock output</b> (MCKO). Provides timing for the MDO and /MSEO signals. The frequency of this clock is the same as the MPC56x operating system frequency.                                                                                                                                                                                                                                                                                                                   |

| MDO[0]<br>MDO[1]<br>MDO[2]<br>MDO[3]                                  | TDO/DSDO/MDO[0]<br>VF[0]/MPIO32B[0]/MDO[1]<br>MPWM[1]/MDO[2]<br>MPWM[17]/MDO[3]              | <b>Message data output signals 0-3</b> (MDO[0:3]). In the reduced-port configuration, only MDO[0:1] are used. The full-port configuration uses MDO[0:7].                                                                                                                                                                                                                                                                                                                                     |

| MDO[4]/MPIO[7]<br>MDO[5]/MPIO[8]<br>MDO[6]/MPIO[9]<br>MDO[7]/MPIO[10] | IRQ[0]/SGPIOC[0]/MDO[4]<br>MPIO32B[5]/MDO[5]<br>MPIO32B[6]/MPWM[4]/MDO[6]<br>MPWM[19]/MDO[7] | <b>Message data output signals 4-7</b> (MDO[4:7]). In the reduced-port configuration, these pins are not used. In full-port configuration, they provide an 8-bit output port to the Nexus tool. On the MPC565, these pins are shared with the MIOS14 General-Purpose Parallel Port. On the MPC561 and MPC563, some are shared with MIOS14 PWM channels and with Interrupt 0. The Nexus pins are automatically selected if the READI module is enabled and configured for the full-port mode. |

| SGPIOC[7]/IRQOUT/LWP[0]                                               | SGPIOC[7]/IRQOUT/LWP[0]                                                                      | <b>Nexus Vendor_IO0</b> (VENDOR_IO0). Used as the MPC56x RCPU L-bus Watchpoint signal 0.                                                                                                                                                                                                                                                                                                                                                                                                     |

| EPEE & B0EPEE                                                         | EPEE & B0EPEE                                                                                | <b>Nexus Vendor_IO1</b> (VENDOR_IO1). Enables<br>programming of the MPC56x's internal Flash. This<br>signal can be used to drive EPEE or B0EPEE if control<br>of the internal Flash is desired by the Nexus tool.<br>EPEE is the internal Flash enable and B0EPEE is the<br>block 0 Flash erase enable. It allows the tool to enable<br>(or disable) internal Flash programming.                                                                                                             |

| VDD2.6                                                                | VDD2.6                                                                                       | <b>Nexus VREF</b> (VREF). Provides a reference for the signal levels of the Nexus device. All input high and low voltages should be referenced to this pin. The Nexus specification defines the input voltages as VIL = $0.3xVREF$ and VIH = $0.7xVREF$ . For the MPC56x, this pin should be approximately 2.6 volts. (All signals in and out of the MPC56x are 2.6 volt signals.)                                                                                                           |

### Table 6. MPC56x Nexus Signal Description (continued)

Enabling the MPC56x READI Port

| Sig      | nal Name      | Nexus Signal Name & Description                                                                                                                                                                                                           |  |  |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MPC565   | MPC561/MPC563 |                                                                                                                                                                                                                                           |  |  |

| VSTBY2.6 | VSTBY2.6      | <b>Nexus VALTREF</b> (VALTREF). Provides a backup<br>power supply for the MPC56x's SRAM. This pin is<br>monitored by the Nexus tool to determine if power is<br>lost to the standby supply of the system.                                 |  |  |

| GND      | GND           | <b>Ground</b> . Ground reference point for the Nexus connectors. Many ground signals are included to provide shielding for the high-speed Nexus signals.                                                                                  |  |  |

| _        | _             | <b>Tool_IO pins</b> (TOOL_IO[1:3]). Designated for Nexus tool use. At this time, there are no defined connections from these pins to the MPC56x device. They may be used for communication between multiple tools on the Nexus connector. |  |  |

| UBATT    | UBATT         | <b>Battery/unregulated module voltage</b> . This voltage (nominally 12 volts) should be made available to power external circuitry needed for extending the Nexus connection to the tool. It should have reverse-bias protection.         |  |  |

Care should be taken in routing the TCK/DSCK/MCKI signal if it is used for more than the MCKI function (i.e. if the DSCK or TCK signals are optionally used for BDM or JTAG boundary scan). Proper termination may be needed to eliminate board reflections. The Nexus connector should be physically mounted near the MPC561/MPC563 to reduce the trace length.

# 4 MPC56x READI Port Configuration

## 4.1 Enabling the MPC56x READI Port

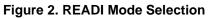

The READI port on the MPC565 is enabled on the rising edge of RSTI only if EVTI is asserted (driven low). The same sequence is needed on the MPC561 and the MPC563, but the MPC561 and MPC563 can only be enabled after PORESET has been negated. In order to trace out of reset, the HRESET should be asserted by the tool until the READI port has been enabled and configured.

| PORESET                 |               |                |               |   |

|-------------------------|---------------|----------------|---------------|---|

| HRESET                  |               |                | /             |   |

| JCOMP/RSTI              |               | <br>           |               |   |

| TMS/EVTI                | JTAG Disabled | READI-Config   | READI Enabled |   |

| Configuration (MDIO[0]) |               | READI-Config / | READI         |   |

| -                       |               |                |               | T |

Nexus Interface Connector Options for MPC56x Devices

1

### Table 6. MPC56x Nexus Signal Description (continued)

The selection of reduced-port configuration or full-port configuration is determined by the state of MDI[0] upon the negation of  $\overline{RSTI}$ . Note that  $\overline{EVTI}$  and MDI[0] must be valid for at least 4 clocks prior to the rising edge of  $\overline{RSTI}$ .  $\overline{RSTI}$  has an internal pull-down resistor that must be overcome to enable the READI Nexus module.

| EVTI | MDI[0] | Configuration                                                         |

|------|--------|-----------------------------------------------------------------------|

| 1    | х      | READI module disabled. All outputs are tri-stated                     |

| 0    | 1      | READI module enabled. Default Port<br>Configuration —2 MDI and 8 MDO. |

| 0    | 0      | READI module enabled. Reduced-Port Configuration—1 MDI and 2 MDO.     |

## 5 Special Considerations for the MPC561/MPC563

The MPC561 and MPC563 have special board considerations due to the configuration of the internal pull resisters. The IEEE-ISTO 5001-1999 Nexus standard specifies that inputs should have 10K  $\Omega$  pull ups. The intent of this specification is to insure that inputs are not floating when no tool is connected. Many of the MPC561 and MPC563 inputs signals have internal weak pull down devices or have pull devices controlled by the PULL\_SEL pin that can be configured as pull up or pull down devices. In general, these weak devices should be augmented with an external resistor to insure the state of the pin, since the pull downs can be disabled with software.

Table 8. MPC561 and MPC563 Input Pull Devices

| Signal Name           | Pull Device                                               |  |  |  |

|-----------------------|-----------------------------------------------------------|--|--|--|

| TMS/EVTI              | Pull Down until SPRDS is set if Nexus is enabled          |  |  |  |

| JCOMP/RSTI            | Pull Down until SPRDS is set                              |  |  |  |

| VF[2]/MPIO32B[2]/MSEI | Pull Device enabled until PULL_DIS[0] is set <sup>1</sup> |  |  |  |

| TCK/DSCK/MCKI         | Pull Down until reset negates                             |  |  |  |

| TDI/DSDI/MDI[0]       | Pull Down until reset negates                             |  |  |  |

| MPWM[0]/MDI[1]        | Pull Device enabled until PULL_DIS[0] is set <sup>1</sup> |  |  |  |

| EPEE & B0EPEE         | Pull Up to 2.6 volts (always enabled)                     |  |  |  |

| HRESET                | Boards should always have an external pull up resistor    |  |  |  |

<sup>1</sup> External pull resistor should be in the same direction as the setting of the PULL\_SEL signal (pin).

To minimize currents, pins with internal pull down devices should have external pull downs. It is recommended that a 10K  $\Omega$  pull down be used on boards.

### 6 References

Photos in Figure 1 copyright Glenair, Inc.

Glenair, Inc. 1211 Air Way Glendale, CA 91201-2497 Phone: 818-247-6000 Fax: 818-500-9912 <http://www.glenair.com/>

### AMP

Tyco Electronics <http://www.amp.com> U.S. Only 800-522-6752 8:00am-8:00pm EST

Axiom Manufacturing, Inc. 2813 Industrial Ln. Garland, TX 75041 Phone: 972-926-9303 Fax: 972-926-6063 <http://www.axman.com>

## Appendix A MPC56x Initial EVB Nexus Connectors

Early versions of the MPC56x evaluation boards included a 40-pin connector. This connector is not compatible with connector B of the revised Nexus connectors. The following pinout information is provided for reference ONLY and should NOT be used for new designs.

# A.1 MPC56x Full-Port Configuration

The MPC56x supports eight message data outputs and two message data inputs. This provides a maximum throughput of debug information to and from the Nexus tool (see Table 2). In the full-port configuration, transfers from the microcontroller can be up to 56 Mbytes (448 Mbits) per second (56-MHz system clock speed x the 8-bit data output port). Messages into the microcontroller can be transmitted at up to 56 Mbits per second (one-half the 56-MHz system clock x the 2-bit data input port).

| MPC565<br>Ball | MPC565<br>Signal    | Nexus<br>Auxiliary<br>Signal | I/O             | Pin<br>Number | Pin<br>Number | I/O                       | Nexus<br>Auxiliary<br>Signal | MPC565<br>Signal              | MPC565<br>Ball |

|----------------|---------------------|------------------------------|-----------------|---------------|---------------|---------------------------|------------------------------|-------------------------------|----------------|

| AB23           | HRESET              | /RESET                       | IN <sup>1</sup> | 1             | 2             | _                         | VREF                         | VCC2.6                        | VDD            |

| M2             | EVTI                | /EVTI                        | IN <sup>1</sup> | 3             | 4             | —                         | VALTREF                      | VSTBY2.6                      | <sup>2</sup>   |

| M3             | RSTI                | /RSTI                        | IN <sup>1</sup> | 5             | 6             | IN or<br>OUT              | VENDOR_IO1                   | SGPIOC[7]/<br>IRQOUT/<br>LWP0 | AC14           |

| M4             | MSEI                | /MSEI                        | IN <sup>1</sup> | 7             | 8             | _                         | GND                          | GND                           | —              |

| L4             | MCKI                | MCKI                         | IN <sup>1</sup> | 9             | 10            |                           | GND                          | GND                           | —              |

| L1             | MDI[0]              | MDI0                         | IN <sup>1</sup> | 11            | 12            | —                         | GND                          | GND                           | —              |

| —              | —                   | Reserved                     | OUT             | 13            | 14            | —                         | GND                          | GND                           | —              |

| —              | _                   | Reserved                     | OUT             | 15            | 16            | IN <sup>1</sup> or<br>OUT | VENDOR_IO2                   | EPEE &<br>B0EPEE              | AF21 &<br>AD20 |

| AF14           | BG/VF[0]/<br>LWP[1] | /EVTO                        | OUT             | 17            | 18            | —                         | GND                          | GND                           | —              |

| T2             | MSEO                | /MSEO                        | OUT             | 19            | 20            | —                         | GND                          | GND                           | —              |

| P3             | МСКО                | МСКО                         | OUT             | 21            | 22            | —                         | GND                          | GND                           | —              |

| P4             | MDO[0]              | MDO0                         | OUT             | 23            | 24            | —                         | GND                          | GND                           | —              |

| R1             | MDO[1]              | MDO1                         | OUT             | 25            | 26            | —                         | GND                          | GND                           | —              |

| R3             | MDO[2]              | MDO2                         | OUT             | 27            | 28            | —                         | GND                          | GND                           | —              |

| T1             | MDO[3]              | MDO3                         | OUT             | 29            | 30            | —                         | GND                          | GND                           | —              |

| N2             | MDO[4]/<br>MPIO[10] | MDO4                         | OUT             | 31            | 32            | —                         | GND                          | GND                           | —              |

| N4             | MDO[5]/<br>MPIO[9]  | MDO5                         | OUT             | 33            | 34            | —                         | GND                          | GND                           | —              |

| N3             | MDO[6]/<br>MPIO[8]  | MDO6                         | OUT             | 35            | 36            | —                         | GND                          | GND                           | —              |

| P1             | MDO[7]/<br>MPIO[7]  | MDO7                         | OUT             | 37            | 38            | —                         | GND                          | GND                           | —              |

| L3             | MDI[1]              | MDI1                         | IN <sup>1</sup> | 39            | 40            | —                         | GND                          | GND                           | —              |

<sup>1</sup> The Nexus standard recommends that all inputs should have 10K  $\Omega$  pull-up resistors to VREF (2.6 volts). Exception: The RSTI input should have a 10K  $\Omega$  pull-down resistor. This is in line with the proposed new standard.

<sup>2</sup> These signals depend on system requirements: KAPWR (Y26), VDDSRAM1 (E3), VDDSRAM2 (D2), VDDSRAM3 (G4).

| MPC561/<br>MPC563<br>Ball | MPC561/<br>MPC563<br>Signal     | Nexus<br>Auxiliary<br>Signal | I/O             | Pin<br>Number | Pin<br>Number | I/O                       | Nexus<br>Auxiliary<br>Signal | MPC561/M<br>PC563<br>Signal            | MPC561/<br>MPC563<br>Ball |

|---------------------------|---------------------------------|------------------------------|-----------------|---------------|---------------|---------------------------|------------------------------|----------------------------------------|---------------------------|

| W23                       | HRESET                          | /RESET                       | IN <sup>1</sup> | 1             | 2             | —                         | VREF                         | VCC2.6                                 | VDD                       |

| M2                        | TMS/EVTI                        | /EVTI                        | IN <sup>2</sup> | 3             | 4             | _                         | VALTREF                      | VSTBY2.6                               | _2                        |

| L1                        | JCOMP/RSTI                      | /RSTI                        | IN <sup>1</sup> | 5             | 6             | IN or<br>OUT              | VENDOR_IO1                   | S <u>GPIOC[7]</u><br>/ IRQOUT/<br>LWP0 | R1                        |

| M24                       | VF[2]/<br>MPIO32B[2]/<br>MSEI   | /MSEI                        | IN <sup>2</sup> | 7             | 8             |                           | GND                          | GND                                    | —                         |

| L2                        | TCK/DSCK/<br>MCKI               | MCKI                         | IN <sup>2</sup> | 9             | 10            | —                         | GND                          | GND                                    | —                         |

| M1                        | TDI/DSDI/<br>MDI[0]             | MDI0                         | IN <sup>2</sup> | 11            | 12            | —                         | GND                          | GND                                    | —                         |

|                           | —                               | Reserved                     | OUT             | 13            | 14            | _                         | GND                          | GND                                    | —                         |

| _                         | —                               | Reserved                     | OUT             | 15            | 16            | IN <sup>2</sup> or<br>OUT | VENDOR_IO2                   | EPEE &<br>B0EPEE                       | T23 &<br>T24              |

| R3                        | BG/VF[0]/<br>LWP[1]             | /EVTO                        | OUT             | 17            | 18            | —                         | GND                          | GND                                    | —                         |

| M25                       | VFLS[0]/<br>MPIO32B[3]/<br>MSEO | /MSEO                        | OUT             | 19            | 20            |                           | GND                          | GND                                    | —                         |

| L24                       | VF[1]/<br>MPIO32B[1]/<br>MCKO   | МСКО                         | OUT             | 21            | 22            |                           | GND                          | GND                                    | —                         |

| M4                        | TDO/DSDO/<br>MDO[0]             | MDO0                         | OUT             | 23            | 24            | —                         | GND                          | GND                                    | —                         |

| L23                       | VF[0]/<br>MPIO32B[0]/<br>MDO[1] | MDO1                         | OUT             | 25            | 26            | _                         | GND                          | GND                                    | —                         |

| G23                       | MPWM[1]/<br>MDO[2]              | MDO2                         | OUT             | 27            | 28            | —                         | GND                          | GND                                    | —                         |

| H23                       | MPWM[17]/<br>MDO[3]             | MDO3                         | OUT             | 29            | 30            | —                         | GND                          | GND                                    | —                         |

| P3                        | IRQ[0]/<br>SGPIOC0/<br>MDO[4]   | MDO4                         | OUT             | 31            | 32            |                           | GND                          | GND                                    | —                         |

### Table A-2. MPC561/MPC563 Nexus 40-Pin Definition (Full-Port Mode)

| MPC561/<br>MPC563<br>Ball | MPC561/<br>MPC563<br>Signal       | Nexus<br>Auxiliary<br>Signal | I/O             | Pin<br>Number | Pin<br>Number | I/O | Nexus<br>Auxiliary<br>Signal | MPC561/M<br>PC563<br>Signal | MPC561/<br>MPC563<br>Ball |

|---------------------------|-----------------------------------|------------------------------|-----------------|---------------|---------------|-----|------------------------------|-----------------------------|---------------------------|

| H26                       | MPIOB32[5]/<br>MDO[5]             | MDO5                         | OUT             | 33            | 34            |     | GND                          | GND                         | —                         |

| J23                       | MPIO32B[6]/<br>MPWM[4]/<br>MDO[6] | MDO6                         | OUT             | 35            | 36            | -   | GND                          | GND                         | —                         |

| H25                       | MPWM[19]/<br>MDO[7]               | MDO7                         | OUT             | 37            | 38            | -   | GND                          | GND                         | —                         |

| F26                       | MPWM[0]/<br>MDI[1]                | MDI1                         | IN <sup>2</sup> | 39            | 40            | 1   | GND                          | GND                         | —                         |

#### Table A-2. MPC561/MPC563 Nexus 40-Pin Definition (Full-Port Mode) (continued)

<sup>1</sup> The Nexus standard recommends that all inputs should have 10K  $\Omega$  pull-up resistors to VREF (2.6 volts). Exception: the RSTI input should have a 10K  $\Omega$  pull-down resistor. This is in line with the proposed new standard.

<sup>2</sup> These signals depend on system requirements: KAPWR (Y26), VDDSRAM1 (E3), VDDSRAM2 (D2), VDDSRAM3 (G4).

#### NOTE

Adapters that connect the 40-pin to the 50-pin connectors, and the 51-pin connectors to the 40-pin or 50-pin connectors, are available from Axiom Manufacturing (http://www.axman.com). See Table A-3.

Table A-3. Adapters Available from Axiom Manufacturing

| Cable Connector<br>(Socket) | Board Connector<br>(Plug) | Axiom Part Number |

|-----------------------------|---------------------------|-------------------|

| 40-pin AMP                  | 50-pin                    | Nexus 4050        |

| 50-pin AMP                  | 40-pin                    | Nexus 5040        |

| 51-pin Robust               | 50-pin                    | Nexus 5150        |

| 51-pin Robust               | 40-pin                    | Nexus 5140        |

| 40-pin AMP                  | 51-pin Robust             | Nexus 4051        |

| 50-pin AMP                  | 51-pin Robust             | Nexus 5051        |

### 7 Revision History

Table 9 provides a revision history for this application note.

**Table 9. Document Revision History**

| Revision Number | Substantive Changes                                                 | Release Date  |  |  |

|-----------------|---------------------------------------------------------------------|---------------|--|--|

| 0               | Initial release.                                                    | December 2002 |  |  |

| 0.1             | Table 1: Corrected part numbers for<br>connector options C1 and C2. | February 2003 |  |  |

THIS PAGE INTENTIONALLY LEFT BLANK

THIS PAGE INTENTIONALLY LEFT BLANK

THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

AN2298/D

For More Information On This Product, Go to: www.freescale.com