# MPC860 and MC68302 Asynchronous Interface

The main point of this document is to show the flexibility of an asynchronous interface between an MPC860 and an MC68302. Wait states and or the external bus speed of the MPC860 can be adjusted to allow for interfacing the MPC860 and MC68302 at different bus speeds. For the purpose of this document, the following parameters are assumed:

- Interface is between a 40MHz MPC860 and a 20MHz MC68302.

- The MC68302 external master internal asynchronous read write timing is used (Please see Figures 6-17 and 6-18 of the *MC68302 User's Manual*).

- Transaction between the two chips is unidirectional. The MPC860 is the master and the 302 is the slave.

- MC68302 is a 16 bit port size that is defined as part of the upper data bus.

- MC68302 stores its serial data in its dual port RAM. It is not a bus master.

- The MPC860 user programmable machine (UPM) is programmed to generate the proper timing of the signals.

- General purpose lines available from the MPC860 UPM are not needed. Existing signals can be programmed to behave like signals received by the MC68302.

# Programming the Option, Mode and Base Registers

The option and base registers of the MPC860 must be programmed as follows for this type of interface. Within the option register, bits 24 through 27 must be programmed according to the timing of the MC68302. Within the base register, bits 20 through 21, and bit 23 must be programmed for a 16 bit non-bursting port. The following tables have been appended from section 15 of the MPC860 Manual.

| Bits  | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                    | Function                        |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 20-21 | PS(0:1)  | <b>Port Size.</b><br>This field specifies the port size of the memory region.                                                                                                                                                                                                                                                                  | 10 = 16 bit port size           |

| 24-25 | MS(0:1)  | Machine Select.<br>This field specifies the machine<br>selected for the memory<br>operations handling.                                                                                                                                                                                                                                         | 10 = U.P.M.A or<br>11 = U.P.M.B |

| 31    | V        | Valid Bit.<br>This bit indicates that the contents<br>of the base register and option<br>register pair are valid. The CS<br>signal does not assert until the V<br>bit is set.<br>Note: An access to a region that<br>does not have the V bit set may<br>cause a bus monitor time out.<br>Following a system reset, the V bit<br>is set in BR0. |                                 |

### Table 15-14. Base Register

© Freescale Semiconductor, Inc., 2004. All rights reserved.

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                          | Function                                                                 |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 23   | BI       | Burst Inhibit.<br>This attribute decides whether or<br>not this memory bank supports<br>burst accesses. In a non-burst<br>case, the memory controller<br>drives the BI signal active when<br>accessing this memory region.<br>Following a system reset, the BI<br>bit is set in OR0. | 1= Drive BI asserted. The<br>bank does not<br>support burst<br>accesses. |

# Table 15-15. Option Register

## Table 15-16. Machine A Mode Register

| Bits | Mnemonic | Description                                                                                                                          | Function                            |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 8    | PTAE     | <b>Periodic Timer A Enable</b><br>This bit allows the periodic timer<br>A to request service. Note:<br>Following a system reset, the | 0 = Periodic timer A is<br>disabled |

|      |          | PTAE bit is reset.                                                                                                                   |                                     |

# Programming the Signals for a Successful MPC860 and MC68302 Interface

For this interface, the MPC860 signals are programmed to communicate with the MC68302. With examination of the timing specifications and the number of wait states needed by the MC68302, the MPC860 can communicate successfully.

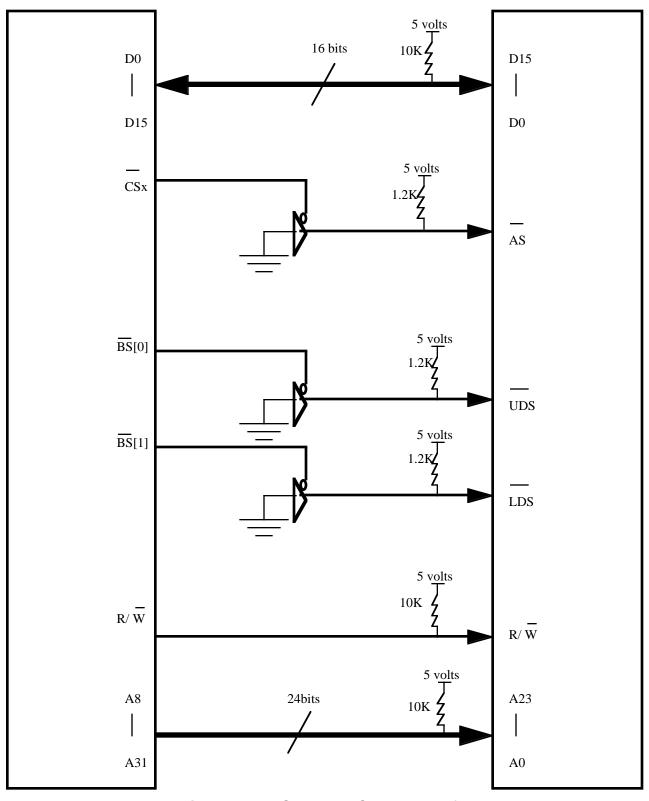

The active low MPC860 chip select signal is programmed to the MC68302 address strobe. The chip select's assertion can be interpreted as a MC68302 address strobe to emulate the MC68302 bus operation. Because you can program chip select like any other MPC860 signal, it makes programming the address strobe simple.

The active low signals BS[0] and BS[1] can be programmed for the upper and lower data strobe signals of the MC68302. These byte select signals are also convenient because they can be programmed using the user programmable machine like any other general purpose signal.

The read/write signal of the MPC860 can directly communicate with the same signal on the MC68302. The timing is not a problem since the read/write signal is asserted directly after the transfer start signal. BS[0] and BS[1] correspond with the byte lanes of the upper half of the data bus.

In Figure 1-1 the interface between the two parts is outlined. There are three three-state buffers. These buffers ensure that more than one device can drive the same line without creating bus contention (for five volt MC68302 parts only). However if a 3.3 volt MC68302 is used, the three-state buffers are not required. It is also important to note that a pull up resistor is connected to each signal keeping the lines high (unasserted) when there is no activity taking place. They should also be sized to meet the MC68302 negation times.

DTACK\* and IAC signals are not used in this interface. DTACK\* will be asserted internally by the MC68302 after a known number of wait states. IAC can be used as a debugging output to tell if the MC68302 is being selected. All that is needed for the

timing of the DTACK\* signal is the cycle length. In order for a 40MHz MPC860 to interface with a MC68302 three wait states must be included in the timing. This will push the number of MPC860 clocks needed to complete the cycle to fourteen (2 x [3 wait states+ 4 clocks] = 14). This interface requires fourteen entries in the UPM RAM. Although only eight entries are available for single read or write operation, the additional burst read and write entries can be used in this application since neither are used. A loop function can also be used to reduce the number entries, but was not included in this application note for clarity. Knowledge of this cycle and the relative bus speeds of the MPC860 and MC68302 enables the user to program the length of the MPC860's read or write cycle appropriately.

The MC68302 SCC's store all data in the internal dual port RAM of the MC68302. This is appropriate for low speed serial channels on the order of 64 kbps or less. It is possible for the MC68302 to obtain bus mastership of the MPC860 bus, but this design is outside of the scope of this document.

A copy of the UPM programming for this interface is available in the MCUinit 860 tool.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail:

support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

MPC860

MC68302