# Software Differences Between the DSP56002 and the DSP56303

By Barbara Johnson

The software differences between the DSP56002 and the DSP56303 must be considered when a system based on the DSP56002 is redesigned to use the DSP56303. This application note describes these software differences in detail. For details on the hardware differences between these two DSP products, refer to the application note AN1830, *Hardware Differences Between the DSP56002 and the DSP56303*, which covers memory, interrupt and mode control, core, and peripherals.

This application note does not describe an application *per se*. Rather it summarizes the differences between two DSP products as a convenient reference for designers/programmers who are migrating to the DSP56303 from the DSP56002. It saves you the time that would be required to determine what these differences are.

#### CONTENTS

| 1   | Introduction                 | 2  |

|-----|------------------------------|----|

| 2   | Instruction Pipeline         | 2  |

| 3   | Instruction Cache Controller |    |

| 3.1 | Software Control             | 4  |

| 3.2 | Instruction Cache Structure  | 4  |

| 3.3 | Burst Mode                   | 4  |

| 3.4 | Cache Visibility Via OnCE    | 4  |

| 4   | Arithmetic Logic Unit        | 4  |

| 5   | Address Generation Unit      |    |

| 6   | Programming Mode             | 16 |

| 7   | Instruction Set              |    |

| 7.1 | Arithmetic Instructions      |    |

| 7.2 | Logical Instructions         | 14 |

| 7.3 | New Loop Instructions        |    |

| 7.4 | Move Instruction             |    |

| 7.5 | Program Control Instructions |    |

|     |                              |    |

# 1 Introduction

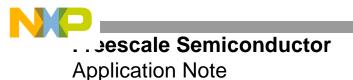

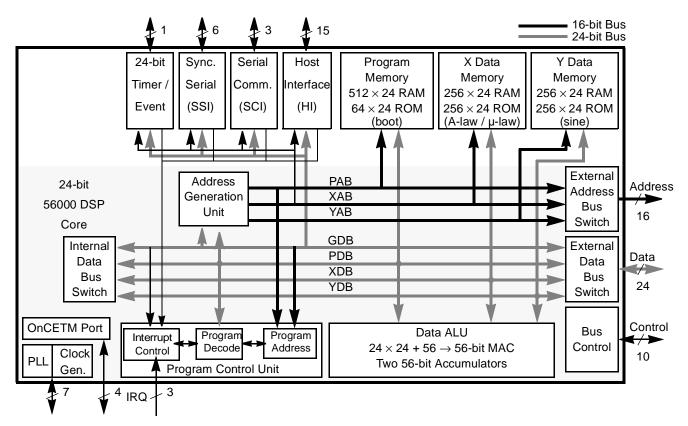

**Figure 1** and **Figure 2** show the block diagrams of the DSP56002 and the DSP56303, respectively, in order to provide a context for the next sections, which compare various features and modules of these two DSP products.

Figure 1. DSP56002 Block Diagram

# 2 Instruction Pipeline

In the DSP56002, the program control unit implements a three-stage instruction execution pipeline:

- 1. prefetch

- 2. decode

- **3.** execute

Each instruction requires a minimum of three instruction cycles to move through this pipeline. There is a delay of three instruction cycles on power-up to fill the pipeline. A new instruction can begin executing immediately after the previous instruction executes. Two-word instructions require a minimum of four instruction cycles to execute—that is, three cycles for the first instruction word to move through the pipeline and execute and one more cycle for the second word to execute. A new instruction can start after two instruction cycles.

Figure 2. DSP56303 Block Diagram

In the DSP56303, the program control unit implements a seven-stage pipeline:

- 1. prefetch-I

- 2. prefetch-II

- **3.** decode

- 4. address generation-I

- 5. address generation-II

- 6. execute-I

- 7. execute-II

Each instruction requires a minimum of seven instruction cycles to move through this pipeline. There is a delay of seven instruction cycles on power-up to fill the pipeline. A new instruction can begin executing immediately after the previous instruction executes. Two-word instructions require a minimum of eight instruction cycles to execute—that is, seven cycles for the first instruction word to move through the pipeline and execute and one more cycle for the second word to execute. A new instruction can start after two instruction cycles.

NP

uction Cache Controller

# 3 Instruction Cache Controller

The instruction cache controller is not available on the DSP56000 core. On the DSP56300 core, the instruction cache stores frequently-used program instructions. When instruction words required by a program are available in the on-chip cache, an increase in throughput may result, and the time required to access them on the external bus is eliminated.

# 3.1 Software Control

On the DSP56300 core, switching between PRAM mode and cache mode is controlled via the Cache Enable CE bit in the Expanded Mode Register (EMR). If EMR[CE] is set, the cache is enabled, instructions are cached into the internal PRAM and fetched from there. If EMR[CE] is cleared, the cache is disabled, and the core fetches instructions from external or internal program memory.

## 3.2 Instruction Cache Structure

The instruction cache memory array contains 1024 x 24-bit words logically divided into eight 128-word cache sectors. The 24-bit address is divided into the following fields:

- vbit field, 7 least significant bits for the word displacement in the sector

- tag field, 17 most significant bits for the sector base address

The cache controller compares its tag field to the tag values currently stored in the tag register file. These tag values are the tag fields of the base addresses of the memory sectors currently mapped into the cache. Each word in each cache sector is associated with a cache word valid bit that specifies whether the data in that word has been fetched from external memory and is therefore valid. There is a total 2048 valid bits arranged as 8 banks of 128 or 256 valid bits each, one bank for every sector. Of these valid bits, 1024 are not used if the instruction cache size is 1024 bytes.

## 3.3 Burst Mode

When the Burst Mode Enable (BE) bit in the Extended Chip Operating Mode Register (EOM) is set, up to four program words are fetched from external memory upon detection of an instruction cache miss. When EOM[BE] is cleared, the burst mode is disabled, and only one program word is fetched from external memory upon detection of an instruction cache miss.

# 3.4 Cache Visibility Via OnCE

When the DSP is in Debug mode, you can observe the memory sectors that are currently mapped into cache, the locked cache sectors, the Least Recently Used cache sector, and the occurrence of a hit. You can also read the valid bits of specific cache locations.

# 4 Arithmetic Logic Unit

Table 1 summarizes the differences in the arithmetic logic unit between the DSP56002 and the DSP56303.

| DSP56002                                                                                                                                                                                                                                                                                        | DSP56303                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MA                                                                                                                                                                                                                                                                                              | C Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| MAC operation is a non-pipelined single-cycle operation.<br>MAC operation is fully pipelined and requires two<br>cycles to complete. In the first clock cycle, the mu<br>performed and the product is stored in the pipelin<br>In the second clock cycle, the accumulator is add<br>subtracted. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit Field                                                                                                                                                                                                                                                                                       | l Unit (BFU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Not Available.                                                                                                                                                                                                                                                                                  | <ul> <li>The BFU contains a 56-bit parallel bidirectional shifter with 56-bit input and a 56-bit output mask generation unit and logic unit. It is used in the following operations:</li> <li>Multiple left/right shift (arithmetic or logical) for ASL/ASR LSL/LSR</li> <li>Bit field merge, insert and extract for MERGE, INSERT, EXTRACT, EXTRACTU, Count leading bits for CLB</li> <li>Fast normalization for NORMF</li> <li>The addition of the BFU on the DSP56300 core has produced new shift and program control-relative instruction (refer to Section 7, "Instruction Set," on page 10).</li> </ul> |  |  |

| Sixteen-Bit /                                                                                                                                                                                                                                                                                   | Arithmetic Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Not Available.                                                                                                                                                                                                                                                                                  | Sixteen-Bit Arithmetic mode is enabled by setting the SA (bi<br>17) in the Status Register (SR). The 16-bit data is right-<br>aligned in 24-bit memory locations and non-Data ALU<br>registers as shown here.<br>Table 4-1.<br>The bit positions in Indenfiembry fong word in Sixteen-Bit<br>Arithmetic mode are as follows:<br>Table 4-2.<br>23:16 15:0 23:16 15:0                                                                                                                                                                                                                                           |  |  |

|                                                                                                                                                                                                                                                                                                 | The 16-bit data is left-aligned in Data ALU input registers as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                                                                                                                                                                                                                                                                                 | aligned in 24-bit memory locations and non-Data ALU registers as shown here.         Table 4-1.         23–16       15–0         The bit positions in Indefiendory fonty word in Sixteen-Bit Arithmetic mode are as follows:         Table 4-2.         23:16       15:0       23:16       15:0         The 16-bit data is left-aligned in Data ALU input register                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                                 | Table 4-4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                 | 55:48 47:32 31:24 23:8 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

## **Table 1.** Arithmetic Logic Unit, Comparison Between DSP56002 and DSP56303

ess Generation Unit

| DSP56002                                 | DSP56303                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Roundi                                   | ng Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Convergent rounding mode is implemented. | Convergent and twos complement rounding are<br>implemented. To select Rounding mode, set the RM bit (bit<br>21) in the SR. If RM is set, twos complement rounding is<br>selected; if RM is cleared, convergent rounding is selected.<br>Convergent rounding rounds down if the number is even<br>(LSB=0) and rounds up if the number is odd (LSB=1). Twos<br>complement rounding rounds down all values below one-half<br>and rounds up all values of one-half or greater. |

| Saturat                                  | ion Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Not Available                            | The arithmetic unit's result is limited to 48 bits by setting the SM (bit 20) in the SR. This bit provides a saturation mode for algorithms that do not recognize or cannot take advantage of the extension accumulator.                                                                                                                                                                                                                                                   |

Table 1.

Arithmetic Logic Unit, Comparison Between DSP56002 and DSP56303 (Continued)

# 5 Address Generation Unit

**Table 2** summarizes the differences in the Address Generation Unit (AGU) between the DSP56002 and the DSP56303.

| DSP56002                                                                                                                                                                                                                                                                                                                                                                                                                     | DSP56303                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AGU Registers                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| The 24 Address Generation Unit (AGU) registers (address registers R0–R7, offset registers N0–N7, and modifier registers M0–M7) are 16 bits wide. When used as a source operand, these registers occupy the low-order portion of the 24-bit word; the high-order portion is read as zeros. When used as a destination operand, these registers receive the low-order portion of the word; the high-order portion is not used. | The 24 AGU registers are 24-bits wide.                                                                                                                                                                                                                                                                         |  |  |  |  |

| Sixteen-Bit Cor                                                                                                                                                                                                                                                                                                                                                                                                              | npatibility Mode                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Not Available                                                                                                                                                                                                                                                                                                                                                                                                                | When the Sixteen-Bit Compatibility Mode bit in the MR is set,<br>move operations to and from the LA, LC, SP, SSL, SSH, EP,<br>SZ, VBA, and SC registers clear the eight most significant<br>bits of the destination. This guarantees compatibility for<br>object code written for the DSP56000 family of DSPs. |  |  |  |  |

Table 2. Address Generation Unit, Comparison of DSP56002 and DSP56303

## 6 Programming Model

This section compares key registers of the DSP56002 and the DSP56303. The registers covered are as follows:

- Status Register (SR), **Table 3** on page 7

- Operating Mode Register (OMR), Table 4 on page 8

- System Stack (SS), Table 5 on page 8

- Program Counter (PC), Table 6 on page 9

- Vector Base Address Register (VBA), Table 7 on page 9

- Loop Counter Register (LC), **Table 8** on page 9

- Loop Address Register (LA), Table 9 on page 9

- Stack Extension Pointer (EP), Table 10 on page 9

- Stack Size Register (SZ), Table 11 on page 9

- Stack Counter Register (SC), Table 12 on page 10

- Stack Pointer Register (SC), **Table 13** on page 10

| Table 3. | Status Register, Comp | parison of the DSP56002 and the DSP56303 |

|----------|-----------------------|------------------------------------------|

|----------|-----------------------|------------------------------------------|

| DSP56002                                                                                                                                                                            |       |            | DSP56303                                                                                                                                                                                  |     |       |             |                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------|-----------------------------------|

| The Status Register (SR) is a 16-bit register that consists of a<br>Mode Register MR in the high-order eight bits and a<br>Condition Code Register CCR in the low-order eight bits. |       |            | The SR is 24-bit register that consists of an Extended Mode<br>Register EMR in the high-order eight bits, an MR in the<br>middle-order eight bits, and a CCR in the low-order eight bits. |     |       |             |                                   |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           | EMR | 23–22 | CP1-<br>CP0 | Core Priority                     |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 21    | RM          | Rounding Mode                     |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 20    | SM          | Arithmetic Saturation Mode        |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 19    | CE          | Instruction Cache Enable          |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 18    | _           | Reserved                          |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 17    | SA          | Sixteen-Bit Arithmetic Mode       |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 16    | FV          | DO-Forever Flag                   |

|                                                                                                                                                                                     |       |            |                                                                                                                                                                                           |     | 15    | LF          | DO-Loop Flag                      |

| MR                                                                                                                                                                                  | 15    | LF         | Loop Flag                                                                                                                                                                                 | MR  | 15    | LF          | Loop Flag                         |

|                                                                                                                                                                                     | 14    | DM         | Double Precision Multiply<br>Mode                                                                                                                                                         |     | 14    | DM          | Double-Precision Multiply<br>Mode |

|                                                                                                                                                                                     | 13    | Т          | Trace Mode                                                                                                                                                                                |     | 13    | SC          | Sixteen-Bit Compatibility<br>Mode |

|                                                                                                                                                                                     | 12    | _          | Reserved                                                                                                                                                                                  |     | 12    | —           | Reserved                          |

|                                                                                                                                                                                     | 11-10 | S1 –<br>S0 | Scaling Mode                                                                                                                                                                              |     | 11-10 | S1 –<br>S0  | Scaling Mode                      |

|                                                                                                                                                                                     | 9–8   | l1–l0      | Interrupt Mask                                                                                                                                                                            |     | 9–8   | l1 – l0     | Interrupt Mask                    |

| CCR                                                                                                                                                                                 | 7     | S          | Scaling                                                                                                                                                                                   | CCR | 7     | S           | Scaling                           |

|                                                                                                                                                                                     | 6     | L          | Limit                                                                                                                                                                                     |     | 6     | L           | Limit                             |

|                                                                                                                                                                                     | 5     | ш          | Extension                                                                                                                                                                                 |     | 5     | E           | Extension                         |

|                                                                                                                                                                                     | 4     | U          | Unnormalized                                                                                                                                                                              |     | 4     | U           | Unnormalized                      |

|                                                                                                                                                                                     | 3     | N          | Negative                                                                                                                                                                                  |     | 3     | N           | Negative                          |

|                                                                                                                                                                                     | 2     | Z          | Zero                                                                                                                                                                                      |     | 2     | Z           | Zero                              |

|                                                                                                                                                                                     | 1     | V          | Overflow                                                                                                                                                                                  |     | 1     | V           | Overflow                          |

|                                                                                                                                                                                     | 0     | С          | Carry                                                                                                                                                                                     |     | 0     | С           | Carry                             |

| DSP56002                                                                           |   |    | DSP56303                                                                                                                                                                                                                                                                                                                                                                       |     |       |                   |                                  |

|------------------------------------------------------------------------------------|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------|----------------------------------|

| The Operating Mode Register (OMR) is a 24-bit register with only six bits defined. |   |    | The OMR is a 24-bit register divided into three 8-bit sections.<br>The upper byte consists of the System Stack Control Status<br>Register (SCS), which controls and monitors the stack<br>extension. The two lower bytes consist of the Extended Chip<br>Operating Mode Register (EOM) and the Chip Operating<br>Mode Register (COM), which control the DSP operating<br>mode. |     |       |                   |                                  |

| -                                                                                  |   |    |                                                                                                                                                                                                                                                                                                                                                                                | SCS | 23–21 | _                 | Reserved                         |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 20    | SEN               | Stack Extension Enable           |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 19    | WRP               | Extended Stack Wrap Flag         |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 18    | EOV               | Extended Stack Overflow Flag     |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 17    | EUN               | Extended Stack Underflow<br>Flag |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 16    | XYS               | Stack Extension Space Select     |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                | EOM | 15    | ATE               | Address Tracing Enable           |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 14–13 | —                 | Reserved                         |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 12    | BRT               | Bus Release Timing               |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 11    | TAS               | TA Synchronize Select            |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 10    | BE                | Burst Mode Enable                |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                |     | 9–8   | CDP1<br>-<br>CDP0 | Interrupt Mask                   |

|                                                                                    |   |    |                                                                                                                                                                                                                                                                                                                                                                                | СОМ | 7     | MS                | Memory Switch Mode               |

|                                                                                    | 6 | SD | Stop Delay                                                                                                                                                                                                                                                                                                                                                                     |     | 6     | SD                | Stop Delay                       |

|                                                                                    | 4 | MC | Operating Mode C                                                                                                                                                                                                                                                                                                                                                               |     | 5     |                   | Reserved                         |

|                                                                                    | 3 | YD | Internal Y Memory Disable                                                                                                                                                                                                                                                                                                                                                      |     | 4     | EBD               | External Bus Disable             |

|                                                                                    | 2 | DE | Data ROM Enable                                                                                                                                                                                                                                                                                                                                                                |     | 3–0   | MD –<br>MA        | Operating Mode D–A               |

|                                                                                    | 1 | MB | Operating Mode B                                                                                                                                                                                                                                                                                                                                                               |     |       |                   |                                  |

|                                                                                    | 0 | MA | Operating Mode A                                                                                                                                                                                                                                                                                                                                                               |     |       |                   |                                  |

| Table 4  | Operating Made Register  | Comparison of the DSDE6002 and the DSDE6202 |

|----------|--------------------------|---------------------------------------------|

| Table 4. | Operating mode Register, | Comparison of the DSP56002 and the DSP56303 |

Table 5.

System Stack, Comparison of the DSP56002 and the DSP56303

| DSP56002                                                                                                                                                                                                                                                                        | DSP56303                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The System Stack (SS) is a separate 15-level by 32-bit<br>internal memory divided into two 16-bit wide banks: the<br>System Stack High (SSH) and the System Stack Low (SSL).<br>The SS accommodates up to 15 long interrupts, 7 DO loops,<br>15 JSRs, or combinations of these. | The SS is a separate 16-level by 48-bit internal memory<br>divided into two 24-bit wide banks: the System Stack High<br>(SSH) and the System Stack Low (SSL). If the Stack<br>Extension Enable (SEN) bit in the OMR is cleared, the SS<br>accommodates up to 15 long interrupts, 7 DO loops, 15<br>JSRs, or combinations of these. If the SEN bit is set, the<br>stack extension is enabled and the limits on the level of<br>nesting of subroutines or DO loops can be set to any desired<br>value. |

| Table 6. Program Counter, Comparison of the DSP56002 and the | ne DSP56303 |

|--------------------------------------------------------------|-------------|

|--------------------------------------------------------------|-------------|

| DSP56002                                                                                                                                        | DSP56303                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| The Program Counter (PC) is a 16-bit register that contains<br>the address of the next location to be fetched from the<br>program memory space. | The PC is a 24-bit register. |

#### **Table 7.** Vector Base Address Register, Comparison of the DSP56002 and the DSP56303

| DSP56002      | DSP56303                                                                                                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not Available | The Vector Base Address Register (VBA) is a 24-bit register that is used as a base address of the interrupt vector and interrupt vector+1. Bits 7–0 are read-only and are always cleared. |

## Table 8. Loop Counter Register, Comparison of the DSP56002 and the DSP56303

| DSP56002                                                                                                                         | DSP56303                    |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| The Loop Counter Register (LC) is a 16-bit counter that specifies the number of times a hardware program loop is to be repeated. | The LC is a 24-bit counter. |

## Table 9. Loop Address Register, Comparison of the DSP56002 and the DSP56303

| DSP56002                                                                                                                         | DSP56303                     |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| The Loop Address Register (LA) is a 16-bit register that indicates the location of the last instruction word in a hardware loop. | The LA is a 24-bit register. |

## Table 10. Stack Extension Pointer Register, Comparison of the DSP56002 and the DSP56303

| DSP56002      | DSP56303                                                                                                                                                                                                                         |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not Available | The Stack Extension Pointer Register (EP) is a 24-bit register<br>that points to the stack extension in data memory when the<br>stack extension is enabled and move operations to/from the<br>on-chip hardware stack are needed. |

## Table 11. Stack Size Register, Comparison of the DSP56002 and the DSP56303

| DSP56002      | DSP56303                                                                                                                                           |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Not Available | The Stack Size Register (SZ) is a 24-bit register that determines the number of data words allocated in memory for the stack in the extended mode. |

uction Set

| DSP56002      | DSP56303                                                                                                             |

|---------------|----------------------------------------------------------------------------------------------------------------------|

| Not Available | The Stack Counter Register (SC) is a 5-bit register that monitors how many entries of the hardware stack are in use. |

| Table 12. | Stack Counter Register, Comparison of the DSP56002 and the DSP56303 |

|-----------|---------------------------------------------------------------------|

|           |                                                                     |

## Table 13. Stack Pointer Register, Comparison of the DSP56002 and the DSP56303

| DSP56002   |     |                                                                |  |      |           | DSP56303                                      |                      |

|------------|-----|----------------------------------------------------------------|--|------|-----------|-----------------------------------------------|----------------------|

| es the loo |     | r (SP) is a 6-bit register tha<br>e top of the SS and the stat |  |      |           | egister. When the ex<br>of the SS is also inc |                      |

| Bit<br>No. |     | Description                                                    |  | Bit  |           | Descriptio                                    | on                   |

| 5          | UF  | Underflow Flag                                                 |  | No.  |           | Extended Mode                                 | Non-Extended<br>Mode |

| 4          | SE  | Stack Error Flag                                               |  | 23–6 | P23-      | Bits 23–6 of the Stack Pointer                |                      |

| 3–0        | P3- | Stack Pointer                                                  |  |      | P6        |                                               |                      |

|            | P0  |                                                                |  | 5    | UF/<br>P5 | Bit 5 of the Stack<br>Pointer                 | Underflow Flag       |

|            |     |                                                                |  | 4    | SE/<br>P4 | Bit 4 of the Stack<br>Pointer                 | Stack Error Flag     |

|            |     |                                                                |  | 3–0  | P3–P<br>0 | Bits 3–0 of the                               | Stack Pointer        |

|            |     |                                                                |  |      | 0         |                                               |                      |

## 7 Instruction Set

**Table 14** shows the DSP56300 instructions that are either available on the DSP56303 but not on the DSP56002 or that are enhanced on the DSP56303.

| Туре       | Instruction | Description                                                      | Status               |

|------------|-------------|------------------------------------------------------------------|----------------------|

| Arithmetic | ADD         | Add                                                              | Enhanced on DSP56300 |

|            | ASL         | Arithmetic Shift Accumulator Left                                | Enhanced on DSP56300 |

|            | ASR         | Arithmetic Shift Accumulator Right                               | Enhanced on DSP56300 |

|            | CMP         | Compare                                                          | Enhanced on DSP56300 |

|            | CMPU        | Compare Unsigned                                                 | DSP56300 only        |

| -          | DMAC        | Double (Multi) Precision Multiply Accumulate with<br>Right Shift | DSP56300 only        |

|            | MACI        | Signed Multiply-Accumulate with Immediate Operand                | DSP56300 only        |

|            | MACsu       | Mixed Multiply Accumulate (S1 signed, S2 unsigned)               | DSP56300 only        |

|            | MACuu       | Mixed Multiply Accumulate (S1 and S2 unsigned)                   | DSP56300 only        |

| -          | MACRI       | Signed Multiply-Accumulate and Round with<br>Immediate Operand   | DSP56300 only        |

## Table 14. DSP56300 Instructions

| Туре       | Instruction | Description                                              | Status               |

|------------|-------------|----------------------------------------------------------|----------------------|

| Arithmetic | MAX         | Transfer by Signed Value                                 | DSP56300 only        |

| cont.      | MAXM        | Transfer by Magnitude                                    | DSP56300 only        |

|            | MERGE       | Merge Two Half Words                                     | DSP56300 only        |

|            | MPYsu       | Mixed Multiply (S1 signed, S2 unsigned)                  | DSP56300 only        |

|            | MPYuu       | Mixed Multiply (S1 and S2 unsigned)                      | DSP56300 only        |

|            | MPYI        | Signed Multiply with Immediate Operand                   | DSP56300 only        |

|            | MPYRI       | Signed Multiply and Round with Immediate Operand         | DSP56300 only        |

|            | NORMF       | Fast Accumulator Normalization                           | DSP56300 only        |

|            | SUB         | Subtract                                                 | Enhanced on DSP56300 |

| Logical    | AND         | Logical AND                                              | Enhanced on DSP56300 |

|            | CLB         | Count Leading Bits                                       | DSP56300 only        |

|            | EOR         | Logical Exclusive OR                                     | Enhanced on DSP56300 |

|            | EXTRACT     | Extract Bit Field                                        | DSP56300 only        |

|            | EXTRACTU    | Extract Unsigned Bit Field                               | DSP56300 only        |

|            | INSERT      | Insert Bit Field                                         | DSP56300 only        |

|            | LSL         | Logical Shift Left                                       | Enhanced on DSP56300 |

|            | LSR         | Logical Shift Right                                      | Enhanced on DSP56300 |

|            | OR          | Logical OR                                               | Enhanced on DSP56300 |

| Loop       | DOR         | Start PC Relative Hardware Loop                          | DSP56300 only        |

|            | BRKcc       | Exit Current Do Loop Conditionally                       | DSP56300 only        |

| Move       | LRA         | Load PC Relative Address                                 | DSP56300 only        |

| Program    | IFcc        | Execute Conditionally                                    | DSP56300 only        |

| Control    | IFcc.U      | Execute Conditionally and Update Condition Code Register | DSP56300 only        |

|            | BRCLR       | Branch if Bit Clear                                      | DSP56300 only        |

|            | BRSET       | Branch if Bit Set                                        | DSP56300 only        |

|            | BSCLR       | Branch to Subroutine if Bit Clear                        | DSP56300 only        |

|            | BSSET       | Branch to Subroutine if Bit Set                          | DSP56300 only        |

|            | PLOCK       | Lock Instruction Cache Sector                            | DSP56300 only        |

|            | PUNLOCK     | Unlock Instruction Cache Sector                          | DSP56300 only        |

|            | PLOCKR      | Lock Instruction Cache Relative Sector                   | DSP56300 only        |

|            | PUNLOCKR    | Unlock Instruction Cache Relative Sector                 | DSP56300 only        |

|            | PFREE       | Program Cache Global Unlock                              | DSP56300 only        |

|            | PFLUSH      | Program Cache Flush                                      | DSP56300 only        |

|            | PFLUSHUN    | Program Cache Flush Unlocked Sectors                     | DSP56300 only        |

|            | TRAP        | Software Interrupt                                       | DSP56300 only        |

|            | TRAPcc      | Conditional Software Interrupt                           | DSP56300 only        |

## Table 14. DSP56300 Instructions (Continued)

## uction Set

## 7.1 Arithmetic Instructions

**Table 15** lists the arithmetic instructions that are either available on the DSP56303 but not on the DSP56002 or enhanced on the DSP56303.

| Instruction | Description                                                                                                                                                          | Valid Asser                                                   | nbler Syntax                                           |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|

| ADD         | Enhanced to support the addition of a 6-bit<br>short immediate or a 24-bit long immediate<br>data to the destination accumulator.                                    | <b>ADD S,D</b><br>X0, X1, Y0, Y1, X, Y, A, B<br>A, B          | ;S is source register<br>;D is destination accumulator |

|             |                                                                                                                                                                      | <b>ADD #ii,D</b><br>data                                      | ;#ii is 6-bit immediate short                          |

|             |                                                                                                                                                                      | ADD #iiiiii,D<br>data extension<br>;word                      | ;#iiiiii is 24-bit immediate long                      |

| ASL/ASR     | Enhanced to support the multi-bit shifting.                                                                                                                          | ASL D<br>A,B                                                  | ;D is destination accumulator                          |

|             |                                                                                                                                                                      | <b>ASL #ii,S2,D</b><br>55]                                    | ;#ii is 6-bit unsigned integer [0-                     |

|             |                                                                                                                                                                      | ;denoting the shift amount                                    | ;S2 is source accumulator A, B                         |

|             |                                                                                                                                                                      | <b>ASL S1,S2,D</b><br>Y0, Y1, A1, B1                          | ;S1 is control register X0, X1,                        |

| СМР         | Enhanced to support the comparison of a 6-bit short immediate data or a 24-bit long                                                                                  | <b>CMP S1,S2</b><br>X1, Y0, Y1, A, B                          | ;S1 is source one register X0,                         |

|             | immediate data to a source accumulator.                                                                                                                              | Α, Β                                                          | ;S2 is source two accumulator                          |

|             |                                                                                                                                                                      | CMP #ii,S2<br>data                                            | ;#ii is 6-bit immediate short                          |

|             |                                                                                                                                                                      | CMP #iiiiii,S2<br>data<br>;extension word                     | ;#iiiiii is 24-bit immediate long                      |

| СМРU        | DSP56300 only. Subtracts the source<br>operand from the source accumulator and<br>updates the condition code register. The<br>result of the operation is not stored. | CMPU S1,S2<br>;S1<br>Y0, Y1, A, B<br>;S2 is source two accumu | is source one register X0, X1,<br>lator A, B           |

| DMAC        | DSP56300 only. Multiplies the two signed<br>24-bit source operands and adds/subtracts<br>the product to/from the specified 56-bit                                    | DMAC (+/-)S1,S2,D<br>;S1, S2 are source registe<br>;X1, Y1    | ers X0, Y0,                                            |

|             | destination accumulator which has been previously shifted 24 bits to the right.                                                                                      | accumulator A, B                                              | ;D is destination                                      |

| MACI        | DSP56300 only. Multiplies the two signed<br>24-bit source operands and adds/subtracts                                                                                | MACI (+/-)#iiiiii,S,D                                         | ;#iiiiii is 24-bit                                     |

|             | the product to/from the specified 56-bit destination accumulator.                                                                                                    | immediate long data<br>;extension word<br>is source register  | ;S                                                     |

|             |                                                                                                                                                                      | ;X0, Y0, X1, Y1<br>accumulator A, B                           | ;D is destination                                      |

Table 15.

Arithmetic Instructions Added/Enhanced on the DSP56303 But Not on the DSP56002

|  |          | 1 |         |

|--|----------|---|---------|

|  |          | 7 |         |

|  |          |   |         |

|  |          |   | <br>× . |

|  | $\sim 1$ |   |         |

| Instruction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                         | Valid Assembler Syntax                                                                                                                          |                                            |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| MACsu/<br>MACuu | DSP56300 only. MACsu multiplies the two<br>24-bit source operands, in which one<br>source operand is unsigned and the other<br>is signed, and adds/subtracts the product<br>to/from the specified 56-bit destination<br>accumulator. MACuu multiplies the two 24-<br>bit source operands, in which both source<br>operands are unsigned, and<br>adds/subtracts the product to/from the<br>specified 56-bit destination accumulator. | MACsu (+/-)S1,S2,D<br>;S1, S2 are source registers X0, X1<br>;Y0, Y1<br>accumulator A, B                                                        | ,<br>; D is destination                    |  |

| MACRI           | DSP56300 only. Multiplies the two signed<br>24-bit source operands and adds/subtracts<br>the product to/from the specified 56-bit<br>destination accumulator.                                                                                                                                                                                                                                                                       | MACRI (+/-)#iiiiii,S,D<br>;#iiiiii is 24-bit immediate long data<br>;extension word<br>;S is source register X0, Y0, X1, Y1<br>accumulator A, B | ;D is destination                          |  |

| MAX             | DSP56300 only. Subtracts the signed<br>value of the source accumulator from the<br>signed value of the destination<br>accumulator. If the difference is negative<br>or zero, the source accumulator is<br>transferred to the destination accumulator.<br>Otherwise, the destination accumulator<br>remains unchanged.                                                                                                               | MAX A,B<br>accumulators                                                                                                                         | ;A, B are source                           |  |

| MAXM            | DSP56300 only. Subtracts the magnitude<br>of the source accumulator from the<br>magnitude of the destination accumulator.<br>If the difference is negative or zero, the<br>source accumulator is transferred to the<br>destination accumulator. Otherwise, the<br>destination accumulator remains<br>unchanged.                                                                                                                     | MAXM A,B<br>accumulators                                                                                                                        | ;A, B are source                           |  |

| MERGE           | DSP56300 only. Concatenates the<br>contents of bits 11–0 of the source register<br>to the contents of bits 35–24 of the<br>destination accumulator. In 16-bit<br>arithmetic mode, the contents of bits 15–8<br>of the source register are concatenated to<br>the contents of bits 39–32 of the<br>destination accumulator. The result is<br>placed in bits 47–32 of the destination<br>accumulator.                                 | MERGE S,D<br>X0, X1, Y0, Y1, A1, B1<br>accumulator A, B                                                                                         | ;S is source register<br>;D is destination |  |

| MPYsu/<br>MPYuu | DSP56300 only. MPYsu multiplies the two<br>24-bit source operands, in which one<br>source operand is unsigned and the other<br>is signed, and stores the product in the<br>specified 56-bit destination accumulator.<br>MPYuu multiplies the two 24-bit source<br>operands, in which both source operands<br>are unsigned, and stores the product in the<br>specified 56-bit destination accumulator.                               | MPYsu (+/-)S1,S2,D<br>source registers X0, X1, Y0,<br>;Y1<br>accumulator A, B                                                                   | ;S1, S2 are<br>;D is destination           |  |

Table 15. Arithmetic Instructions Added/Enhanced on the DSP56303 But Not on the DSP56002 (Continued)

| Instruction | Description                                                                                                                                                                                                                                                                                                                                                                                              | Valid As                                                                                                       | sembler Syntax                                                                                                                       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| MPYI        | DSP56300 only. Multiplies the immediate<br>24-bit source operand with the 24-bit<br>source operand and stores the resulting<br>product in the specified 56-bit destination<br>accumulator.                                                                                                                                                                                                               | MPYI (+/-)#iiiiii,S,D<br>immediate long data<br>;extension word<br>X0, Y0, X1, Y1<br>accumulator A, B          | ;#iiiiii is 24-bit<br>;S is source register<br>;D is destination                                                                     |