# AN14879

## FS6500 and FS4500 software quick start guide

Rev. 1.0 — 17 December 2025

**Application note**

#### **Document information**

| Information | Content                                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FS4500, FS6500, safety, SBC, software, ASIL B, ASIL D                                                                                              |

| Abstract    | This application note is meant to be used as a launching point for software engineers, as a complement or a substitute for NXP's software drivers. |

FS6500 and FS4500 software quick start guide

### 1 Introduction

This application note is meant for software engineers who use the FS6500 and FS4500 series of devices.

This document gives guidelines on the implementation of the serial peripheral interface (SPI) communication protocol between the MCU and the SBC, illustrates the initialization procedure of the FS6500 and FS4500 series of devices, watchdog refresh, and fail-safe pin releases to help software engineers quickly start with development.

#### 1.1 Device introduction

The FS6500 and FS4500 SMARTMOS devices are a multi-output, power supply, integrated circuit (IC), including controller area network (CAN) flexible data (FD) and/or local interconnect network (LIN) transceivers, dedicated to the automotive market. The FS6500 and FS4500 include configurable fail-safe/fail-silent safety behavior and features, with two fail-safe outputs, becoming a full part of a safety-oriented system partitioning. There are ASIL B and ASIL D parts to fit different system requirements.

#### 1.2 Reference documents

Reference documents and various materials are available on the <u>FS6500 and FS4500 series devices webpage</u> and <u>NXP SBC/PMIC - real-time drivers site</u>. The webpage provides more detailed information about specific topics:

<u>FS4500-FS6500 data sheet</u>: Information, such as features, functional description, parametric description, register mapping.

<u>FS4500-FS6500 hardware design guideline application note (AN5238)</u>: Information, such as application schematics, bill of materials, placement and layout guidelines, application validation data including ISO/non-ISO pulses, electromagnetic compatibility (EMC).

BSPs and device drivers: There are demo drivers and examples with MPC574xP-MC33FS65xx/MC33FS45xx and Embedded Software Driver.

<u>FS6500 and FS4500 SBC Autosar 4.4 version 0.8.0</u>: AUTOSAR and ISO 26262-compliant basic start-up drivers for low-level interfaces, software driver package (FS4500 and FS6500 series devices share the same driver), detailing supported features, such as:

- SBC\_FS65 CDD: Complex driver for the device.

- WDG FS65: Watchdog function services.

- CANTRCV FS65: CAN PHY driver and functions.

- · LINTRCV FS65: LIN PHY driver and functions.

FS6500 and FS4500 software quick start guide

## 2 SPI protocol and configurations

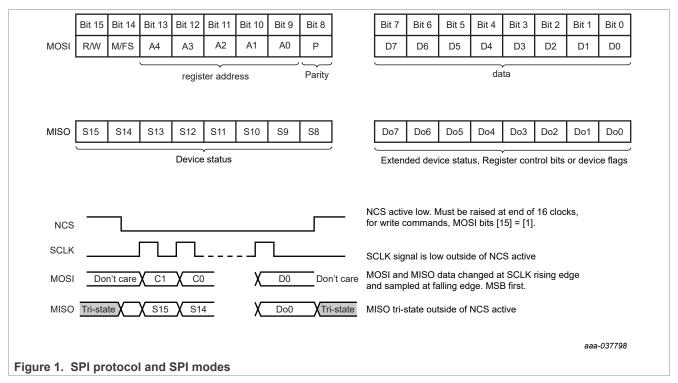

Shown in Figure 1, the device uses a 16-bit SPI with the following register bits definitions and arrangements:

- MOSI Bit 15: R/W: 0 Read, 1 Write

- MOSI Bit 14: M/FS: 0 Main, 1 Fail-safe

- MOSI Bit 9~13: Register address

- MOSI Bit 8: Parity bit, 0 Number of 1 (bit 15:9 and bit 7:0) is odd. 1 Number of 1 (bit 15:9 and bit 7:0) is

even

- MOSI Bit 7~0: in Write mode. Must be set to 00h in Read mode.

- MISO Bit 15~8: Device status

- MISO Bit 7~0: Extended device status. Register control bits or device flags.

When configuring the SPI protocol in the MCU driver or in the configuration tool, configure it as:

- 16-bit SPI

- NCS active low

- MSB first

- SPI mode1: CPOL = 0 and CPHA = 1: CLK idle state = low, data sampled on the falling edge and shifted on the rising edge

Detailed main and fail-safe register addresses and bits descriptions can reach to data sheet <u>ref.[1]</u>, in Section 13.2, "Detailed operation".

FS6500 and FS4500 software quick start guide

## 3 FS6500 and FS4500 initialization flow chart and demo commands

#### 3.1 Software flow chart

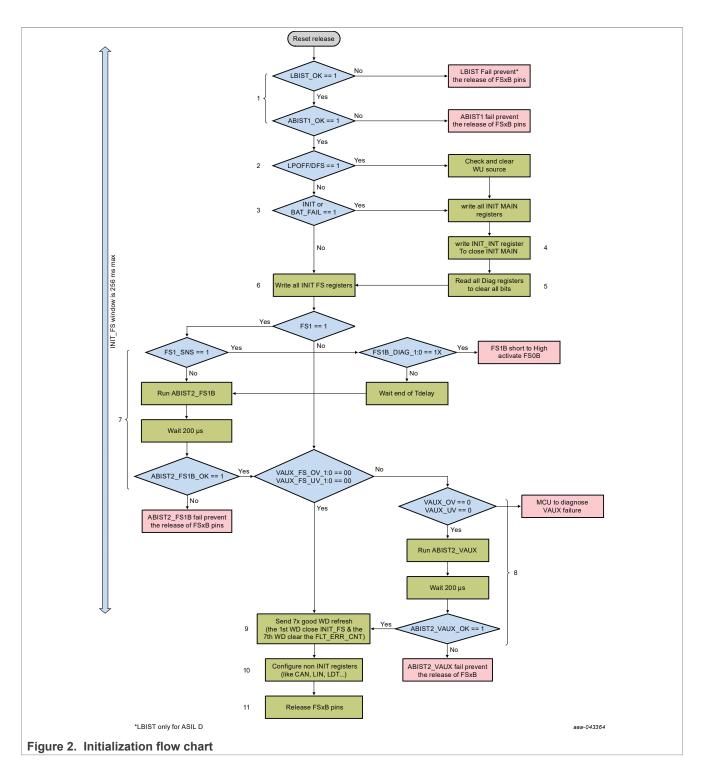

<u>Figure 2</u> is a flow chart to describe the initialization process of FS6500 and FS4500 devices. The process can be described as follows:

- 1. Check LBIST/ABIST1 check result. FSxB cannot be released when either check is a failure.

- 2. Check power-up reason: When the device is POR(BAT\_FAIL = 1) and wakeup is from LPOFF/DFS, both main and fail-safe initial registers are configured and all Diag registers are read once to clear initial states. When the device has entered Main mode and an RSTB event happens, only fail-safe initial registers are configured.

- 3. ABIST2 is run by MCU SPI commands to check VAUX and FS1B block safety states. If either ABIST2 fails, FSxB cannot be released.

- 4. Seven continuous good watchdog refreshes are needed to clear a fault error counter value, as it is 1 by default when device goes through power-on reset (POR) or wakes up from LPOFF.

- 5. Configure non-initial registers.

- 6. Release FSxB with required commands.

### FS6500 and FS4500 software quick start guide

#### 3.2 SPI commands of initialization

Startup SPI sequence example SPI commands based on FS6500 and FS4500 flow chart. A SPI command can be a quick-check command to quick start or issue debug.

## FS6500 and FS4500 software quick start guide

Table 1. Startup SPI sequence

|   |                      | Register                   | Read     | Write  | Comment                                                                            |  |  |

|---|----------------------|----------------------------|----------|--------|------------------------------------------------------------------------------------|--|--|

| 1 | Check BIST           | BIST                       | 0x4400   | _      | Check LBIST_OK and ABIST1_OK bits <sup>[1]</sup>                                   |  |  |

| 2 | Check WU source      | WU_SOURCE                  | 0x1200   | _      | Check wake-up sources if wake-up from LPOFF                                        |  |  |

| 3 | Check POR            | INIT_VREG                  | 0x0200   | _      | Check BAT_FAIL bit                                                                 |  |  |

|   |                      | INIT_VREG                  | _        | 0x8210 | Activate Vcan monitoring Vaux tracker disable                                      |  |  |

| 4 | INIT_MAIN            | INIT_WU1                   | _        | 0x8440 | Default value IO_0 wake-up on rising edge or high-level enable                     |  |  |

|   |                      | INIT_WU2                   | _        | 0x8600 | Default value                                                                      |  |  |

|   |                      | INIT_INH_INT               | _        | 0x8A00 | Default value                                                                      |  |  |

|   |                      | INIT_INT                   | -        | 0x8900 | Default value                                                                      |  |  |

|   |                      | DIAG_VPRE                  | 0x1800   | _      | Clear VPRE_UV after POR or wake-up                                                 |  |  |

|   |                      | DIAG_VCORE                 | 0x1A00   | _      | Clear VCORE_FB_UV after POR or wake-up                                             |  |  |

| 5 | Read Diag registers  | DIAG_VCCA                  | 0x1C00   | _      | Clear VCCA_UV after POR or wake-up                                                 |  |  |

| ı | Tread Diag registers | DIAG_VAUX                  | 0x1E00   | _      | Clear VAUX_UV after POR or wake-up                                                 |  |  |

|   |                      | DIAG_VSUP_VCAN             | 0x2000   | _      | Clear VSNS_UV and VSUP_UV_7 after POR Clear VCAN_UV after wake-up                  |  |  |

|   |                      | INIT_FS1B_Timing           | _        | 0xC265 | Default value                                                                      |  |  |

|   |                      | INIT_SUPERVISOR            | <u> </u> | 0xC70C | Default value                                                                      |  |  |

|   |                      | INIT_FAULT                 | _        | 0xC80C | FLT_ERR_CNT = 6, FS1B has no impact on CAN                                         |  |  |

|   |                      | INIT_FSSM                  | -        | 0xCB0C | IO_2:3 and IO_4:5 are not safety critical                                          |  |  |

|   |                      | INIT_SF_IMPACT             | _        | 0xCD18 | Default value FS1B Tdelay. Reset only at WD_CNT_ERR final value                    |  |  |

| 6 | INIT_FS              | INIT_WD_CNT                | _        | 0xD90C | Default value WD_CNT_ERR = WD_CNT_RFR = 6                                          |  |  |

|   |                      | INIT_VCORE_UVOV_<br>IMPACT | _        | 0xE3E7 | Default value VCORE_FB_OV impact on RSTB and FS0B, VCORE_FB_UV impact on FS0B only |  |  |

|   |                      | INIT_VCCA_UVOV_<br>IMPACT  | _        | 0xE5E7 | Default value VCCA_OV impact on RSTB and FS0B, VCCA_UV impact on FS0B only         |  |  |

|   |                      | INIT_VAUX_UVOV_<br>IMPACT  | _        | 0xE6E7 | Default value VAUX_OV impact on RSTB and FS0B, VAUX_UV impact on FS0B only         |  |  |

|   |                      | Device_ID_FS               | 0x6800   | _      | Check FS1 bit                                                                      |  |  |

| 7 | ABIST                | RELEASE_FSxB               | 0x5400   | _      | Check FS1B_SNS bit                                                                 |  |  |

| 1 | FS1B                 | BIST                       | _        | 0xC44D | Start FS1B ABIST                                                                   |  |  |

|   |                      | BIST                       | 0x4400   | _      | Check FS1B ABIST result                                                            |  |  |

| Ω | ABIST                | BIST                       | _        | 0xC424 | Start VAUX ABIST <sup>[2]</sup>                                                    |  |  |

| 8 | VAUX                 | BIST                       | 0x4400   | _      | Check VAUX ABIST result                                                            |  |  |

|   |                      | WD_LFSR                    | 0x5000   | _      | Read LFSR                                                                          |  |  |

| 0 | Ty good MD refresh   | WD_ANSWER                  | _        | 0xD34D | Watchdog answer to be calculated <sup>[3]</sup>                                    |  |  |

| 9 | 7x good WD refresh   | WD_LFSR                    | 0x5000   | _      | Read LFSR                                                                          |  |  |

|   |                      | WD_ANSWER                  | _        | 0xD29B | Watchdog answer to be calculated <sup>[3]</sup>                                    |  |  |

### FS6500 and FS4500 software quick start guide

Table 1. Startup SPI sequence...continued

|    |              | Register              | Read   | Write    | Comment                                                                       |

|----|--------------|-----------------------|--------|----------|-------------------------------------------------------------------------------|

|    |              | WD_LFSR               | 0x5000 | _        | Read LFSR                                                                     |

|    |              | WD_ANSWER             | _      | 0xD237   | Watchdog answer to be calculated <sup>[3]</sup>                               |

|    |              | WD_LFSR               | 0x5000 | _        | Read LFSR                                                                     |

|    |              | WD_ANSWER             | _      | 0xD26E   | Watchdog answer to be calculated <sup>[3]</sup>                               |

|    |              | WD_LFSR               | 0x5000 | _        | Read LFSR                                                                     |

|    |              | WD_ANSWER             | _      | 0xD2DC   | Watchdog answer to be calculated <sup>[3]</sup>                               |

|    |              | WD_LFSR               | 0x5000 | _        | Read LFSR                                                                     |

|    |              | WD_ANSWER             | _      | 0xD2B9   | Watchdog answer to be calculated <sup>[3]</sup>                               |

|    |              | WD_LFSR               | 0x5000 | _        | Read LFSR                                                                     |

|    |              | WD_ANSWER             | _      | 0xD372   | Watchdog answer to be calculated <sup>[3]</sup>                               |

| 10 | CAN_LIN_MODE | CAN_LIN_MODE          | _      | 0xB0C0   | CAN in normal operation mode                                                  |

|    |              | SF_OUTPUT_<br>REQUEST | _      | 0xD60C   | Close S1 switch between VPRE and VPU_FS <sup>[4]</sup>                        |

| 11 | RELEASE FSxB | WD_LFSR               | 0x5000 | <u> </u> | Read LFSR                                                                     |

|    |              | RELEASE_FSxB          | _      | 0xD4A7   | Release both FS0B and FS1B at the same time RELEASE_FSxB_4:0 to be calculated |

LBIST for ASIL D only. ABIST on FS1B and VAUX can be launched simultaneously with SPI command 0xC465. The wait time remains  $200~\mu s$  for both ABIST. [1] [2]

For ASIL B version, only write commands in WD\_ANSWER register are needed.

When FS1B is used, the switch S1 can be closed earlier, just after ABIST2 on FS1B, to allow the charge of Cpd while the fault error counter is cleared, reducing the application starting time.

FS6500 and FS4500 software quick start guide

## 4 Watchdog refresh procedure

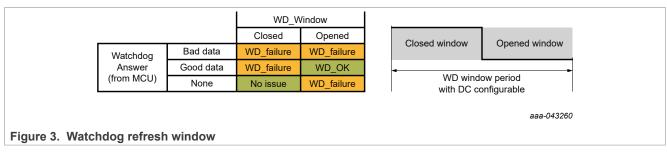

A windowed watchdog is implemented in the FS6500 and FS4500, and is based on the question/answer principle (challenger). The watchdog must be continuously triggered by the MCU in the open watchdog window, otherwise an error is generated. The Fail-Safe state machine manages error handling and watchdog operations.

The first good watchdog refresh closes the initialization phase (INIT\_FS). As soon as the initialization phase is closed, the watchdog monitors the software failures from the MCU by doing a periodic handshake with the FS6500 and FS4500 through the SPI communication protocol. The watchdog must be continuously triggered by the MCU in the open watchdog window, otherwise an error is generated. The Fail-Safe state machine manages error handling and watchdog operations. The MCU must refresh the watchdog periodically in the middle of the open window by writing the right watchdog answer in the WD\_ANSWER register.

For FS6500 and FS4500 ASIL B version, the watchdog is simple and refreshed by the MCU using any key. The only requirement is the watchdog refresh time must in the second half (open window) of the whole watchdog window. It is suggested to make the watchdog refresh at 3/4 of the watchdog window.

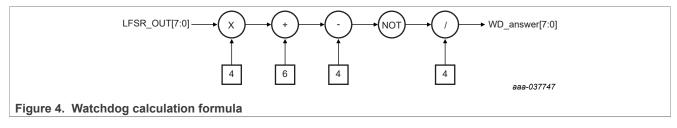

For FS6500 and FS4500 ASIL D version, the watchdog is a challenger watchdog that must be refreshed with a key calculated from the seed value, which can be read in the WD\_LFSR register. (The seed can also be written by the MCU during INIT\_FS). At the INIT\_FS phase, the MCU must read the seed value before starting in order to calculate the watchdog answer using the formula shown in <a href="Figure 4">Figure 4</a>. It is suggested to make the watchdog refresh at 3/4 of the watchdog window.

FS6500 and FS4500 software quick start guide

## 5 Release FSxB calculation procedure

- 1. ABIST2 VAUX OK = 1, except if VAUX FS OV 1:0 = VAUX FS UV 1:0 = 00

- 2. ABIST2 FS1B OK = 1, if part number with FS1B

- 3. Close S1 switch between VPRE and VPU FS if FS1B is pulled up to VPU FS

- Fault error counter must be at 0; decrease it with N consecutive good WD refreshes with N = FLT\_ERR\_2:0 x (WD\_RFR\_2:0 + 1)

- 5. Read LSFR data via the SPI

- 6. Invert all bits of LFSR and swap MSB and LSB bits; the new byte is used to fill in the RELEASE\_FSxB register as described in <u>Table 2</u>:

Table 2. RELEASE\_FSxB register

|                       | WD_LFSR_7:0      | b7 | b6 | b5 | b4             | b3        | b2             | b1             | b0            |

|-----------------------|------------------|----|----|----|----------------|-----------|----------------|----------------|---------------|

| Release FS0B          | Release_FSxB_7:0 | 0  | 1  | 1  | <del>b0</del>  | <u>b1</u> | <del>b</del> 2 | <del>b</del> 3 | <del>b4</del> |

| Release FS1B          | Release_FSxB_7:0 | 1  | 1  | 0  | <del>b</del> 3 | b4        | b5             | <del>b</del> 6 | b7            |

| Release FS0B and FS1B | Release_FSxB_7:0 | 1  | 0  | 1  | <del>b0</del>  | b1        | b2             | <del>b6</del>  | b7            |

Note: It is recommended to release FS0B in Application mode rather than Boot Loader mode.

The RELEASE\_FSxB write command must be done after the WD\_LFSR read command within the same WD period, and one time only. If FS0B and FS1B are released sequentially, the procedure must be done a first time for FS0B, and a second time for FS1B.

FS6500 and FS4500 software quick start guide

## 6 References

- [1] FS6500-FS4500-ASILD Safety power system basis chip with CAN FD and LIN transceivers, data sheet

- [2] AN5238 FS6500 and FS4500 safe system basis chip hardware design and product guidelines, application note

- [3] FS45FS65 software drivers at NXP website: <a href="https://www.nxp.com/products/FS4500">https://www.nxp.com/products/FS4500</a>, <a href="https://www.nxp.com/products/FS4500">https://www.nxp.com/products/FS4500</a>, <a href="https://www.nxp.com/products/FS4500">https://www.nxp.com/products/FS4500</a>, <a href="https://www.nxp.com/products/FS4500">https://www.nxp.com/products/FS4500</a>, <a href="https://www.nxp.com/products/FS4500">https://www.nxp.com/products/FS4500</a>

- [4] FS45FS65 AUTOSAR Driver website: <a href="https://nxp.flexnetoperations.com/control/frse/product?entitlement">https://nxp.flexnetoperations.com/control/frse/product?entitlement</a> Id=672573417&lineNum=1&authContactId=113165297&authPartyId=120061187

FS6500 and FS4500 software quick start guide

## 7 Revision history

#### Table 3. Revision history

| Document ID   | Release date     | Description     |

|---------------|------------------|-----------------|

| AN14879 v.1.0 | 17 December 2025 | Initial version |

#### FS6500 and FS4500 software quick start guide

## Legal information

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace \ensuremath{\mathsf{B.V.}}\xspace - \ensuremath{\mathsf{NXP}}\xspace \ensuremath{\mathsf{B.V.}}\xspace$  is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

## FS6500 and FS4500 software quick start guide

## **Tables**

| Tab. 1. | Startup SPI sequence6  | Tab. 3. | Revision history1 |

|---------|------------------------|---------|-------------------|

| Tab. 2. | RELEASE_FSxB register9 |         |                   |

## FS6500 and FS4500 software quick start guide

## **Figures**

| Fig. 1. | SPI protocol and SPI modes3 | Fig. 3. | Watchdog refresh window      |

|---------|-----------------------------|---------|------------------------------|

| Fig. 2. | Initialization flow chart5  | Fig. 4. | Watchdog calculation formula |

### FS6500 and FS4500 software quick start guide

### **Contents**

| 2      |

|--------|

| 2      |

| 2      |

| s 3    |

| n flow |

| 4      |

| 4      |

| 5      |

| 8      |

| edure9 |

| 10     |

| 11     |

| 12     |

|        |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.