## AN14806

# KE1xF to MCX E24x Migration Guide Rev. 1.0 — 22 September 2025

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14806, KE1xF, MCX E24x, migration                                                                                                                                 |

| Abstract    | This application note describes the key differences between the KE1xF and MCX E24x families and their general considerations when migrating from KE1xF to MCX E24x. |

**KE1xF** to MCX E24x Migration Guide

## 1 Introduction

This application note describes the key differences between the KE1xF and MCX E24x families and their general considerations when migrating from KE1xF to MCX E24x.

The goal of this document is to enable developers to extend their existing KE1xF-based applications by leveraging the MCX E24x family, which offers higher flash and RAM capacity, improved integration, and enhanced long-term support. In many cases, the hardware remains pin-to-pin compatible and the software transition is simplified thanks to the shared MCUXpresso SDK architecture. This document highlights the key hardware and software aspects to achieve a seamless and efficient migration path.

## 2 High-level change summary

Taking the KE1xF family as a reference, <u>Table 1</u> presents the high-level changes observed when migrating to the MCX E24x family. It includes a column labeled "Migration impact", which qualifies the level of impact that each change may have on software migration efforts.

The classification used for the "Migration impact" column is as follows:

- High: IP differs significantly (new version, different register map, or new behavior). It requires to rewrite the software component.

- Medium: A major change to an existing IP, such as a new version or extended functionality, potentially impacting driver configuration or register-level access.

- Low: A minor update or no significant change to the IP, typically requiring minimal or no software modifications.

- No Diff: Identical IP with the same software interface (API). No code changes are required when migrating from KE1xF to MCX E24x.

- N/A: The IP does not exist in the source platform (KE1xF), so no migration is applicable.

Table 1. KE1xF and MCX E24x family level comparison

|                  | Family name          | KE1xF                  | Migration impact | MCX E24x                                                   |

|------------------|----------------------|------------------------|------------------|------------------------------------------------------------|

| Memory and       | P-flash              | 256 kB to 512 kB       | No diff          | 512 kB to 2 MB                                             |

| security         | D-flash [kB]         | Up to 32 kB (Flex NVM) | Low              | Up to 64 kB                                                |

|                  | EEPROM [kB]          | Up to 4 kB (Flex RAM)  | No diff          | 4 kB (FlexRAM)                                             |

|                  | Total RAM [kB]       | Up to 64 kB            | Low              | 64 kB to 256 kB                                            |

|                  | Security<br>solution | MPU, CRC, WDT,<br>EWM  | High             | MPU, CRC,<br>WDT EWM,<br>EdgeLock<br>Accelerator<br>(CSEC) |

| Core/performance | Core quantity        | 1 x CM4F               | No diff          | 1 x CM4F                                                   |

|                  | Frequency<br>[MHz]   | Up to 168 MHz          | No diff          | Up to 112 MHz                                              |

|                  | DMA                  | 16 channels            | Low              | 16 channels                                                |

|                  | DMIPS                | ~ 200                  | No diff          | ~ 100                                                      |

| Communication    | FlexCAN              | 2 (No FD)              | Medium           | 3 FlexCAN (1 x<br>FD MCX E245,<br>2 x FD MCX               |

KE1xF to MCX E24x Migration Guide

Table 1. KE1xF and MCX E24x family level comparison...continued

|                   | Family name                  | KE1xF                 | Migration impact | MCX E24x                               |

|-------------------|------------------------------|-----------------------|------------------|----------------------------------------|

|                   |                              |                       |                  | E246, 3 x FD<br>MCX E247)              |

|                   | Ethernet                     | <b>X</b> No           | N/A              | 10/100 Mbps<br>IEEE-1588<br>(MCX E247) |

|                   | SAI                          | <b>X</b> No           | N/A              | 2 (MCX E247)                           |

|                   | LIN/LPUART                   | 3                     | Low              | 3                                      |

|                   | LPSPI                        | 2                     | Low              | 3                                      |

|                   | LPI2C                        | 2                     | Low              | 1 up to 2 (MCX<br>E247)                |

| Extensions        | FlexIO                       | 8 channels            | Low              | 8 channels                             |

|                   | QSPI                         | <b>X</b> No           | N/A              |                                        |

| Analog and timers | 12-bit ADC                   | 3                     | Low              | 2                                      |

|                   | ACMP (instances)             | 3                     | Low              | 1                                      |

|                   | TRGMUX, ADC cross triggering | ∀ Yes                 | Low              | √ Yes                                  |

|                   | Timer modules/<br>channels   | 4 FTM/8 channels each | Low              | 4 up to 8 FTM/8 channels each          |

|                   | RTC                          | √ Yes                 | No Diff          | √ Yes                                  |

| Packaging         | 48 LQFP                      | <b>X</b> No           | N/A              | √ Yes (MCX E245)                       |

|                   | 64 LQFP                      | ∀ Yes                 | Low              | √ Yes (MCX E245/246)                   |

|                   | 100 LQFP                     | √ Yes                 | Low              | ∀ Yes                                  |

|                   | 144 LQFP                     | <b>X</b> No           | N/A              | √ Yes (MCX E246/247)                   |

#### In summary:

- Depending on the application profile, around 50 % of the IPs and peripherals are reused or functionally equivalent between KE1xF and MCX E24x, while the remaining of 50 % shows functional or architectural changes, including updated peripheral versions, added features (for example, QSPI), or renamed modules. Migration at a software level is facilitated through updated SDKs available in MCUXpresso.

- While both families are based on Arm Cortex-M4F cores, the performance profiles differ, with KE1xF reaching up to 168 MHz versus 112 MHz for MCX E24x. Although this results in a lower raw CPU frequency on MCX E24x, the overall application performance is comparable or improved thanks to enhanced system-level features, such as additional CAN FD interfaces, QSPI, and other peripheral and accelerator improvements.

- Security capabilities differ significantly as MCX E24x integrates the EdgeLock Accelerator (CSEC) and additional memory protection logic compared to KE1xF, which may require a software adaptation for secure boot or key storage use cases.

- Packaging compatibility is maintained for shared options, such as 64 and 100 LQFP, which are pin-to-pin compatible between KE1xF and MCX E24x. Additional package variants introduced with MCX E24x (such as 48 LQFP and 144 LQFP) offer more compact or feature-rich design. A hardware redesign may

KE1xF to MCX E24x Migration Guide

be required, but the pin assignment and peripheral distribution remain similar to support easier migration between equivalent packages.

## 3 Platform architecture

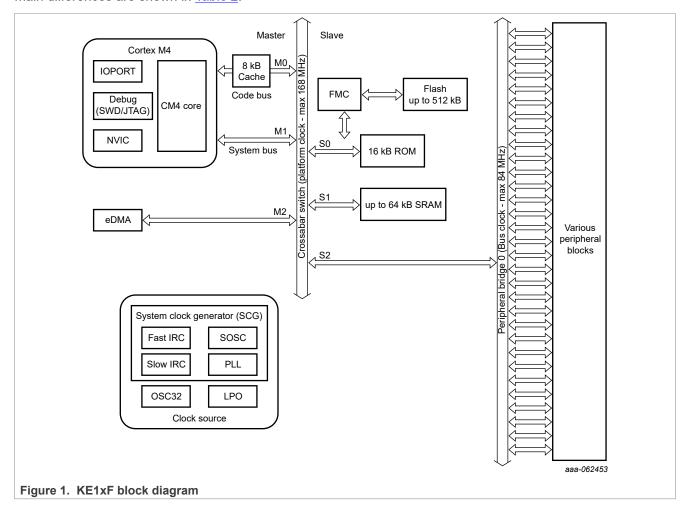

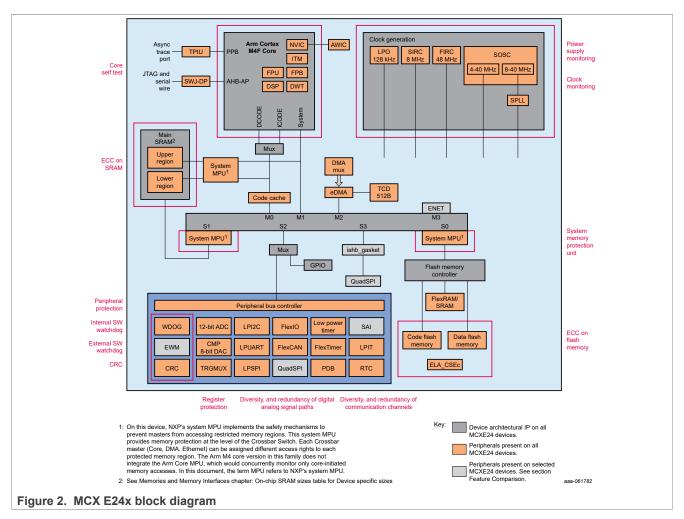

The following figure shows the block diagram for KE1xF. Figure 2 shows the block diagram for MCX E24x. The main differences are shown in Table 2.

## **KE1xF** to MCX E24x Migration Guide

Table 2. Platform differences

| Feature       | KE1xF        | MCX E24x                         |

|---------------|--------------|----------------------------------|

| BootROM       | √ Yes        | √ Yes (with flashloader support) |

| Voltage range | 2.7 to 5.5 V | 2.7 to 5.5 V                     |

| Code cache    | 8 kB         | 4 kB                             |

For a typical KE1xF application, migrating to MCX E24x does not require deep architectural changes at the core or bus levels, because both families are based on Cortex-M4F and share similar XBAR architectures. However, additional adaptation may be needed if the application is updated to leverage new features introduced in MCX E24x, such as the EdgeLock Accelerator (CSEC) security module, code cache, QSPI, or advanced clock/power domains.

## 4 Memory and OTA

The following table shows an extended comparison between the different memories and their interfaces for KE1xF and MCX E24x.

KE1xF to MCX E24x Migration Guide

Table 3. Memory general differences

| Feature                                | KE1xF                                                                                                                 | MCX E24x                                                                                                                                     |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Program flash memory                   | 256 to 512 kB                                                                                                         | 512 kB to 2 MB                                                                                                                               |

| FlexMemory                             | 64 kB                                                                                                                 | Up to 64 kB                                                                                                                                  |

| Data flash                             | Up to 64 kB                                                                                                           | Up to 64 kB                                                                                                                                  |

| Flash memory controller cache          | Single speculative prefetch buffer                                                                                    | Single speculative prefetch buffer                                                                                                           |

| Random-Access Memory (RAM)             | Up to 64 kB                                                                                                           | 64 kB to 256 kB                                                                                                                              |

| FlexRAM (also available as system RAM) | Up to 4 kB, used with FlexNVM for EEPROM emulation                                                                    | 4 kB                                                                                                                                         |

| Low-leakage stand-by memory            | <b>X</b> No                                                                                                           | RAM retained in all modes                                                                                                                    |

| QuadSPI (external memory interface)    | <b>X</b> No                                                                                                           | Supports SDR and HyperRAM modes with up to 4 and 8 bidirectional data lines, respectively                                                    |

| Error correcting code                  | √ Yes                                                                                                                 | ∜ Yes                                                                                                                                        |

| Cache                                  | 8 kB I/D                                                                                                              | 4 kB                                                                                                                                         |

| EEPROM emulated by FlexRAM             | Up to 4 kB EEPROM emulated using up to 32 kB FlexNVM with FlexRAM as the EEPROM buffer (SW-configurable partitioning) | 4 kB EEPROM supported via 64 kB D-<br>flash with FlexRAM as the EEPROM<br>buffer; the remaining D-flash can be<br>used as data/program flash |

| ОТА                                    | Some derivatives support it through MCUBoot                                                                           | Supported via MCUBoot for safe OTA updates                                                                                                   |

There are significant changes in memory architecture between the KE1xF and MCX E24x devices. The following sections describe the most important features and points in detail.

## 4.1 RAM

The MCX E24x family offers a significant improvement in the available RAM compared to the KE1xF family. While KE1xF devices include up to 64 kB of RAM, the MCX E24x devices scale from 64 kB up to 256 kB, depending on the derivative. This extended RAM enables more complex applications and supports use cases requiring higher data buffering, such as networking stacks, graphics, or edge processing. Additionally, both families feature 4 kB of FlexRAM, primarily intended for EEPROM emulation, which can also be repurposed as system RAM if the EEPROM function is not used. The increased RAM in the MCX E24x devices is a key differentiator and allows developers to consolidate functionality previously distributed across multiple MCUs.

## 4.1.1 Considerations for migrating to MCX E24x

When migrating from KE1xF to MCX E24x, account for the following key considerations regarding the RAM architecture:

- RAM size and distribution: MCX E24x offers significantly more RAM (up to 256 kB) compared to KE1xF (up to 64 kB). However, this memory is distributed across multiple blocks, which may require linker script adjustments and code/data relocation planning during migration.

- FlexRAM usage: While both families support FlexRAM, its configuration and integration differ. On KE1xF, FlexRAM is more tightly coupled with FlexNVM for EEPROM emulation, whereas on MCX E24x, FlexRAM can be more flexibly configured for system RAM or EEPROM backup. Developers should carefully verify how the EEPROM emulation is handled and adjust the initialization code, if needed.

**KE1xF** to MCX E24x Migration Guide

• Stand-by memory retention: MCX E24x includes low-leakage stand-by memory retained across low-power modes, which is limited or absent in KE1xF. Applications relying on RAM retention across deep sleep benefit from this, but they may require updates to power-management strategies.

- Cache architecture: KE1xF includes an explicit 8 kB instruction/data cache, whereas MCX E24x provides 4 kB. This can affect performance for memory-intensive applications and optimization may be needed when migrating timing-critical code.

- Toolchain and SDK differences: RAM layout and memory definitions differ between the MCUXpresso SDK for KE1xF and MCX E24x. The migration typically requires updating the linker scripts, startup code, and memory protection configuration (MPU).

A careful review of the MCX E24x reference manual and SDK memory configuration examples is essential to ensure a smooth transition, particularly when working with low-power features or EEPROM emulation.

#### 4.2 Flash

The flash memory architecture differs moderately between KE1xF and MCX E24x, with MCX E24x offering more capacity and expanded flexibility for OTA and EEPROM use cases.

The KE1xF family provides 256 kB to 512 kB of program flash, backed by an 8 kB cache and FlexMemory support, including FlexNVM and FlexRAM. This allows applications to emulate EEPROM in a reliable and configurable manner, suitable for parameters or runtime configuration storage.

The MCX E24x family extends the flash capacity from 512 kB up to 2 MB, while also retaining FlexMemory, including up to 64 kB of FlexNVM and 4 kB of FlexRAM. The flash cache is 4 kB, slightly smaller than KE1xF, but combined with a more advanced memory controller.

## 4.2.1 Considerations for migrating to MCX E24x

When migrating from KE1xF to MCX E24x, consider the following aspects of the flash architecture:

- Flash size and organization: While KE1xF devices offer between 256 kB and 512 kB of P-flash, MCX E24x devices extend this range up to 2 MB, providing more room for application code, data, and Over-The-Air (OTA) capabilities. This expanded space allows for more flexibility but it may also impact flash partitioning and memory map configuration. MCX E24x introduces the Read-While-Write (RWW) capability, allowing the application to execute code from one flash bank while programming another. This feature is essential to support safe Over-The-Air (OTA) updates, as it enables seamless firmware download and installation without interrupting normal application execution.

- FlexNVM and FlexRAM usage: Both families support 64 kB of FlexNVM and 4 kB of FlexRAM. However, their behavior and configuration may differ in terms of EEPROM emulation or partitioning options. Applications that rely on EEPROM emulation should verify the compatibility and reconfigure the FlexNVM partition as needed on MCX E24x.

- Cache configuration: KE1xF features an 8 kB cache, whereas MCX E24x provides 4 kB. While this is sufficient for most applications, performance-critical code sections must be reviewed and optimized for the new cache size.

- Flash driver migration considerations: Both KE1xF and MCX E24x families use the MCUXpresso SDK flash driver, meaning that the core flash API (such as initialization, sector erase, program, and verify operations) remains consistent across both families. Developers migrating applications from KE1xF will find the flash interface largely compatible, with minimal or no changes required at the API level. Differences may exist in the peripheral base addresses and flash layout, but the overall software migration is straightforward. However, the MCX E24x family introduces new use cases, enabled by the additional boot and memory management features. MCX E24x supports integration with the open-source MCUBoot second-stage bootloader. This enables more advanced firmware-update mechanisms, including Over-The-Air (OTA) updates with support for dual image slots and image validation before activation. The MCUXpresso SDK for MCX E24x includes a preconfigured example (ota mcuboot basic) that demonstrates how to configure and manage the OTA-

KE1xF to MCX E24x Migration Guide

capable flash partitions. This capability is not natively supported on KE1xF, where any firmware update mechanism must be fully implemented by the user application. As a result, while the flash driver APIs are similar, developers migrating to MCX E24x must also consider the opportunity to adopt a more robust and secure firmware update strategy using MCUBoot, which may require adaptations in memory layout, linker scripts, and boot flow.

Flash performance considerations: Both KE1xF and MCX E24x feature flash memory designed for read

access at system clock speeds. However, to maintain reliable operation and optimal performance, the flash

controller must be configured with appropriate wait states depending on the system clock frequency. On MCX

E24x, this is managed via the Flash Memory Controller (FMC), which dynamically adjusts access latency.

MCX E24x integrates a prefetch buffer mechanism within the FMC that improves performance by reducing

wait states during instruction fetches and data reads.

#### 4.2.2 KE1xF versus MCX E24x reliability and time specifications

Table 4. Endurance and performance

| Feature                                   | KE1xF | MCX E24x                                                       | Units  |

|-------------------------------------------|-------|----------------------------------------------------------------|--------|

| Data retention up to 1 K cycles           | 20    | 20                                                             | Years  |

| Cycling endurance (min)                   | 10 K  | 10 K                                                           | Cycles |

| Erase flash block execution time (512 kB) | 435   | 250                                                            | ms     |

| Program section execution time (1 kB)     | 5     | 5                                                              | ms     |

| Erase all blocks execution time           | 500   | 400/700/1400 (MCX E245/E246/E247 flash size: 512 kB/1 MB/2 MB) | ms     |

## 4.3 Over-The-Air (OTA)

The Over-The-Air (OTA) firmware update capability is a key feature for modern embedded systems that require remote firmware updates, especially in automotive and IoT applications. The KE1xF family does not natively support OTA-specific hardware features, meaning that any OTA mechanism must be fully implemented in software by the application developer. The MCX E24x family offers a structured solution using a two-stage bootloader approach:

- 1. ROM bootloader (first stage): Provides basic functionality, such as code signature validation and factory image management.

- 2. MCUBoot (second stage): Integrated in the MCUXpresso SDK, it handles a full OTA flow with signed image verification and flash partitioning into primary/secondary slots.

This feature does not rely on a hardware A/B flash swap. Instead, MCX E24x uses a software-driven dual-slot partitioning strategy implemented via MCUBoot (included in the MCUXpresso SDK).

Table 5. OTA features

| able of a fix founding     |                          |                                           |  |

|----------------------------|--------------------------|-------------------------------------------|--|

| OTA feature                | KE1xF                    | MCX E24x                                  |  |

| A/B swap                   | <b>X</b> No              | X No natively (supported through MCUBoot) |  |

| Number of flash partitions | 1 main, optional D-flash | 2 (or more) via partitioning              |  |

| Read while write           | Limited support          | Enhanced support                          |  |

| Image verification         | By application           | EdgeLock Accelerator (CSEC) functions     |  |

**KE1xF** to MCX E24x Migration Guide

Table 5. OTA features...continued

| OTA feature                             | KE1xF             | MCX E24x                                 |  |

|-----------------------------------------|-------------------|------------------------------------------|--|

| Lockable flash regions                  | Limited via FPROT | Enhanced                                 |  |

| Update while the application is running | Not safe          | Possible (with constraints)              |  |

| Secure boot                             | <b>X</b> No       | EdgeLock Accelerator (CSEC) is supported |  |

## 4.3.1 Considerations for migrating to MCX E24x

When migrating from KE1xF to MCX E24x, you can leverage several improvements in the Over-The-Air (OTA) update capabilities, although they are not natively implemented in the hardware. Unlike KE1xF, which requires a fully custom implementation for features such as dual-image management and update rollback, MCX E24x offers a more modern hardware foundation with better integration possibilities for secure boot, flash partitioning, and secure provisioning tools.

The secure boot mechanisms and cryptographic verification can be integrated easier on MCX E24x using the MCUXpresso Secure Provisioning Tool or Flashloader.

Migrating to MCX E24x requires rethinking the flash layout and linker scripts to accommodate multiple firmware images and version metadata. Support for Position-Independent Code (PIC), secure boot, image verification, and rollback logic must be added at the software level. While this adds complexity, it enables more robust and secure update flows than what is typically feasible on KE1xF.

## 5 Clocking, power management, reset, and boot

This section describes the clocking, power management, reset, and boot.

## 5.1 Clocking architecture

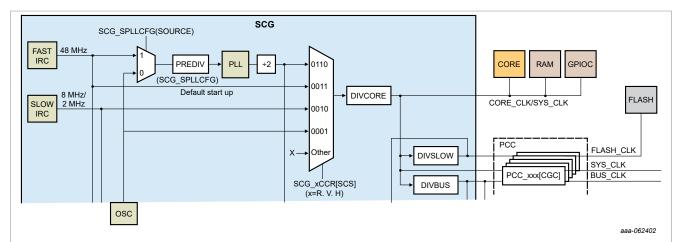

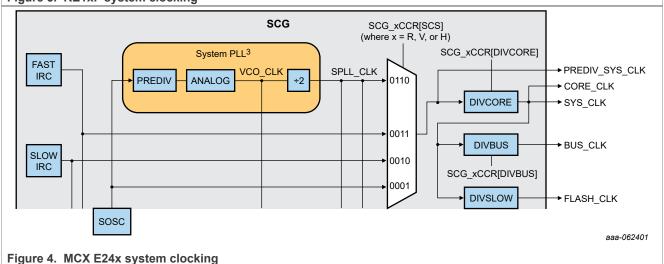

The clocking architecture defines how the microcontroller distributes and manages clock signals across its core and peripherals, impacting both performance and power consumption. Both the KE1xF and MCX E24x platforms use a System Clock Generator (SCG) and Peripheral Clock Controller (PCC) scheme, but the MCX E24x family introduces notable enhancements in configurability and fine-grained control.

KE1xF provides essential clock sources (FIRC, SIRC, SOSC, and SPLL) and allows dynamic switching between them using the SCG. However, its configuration is relatively static and centralized, with limited flexibility per a peripheral domain.

In contrast, MCX E24x significantly improves on this model by introducing a hierarchical and modular clocking architecture. It supports multiple clock roots per subsystem, allowing independent configuration for different groups of peripherals. This is complemented by additional modules such as the Clock Monitor Unit (CMU) for enhanced fault detection and the Clock Control Module (CCM) for managing complex scenarios like low-power transitions or domain-specific clock gating. The MCX E24x platform also supports more extensive use of fractional dividers and more fine-tuned PLL/DIV settings, enabling precise clock tailoring for performance or energy optimization.

These architectural improvements enable the MCX E24x to better support advanced low-power modes, improve startup behavior, and offer greater flexibility in mixed-performance applications.

Table 6. KE1xF and MCX E24x clock sources

| KE1xF           | MCX E24x | Key comments                                           |

|-----------------|----------|--------------------------------------------------------|

| Fast IRC 48 MHz |          | Default clock source after reset in both architectures |

#### KE1xF to MCX E24x Migration Guide

Table 6. KE1xF and MCX E24x clock sources...continued

| KE1xF                | MCX E24x                                          | Key comments                                                                         |

|----------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|

| Slow IRC 8 MHz/2 MHz | Slow IRC 8 MHz                                    | -                                                                                    |

| OSC 4 to 40 MHz      | SOSC 4 to 40 MHz                                  | -                                                                                    |

| PLL up to 50 MHz     | SPLL up to 112 MHz (HSRUN)<br>Up to 160 MHz (RUN) | MCX E24x: VCO frequency up to 320 MHz (KE1xF up to 360 MHz)                          |

| LPO 128 kHz          | LPO 128 kHz                                       | Intended RTC clock source for both architectures. No software trimming is supported. |

Figure 3. KE1xF system clocking

## 5.1.1 Considerations for migrating to MCX E24x

When migrating from KE1xF to MCX E24x, developers must adapt to a more modular and flexible clocking system. While both platforms share a similar System Clock Generator concept with key components like FIRC, SIRC, and SPLL, MCX E24x introduces enhancements in configurability and behavior.

Key differences include additional tuning and trimming capabilities for internal oscillators, a more advanced handling of clock stabilization, and subtle changes in register fields. Although the MCX E24x retains familiar modules, clock sources may behave differently during low-power modes or boot sequences.

**KE1xF** to MCX E24x Migration Guide

Clock initialization and transitions must be reviewed carefully, especially for applications sensitive to oscillator stability or timing precision. The greater flexibility offered by MCX E24x comes with additional responsibility in configuration.

## 5.2 Power management and operating modes

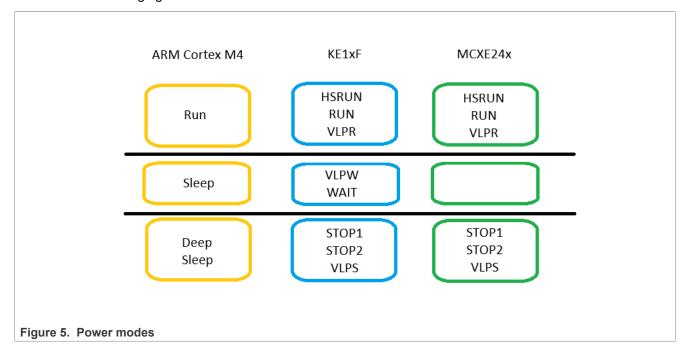

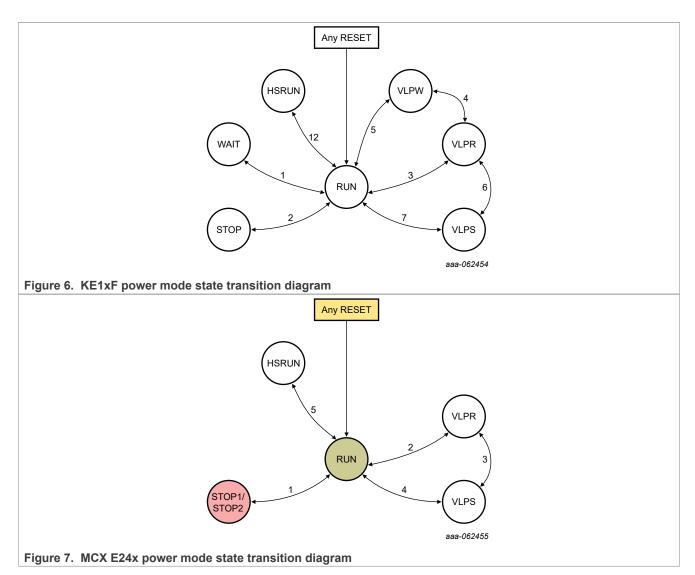

One of the most eye catching differences in the transition from KE1xF to MCX E24x is the number of supported power modes. The implemented power modes in both architectures and their relationship with Cortex M4 are shown in the following figure.

## 5.2.1 Considerations for migrating to MCX E24x

Both KE1xF and MCX E24x devices implement multiple low-power operating modes and follow a similar power mode state machine structure: any reset leads the system back to the Normal Run mode, and the power regulation is active in the RUN and STOP modes. However, a few differences must be considered during migration.

On KE1xF, modes like WAIT, STOP, VLPR, and VLPW are available. VLPR and VLPW modes are frequency-limited and suitable for applications requiring reduced energy consumption while keeping the core active.

On MCX E24x, while modes such as RUN, STOP, and VLPR are still present, some intermediate modes are removed and VLPR is still frequency-limited. The power mode control is more tightly integrated with enhanced wake-up and retention features, although the power-regulation concept remains consistent (active in RUN and STOP modes).

Because of these similarities, transitioning existing low-power applications from KE1xF to MCX E24x is conceptually straightforward.

## KE1xF to MCX E24x Migration Guide

The following table lists the modules available during the deep sleep mode.

Table 7. KE1xF and MCX E24x module operation in low-power mode (deep sleep)

| Modules    | KE1xF VLPS  | MCX E24x VLPS |

|------------|-------------|---------------|

| Core, NVIC | Static      | OFF           |

| LVD/LVR    | LVR active  | LVR active    |

| DMA        | Async Op    | Async Op      |

| Watchdog   | FF          | Async Op      |

| LPO        | FF          | FF            |

| SIRC       | Optional ON | FF            |

| FIRC       | Optional ON | OFF           |

| SOSC       | Optional ON | OFF           |

| LPUART     | Async Op    | Async Op      |

| LPSPI      | Async Op    | Async Op      |

AN14806

All information provided in this document is subject to legal disclaimers.

KE1xF to MCX E24x Migration Guide

Table 7. KE1xF and MCX E24x module operation in low-power mode (deep sleep)...continued

| Modules | KE1xF VLPS      | MCX E24x VLPS   |

|---------|-----------------|-----------------|

| LPI2C   | Async Op        | Async Op        |

| FlexIO  | Async Op        | OFF             |

| CAN     | Wakeup          | OFF             |

| FTM     | Static          | OFF             |

| LPIT    | Async Op        | Async Op        |

| RTC     | Async Op        | FF              |

| CRC     | Static          | OFF             |

| CMP     | LS compare only | LS compare only |

| ADC     | FF              | OFF             |

The legend for the above table is the following:

- \*FF: Full functionality

- \*\*Async Op: Fully functional with alternate clock source

- \*\*\*Static: Module register states and associated memories are retained

#### 5.3 Reset and boot

Both KE1xF and MCX E24x families implement multiple types of reset to ensure reliable system startup and fault recovery. These resets are typically triggered by power conditions, external signals, software requests, or internal system events. While the core concept remains similar across both platforms, the underlying reset sources and their handling mechanisms may slightly differ.

The following table summarizes the primary reset sources available on each platform.

Table 8. KE1xF and MCX E24x reset sources

| Event type     | KE1xF                                                                             | MCX E24x                          |  |

|----------------|-----------------------------------------------------------------------------------|-----------------------------------|--|

| Power-on reset | Power supply is initially applied                                                 | Power supply is initially applied |  |

|                | Supply voltage drops below VPOR                                                   | Supply voltage drops below VPOR   |  |

| System reset   | Asserting RESET_B pin                                                             |                                   |  |

|                | WDOG                                                                              |                                   |  |

|                | Software reset Loss of clock Loss of lock                                         |                                   |  |

|                |                                                                                   |                                   |  |

|                |                                                                                   |                                   |  |

|                | Core LOCKUP                                                                       |                                   |  |

|                | Core attempts to enter the Stop mode, but not all modules acknowledge the request |                                   |  |

| Debug reset    | MDM-AP (reset via JTAG/SWD) JTAG module                                           |                                   |  |

|                |                                                                                   |                                   |  |

**Note:** Many reset functions for the chip as well as the reset sequence monitoring are managed by the Reset Control Module (RCM) in both families.

**KE1xF** to MCX E24x Migration Guide

## 5.3.1 Secure installer for unsecure manufacturing lines

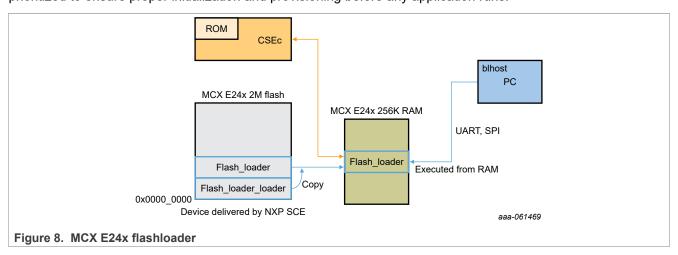

<u>Figure 8</u> illustrates the difference between the KE1xF and MCX E24x flash layouts in the context of OEM factory provisioning using the Flash\_loader. KE1xF devices are delivered with blank flash, whereas MCX E24x devices come preloaded with a one-time Flash\_loader and Flash\_loader\_loader image in the flash memory (starting at address 0x0000 0000), as provided by NXP SCE.

Upon boot, the loader is copied from the flash to the RAM and executed from there. This loader interacts with a host PC (via UART or SPI) using tools like blhost, allowing flash programming and CSEc key provisioning. The setup also requires a boot hold from the factory for testing and IFR locking. The Flash\_loader execution is prioritized to ensure proper initialization and provisioning before any application runs.

#### 5.3.2 MCUBoot support

On the MCX E24x devices, the MCUBoot open-source bootloader is provided as a secondary bootloader to enable the secure firmware boot and update capabilities. It is a widely adopted, vendor-agnostic solution that can work with Zephyr, FreeRTOS, or bare-metal MCUXpresso applications.

#### 5.3.2.1 Key features

The key features are as follows:

- · Authenticated firmware execution

- Only digitally signed images are allowed to run (preventing unauthorized or tampered code)

- · Cryptographic algorithms

- Signing: ECDSA, ED25519, RSA

- Integrity: SHA-256, SHA-512

- Optional encryption: AES

- Crypto libraries: Mbed TLS or TinyCrypt

- · Firmware updates

- UART, USB, or Over-The-Air (OTA) support

- Rollback mechanism in case of a boot failure (not default behavior, configurable)

- Supports direct update strategies

- Partition management; uses predefined flash areas for application images and metadata:

- primary slot (active image)

- secondary slot (update candidate)

- scratch

KE1xF to MCX E24x Migration Guide

## 5.4 Migration considerations

When migrating from the KE1xF platform using the MCUXpresso SDK to the MCX E24x family with MCUBoot integration enabled, consider the following adjustments for boot and image management:

- Image format: The application binary must now be wrapped in a MCUBoot-compatible format, which includes

a header, optional cryptographic signature, and metadata. This packaging can be handled using imgtool.py,

west, or integrated build system steps.

- Signing process: Establish a signing mechanism using a private key (via imgtool or Zephyr's west toolchain).

- Bootloader configuration: Make sure that linker files match the expected layout of MCUBoot (for example, vector table offset).

- Tools: Flashing may now involve MCUBoot-specific tools (blhost) instead of traditional flashing utilities.

## 6 Security

The KE1xF family provides a basic security model focused on flash memory protection and CRC. In contrast, the MCX E24x family introduces a more robust and modern security architecture that aligns with evolving market demands. This includes enhanced features, such as secure boot, key management, and hardware cryptographic acceleration.

This section describes the security features offered by both families and highlights the key differences. It also outlines considerations for a secure migration from KE1xF to MCX E24x.

Table 9. KE1xF and MCX E24x security differences

|                   |              | KE1xF                        | MCX E24x                                                                                     |

|-------------------|--------------|------------------------------|----------------------------------------------------------------------------------------------|

| Security system   |              | <b>X</b> No                  | EdgeLock Accelerator (CSEC)                                                                  |

| Location in SoC   |              | X No                         | EdgeLock Accelerator (CSEC) tightly coupled to flash controller                              |

| Firmware upgradal | ble          | Not natively                 | Not natively - through secure boot                                                           |

| Security ciphers  | Symmetric    | <b>X</b> No                  | AES-128                                                                                      |

|                   | Cipher modes | <b>X</b> No                  | ECB, CBC, and CMAC                                                                           |

|                   | Hash         | Software implementation only | Miyaguchi-Prenell No SHA HW in EdgeLock Accelerator (CSEC), must use software implementation |

| Secure boot       |              | <b>X</b> No                  | Three different modes: parallel boot, sequential boot, strict sequential boot                |

| Random number g   | enerator     | <b>X</b> No                  | TRNG and PRNG                                                                                |

| Attack resistance |              | <b>X</b> No                  | Secure key storage                                                                           |

| Requirement cover | rage         | Basic reliability            | SHE - automotive-grade intermediate security                                                 |

## 6.1 Considerations for migrating to MCX E24x

When migrating from KE1xF to MCX E24x, consider the following key security enhancements:

Transition from CRC to real cryptography: KE1xF relies solely on a CRC module for error detection, which, while suitable for basic integrity checks (IEC 60730), offers no cryptographic security or protection against intentional tampering. MCX E24x integrates the EdgeLock Accelerator (CSEC), enabling hardwareaccelerated AES-128 encryption, CMAC-based authentication, and a true RNG.

KE1xF to MCX E24x Migration Guide

Secure boot and image authenticity: KE1xF lacks a secure boot mechanism and starts executing code immediately. MCX E24x employs a ROM-based secure boot that uses EdgeLock Accelerator (CSEC) to verify signed firmware images before execution. MCX E24x supports multiple secure boot strategies (parallel, sequential, and strict sequential), balancing security and boot latency.

- Firmware update security: Unlike KE1xF, all firmware updates on MCX E24x must be cryptographically signed

and validated before flashing. The system also enforces antirollback through image versioning and key

management, preventing unauthorized downgrades.

- Hardware-enforced key protection and debug lockdown: KE1xF offers no secure key storage. On MCX E24x,

EdgeLock Accelerator (CSEC) provides hardware key slots, including one for the boot MAC key, and prohibits

key use in case of failed authentication or debug detection. This includes the debug interface lockdown and

permanent hardware lock after entering locked life cycle modes.

- Upgrade path and tool support: Adopting MCX E24x requires a transition to NXP's MCUXpresso Secure

Provisioning workflow, including key generation, image signing, and configuration of secure flash regions via

PRINCE/IPED. Developers must be familiar with the partitioning of secure memory regions and secure key life

cycles.

## 7 Safety

The KE1xF family integrates a robust set of IEC 60730 Class B safety features, including comprehensive self-test routines (CPU, flash, RAM, clock, I/O), watchdog timers, CRC engines, and ECC support, all enabled via NXP's safety library.

These capabilities make KE1xF ideal for consumer appliances and general industrial applications where reliable error detection and system integrity are paramount.

The MCX E24x family enhances safety support with compliance to IEC 60730 (class B-certified) and provides features and documentation aligned with IEC 61508 requirements. It is ready for system-level SIL2 certification through NXP's SafeAssure program, offering key safety features such as error-correcting code on flash and SRAM, internal and external watchdogs (WDOG/EWM), system memory protection unit, and cyclic redundancy check module. Software libraries and guidelines are available to support integration in functional safety applications:

- Industrial Structural Core Self-Test (ISCST) library, which is designed to detect permanent faults in the Cortex-M4F core and is qualified to support SIL2 certification.

- Error Reporting Module (ERM) for real-time detection of single-bit faults and an Error Injection Module (EIM) to validate the fault-detection mechanisms.

These additions provide a much stronger foundation for industrial safety applications, especially in systems that must meet the IEC 61508 SIL2 certification requirements.

Table 10. KE1xF and MCX E24x safety-related differences

|                                               | KE1xF                                                         | MCX E24x        |

|-----------------------------------------------|---------------------------------------------------------------|-----------------|

| Memory protection unit                        | NXP proprietary                                               | NXP proprietary |

| Error injection module Error reporting module | <b>X</b> No                                                   | √ Yes (both)    |

| Temperature sensor                            |                                                               | <b>X</b> No     |

| eDMA controller                               | √ Yes                                                         | √ Yes           |

| Clock monitoring units                        | 1 (on-chip clock loss monitoring)                             | 2               |

| Interconnect bus                              | Crossbar switch (AXBS-Lite) and peripheral bridge (AIPS-Lite) |                 |

| External watchdog monitor                     | √ Yes                                                         |                 |

KE1xF to MCX E24x Migration Guide

Table 10. KE1xF and MCX E24x safety-related differences...continued

|   | KE1xF                                               | MCX E24x                                    |

|---|-----------------------------------------------------|---------------------------------------------|

| , | Hardware protection against undervoltage conditions | Hardware-level fault-detection capabilities |

## 8 Timing, Cross Triggering, and ADC

In general industrial applications, such as motor control, power conversion, and high-speed sensor interfacing, tight integration between timing, analog sampling, and event coordination is essential. Key modules like ADC, PDB, FTM, and TRGMUX are commonly used together to implement synchronized control loops and real-time monitoring. This section describes the architectural and functional differences between the KE1xF and MCX E24x families, focusing on how these IP blocks interact to support deterministic timing, cross-triggering mechanisms, and analog signal acquisition in complex industrial systems.

#### 8.1 TRGMUX

The Trigger Multiplexer (TRGMUX) is a central routing IP that enables flexible interconnection of peripheral and timer events without CPU intervention. By selecting and forwarding trigger signals from sources like timers, PWM modules, and ADCs to target peripherals, TRGMUX facilitates precise hardware synchronization in tasks like synchronized sampling, multi-phase motor control, and time-critical event chaining. KE1xF features a two-stage TRGMUX (prestage and main stage), while MCX E24x platforms implement only one stage with up to 72 sources and multiple outputs, ensuring consistent trigger-routing capabilities. This section describes the configuration model, signal mapping, and migration considerations to leverage TRGMUX for deterministic cross-peripheral orchestration on MCX E24x.

Table 11. KE1xF and MCX E24x TRGMUX differences

| TRGMUX                                | KE1xF                    | MCX E24x                   |

|---------------------------------------|--------------------------|----------------------------|

| Internal and external routing options | Inputs:32<br>Outputs:112 | Inputs: 72<br>Outputs: 128 |

#### 8.1.1 Considerations for migrating to MCX E24x

The TRGMUX module on MCX E24x provides a single-stage, centralized trigger routing system that simplifies the configuration compared to the two-stage TRGMUX architecture on KE1xF. While KE1xF uses a prestage (TRGMUX1) to multiplex a limited number of sources into TRGMUX0, MCX E24x consolidates the whole trigger routing into a unified matrix capable of supporting up to 72 input sources with direct mappings to peripheral targets. This not only streamlines the routing logic, but it also expands the range of available trigger sources and destinations. When migrating, review how the triggers are cascaded across both stages on KE1xF and adjust the configurations to leverage the single-stage routing model on MCX E24x, reducing complexity and improving determinism.

#### 8.2 ADC

Analog-to-Digital Converters (ADCs) are essential components in many industrial applications that require precise analog signal sampling, such as motor control, sensor interfacing, or power monitoring. The KE1xF and MCX E24x families integrate SAR-based ADCs with comparable resolution, conversion modes, and hardware trigger support. While the architectural foundations are similar, there are a few implementation differences, such as the internal temperature sensing support. This section describes the key similarities and migration considerations between the ADC modules on both platforms.

KE1xF to MCX E24x Migration Guide

Table 12. KE1xF and MCX E24x ADC differences

| ADC                | KE1xF  | MCX E24x                                                         |

|--------------------|--------|------------------------------------------------------------------|

| Instances/channels |        | ADC_0: 14-32 (following package) ADC_1: 9-32 (following package) |

| Resolution         | 12-bit | 12-bit                                                           |

| Temperature sensor | √ Yes  | <b>X</b> No                                                      |

#### 8.2.1 Considerations for migrating to MCX E24x

When migrating from the KE1xF family to the MCX E24x family, the ADC modules present a largely compatible architecture with a 12-bit resolution, multiple input channels, and similar trigger and conversion capabilities. However, there are two key differences. First, the number of available ADC channels may vary depending on the package, with MCX E24x offering up to 32 input channels per instance, which enable broader analog coverage in certain designs. Second, the KE1xF ADC supports an internal temperature sensor (accessible via a dedicated ADC channel), but this feature is not available on MCX E24x. Applications relying on internal thermal monitoring must therefore use an external temperature sensing solution when migrating.

#### 8.3 FTM

The FlexTimer Module (FTM) is a versatile timer peripheral widely used in industrial and control applications that require precise pulse generation, capture, and modulation. It supports key functionalities such as PWM generation, input capture, output compare, and quadrature decoding. The KE1xF and MCX E24x families integrate FTM modules, enabling applications such as motor control, signal measurement, and actuator control. While the core capabilities remain similar in both families, there are differences in the number of channels, instances, and signal routing options, depending on the specific device and package. The following table summarizes the differences between the FTM on KE1xF and MCX E24x.

Table 13. KE1xF and MCX E24x timer modules differences

| Timer modules          | KE1xF                                                                           | MCX E24x                                              |

|------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------|

| FTM                    |                                                                                 |                                                       |

| Instances and channels | 4 FTMs, 8 channels each                                                         | 4 to 8 FTMs, 8 channels each                          |

| Prescaler              | Prescaler divide-by 1, 2, 4, 8, 16, 32, 64, or 128                              | Prescaler divide-by 1, 2, 4, 8, 16, 32, 64, or 128    |

| Operation modes        | <ul><li>Input capture</li><li>Output compare</li><li>Edge-aligned PWM</li></ul> | Input capture     Output compare     Edge-aligned PWM |

| Fault control          | Up to four fault inputs for global fault control                                | Up to four fault inputs for global fault control      |

## 8.3.1 Considerations for migrating to MCX E24x

While the general functionality of the FTM module is preserved on both platforms, supporting edge-aligned PWM, center-aligned PWM, and input capture modes, there are some differences. The MCX E24x devices may integrate newer or more power-efficient timer implementations. The total number of FTM instances or channels per instance may vary depending on the selected package. The peripheral signal routing via the TRGMUX and pin multiplexing configuration may differ and require changes in software. A careful review of the channel count and TRGMUX mappings is recommended during migration planning to preserve timing behavior consistency.

KE1xF to MCX E24x Migration Guide

#### 8.4 PDB

The Programmable Delay Block (PDB) is a timer-based triggering module designed to coordinate and schedule the operation of analog peripherals, such as ADCs and DACs. It enables precise, hardware-controlled triggering of conversions, often synchronized with timer events, such as PWM edges. This is particularly useful in applications requiring deterministic sampling, such as motor control, power monitoring, or industrial signal processing. The KE1xF and MCX E24x families integrate the PDB module with comparable features, allowing for consistent timing behavior and synchronization across migrations.

The following table indicates the main differences.

Table 14. KE1xF and MCX E24x PDB differences

| Table 1 II TELL and Mex El IX I De anticioned |                                                                |                                                                |

|-----------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| Timer modules                                 | KE1xF                                                          | MCX E24x                                                       |

| PDB                                           |                                                                |                                                                |

| Trigger inputs                                | Up to 15 trigger input sources 1 software trigger source       | Up to 2 trigger input sources 1 software trigger source        |

| ADC hardware trigger                          | Up to 8 configurable PDB channels for the ADC hardware trigger | Up to 8 configurable PDB channels for the ADC hardware trigger |

## 8.4.1 Considerations for migrating to MCX E24x

The Programmable Delay Block (PDB) IP is the same on both KE1xF and MCX E24x: a single module instance offering multiple programmable delay channels, hardware-trigger generation for ADC (and DAC), prescaler/divider configuration, and interrupt/DMA support. The migration is straightforward at the driver level. For example, all key registers (PDBx\_MCR, PDBx\_MOD, PDBx\_CHnC1, PDBx\_IDLY) retain identical offsets and bit fields. However, there are a few platform-specific details:

- Trigger routing: MCX E24x introduces tighter integration with its TRGMUX, allowing PDB triggers to feed directly into the system's flexible trigger mux, whereas KE1xF uses fixed trigger outputs that must be remapped via SIM settings.

- Clock and reset control: On KE1xF, the PDB clock and gating are managed by the SIM module, while MCX E24x uses the PCC. The migrating code must update the clock-enable calls accordingly.

Overall, the application code that configures PDB delays, prescalers, and channel triggers is largely unchanged; only the trigger-routing setup and peripheral-enable calls require an adjustment to match the MCX E24x's SIM→PCC differences and enhanced TRGMUX connectivity.

## 9 Communication modules

This section describes the communication modules.

#### 9.1 Ethernet MAC

The MCX E24x family introduces an integrated 10/100 Mbit/s Ethernet MAC with IEEE-1588 support (available on MCX E247 derivatives), which is a significant enhancement compared to the KE1xF family that lacks native Ethernet capability. This addition enables real-time Ethernet-based industrial communication, supporting precise time synchronization. The presence of the Ethernet MAC makes the MCX E24x more suitable for connected industrial applications, diagnostics, and gateway functionalities, reducing the need for external Ethernet controllers in many use cases.

The following table provides a high-level overview of the MCX E24x Ethernet IP.

KE1xF to MCX E24x Migration Guide

Table 15. Ethernet MAC on MCX E247

| Features                        | MCX E247                                                                                                         |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Ethernet MAC controller         | ENET                                                                                                             |  |

| Supported speeds                | 10/100 Mbit/s                                                                                                    |  |

| TX queues                       | 1                                                                                                                |  |

| RX queues                       | 1                                                                                                                |  |

| Network acceleration features   | CRC generation and checking (Pv4, IPv6, TCP, UDP, ICMP) Additional padding processing Payload alignment (32-bit) |  |

| Address filtering               | MAC address Multicast and unicast, based on a 64-bit hash filter                                                 |  |

| VLAN tags                       | RX frames: detection                                                                                             |  |

| Time stamping (IEEE 1588)       | ∀ Yes                                                                                                            |  |

| Time Sensitive Networking (TSN) | <b>X</b> No                                                                                                      |  |

## 9.1.1 Considerations for migrating to MCX E24x

The KE1xF family does not feature an Ethernet MAC controller, whereas the MCX E247 introduces a 10/100 Mbit/s ENET controller with support for the IEEE 1588 time stamping. This significantly broadens the use cases for industrial and connected applications, enabling real-time Ethernet communication and protocol synchronization. The ENET controller includes basic network acceleration features, such as hardware CRC generation/checking and payload alignment, as well as multicast/unicast address filtering using a 64-bit hash table. However, advanced features such as Time-Sensitive Networking (TSN), VLAN tag insertion/replacement, and layer 3/4 filtering are not supported. VLAN tags are only detected on RX frames. Applications migrating from KE1xF to MCX E247 must therefore take into account the software implementation effort required to fully leverage Ethernet features, particularly for VLAN-based or time-sensitive communication.

#### 9.2 FlexCAN

The KE1xF and MCX E24x families integrate the FlexCAN module, supporting CAN protocol communication in line with ISO 11898-1. Widely used in industrial and automotive systems, FlexCAN offers robust, deterministic messaging for real-time applications. While the core FlexCAN functionality remains similar on both platforms, supporting classical CAN and CAN FD, the MCX E24x introduces enhancements aligned with modern embedded system requirements. These include improved message buffer handling, enhanced filtering capabilities, and tighter integration with the system DMA and interrupt structures. Migrating from KE1xF to MCX E24x ensures continuity of CAN features, but it also offers the opportunity to optimize system performance and safety by leveraging the newer architecture's added features and configurability.

The following table summarizes the differences between FlexCAN on KE1xF and MCX E24x.

Table 16. Changes of the FlexCAN peripheral between KE1xF and MCX E24x

| Features                 | KE1xF                                         | MCX E24x                                           |

|--------------------------|-----------------------------------------------|----------------------------------------------------|

| CAN-FD                   | <b>X</b> No                                   | 3 for MCX E247<br>2 for MCX E246<br>1 for MCX E245 |

| Reception FIFO (RX FIFO) | For CAN 2.0 B frames                          | For CAN 2.0 B frames                               |

| Timestamping timer       | 16 bits wide with optional external time tick | 16 bits wide with optional external time tick      |

AN14806

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**KE1xF** to MCX E24x Migration Guide

Table 16. Changes of the FlexCAN peripheral between KE1xF and MCX E24x...continued

| Features                    | KE1xF              | MCX E24x           |

|-----------------------------|--------------------|--------------------|

| DMA transfers               | Only for CAN 2.0 B | Only for CAN 2.0 B |

| Message buffers             | 16                 | Up to 32           |

| Pretended Networking (PNET) | <b>X</b> No        | Only for CAN 2.0 B |

## 9.2.1 Considerations for migrating to MCX E24x

The migration from KE1xF to MCX E24x offers significant enhancements in CAN capabilities. While the KE1xF platform supports only Classic CAN (CAN 2.0 B), the MCX E24x family introduces the CAN-FD support, with up to three FlexCAN instances on the MCX E247. This enables higher data throughput and more efficient communication for industrial applications requiring frequent or large data exchanges. The number of message buffers increases from 16 to up to 32, allowing for improved buffering and message handling. The timestamping timer remains similar on both platforms, with a 16-bit width and optional external clock input. The DMA transfers and RX FIFO remain limited to CAN 2.0B frames and the Pretended Networking (PNET), useful for reducing power consumption, is now supported on MCX E24x, though still only for Classic CAN. The developers benefit from enhanced scalability and improved CAN peripheral flexibility when migrating to MCX E24x.

#### 9.3 FlexIO

The FlexIO peripheral is a highly configurable serial and parallel interface module designed to emulate a wide variety of communication protocols such as UART, SPI, and I2C. Present on the KE1xF and MCX E24x families, FlexIO provides a flexible alternative to dedicated peripherals, especially useful in industrial applications where customization and scalability are required. Its capability to be reconfigured entirely through software allows developers to adapt to evolving protocol needs without changing hardware.

The following table outlines the key similarities and enhancements brought by the MCX E24x implementation compared to KE1xF.

Table 17. FlexIO differences

| Features                    | KE1xF | MCX E24x |

|-----------------------------|-------|----------|

| Number of pins              | 8     | 8        |

| Number of timers            | 4     | 4        |

| Number of shifter registers | 4     | 4        |

| Number of bits in counter   | 16    | 16       |

| Interrupt request           | √ Yes | √ Yes    |

| DMA request                 | √ Yes | √ Yes    |

Table 18. FlexIO protocol support

| Protocol | KE1xF | MCX E24x |  |

|----------|-------|----------|--|

| UART     | √ Yes | ∀ Yes    |  |

| I2C      | √ Yes | √ Yes    |  |

| SPI      | √ Yes | √ Yes    |  |

| 128      | √ Yes | ∀ Yes    |  |

| PWM      | √ Yes | ∀ Yes    |  |

**KE1xF** to MCX E24x Migration Guide

## 9.3.1 Considerations for migrating to MCX E24x

The FlexIO peripheral on MCX E24x devices provides a feature parity with KE1xF in terms of pin count, number of shifters, timers, and supported protocols. Both platforms support the emulation of UART, I2C, SPI, I2S, and PWM protocols through software configuration. As such, migrating FlexIO-based implementations from KE1xF to MCX E24x is straightforward, with no significant architectural or capability differences. Developers can reuse their existing FlexIO logic while benefiting from the enhanced peripheral integration and toolchain support of the MCX E24x family.

#### 9.4 QuadSPI

Although QuadSPI (QSPI) is a communication protocol, its main use case is as a memory interface, providing greater possibilities to store and execute code from an external memory connected. The table below shows the main differences.

Table 19. KE1xF and MCX E247 QSPI differences

| Feature                      | KE1xF       | MCX E247                                     |

|------------------------------|-------------|----------------------------------------------|

| QSPI max communication clock | <b>X</b> No | Side A: up to 80 MHz<br>Side B: up to 20 MHz |

| Data lines                   |             | 4 for SDR and 8 for HyperRAM (bidirectional) |

| SDR support                  |             | √ Yes                                        |

| DDR support                  |             | √ Yes: Only side B                           |

| AHB access read/write        |             | √ Yes/√ Yes                                  |

| AHB buffer                   |             | 1 kB                                         |

| QSPI and ENET simultaneously |             | √ Yes                                        |

## 9.4.1 Considerations for migrating to MCX E24x

MCX E247 introduces a versatile QuadSPI module that significantly enhances external memory interfacing capabilities compared to the KE1xF family, which lacks such a peripheral. The MCX E247 QuadSPI supports both the SDR and DDR modes, with up to four data lines for standard SPI and 8 lines for the HyperRAM in a bidirectional mode. The interface provides two sides: side A supports clock frequencies up to 80 MHz, while side B operates at up to 20 MHz with a DDR capability. The QuadSPI interface allows AHB read and write access with a 1 kB internal buffer, offering efficient data transactions between the processor and external memory. QuadSPI can operate simultaneously with the Ethernet and SAI modules when the external voltage is within  $3.3 \text{ V} \pm 10 \text{ \%}$ , ensuring reliable communication across these high-speed peripherals.

#### 9.5 UART/LIN

The LPUART module includes registers to control the baud rate, select options, report status, and store transmit/receive data. Access to an address outside the valid memory map generates a bus error. The LPUART supports full-duplex, asynchronous, NRZ serial communication and comprises a baud rate generator, a transmitter, and a receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. The following table describes each block of the LPUART module.

Table 20. LPUART functional blocks

| Feature     | KE1xF | MCX E24x |  |  |

|-------------|-------|----------|--|--|

| LIN support | ∀ Yes | ✓ Yes    |  |  |

**KE1xF** to MCX E24x Migration Guide

Table 20. LPUART functional blocks...continued

| Feature             | KE1xF       | MCX E24x |

|---------------------|-------------|----------|

| LIN master          | <b>X</b> No | ✓ Yes    |

| LIN slave           | <b>X</b> No | √ Yes    |

| Autosynchronization | √ Yes       | ✓ Yes    |

| RXFIFO              | 4 words     | 4 words  |

| TXFIFO              | 4 words     | 4 words  |

| Parity              | Even/odd    | Even/odd |

| DMA support         | √ Yes       | √ Yes    |

| Number of instances | 3           | 3        |

## 9.5.1 Considerations for migrating to MCX E24x

When migrating from KE1xF to the MCX E24x family, the LPUART module maintains a similar structure, with three instances, four-word TX and RX FIFOs, support for even and odd parity, and DMA support. However, the MCX E24x family introduces extended functionality, most notably the native support for both the LIN master and LIN slave modes, which are not fully supported on KE1xF (only basic LIN communication primitives are available). Automatic resynchronization is supported on both families, helping to maintain communication robustness in systems subject to clock drift. Overall, the enhancements in MCX E24x make the LPUART module more capable for serial communication in applications such as automotive or industrial systems requiring full LIN support.

## 9.6 SPI

The LPSPI is a low-power Serial Peripheral Interface (SPI) module that supports an efficient interface to an SPI bus, either as a master and/or as a slave.

Table 21. LPSPI features

| Feature          | KE1xF   | MCX E24X |  |

|------------------|---------|----------|--|

| Word size        | 32 bits | 32 bits  |  |

| Slave operation  | √ Yes   | √ Yes    |  |

| Master operation | ✓ Yes   | ✓ Yes    |  |

| DMA              | ✓ Yes   | √ Yes    |  |

| Command/transmit | 4 words | 4 words  |  |

| Receive FIFO     | 4 words | 4 words  |  |

## 9.6.1 Considerations for migrating to MCX E24x

The SPI modules on the KE1xF and MCX E24x families are very similar, ensuring a smooth migration path. Both families support master and slave modes, DMA for data transfers, and 32-bit word size. The command/transmit and receive FIFOs are four words deep in both cases, offering consistent buffering capabilities. As the register structure and core functionalities remain aligned, software migration typically requires minimal changes. Review instance-specific details, such as pin multiplexing and clock sources, to ensure full compatibility on the MCX E24x platform.

KE1xF to MCX E24x Migration Guide

## 9.7 LPI2C

LPI2C is a low-power Inter-Integrated Circuit (I2C) module that supports an efficient interface to an I2C bus as a master and/or as a slave.

- The LPI2C implements logic support for the standard-mode, fast-mode plus, and ultrafast modes

of operation.

- The LPI2C is designed to use little CPU overhead, with the DMA offloading of FIFO register accesses.

The LPI2C module also complies with the System Management Bus (SMBus) specification, version 2. The SMBus is a single-ended, simple, two-wire bus, which is typically used for low-bandwidth communications.

Table 22. LPI2C features

| Feature                                   | KE1xF   | MCX E24x |  |

|-------------------------------------------|---------|----------|--|

| I2C max communication speed (slave mode)  | 3.4 MHz | 3.4 MHz  |  |

| I2C max communication speed (master mode) | 5 MHz   | 5 MHz    |  |

| SMBus support                             | √ Yes   | √ Yes    |  |

| RXFIFO                                    | 4 words | 4 words  |  |

| TXFIFO                                    | 4 words | 4 words  |  |

| DMA support                               | ∀ Yes   | √ Yes    |  |

| Number of instances                       | 2       | 3        |  |

#### 9.7.1 Considerations for migrating to MCX E24x

When migrating from the KE1xF family to the MCX E24x series, the LPI2C module offers improved communication performance and enhanced flexibility. MCX E24x supports higher I2C communication speeds (up to 12 MHz in both the master and slave modes) when compared to the 5 MHz maximum supported by KE1xF. This allows faster data transfers, particularly beneficial in applications requiring high-speed sensor or peripheral communication. Both families support the SMBus protocols and provide RX and TX FIFOs of four words each, along with DMA support for efficient data handling. The MCX E24x family also increases the number of LPI2C instances from two (on KE1xF) to three, enabling more simultaneous I2C connections. These improvements can reduce communication bottlenecks and allow for more complex and scalable designs.

#### 9.8 SAI

The Synchronous Audio Interface (SAI) module provides an interface that supports full-duplex serial interfaces with frame synchronization, different protocol support (I2S, AC97, TDM), and codec/DSP interfaces.

Table 23. SAI features

| Feature                           | KE1xF       | MCX E247                         |  |  |

|-----------------------------------|-------------|----------------------------------|--|--|

| Word size                         | <b>X</b> No | Between 8 and 32 bits            |  |  |

| Number of communications channels |             | 4 of SAI0 and 1 of SAI1          |  |  |

| Frame synchronization             |             | I2S/AC97/TDM/Codec-IF/DSP-IF/TDM |  |  |

| DMA                               |             | ✓ Yes                            |  |  |

| TX FIFO size                      |             | 8 x 32-bit                       |  |  |

| Maximum frame size per data line  |             | 16 words                         |  |  |

KE1xF to MCX E24x Migration Guide

Table 23. SAI features...continued

| Feature                   | KE1xF | MCX E247 |

|---------------------------|-------|----------|

| Working in low-power mode |       | OFF      |

#### 9.8.1 Considerations for migrating to MCX E24x

MCX E247 has a significantly enhanced Serial Audio Interface (SAI) peripheral. Unlike the KE1xF, which lacks an SAI module, the MCX E247 includes two SAI modules. SAI0 has four communication channels and SAI1 has one channel, offering flexible audio interface options for industrial and multimedia applications. It supports word sizes configurable from 8 to 32 bits and it can synchronize over various interface protocols, such as I2S, AC97, codec-IF, DSP-IF, and TDM. The SAI includes DMA support and an 8×32-bit FIFO per a transmit channel, allowing robust buffering and low CPU load during streaming. The maximum frame size per a data line is 16 words. While the SAI is not currently functional in low-power modes, its full DMA-based throughput and configurable frame synchronization make it a strong addition to the MCX E247. Update your audio driver initialization and buffer-management logic to align with the deeper FIFO and wider protocol support.

## 10 Pin management and characteristics

The KE1xF and MCX E24x families support 64 LQFP and 100 LQFP packages with similar pinouts and signal assignments. This ensures a smooth hardware migration path with no need for PCB redesign when upgrading between equivalent LQFP packages.

However, while the pinout remains similar, some peripheral functions (for example, QSPI and Ethernet) may differ between the two families. Certain pins may be multiplexed differently or reserved for peripherals not present on KE1xF. For this reason, a detailed pinout comparison is shown in <u>Table 24</u> and <u>Table 25</u> to help evaluate function-level compatibility in your specific use case.

**Note:** The ALT1 column is omitted, as it is identical on both devices.

Table 24. LQFP100 pinout comparison

| 100 LQFP | Pin name | Default                                             | ALT0                     | ALT2                                                    | ALT3                          | ALT4      | ALT5                                | ALT6    | ALT7        |

|----------|----------|-----------------------------------------------------|--------------------------|---------------------------------------------------------|-------------------------------|-----------|-------------------------------------|---------|-------------|

| 1        | PTE16    | DISABLED                                            | -                        | LPUART1_<br>RTS <sup>[1]</sup>                          | LPSPI2_<br>SIN <sup>[1]</sup> | FTM2_CH7  | FTM4<br>FLT0 <sup>[†]</sup>         | FXIO_D3 | TRGMUX_OUT7 |

| 2        | PTE15    | DISABLED                                            | -                        | LPUART1_<br>CTS <sup>[1]</sup>                          | LPSPI2_<br>SCK <sup>[1]</sup> | FTM2_CH6  | FTM4<br>FLT1 <sup>[1]</sup>         | FXIO_D2 | TRGMUX_OUT6 |

| 3        | PTD1     | ADC2_SE1 <sup>[2]</sup><br>DISABLED <sup>[1]</sup>  | ADC2_SE1 <sup>[2]</sup>  | FTM0_CH3                                                | LPSPI1_<br>SIN                | FTM2_CH1  | SAI0_<br>MCLK <sup>[1]</sup>        | FXIO_D1 | TRGMUX_OUT2 |

| 4        | PTD0     | ADC2_SE0 <sup>[2]</sup><br>DISABLED <sup>[1]</sup>  | ADC2_SE0 <sup>[2]</sup>  | FTM0_CH2                                                | LPSPI1_<br>SCK                | FTM2_CH0  | ETM_<br>TRACE_<br>D0 <sup>[1]</sup> | FXIO_D0 | TRGMUX_OUT1 |

| 5        | PTE11    | ADC2_SE13 <sup>[2]</sup><br>DISABLED <sup>[1]</sup> | ADC2_SE13 <sup>[2]</sup> | PWT_IN1 <sup>[2]</sup><br>LPSPI2<br>PCS0 <sup>[1]</sup> | LPTMR0_<br>ALT1               | FTM2_CH5  | -                                   | FXIO_D5 | TRGMUX_OUT5 |