# AN14709

# **Power Management Hardware for the KW47**

Rev. 2.0 — 10 December 2025

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14709, power management, KW47, LDO, DC-DC                                                                                                                                                                                                                                                                                                                                |

| Abstract    | This application note describes the usage of the different modules dedicated to power management in the KW47 microcontroller. The KW47 integrates a DC-DC buck converter, a couple of low-dropout regulators, and a programmable solid-state switch to turn on/off the KW47 power domains. Also, the KW47 integrates independent power domains for each group of hardware. |

**Power Management Hardware for the KW47**

# 1 Introduction

This application note describes the usage of the different modules dedicated to power management in the KW47 microcontroller. The KW47 integrates a DC-DC buck converter, a couple of low-dropout regulators, and a programmable solid-state switch to turn on/off the KW47 power domains. Also, the KW47 integrates independent power domains for each group of hardware. For example, there is a dedicated power domain for the reset hardware, general-purpose input/output (GPIOs), and analog. The dedicated hardware for power management and the option to use different voltages for each power domain give flexibility. This helps to meet most of the application requirements in wireless applications.

# 2 KW47 dower domains

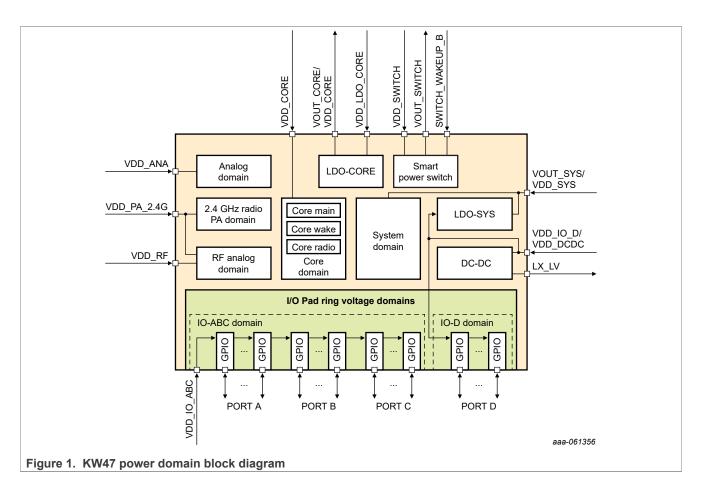

The KW47 microcontroller has independent power domains, which are grouped as follows:

- VDD\_SWITCH: Represents the input voltage for the smart power switch (VBAT). This power domain supplies the voltage to the internal hardware associated with the VBAT.

- VDD\_ANA: Drives the analog peripherals on this microcontroller, such as the analog-to-digital converter (ADC) and the VREF regulator.

- VDD\_IO\_ABC: Drives the voltage on the PTA, PTB, and PTC pins.

- VDD\_IO\_D/VDD\_DCDC: Drives the voltage on the PTD pins, including the reset system. It is also shared with the inputs for the DC-DC Buck converter, and for the LDO\_SYS regulator.

- VDD\_SYS: Manages the power delivered to some peripherals on this chip. <u>Table 1</u> shows the list of peripherals, which VDD\_SYS domain supplies.

- VDD\_CORE: The core-power domain supplies to the main core processor and some peripherals on this chip.

This power domain is split into core main, core wake, and core radio domains for an independent power mode

selection. The voltage on this power domain is associated with the maximum clocking frequency at which this

device can operate. <a href="Italie-1">Italie 1</a> shows the list of peripherals, which VDD\_CORE domain supplies.

- VDD\_RF: The RF power domain provides the voltage that drives the radio analog system in this chip and the 32 MHz-OSC oscillator.

- VDD\_PA\_2.4G: Drives the voltage for the radio power amplifier. The VDD\_PA\_2.4G voltage can be provided internally from the VDD\_RF power domain.

# **Power Management Hardware for the KW47**

# 2.1 Peripherals supplied by each power domain

Table 1 shows the KW47 power domains and their associated on-chip peripherals, which these domains supply.

Table 1. Peripheral power domain assignments

| Power domain  | Voltage supply                                         | Modules associated with the power domain                                                                                                                                                                                                                                                                                             |

|---------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog domain | VDD_ANA and VSS_ANA                                    | ADC0 and VREF0                                                                                                                                                                                                                                                                                                                       |

| Core main     | VDD_CORE_MAIN (Tied internally to VDD_ CORE pin)       | CM33, DSP, FPU, MPU, NVIC, SYSTICK, TZM, DAP, DWT, ITM, TPIU, AXBS0, eDMA0, MSCM, SMSCM, PRBRIGDE2, TRGMUX, MRCC, SFA0, CACHE-CODE, FLASH, ROM-BOOT, CRC0, EdgeLock Secure Enclave, TRDC0, LPIT0, TPM1, FlexCAN0, FlexCAN1, FlexIO0, LPI2C 1, I3C0, LPSPI 1, LPUART 1, GPIOB, GPIOC, SEMA42, PORTB, PORTC, ADC0, VREF0, and TCM- SYS |

| Core wake     | VDD_CORE_WAKE<br>(Tied internally to VDD_<br>CORE pin) | SWD, CMC0, EWM0, WDOG0, WDOG1, FRO-6M, MRCC, SCG0, TSTMR0, TPM0, LPI2C0, LPUART0, LPSPI0, GPIOA, PORTA, LPCMP0, and LPCMP1                                                                                                                                                                                                           |

| Core radio    | VDD_CORE_2.4G<br>(Tied internally to VDD_<br>CORE pin) | RF-2.4G, NBU, RF-FMU, RF-FRO192M, TPM2, and LPUART2                                                                                                                                                                                                                                                                                  |

| IO-ABC        | VDD_IO_ABC                                             | PORTA, PORTB, PORTC, LPCMP0, and LPCMP1                                                                                                                                                                                                                                                                                              |

| IO-D          | VDD_IO_D                                               | LDO-SYS, DC-DC, and PORTD                                                                                                                                                                                                                                                                                                            |

# **Power Management Hardware for the KW47**

Table 1. Peripheral power domain assignments...continued

| Power domain       | Voltage supply                                           | Modules associated with the power domain                                                                                            |

|--------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Smart power switch | VDD_SWITCH                                               | Power switch, RAM LDO, FRO16K, and power switch controller                                                                          |

| System             | VDD_SYS                                                  | RFMC0, Bluetooth LE LL (from MBU), WUU0, FRO192M, LPTMR0/1, SPC0, OSC-RTC, FRO32K, REGFILE0/1 – RTC, TAMPER, RTC0, GPIOD, and PORTD |

| RF analog          | VDD_RF                                                   | OSC-RF and RF-2.4G                                                                                                                  |

| 2.4 GHz radio PA   | VPA_2.4G                                                 | RF-PA-2.4G                                                                                                                          |

| VDD_DCDC           | Direct current to direct current converter – Low voltage | DCDC-LV                                                                                                                             |

The KW47 includes hardware dedicated to power management embedded in the chip. <u>Table 2</u> shows a brief description of the regulators available on this MCU.

Table 2. On-chip regulator descriptor

| On-chip regulator | Voltage supply | Description                                                                                                                                                                                                                                                                                                           |

|-------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC-DC             | VDD_DCDC       | The DC-DC can be used to power the LDO-SYS, I/O ring, RF analog, and 2.4 GHz radio power amplifier. It also powers the external components. The user must consider that the total load current expected never exceeds the maximum DC-DC current capacity. The DC-DC current capacity depends on the DC-DC Drive mode. |

| LDO-CORE          | VDD_LDO_CORE   | The LDO-CORE can be used to power the VDD_CORE domain. It is not intended to supply external loads.                                                                                                                                                                                                                   |

| LDO-SYS           | VDD_IO_D       | The LDO-SYS can be used to power the VDD_SYS domain. It is not intended to supply external loads.                                                                                                                                                                                                                     |

Table 3 shows the supported voltage options for each on-chip regulator.

Table 3. On-chip regulator voltages

| On-chip regulator | Voltage options                         |

|-------------------|-----------------------------------------|

| DC-DC             | 1.25 V, 1.35 V, 1.5 V, 1.8 V, and 2.5 V |

| LDO-CORE          | 1.05 V, 1.1 V, and 1.15 V               |

| LDO-SYS           | 1.8 V and 2.5 V <sup>[1]</sup>          |

<sup>[1]</sup> Do not enable the LDO-SYS 2.5 V option while the application is running. This option is intended only to program the eFuses.

#### 2.2 Power domain rates

<u>Table 4</u> shows the maximum and minimum DC voltage requirements for each power domain in the KW47 MCUs.

Table 4. Power domain rates

| Power domain | Voltage supply       | Minimum | Maximum | Unit |

|--------------|----------------------|---------|---------|------|

| Core domain  | VDD_CORE:            |         |         |      |

|              | • Mid Drive (1.05 V) | 1.0     | 1.1     | V    |

|              | Normal Drive (1.1 V) | 1.04    | 1.21    | V    |

AN14709

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

#### **Power Management Hardware for the KW47**

Table 4. Power domain rates...continued

| Power domain       | Voltage supply       | Minimum | Maximum | Unit |

|--------------------|----------------------|---------|---------|------|

|                    | • Safe-mode (1.15 V) | 1.04    | 1.21    | V    |

| System domain      | VDD_SYS:             |         |         |      |

|                    | Normal mode          | 1.71    | 1.98    | V    |

|                    | Fuse programming     | 2.25    | 2.75    | V    |

| IO-ABC domain      | VDD_IO_ABC           | 1.71    | 3.6     | V    |

| IO-D domain        | VDD_IO_D             | 1.86    | 3.6     | V    |

| Smart power switch | VDD_SWITCH           | 1.9     | 3.6     | V    |

| RF analog domain   | VDD_RF               | 1.175   | 3.6     | V    |

| 2.4 GHz radio PA   | VPA_2.4G             | 0.9     | 2.4     | V    |

| Analog domain      | VDD_ANA              | 1.71    | 3.6     | V    |

# 3 KW47 power configurations

The KW47 microcontroller has independent power domains, allowing various power configurations. You can implement any power configuration depending on the voltage required on each power domain, according to the application requirement. For more information on DC voltage requirements for each power domain in KW47, see <u>Section 2.2</u>.

The purpose of this section is to show the most common power configurations, advantages, and considerations.

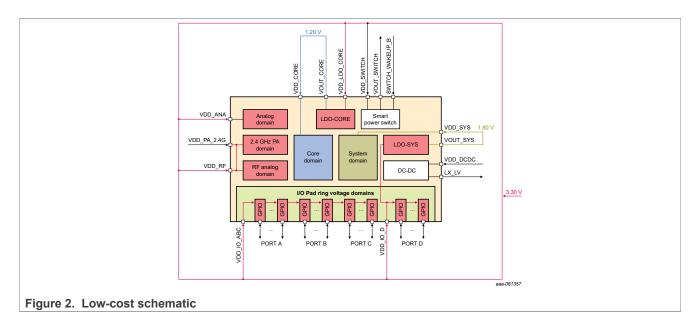

# 3.1 KW47 low-cost supply configuration

The following is the KW47 low-cost supply mode configuration:

- The KW47 low-cost supply mode disables the DC-DC and directly connects each power domain to a unique power supply.

- This configuration is the lowest-cost hardware implementation due to the small number of external components required.

- However, this configuration does not allow you to have independent voltages on each power domain, and therefore, has the highest power consumption.

- In this configuration, the following is recommended:

- Disable the DC-DC

- Clear the SPC -> CNTRL[DCDC\_EN] = 0

- Leave the DCDC\_LX pin (DC-DC output pin) floating in the design

#### **Power Management Hardware for the KW47**

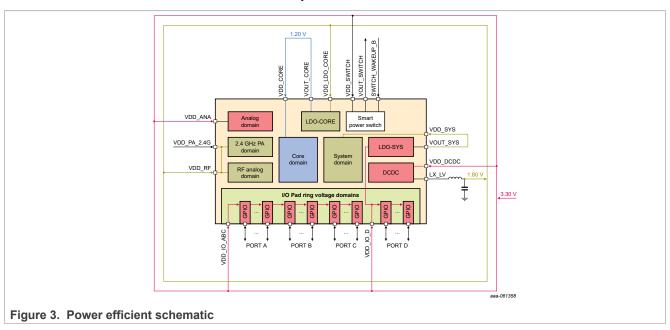

# 3.2 KW47 power efficient mode configuration

The following is the KW47 DC-DC Buck mode configuration:

- The DC-DC Buck mode configuration provides the best balance in power consumption and cost. As a consequence, this mode is the most-used configuration.

- In DC-DC Buck mode, a single power supply is used to deliver power to many power domains including the DC-DC input.

- The DC-DC output can provide a different configurable voltage for the RF domain and LDO-CORE.

- The DC-DC output is targeted to deliver the voltage needed for the RF power domain to reach up to +10 dBm TX output power.

- It is also possible to decrease the DC-DC output voltage as a power-saving mechanism while the RF domain is idle.

- The DC-DC can be used to feed external circuitry.

AN14709

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**Power Management Hardware for the KW47**

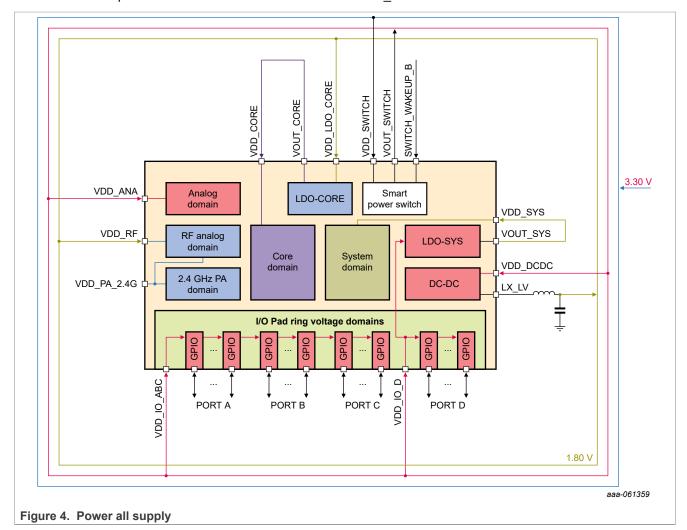

# 3.3 KW47 DC-DC mode controlled with smart power switch

This section describes the KW47 DC-DC mode controlled with the smart power switch as follows:

- The smart power switch (VBAT) is a low-resistance solid-state switch that works with the power management system to implement the power-saving mechanisms.

- It provides two bandgap timers and an LDO voltage regulator dedicated to supply the retention SRAM while the rest of the MCU remains switched off.

- The smart power switch can be used to turn off all the MCUs or some specific power domains to obtain an optimized power consumption.

- The smart power switch can be used to switch on/off external circuitry with a low-dropout voltage.

- In this mode, the smart power switch domain (VDD\_SWITCH) is the only voltage domain required to be powered permanently.

- The software can disable the smart power switch and enable it using any of the VBAT bandgap timers or a falling edge on the SWITCH\_WAKEUP\_B pin.

Figure 4 shows the configuration with the smart power switch as follows:

- The 3.3 V external power source supplies the power to the smart power switch.

- Its output is connected to the DC-DC, LDO-SYS, VDD ANA, VDD IO D, and VDD IO ABC.

- The DC-DC output is connected to the LDO-CORE and VDD RF.

**Power Management Hardware for the KW47**

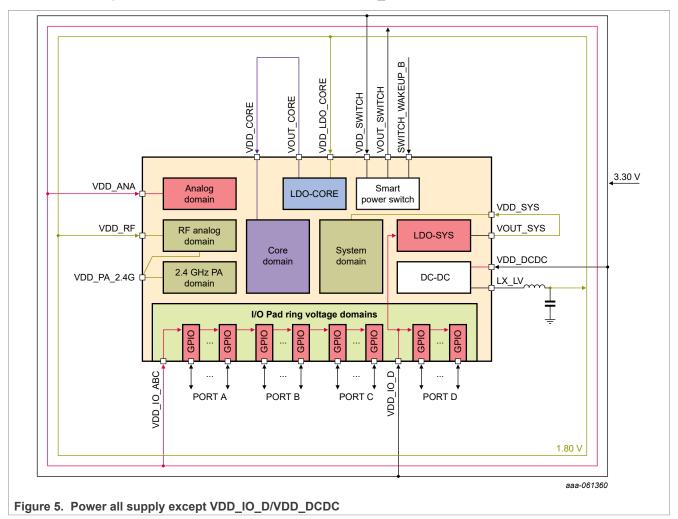

Figure 5 shows the configuration with the smart power switch as follows:

- The 3.3 V external power source supplies the power to the smart power switch and VDD DCDC/VDD IO D.

- Its output is connected to the VDD ANA and VDD IO ABC.

- The DC-DC output is connected to the LDO-CORE and VDD\_RF.

# 4 DC-DC buck converter

This section describes the characteristics, features, and operation of the DC-DC buck converter.

# 4.1 Enabling and disabling DC-DC buck converter

The DC-DC buck converter can be enabled and disabled according to the application configuration and requirements. The SPC regulator control register (CNTRL) can enable or disable the DC-DC on-chip converter by writing the SPC -> CNTRL[DCDC\_EN] = 0. As a default setting, the DC-DC is enabled. However, if your design is bypassing the DC-DC, clear this bit to disable the DC-DC converter and prevent a leakage current.

#### 4.1.1 DC-DC timing characteristics

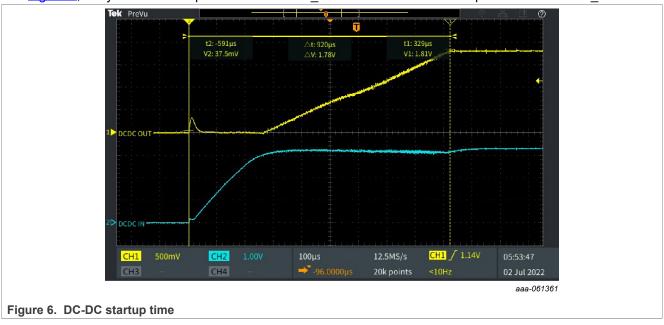

Figure 6 shows the DC-DC startup time:

**Power Management Hardware for the KW47**

- The KW47 is connected in the DC-DC Buck mode and no external loads have been added.

- The DC-DC input and output voltages are DCDC IN = 3.3 V and DCDC OUT = 1.8 V.

- The DC-DC is configured in Normal drive strength mode.

- In Figure 6, the yellow curve represents the DCDC OUT and the blue curve represents the DCDC IN.

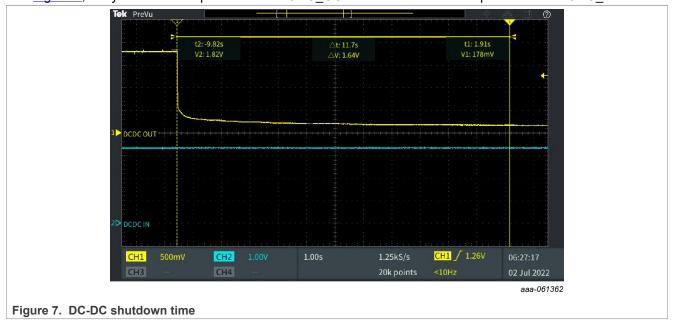

Figure 7 shows the DC-DC shutdown time, considering the drop from 100 % to 10 % of the configured voltage:

- The KW47 is connected in the DC-DC Buck mode and no external loads have been added.

- The DC-DC input and output voltages are DCDC\_IN = 3.3 V and DCDC\_OUT = 1.8 V.

- The DC-DC is configured in the Normal drive strength mode.

- In Figure 7, the yellow curve represents the DCDC\_OUT and the blue curve represents the DCDC\_IN.

**Power Management Hardware for the KW47**

# 4.2 DC-DC Drive strength modes

The DC-DC can operate in the following two different drive modes:

- · Active mode

- · Pulse refresh mode

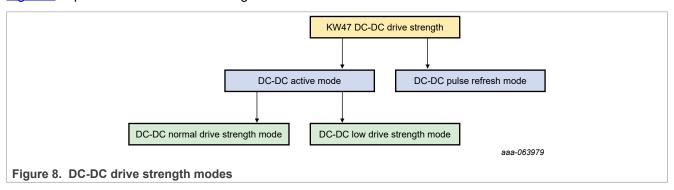

Figure 8 depicts the DC-DC Drive Strength modes.

# 4.2.1 DC-DC Active mode

When operating in the Active mode, the DC-DC periodically issues a pulsed burst to maintain the output at the configured regulation voltage based on an internal analog-comparator monitoring system. This control mechanism ensures the regulation voltage always as long as the DC-DC load current is limited within the maximum specification. When the DC-DC is running in the Active mode, it can work in two different regulator drive strength modes: Normal drive strength and Low drive strength. Having different drive strength modes allow control over the quiescent current, which the DC-DC output driver manages. As a result, the DC-DC changes its maximum output current, the transient response, and efficiency as follows:

- **Normal drive strength mode**: The DC-DC provides the maximum output current capacity with the maximum DC-DC efficiency. This configuration provides the fastest transient response. However, the higher quiescent current at the operating point leads to a bigger DC-DC power consumption.

- Low drive strength mode: The DC-DC provides a limited output current capacity and less DC-DC efficiency. The transient response is slower than in Normal drive strength mode. However, this configuration decreases the overall power consumption of the DC-DC block due to a low quiescent current.

The selection of the Drive strength mode must account for the maximum current required by the application and the transient response requirements. If the DC-DC Drive mode operation is not critical in your application, or if the application behavior is hard to predict, keep these settings in the default configuration. It means using DC-DC Active mode with Normal drive strength mode. However, if your application requires optimizing the power consumption entering and exiting Low-power modes, consider setting the DC-DC Low drive strength mode.

Another option is to combine the DC-DC Normal drive strength in the MCU Active mode and DC-DC Low drive strength for Low-power modes.

# 4.2.2 DC-DC Pulse refresh mode

When the DC-DC is enabled and running in Pulse refresh mode, the DC-DC periodically issues a pulsed burst based on a programmed timer embedded on the system power control (SPC). In this mode, the analog-comparator monitoring system is disabled. Therefore, the DC-DC does not perform pulsed bursts to reload the output when the DC-DC output drops below the regulation voltage. Also, the SPC programmable timer period controls the DC-DC refresh burst entirely. In this mode, the DC-DC is turned off after completing the previous DC-DC burst. It turns on at the next timer timeout to reload the output.

#### **Power Management Hardware for the KW47**

The SPC -> DCDC\_BURST\_CFG [PULSE\_REFRESH\_COUNT] bit field controls how often the DC-DC is pulsed on and off based on the reference clock, which the CCM32K module (f<sub>CCM32K</sub>) provides.

The SPC -> DCDC\_BURST\_CFG[PULSE\_REFRESH\_COUNT] bit field is a 16-bit counter value. It controls the frequency of the DC-DC refresh when DC-DC is configured in Pulse refresh mode.

The formula in Equation (1) is used to calculate the DC-DC refresh period (T<sub>DCDC RESH</sub>) in Pulse refresh mode:

$$T_{DCDC\_RFSH} = \frac{1}{f_{CCM32K}} \times \left( PULSE\_REFRESH\_COUNT + 2 \right)$$

(1)

# 4.2.2.1 Conditions to operate in the DC-DC Pulse refresh mode

The following conditions must be accomplished to operate the DC-DC in the Pulse refresh mode:

- 1. The software must configure the DC-DC Pulse refresh mode before the MCU goes to sleep. However, the DC- DC does not enter the Pulse refresh mode until:

- All power domains have requested to enter the Low-power mode

- The SPC has entered a low-power state

- · The MCU has successfully gone to sleep

At wake-up, the DC-DC returns to the DC-DC Active mode.

- 2. The DC-DC Pulse refresh mode is not intended to supply external loads, but only the MCU itself. In DC-DC Pulse refresh mode, the DC-DC is enabled periodically to reload the DC-DC output capacitor based on the PULSE\_REFRESH\_CNT counter value. The rest of the time the DC-DC remains disabled. The application must configure the PULSE\_REFRESH\_CNT refresh rate to manage the voltage drop on the DC-DC capacitor and avoid a brownout condition. When the DC-DC is in Pulse refresh mode, an external load can cause the DC-DC output voltage to drop faster than the next DC-DC reload cycle. This condition brings the device to a brownout condition. Therefore, this mode is recommended when the MCU power domains are the only load connected on the DC-DC. For cases, when the DC-DC supplies the external loads while the MCU enters Deep power-down mode and a low DC-DC power consumption is desired, use the DC-DC in Low drive strength instead of DC-DC Pulse refresh mode.

- 3. The DC-DC Pulse refresh mode must enable the CCM32K clock output while the MCU enters low power to generate the periodic PWM bursts based on the PULSE\_REFRESH\_COUNT. The CCM32K peripheral can generate the clock output either from the external 32 kHz Xtal or from the internal FRO32K. If the application must disable the 32 kHz Xtal pins to enter the Sleep mode, and DC-DC is configured for Pulse refresh mode, perform the following:

- Ensure that the FRO32K is enabled.

- To generate the CCM32K clock before entering low-power mode, select FRO32K as the main source.

# 4.3 DC-DC frequency stabilization

The DC-DC frequency stabilization feature improves the switching frequency variations caused due to voltage transients in the DC-DC input, or dynamic loads at the DC-DC output. This feature can adjust the center switching frequency of the burst pulses. Therefore, you can consider it for applications sensitive to a particular frequency domain that can suffer interference from the DC-DC switching harmonics. Enabling the frequency stabilization feature causes a reduction of the DC-DC input reload current. However, there is a significant reduction of the maximum output current that the DC-DC can drive at its output.

If the DC-DC does not experience significant transients or drastic changes in the load, keep this feature disabled. As a default setting, the DC-DC frequency stabilization feature is disabled. You can try this feature considering that the DC-DC output current capability is going to get reduced, if:

The application requires strict control over the DC-DC spectral content to avoid interference with other systems.

**Power Management Hardware for the KW47**

• If the application uses a coincell battery where the DC-DC current peaks impact directly on the battery lifetime.

To enable/disable the DC-DC frequency stabilization, write the SPC -> DCDC\_CFG[FREQ\_CNTRL\_ON] bit field. When the frequency stabilization feature is enabled, the DC-DC switching frequency can be adjusted through the SPC -> DCDC\_CFG[FREQ\_CNTRL] 6-bit trimming value. The DC-DC frequency stabilization is only available for the DC-DC Active mode.

## 4.4 DC-DC burst synchronization

The application controls and monitors the DC-DC burst. Synchronizing with the quiet period between consecutive DC-DC bursts can be valuable for noise-sensitive applications, such as during a high-resolution ADC measurement. For this purpose, the DC-DC and the SPC provide the DCDC\_BURST\_TRIG\_PULSE signal to synchronize the DC-DC burst activity with other peripherals in the device. This signal is asserted when the DC-DC burst completes and has entered the quiet period. This signal can trigger the ADC. To activate this signal, it is necessary to set SPC -> DCDC\_BURST\_CFG[EXT\_BURST\_EN] = 1. It is available as a trigger source in the TRGMUX peripheral and can be configured to trigger some on-chip peripherals. For more detail, see the *KW47 Reference Manual* (document <u>KW47RM</u>).

The application can request to initiate the DC-DC burst. For that purpose, the SPC -> DCDC\_BURST\_CFG[BURST\_ACK] must be equal to '0' in the first instance. Then the software can set the SPC -> DCDC\_BURST\_CFG[BURST\_REQ] = 1 to request a burst. The DC-DC and SPC hardware sets the SPC -> DCDC\_BURST\_CFG[BURST\_ACK] = 1 when the burst has completed and the DC-DC has entered in the quiet period. Finally, the software writes '1' to the SPC -> DCDC\_BURST\_CFG[BURST\_ACK] bit to clear the burst acknowledge flag.

For a high-resolution ADC conversion, you can configure the DCDC\_BURST\_TRIG\_PULSE signal to trigger the ADC conversion and then the software initiates a DC-DC burst. At the completion of the current DC-DC burst, the ADC conversion is triggered in the DC-DC guiet period for an optimum ADC conversion result.

## 4.5 DC-DC voltage ramp-up control

The KW47 DC-DC integrates a voltage ramp-up control feature that inserts a delay in DC-DC voltage update when the DC-DC transitions to a higher voltage. This feature helps to control the DC-DC max transient current during the transition, decreasing the current peak due to DC-DC capacitor recharge. This feature is only available when:

- Switching the DC-DC voltage to a higher voltage level in the Active modes.

- The DC-DC drive strength is set to Normal and only supports the DC-DC voltage to 1.8 V maximum, does not support a transition to 2.5 V.

The following DC-DC voltage ramp is controlled on using the next registers:

- DCDC CFG[RAMP CNTRL EN] provides an enable control of the feature.

- DCDC CFG[RAMP CNTRL] adjusts the ramp rate during the voltage transition.

# 4.6 DC-DC operation in power modes

The SPC peripheral has control over the DC-DC work modes. The SPC has the following three configuration registers:

- SPC Active power mode configuration register (ACTIVE CFG)

- SPC Low-power mode configuration register (LP CFG)

- SPC High-power mode configuration register (HP CFG)

#### **Power Management Hardware for the KW47**

These registers are intended to have independent settings for the DC-DC when the KW47 transitions between the Active mode and Low-power mode or High-power request mode.

The ACTIVE\_CFG, LP\_CFG, and HP\_CFG registers can configure the DC-DC voltage and Drive strength modes. Therefore, it is possible to configure the DC-DC in a different way automatically when the device moves to low power and exits it. Having independent configurations for the Active mode and Low-power mode allow the implementation of power-saving mechanisms by software. For example, it is possible to reduce the DC-DC voltage and set the DC-DC Low drive strength mode when the device goes to sleep, configuring the proper settings on the LP\_CFG register. Then restore the DC-DC to a higher voltage and Normal drive mode at wake-up with the programmed settings in the ACTIVE\_CFG. Even if the previous example is the expected operation for most of the applications, it is also possible to set the DC-DC to a higher voltage in the Low-power mode than in the Active mode if the application requires it.

In use cases where the radio must transmit at a high power (that is +10 dBm), it is required to increase the DC-DC output voltage. This request can be managed directly from the radio power domain (without the need to wake up the main power domain), using the RF\_CMC. To request the High-power mode entry, the radio software configures the SPC\_HP\_CTRL[SPC\_HP\_MODE][3:0] to provide the target DC-DC output level. This parameter is one-hot encoded; possible DC-DC output values are: 1.35 V, 1.8 V, and 2.5 V while when setting the SPC\_HP\_MODE to 0x0, the DC-DC output remains unchanged.

Once the SPC\_HP\_MODE is configured, the radio software sets the SPC\_HP\_CTRL[SPC\_HP\_REQ] to initiate a request, and then waits for this request to be acknowledged. To acknowledge the request, the radio software reads the SPC\_HP\_STAT[SPC\_HP\_ACK]. Once acknowledged, the SPC has finalized the transition from the ACTIVE\_CFG to HP\_CFG.

Resetting the SPC\_HP\_CTRL[SPC\_HP\_REQ] triggers SPC to transition back from the HP\_CFG to ACTIVE\_CFG. You can monitor the end of this transition when polling the SPC\_HP\_ACK that returns to 0.

Table 5 describes the DC-DC operation modes allowed in each KW47 Power mode.

Table 5. DC-DC operation modes

| Module                  | Active                                                                                                   | Sleep                                                                          | Deep Sleep                                                                   | Power Down                                                                             | Deep power-<br>down mode |

|-------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------|

| DC-DC buck<br>converter | SPC ACTIVE_<br>CFG register<br>controls the<br>Normal or Low<br>drive strength<br>mode                   | SPC LP_CFG<br>register controls<br>the Normal or Low<br>drive strength<br>mode | SPC LP_CFG<br>controls the<br>Normal, Low Drive<br>Strength, Refresh<br>mode | SPC LP_CFG<br>controls the Normal,<br>Low Drive Strength,<br>or Pulsed Refresh<br>mode | Off                      |

|                         | SPC HP_CFG<br>controls the<br>Normal drive<br>strength mode<br>when a high<br>power request is<br>active |                                                                                | Off (Optional)                                                               | Off (Optional)                                                                         |                          |

To configure the DC- DC in the Low drive strength mode when the MCU is in the Active mode, the application must set the same DC-DC output voltage on the ACTIVE\_CFG and LP\_CFG registers. It is mandatory to disable the HVD/LVD in the LP\_CFG register before configuring the DC-DC in Pulsed refresh mode.

Any changes to the DC-DC drive strength or voltage level cause the SPC -> SC[BUSY] flag to assert to '1' logic level until SPC has completed changing its state to the new value. Therefore, software must check this status bit and wait until this bit clears to '0', to ensure that the SPC has completed the drive strength or voltage transition.

**Power Management Hardware for the KW47**

# 4.7 DC-DC main configuration registers

This section summarizes the main SPC registers involved in the configuration of the DC-DC buck converter in the KW47 MCU. <u>Table 6</u> describes the SPC registers that configure the DC-DC behavior. For more details on the peripheral description, see the *KW47 Reference Manual* (document <u>KW47RM</u>).

#### SPC0 base address 4001 6000h

Table 6. DC-DC main configuration registers

| Offset | Register                                                                                                                                                               | Width (bits) | Access | Reset value |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|-------------|

| 14h    | SPC regulator control register (CNTRL)  This register controls the enablement of the SPC regulators.                                                                   | 32           | WONCE  | 0000_0007h  |

| 60h    | High power config control register (HP_CNFG_CNTRL)  This register is used to enable the high power request feature.                                                    | 32           | RW     | 0000_0000h  |

| 100h   | Active power mode configuration register (ACTIVE_CFG) This register controls the settings of the SPC regulators in the Active mode.                                    | 32           | RW     | 3F10_0E15h  |

| 108h   | Low-power mode configuration register (LP_CFG)  This register controls the settings of the SPC regulators in the Low-power modes.                                      | 32           | RW     | 0002_1104h  |

| 110h   | High-Power mode configuration register (HP_CFG)  This register controls the settings of the SPC regulators when in the Active mode and a high power request is active. | 32           | RW     | 3F10_0E15h  |

| 500h   | DC-DC configuration register (DCDC_CFG)  This register configures the frequency stabilization bit fields.                                                              | 32           | RW     | 0000_0000h  |

| 504h   | DC-DC burst configuration register (DCDC_BURST_CFG) This register configures the DC-DC burst control bit fields.                                                       | 32           | RW     | 0140_0000h  |

#### 4.7.1 SPC regulator control register (CNTRL)

**CNTRL[DCDC\_EN]**: This bit field controls if the DC-DC is turned on (DCDC\_EN = 1) or turned off (DCDC\_EN = 0). As a default setting, the DC-DC is turned on. Ensure that the power domains, which this domain supplies can be disabled before disabling the DC-DC. If the DC-DC is bypassed, disable the DC-DC writing (DCDC\_EN = 0).

#### 4.7.2 High power config control register (HP CNFG CNTRL)

**HP\_CNFG\_CNTRL[HP\_REQ\_EN]**: This bit field controls the high power request HP\_REQ\_EN = 1 to enable or HP\_REQ\_EN = 0 to disable. Once this bit field is enabled, we need one of these two conditions to activate the high power request.

- HP\_CNFG\_CTRL[OVERRIDE\_EN] = 0 and the secondary core domain asserts the external HP request.

- HP\_CNFG\_CTRL[OVERRIDE\_EN] = 0 and HP\_CNFG\_CTRL[OVERRIDE\_SEL] = 1.

**HP\_CNFG\_CNTRL[OVERRIDE\_EN]**: This bit field overrides the high power request to a value, which the OVERRIDE SEL sets. To enable OVERRIDE EN = 1 and to disable OVERRIDE = 0.

**HP\_CNFG\_CNTRL[OVERRIDE\_SEL]**: This bit field overrides the external high power request and forces the high power request to the OVERRIDE SEL value.

AN14709

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**Power Management Hardware for the KW47**

# 4.7.3 Active power mode configuration register (ACTIVE\_CFG)

• ACTIVE\_CFG[DCDC\_VDD\_LVL]: This bit field controls the DC-DC output voltage when the SPC is in the Active mode. The DCDC\_OUT = 2.5 V is only available for DC-DC Normal drive strength. To set the DCDC\_OUT = 2.5 V, it is required to set the DCDC\_CFG[VOUT2P5\_SEL] = 1. For the rest of the voltage options, the VOUT2P5\_SEL bit must be 0.

Table 7. DC-DC VDD regulator level

| DCDC_VDD_LVL | VOUT2P5_SEL | DC-DC voltage |

|--------------|-------------|---------------|

| 00b          | 0b          | 1.25 V        |

| 01b          | 0b          | 1.35 V        |

| 10b          | 0b          | 1.5 V         |

| 11b          | 0b          | 1.8 V         |

| xxb          | 1b          | 2.5 V         |

• ACTIVE\_CFG[DCDC\_VDD\_DS]: This bit field controls the DC-DC Drive strength mode when the SPC is in the Active mode. The valid Drive strength modes when the SPC is in the Active mode are DC-DC Normal and DC-DC Low drive strength. DC-DC Pulsed refresh mode is not available for SPC Active mode.

Table 8. DC-DC VDD regulator drive strength

| DCDC_VDD_DS | DC-DC Drive mode             |

|-------------|------------------------------|

| 00b         | Reserved                     |

| 01b         | Set to Low drive strength    |

| 10b         | Set to Normal drive strength |

| 11b         | Reserved                     |

# 4.7.4 Low-power mode configuration register (LP\_CFG)

• LP\_CFG[DCDC\_VDD\_LVL]: This bit field controls the DC-DC output voltage when the SPC is in the Low-power mode. The DCDC\_OUT = 2.5 V is only available for DC-DC Normal drive strength. To set the DCDC\_OUT = 2.5 V, it is required to set the DCDC\_CFG[VOUT2P5\_SEL] = 1. For the rest of the voltage options, the VOUT2P5\_SEL bit must be 0.

Table 9. DC-DC VDD regulator level

| able of De De 109 alate. 10101 |             |               |  |  |

|--------------------------------|-------------|---------------|--|--|

| DCDC_VDD_LVL                   | VOUT2P5_SEL | DC-DC voltage |  |  |

| 00b                            | 0b          | 1.25 V        |  |  |

| 01b                            | 0b          | 1.35 V        |  |  |

| 10b                            | 0b          | 1.5 V         |  |  |

| 11b                            | 0b          | 1.8 V         |  |  |

| xxb                            | 1b          | 2.5 V         |  |  |

• LP\_CFG[DCDC\_VDD\_DS]: This bit field controls the DC-DC Drive strength mode when the SPC is in the Low- power mode.

Table 10. DC-DC VDD regulator drive strength

| DCDC_VDD_DS | DC-DC Drive mode          |

|-------------|---------------------------|

| 00b         | Set to Pulse Refresh mode |

14709 All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

# **Power Management Hardware for the KW47**

Table 10. DC-DC VDD regulator drive strength...continued

| DCDC_VDD_DS | DC-DC Drive mode             |

|-------------|------------------------------|

| 01b         | Set to Low drive strength    |

| 10b         | Set to Normal drive strength |

| 11b         | Reserved                     |

# 4.7.5 High-Power mode configuration register (HP\_CFG)

**HP\_CFG[DCDC\_VDD\_LVL]**: This bit field controls the DC-DC output voltage when the SPC is in active configuration register when HP\_CNFG\_CTRL[HP\_REQ\_EN] = 1 and if any of the following conditions are true:

- HP CNFG CTRL[OVERRIDE EN] = 0 and the secondary core domain asserts the external HP request.

- HP CNFG CTRL[OVERRIDE EN] = 0 and HP CNFG CTRL[OVERRIDE SEL] = 1.

The DCDC\_OUT = 2.5 V is only available for DC-DC Normal drive strength mode. To set DCDC\_OUT = 2.5 V, it is required to set DCDC\_CFG[VOUT2P5\_SEL] = 1. For the rest of the voltage options, the VOUT2P5\_SEL bit must be 0.

The voltages in this register are only valid when SPC\_HP\_CTRL[SPC\_HP\_MODE] = 0.

Table 11. DC-DC VDD regulator level

| 3            |             |                          |               |

|--------------|-------------|--------------------------|---------------|

| DCDC_VDD_LVL | VOUT2P5_SEL | SPC_HP_CTRL[SPC_HP_MODE] | DC-DC voltage |

| 00b          | 0b          | 0000Ь                    | 1.25 V        |

| 01b          | 0b          | 0000Ь                    | 1.35 V        |

| 10b          | 0b          | 0000Ь                    | 1.5 V         |

| 11b          | 0b          | 0000Ь                    | 1.8 V         |

| xxb          | 1b          | 0000Ь                    | 2.5 V         |

|              |             |                          |               |

**HP\_CFG[DCDC\_VDD\_DS]**: This bit field controls the DC-DC drive strength mode when the SPC is active is in active configuration register when HP\_CNFG\_CTRL[HP\_REQ\_EN] = 1 and if any of the following conditions are true:

- HP\_CNFG\_CTRL[OVERRIDE\_EN] = 0 and the secondary core domain asserts the external HP request.

- HP\_CNFG\_CTRL[OVERRIDE\_EN] = 0 and HP\_CNFG\_CTRL[OVERRIDE\_SEL] = 1.

Table 12. DC-DC VDD regulator drive strength

| DCDC_VDD_DS | DC-DC Drive mode             |

|-------------|------------------------------|

| 00b         | Reserved                     |

| 01b         | Set to Low drive strength    |

| 10b         | Set to Normal drive strength |

| 11b         | Reserved                     |

# 4.7.6 DC-DC configuration register (DCDC\_CFG)

DCDC\_CFG[VOUT2P5\_SEL]: This bit field must remain enabled (VOUT2P5\_SEL = 1) if the desired DC-DC output is 2.5 V (DCDC\_VDD\_LVL = 10b). Otherwise, this bit must remain disabled (VOUT2P5\_SEL = 0). If VOUT2P5\_SEL = 1 and DCDC\_VDD\_LVL is different than 10b (DC-DC output voltage selection is not 2.5 V), the DC-DC output voltage is not predictable. Therefore, you must enable this bit only if the output voltage is 2.5 V. If the output voltage must move from 2.5 V to another voltage level, this bit must be cleared (VOUT2P5\_SEL = 0). The 2.5 V option is only available in DC-DC Normal drive strength mode. If the DC-DC

#### **Power Management Hardware for the KW47**

is operating at 2.5 V in DC-DC Normal drive strength mode and you must change the DC-DC drive strength mode, do the following:

- Update the DC-DC output value to any other allowed value

- Clear this bit

- DCDC\_CFG[FREQ\_CNTRL\_ON]: This bit field enables/disables the frequency stabilization function in the DC-DC. Frequency stabilization is enabled with FREQ\_CNTRL\_ON = 1 and disabled with FREQ\_CNTRL\_ON = 0. When it is enabled, the DC-DC burst frequency can be adjusted with the FREQ\_CNTRL bit field from the central frequency.

- DCDC\_CFG[FREQ\_CNTRL]: This bit field represents a 6-bit trimming value for the DC-DC burst frequency when the frequency stabilization feature is enabled, FREQ\_CNTRL\_ON = 1. When FREQ\_CNTRL\_ON = 0, FREQ\_CNTRL trimming value is ignored.

## 4.7.7 DC-DC burst configuration register (DCDC\_BURST\_CFG)

- DCDC\_BURST\_CFG[PULSE\_REFRESH\_CNT]: This bit field is a 16-bit multiplier value that determines the DC-DC burst occurrence when the DC-DC is in Pulse refresh mode based on the CCM32K output frequency. See Section 4.2.2.

- DCDC\_BURST\_CFG[BURST\_ACK]: This bit field is an indicator flag that sets to '1' when the previous DC-DC burst has completed successfully that the software has requested. This bit must be cleared each time at the completion of a burst, which the software requests when writing BURST\_ACK = 1.

- DCDC\_BURST\_CFG[EXT\_BURST\_EN]: This bit enables/disables the internal

DCDC\_BURST\_TRIG\_PULSE signal that is used to trigger some peripherals with the TRGMUX when

the DC-DC enters in the quiet period. The EXT\_BURST\_EN = 1 enables the trigger signal and the

EXT\_BURST\_EN = 0 disables the trigger signal. This bit must be written only when the BURST\_ACK = 0 and

before writing the BURST\_REQ = 1 to request a DC-DC burst.

- DCDC\_BURST\_CFG[BURST\_REQ]: Write BURST\_REQ = 1 to initiate a burst request. Do not initiate a new burst request until the previous one has been completed and acknowledged (clearing the BURST\_ACK flag).

# 4.8 DC-DC main configuration registers

This section includes the DC-DC electrical characteristics.

#### 4.8.1 DC-DC converter specifications

Table 13 summarizes the DC-DC converter specifications.

Table 13. DC-DC converter specifications

| Symbol         | Description                     | Min    | Тур  | Max    | Unit | Notes |

|----------------|---------------------------------|--------|------|--------|------|-------|

| V_DCDC_IN      | DC-DC input voltage             | 1.71   | -    | 3.6    | V    | 1, 2  |

| V_DCDC_OUT     | DC-DC output voltage            |        |      |        |      | 1, 2  |

|                | 1.25                            | 1.1875 | 1.25 | 1.3125 | V    |       |

|                | 1.35                            | 1.2825 | 1.35 | 1.475  | V    |       |

|                | 1.5                             | 1.425  | 1.5  | 1.575  | V    |       |

|                | 1.8                             | 1.71   | 1.8  | 1.89   | V    |       |

|                | 2.5                             | 2.375  | 2.5  | 2.625  | V    |       |

| V_DCDC_ RIPPLE | Ripple voltage at DC-DC output: |        |      |        |      |       |

|                | Normal drive strength mode      | -      | 1    | -      | %    | 3     |

|                | Low drive strength mode         | -      | 25   | -      | mV   | -     |

# **Power Management Hardware for the KW47**

Table 13. DC-DC converter specifications...continued

| Symbol            | Description                                        | Min | Тур | Max | Unit | Notes |

|-------------------|----------------------------------------------------|-----|-----|-----|------|-------|

| I_DCDC_LOAD       | Load current at DC-DC output:                      |     |     |     |      |       |

|                   | Normal drive strength mode                         | -   | -   | 105 | mA   | 1, 4  |

|                   | Low drive strength mode                            | -   | -   | 15  | mA   | 1, 4  |

|                   | Frequency Stabilization on [FREQ_<br>CNTRL_ON = 1] | -   | -   | 45  | mA   | 1, 4  |

| LX                | DC-DC output inductor value                        | 0.8 | 1   | 2.2 | μH   | 5     |

| ESR               | DC-DC inductor equivalent series resistance        | -   | 110 | -   | mΩ   | 6     |

| COUT              | DC-DC output capacitance                           | 6   | 22  | 30  | μF   | 7     |

| F_Burst           | DC-DC reload burst frequency                       | 3   | 5   | 8   | MHz  | 8     |

| F_Burst_ Accuracy | DC-DC reload burst frequency accuracy              | -   | 10  | -   | %    | 8     |

#### Note:

- 1. The DC-DC converter generates 1.8 V at DCDC\_LX by default. The DC-DC can be used to power VDD\_RF, VDD\_LDO\_CORE, and external components as long as the maximum ILOAD is not exceeded.

- 2. The VDD\_DCDC input supply to DC-DC must be at least 500 mV higher than the desired output at DCDC LX.

- 3. The DC ripple is shown as a percentage in relation with the programmed DC-DC output voltage.

- 4. The maximum load current during boot-up must not exceed 60 mA.

- 5. The recommended inductor value is 1  $\mu$ H to 1.5  $\mu$ H. If the inductor is < 1  $\mu$ H, the DC-DC efficiency is not guaranteed.

- 6. The maximum recommended ESR is 250 m $\Omega$  (not a hard limit).

- 7. The variation in capacitance of the capacitor at DCDC\_LX due to aging, temperature, and voltage degradation must not exceed the min/max values.

- 8.  $FREQ_CNTRL_ON = 1$ .

# 5 LDO core and LDO system regulators

This section describes the characteristics, features, and operation of the LDO core and LDO system regulators.

# 5.1 Enabling and disabling LDOs

Both the LDO core and LDO system can be enabled and disabled according to the application requirements. The SPC regulator Control register (CNTRL) can enable or disable the LDO CORE and LDO SYS. To enable or disable the LDO CORE and LDO SYS, write the SPC -> CNTRL[CORELDO\_EN] = 0 and SPC -> CNTRL[SYSLDO\_EN] = 0 respectively. As a default setting, both the LDOs are enabled. However, if your design is bypassing any of these regulators, you must disable such LDO to prevent a leakage current. The LDO outputs, VOUT\_CORE and VOUT\_SYS, are internally tied with VDD\_CORE and VDD\_SYS power domains respectively. Therefore, before disabling any of these regulators, ensure that such power domain is connected with an external power supply. Some power modes are allowed to turn off the VDD\_CORE power domain.

Therefore, if no external voltage is connected on the VDD\_SYS power domain, the LDO system regulator cannot be disabled. Disable the LDO core or LDO system as follows:

• To disable the high and low voltage detectors (SYS\_HVDE, CORE\_HVDE, SYS\_LVDE, and CORE\_LVDE), change the value to 0b in the corresponding bit fields in the SPC -> ACTIVE\_CFG register

**Power Management Hardware for the KW47**

• Wait until the SPC -> SC[BUSY] = 0

To disable the LDO core regulator, clear the SPC -> CNTRL[CORELDO\_EN] or SPC -> CNTRL[SYSLDO\_EN] bit fields as it corresponds.

The LDO core and LDO system have a pulldown resistor that forces the LDO discharge when the software disables the regulator or, in the specific case of the LDO core, when the MCU enters in Deep power-down mode. This feature is enabled as a default setting. However, when the LDO core and LDO system are disabled to drive the VDD\_CORE and VDD\_SYS voltages from an external power supply, it is recommended to disable the pulldown resistors to prevent current leakage. To disable the pulldown resistors, write SPC -> CORELDO\_CFG[DPDOWN\_PULLDOWN\_DISABLE] = 1 for the LDO CORE regulator and SPC ->SYSLDO\_CFG[ISINKEN] = 0 for the LDO SYS regulator.

# 5.1.1 LDO timing characteristics

This section includes the timing characteristics of the LDO core and LDO system regulators.

## 5.1.1.1 LDO core timing characteristics

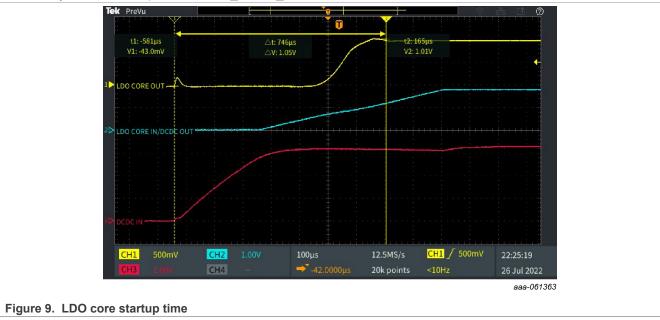

Figure 9 shows the LDO core startup time:

- The KW47 has been connected in the DC-DC Buck mode and no external loads have been added.

- In this configuration, the DC-DC output serves as the power supply for the LDO core.

- The DC-DC input voltage is DCDC\_IN = 3.3 V.

- The LDO core input and output voltages are LDO\_CORE\_IN = DCDC\_OUT = 1.8 V and LDO\_CORE\_OUT = 1.05 V.

- The DC-DC and LDO core are configured in Normal drive strength mode.

- In this capture, the red curve represents DCDC\_IN, the blue curve represents LDO\_CORE\_IN/DCDC\_OUT, and the yellow curve represents LDO\_CORE\_OUT.

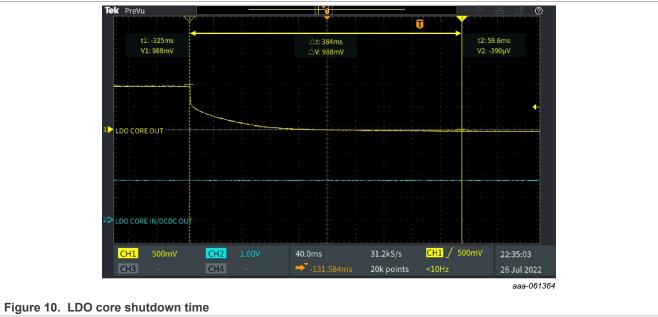

Figure 10 shows the LDO core shutdown time:

- The KW47 has been connected in the DC-DC Buck mode and no external loads have been added.

- The DC-DC input voltage is DCDC\_IN = 3.3 V.

**Power Management Hardware for the KW47**

- The LDO core input and output voltages are LDO\_CORE\_IN/DCDC\_OUT = 1.8 V and LDO\_CORE\_OUT = 1.05 V.

- The LDO core and DC-DC are configured in Normal drive strength mode.

- In <u>Figure 10</u>, the yellow curve represents LDO\_CORE\_OUT and the blue curve represents LDO\_CORE\_IN/DCDC\_OUT.

# 5.1.1.2 LDO system timing characteristics

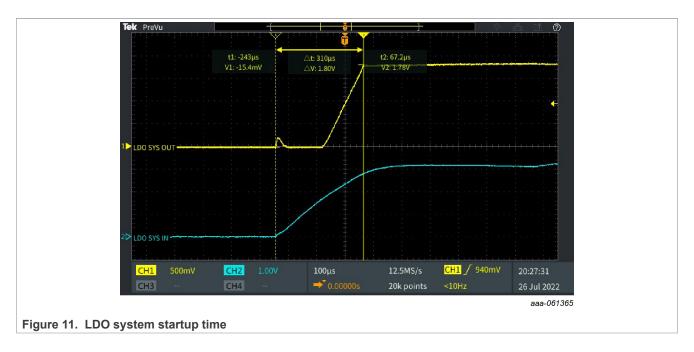

Figure 11 shows the LDO system startup time:

- The KW47 has been connected in the DC-DC Buck mode and no external loads have been added.

- The LDO system input and output voltages are LDO\_SYS\_IN = 3.3 V and LDO\_SYS\_OUT = 1.8 V.

- The LDO SYS is configured in Normal drive strength mode.

- In Figure 11, the yellow curve represents LDO\_SYS\_OUT and the blue curve represents LDO\_SYS\_IN.

#### **Power Management Hardware for the KW47**

# 5.2 LDO drive strength modes

The LDO core and LDO system have the following two drive strength modes:

- · Normal drive strength

- · Low drive strength

In Normal drive strength mode, the LDO regulator provides the maximum output current capability. On the other hand, the Low drive strength LDO mode limits the output current. The LDO regulator supplies the core and power systems domains but does not supply the external loads. If the LDO drive strength mode selection is not critical in your application while the MCU runs in the Active mode, keep the default settings, that is, the LDO core and LDO system in Normal drive strength mode. If the application requires to enter low-power mode, configure the LDO in the Low drive strength to reduce power consumption. This approach considers that the power domains supplied through the LDO regulators do not exceed a few microamps and the LDO is not overstressed in this condition. Once the MCU wakes up, you can select the Normal drive strength mode for each LDO if required.

# 5.3 LDO operation in power modes

Similar to the DC-DC buck converter, the LDO core and LDO system regulators can be configured in an independent way in the Active and Low-power modes. The SPC registers, Active power mode configuration register (ACTIVE\_CFG) when in high power request (HP\_CFG), and SPC low-power mode configuration register (LP\_CFG) provide the configuration alternatives for the corresponding mode.

Table 14 describes the LDO operation modes allowed in each KW47 power mode.

Table 14. LDO operation modes

| Module   | Active                                                                     | Sleep                                                              | Deep Sleep                                                            | Power down                                                            | Deep power down |

|----------|----------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|

| LDO core | SPC ACTIVE_<br>CFG controls the<br>Normal or Low<br>drive strength<br>mode | SPC LP_CFG<br>controls the Normal<br>or Low drive<br>strength mode | SPC LP_CFG<br>controls the<br>Normal or Low<br>drive strength<br>mode | SPC LP_CFG<br>controls the<br>Normal or Low<br>drive strength<br>mode | Off             |

#### **Power Management Hardware for the KW47**

Table 14. LDO operation modes...continued

| Module     | Active                                                                     | Sleep                                                              | Deep Sleep                                                         | Power down                                                         | Deep power down                                                    |

|------------|----------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

|            | SPC HP_CFG<br>controls the<br>Normal drive<br>strength mode                |                                                                    | Off (optional)                                                     | Off (optional)                                                     |                                                                    |

| LDO system | SPC ACTIVE_<br>CFG controls the<br>Normal or Low<br>drive strength<br>mode | SPC LP_CFG<br>controls the Normal<br>or Low drive<br>strength mode |

|            | SPC HP_CFG<br>controls the<br>Normal drive<br>strength mode                |                                                                    |                                                                    |                                                                    |                                                                    |

When the application is running, the LDO system must be configured at 1.8 V. The LDO system 2.5 V output voltage alternative must be selected only when the MCU must program the eFuses. Therefore, this voltage option is only available when the MCU is running in the Active mode. When the LDO system is running at 2.5 V, the LDO is forced to operate in the Normal drive strength mode.

The LDO system Low drive strength mode is available only if the LDO is configured at 1.8 V. Before changing the LDO system drive strength to Low drive strength in the ACTIVE\_CFG or LP\_CFG, ensure to disable all the HVD/LVD in the corresponding configuration. Enabling any HVD/LVD while the LDO system is in the Low drive strength mode forces the LDO to operate in Normal drive strength mode.

**Note:** Any changes to the DC-DC drive strength or voltage level cause the SPC -> SC[BUSY] flag to assert to '1' logic level until the SPC has completed changing its state to the new value. Therefore, the software must check the SPC -> SC[BUSY] status bit and wait until this bit clears to '0' to ensure that the SPC has completed the drive strength or voltage transition.

# 5.4 LDO main configuration registers

This section summarizes the main SPC registers involved in the configuration of the LDO regulators in the KW47 MCU. <u>Table 15</u> describes the SPC registers that configure the behavior of each LDO. For more details on the peripheral description, see the *KW47 Reference Manual* (document <u>KW47RM</u>).

#### SPC0 base address 4001 6000h

Table 15. SPC registers

| Offset | Register                                                                                                                            | Width (bits) | Access | Reset value |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|-------------|

| 14h    | SPC regulator control register (CNTRL)  This register controls the enablement of the SPC regulators.                                | 32           | WONCE  | 0000_0007h  |

| 100h   | Active power mode configuration register (ACTIVE_CFG) This register controls the settings of the SPC regulators in the Active mode. | 32           | RW     | 3F10_0E15h  |

| 108h   | Low-power mode configuration register (LP_CFG)  This register controls the settings of the SPC regulators in the Low-power modes.   | 32           | RW     | 0002_1104h  |

| 110h   | High power mode configuration register (HP_CFG)                                                                                     | 32           | RW     | 3F10_0E15h  |

# **Power Management Hardware for the KW47**

Table 15. SPC registers...continued

| Offset | Register                                                                                                              | Width (bits) | Access | Reset value |

|--------|-----------------------------------------------------------------------------------------------------------------------|--------------|--------|-------------|

|        | This register controls the settings of the SPC regulators when in the Active mode and a high power request is active. |              |        |             |

| 300h   | LDO_CORE configuration register (CORELDO_CFG)                                                                         | 32           | RW     | 0000_0000h  |

| 400h   | LDO_SYS configuration register (SYSLDO_CFG)                                                                           | 32           | RW     | 0000_0101h  |

# 5.4.1 SPC regulator control register (CNTRL)

- CNTRL[CORELDO\_EN]: This bit field controls whether the LDO core is turned on (CORELDO\_EN = 1) or turned off (CORELDO\_EN = 0). As a default setting, the LDO core is turned on. Ensure that the power domains, which this domain supplies can be disabled before disabling this LDO. If the LDO core is bypassed, to disable the LDO core write CORELDO\_EN = 0.

- CNTRL[SYSLDO\_EN]: This bit field controls whether the LDO system is turned on (SYSLDO\_EN = 1) or turned off (SYSLDO\_EN = 0). As a default setting, the LDO system is turned on. If the LDO system is bypassed, to disable the LDO system write SYSLDO\_EN = 0.

- 5.4.2 Active power mode configuration register (ACTIVE\_CFG)

- ACTIVE\_CFG[CORELDO\_VDD\_LVL]: This bit field controls the LDO core output voltage when the SPC is in the Active mode.

Table 16. CORELDO VDD LVL and LDO voltage

| CORELDO_VDD_LVL | LDO voltage |

|-----------------|-------------|

| 00b             | Reserved    |

| 01b             | 1.05 V      |

| 10b             | 1.1 V       |

| 11b             | 1.15 V      |

ACTIVE\_CFG[SYSLDO\_VDD\_LVL]: This bit field controls the LDO system output voltage when the SPC is in the Active mode.

Table 17. SYSLDO\_VDD\_LVL and LDO voltage

| SYSLDO_VDD_LVL | LDO voltage |

|----------------|-------------|

| 0b             | 1.8 V       |

| 1b             | 2.5 V       |

• ACTIVE\_CFG[SYSLDO\_VDD\_DS]: This bit field controls the LDO System drive strength mode when the SPC is in the Active mode.

Table 18. SYSLDO\_VDD\_DS and LDO Drive mode

| SYSLDO_VDD_DS | LDO Drive mode               |

|---------------|------------------------------|

| 0b            | Set to low drive strength    |

| 1b            | Set to normal drive strength |

**Power Management Hardware for the KW47**

# 5.4.3 Low-power mode configuration register (LP\_CFG)

• LP\_CFG[CORELDO\_VDD\_LVL]: This bit field controls the LDO core output voltage when the SPC is in the Low- power mode.

Table 19. CORELDO\_VDD\_LVL and LDO voltage

| CORELDO_VDD_LVL | LDO voltage |

|-----------------|-------------|

| 00b             | Reserved    |

| 01b             | 1.05 V      |

| 10b             | 1.1 V       |

| 11b             | 1.15 V      |

• LP\_CFG[CORELDO\_VDD\_DS]: This bit field controls the LDO Core drive strength mode when the SPC is in the Low-power mode.

Table 20. CORELDO\_VDD\_DS and LDO Drive mode

| CORELDO_VDD_DS | LDO Drive mode               |

|----------------|------------------------------|

| 0b             | Set to low drive strength    |

| 1b             | Set to normal drive strength |

• LP\_CFG[SYSLDO\_VDD\_DS]: This bit field controls the LDO System drive strength mode when the SPC is in Low-power mode.

Table 21. SYSLDO\_VDD\_DS and LDO Drive mode

| SYSLDO_VDD_DS | LDO Drive mode               |

|---------------|------------------------------|

| 0b            | Set to low drive strength    |

| 1b            | Set to normal drive strength |

# 5.4.4 High power mode configuration register (HP\_CFG)

• **HP\_CFG[CORELDO\_VDD\_LVL]**: This bit field controls the LDO core output voltage when the SPC is in the High power request mode.

Table 22. CORELDO VDD LVL and LDO voltage

| CORELDO_VDD_LVL | LDO voltage |

|-----------------|-------------|

| 00b             | Reserved    |

| 01b             | 1.05 V      |

| 10b             | 1.1 V       |

| 11b             | 1.15 V      |

• **HP\_CFG[SYSLDO\_VDD\_LVL]**: This bit field controls the LDO system output voltage when the SPC is in the High power request mode.

Table 23. SYSLDO\_VDD\_LVL and LDO voltage

| SYSLDO_VDD_LVL | LDO voltage |

|----------------|-------------|

| 0b             | 1.8 V       |

| 1b             | 2.5 V       |

AN14709 All inform

All information provided in this document is subject to legal disclaimers

© 2025 NXP B.V. All rights reserved.

#### **Power Management Hardware for the KW47**

HP\_CFG[SYSLDO\_VDD\_DS]: This bit field controls the LDO System drive strength mode when the SPC is in the High power request mode.

Table 24. SYSLDO\_VDD\_DS and LDO Drive mode

| SYSLDO_VDD_DS | LDO Drive mode               |

|---------------|------------------------------|

| 0b            | Set to low drive strength    |

| 1b            | Set to normal drive strength |

# 5.4.5 LDO\_CORE configuration register (CORELDO\_CFG)

**CORELDO\_CFG[DPDOWN\_PULLDOWN\_DISABLE]**: This configuration register is used to control whether the pull-down sink resistor is enabled or disabled in the LDO core. It is used to discharge the LDO output voltage fast when this regulator is shut down in Deep power-down mode. This resistor is enabled by default and it is recommended not to change this setting.

# 5.4.6 LDO\_SYS configuration register (SYSLDO\_CFG)

**SYSLDO\_CFG[ISINKEN]**: This configuration register is used to control whether the pull-down sink resistor is enabled or disabled in the LDO system. It is used to discharge the LDO output voltage fast when this regulator is shut down. This resistor is enabled by default and it is recommended not to change this setting.

#### 5.5 LDO electrical characteristics

This section includes the electrical characteristics of the LDO core and LDO system regulators.

## 5.5.1 LDO core electrical characteristics

Table 25 summarizes the LDO core regulator specifications.

Table 25. LDO core regulator specifications

| Symbol        | Description                                           | Min  | Тур | Max  | Unit | Notes |

|---------------|-------------------------------------------------------|------|-----|------|------|-------|

| V_LDO_CORE_IN | LDO core input voltage                                | 1.25 | -   | 3.6  | V    | 1, 2  |

| V_LDO_CORE_   | LDO core output voltage:                              |      |     |      |      |       |

| OUT           | Normal drive strength mode                            | 1.05 | -   | 1.15 | V    |       |

|               | Low drive strength mode                               | 1.05 | -   | 1.15 | V    |       |

| I_LDO_CORE_   | LDO core max load current at LDO output:              |      |     |      |      |       |

| LOAD          | Normal drive strength: 0.20 V < VDROP_<br>OUT < 0.4 V | -    | -   | 40   | mA   |       |

|               | Normal drive strength: VDROP_OUT >     0.4 V          | -    | -   | 60   | mA   |       |

|               | Low drive strength: 0.20 V < VDROP_ OUT < 0.4 V       | -    | -   | 18   | mA   |       |

|               | • Low drive strength: VDROP_OUT > 0.4 V               | -    | -   | 28   | mA   |       |

| linrush       | LDO core inrush current                               | -    | -   | 500  | mA   |       |

| COUT          | LDO core external output capacitor                    | 3.7  | 4.7 | 10   | μF   |       |

| Cdec          | LDO core external decoupling capacitor                | -    | 0.1 | -    | μF   |       |

# Power Management Hardware for the KW47

Table 25. LDO core regulator specifications...continued

| Symbol | Description                                            | Min | Тур | Max | Unit | Notes |

|--------|--------------------------------------------------------|-----|-----|-----|------|-------|

|        | External output capacitor equivalent series resistance | -   | 10  | -   | mΩ   |       |

#### Note:

- 1. To bypass the LDO\_CORE, tie VDD\_LDO\_CORE to VDD\_CORE.

- 2. The VDD\_LDO\_CORE input supply must be set to 200 mV higher than the VOUT\_CORE in the mid-voltage regulation option (1.05 V). For the rest of the supported voltage regulation options, it must be set to 250 mV higher than the VOUT\_CORE.

# 5.5.2 LDO system electrical characteristics

Table 26 summarizes the LDO system regulator specifications.

Table 26. LDO system regulator specifications

| Symbol         | Description                                            | Min  | Тур | Max  | Unit | Notes      |

|----------------|--------------------------------------------------------|------|-----|------|------|------------|

| V_LDO_SYS_IN   | LDO system input voltage:                              |      |     |      |      |            |

|                | LDO_SYS input supply voltage in<br>Regulation mode     | 1.86 | -   | 3.6  | V    | 1          |

|                | LDO_SYS input supply voltage in Bypass<br>mode         | 1.8  | -   | 1.98 | V    | 1          |

|                | LDO_SYS input in Fuse programming mode                 | 2.75 | -   | 3.6  | V    | 1          |

| V_LDO_SYS_OUT  | LDO system output voltage:                             |      |     |      |      |            |

|                | Normal drive strength mode                             | 1.71 | 1.8 | 1.98 | V    | 2, 3, 4, 5 |

|                | Fuse Programming mode                                  | 2.25 | 2.5 | 2.75 | V    | 2, 3, 4, 5 |

| I_LDO_SYS_LOAD | LDO system max load current at LDO output:             |      |     |      |      |            |

|                | Normal drive strength mode                             | -    | -   | 50   | mA   |            |

|                | Low drive strength mode                                | -    | -   | 2    | mA   |            |

|                | Fuse programming mode                                  | -    | -   | 40   | mA   |            |

| I_LDO_SYS_IN   | LDO system input current consumption:                  |      |     |      |      |            |

|                | Normal drive strength mode                             | -    | 100 | -    | μA   | 6          |

|                | Low drive strength mode                                | -    | 70  | -    | nA   | 6          |

| linrush        | LDO core inrush current                                | -    | -   | 120  | mA   |            |

| COUT           | LDO core external output capacitor                     | -    | 1.5 | 10   | μF   |            |

| Cdec           | LDO core external decoupling capacitor                 | -    | 0.1 | -    | μF   |            |

| ESR            | External output capacitor equivalent series resistance | -    | 30  | -    | mΩ   |            |

#### Note:

1. The regulator automatically switches to pass through, that is the driver of the regulator is fully on, with the supply below 1.95 V.

**Power Management Hardware for the KW47**

- 2. The LDO\_SYS converter generates 1.8 V by default at the VOUT\_SYS. The VOUT\_SYS can be used to power the VDD\_SYS, VDD\_RF, VDD\_IO\_X, and VDD\_ANA, as long as the max ILOAD is not exceeded.

- 3. The VOUT SYS and VDD SYS are connected.

- 4. The VDD IO D must be at least 150 mV higher than the desired VOUT\_SYS.

- 5. The LDO\_SYS can be used to program efuse and in this configuration the output voltage can range between 2.25 V and 2.75 V.

- 6. In Normal drive strength, the LDO\_SYS draws ~100 μA for every 20 mA of load current. For an external output capacitor, the value is 1.5 μF. If the capacitor has a 10 μF value, this value must be 300 mA instead.

# 6 Smart power switch - VBAT

VBAT is a smart power and low-resistance switch that works with the power management system to implement the power-saving mechanisms. It can be used to switch off all or some power domains to obtain the lowest power consumption possible.

However, if the KW47 is running on a battery with limited peak current, do not use the smart power switch constantly. The DC-DC introduces a high inrush current during the DC-DC startup, which can shorten the lifespan of the battery. Therefore, for battery-powered applications, it is recommended to use the smart power switch carefully when the system is powered off for an extended period. This switch can also be used for power distribution control of external loads on the board as load and voltage requirements are within the VBAT specifications. For some typical configurations for the smart power switch, see <a href="Section 3.3">Section 3.3</a>.

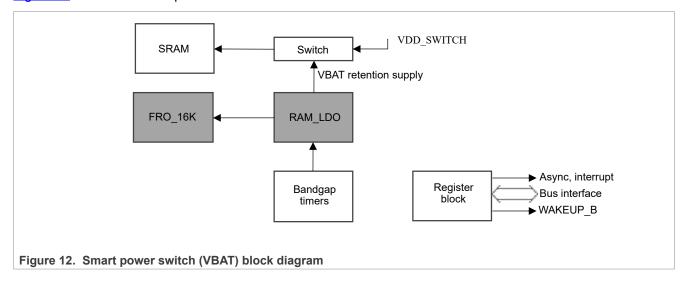

Figure 12 shows the smart power switch architecture in the KW47 MCU.

# 6.1 Smart power switch hardware

The smart power switch can switch on/off a load but also includes hardware embedded on it, which the independent power domain VDD-SWITCH supplies. This hardware offers extra features to fulfill many application requirements for the KW47 MCU.

The following sections describe the smart power switch hardware and its capabilities.

#### 6.1.1 VBAT FRO16K and bandgap timers

The smart power switch has an internal 16.384 kHz oscillator, which the VDD- SWITCH power domain known as the VBAT FRO16K oscillator supplies. The FRO16K can remain active in all Low-power modes. The

**Power Management Hardware for the KW47**

FRO16K is used by the VBAT. However, some other peripherals in the KW47 can also use it. For more details, see the *KW47 Reference Manual* (document <u>KW47RM</u>).

In addition to the FRO16K oscillator, the smart power switch has the following two bandgap timers:

- · Bandgap timer 0

- · Bandgap timer 1

Both the bandgap timers use FRO16K as a reference clock to determine its counter value and are supplied with the VDD-SWITCH power domain. The bandgap timers can turn on the smart power switch when the timer count expires. The bandgap timers can also program the VBAT to switch off the system for a determined period. In the KW47 MCU, the bandgap timers can be configured as follows:

- The bandgap timer 0 timeout can be configured in the range of 7.8125 ms to 1 s

- The bandgap timer 1 timeout ranges from 1 s to 65535 s

Before starting any bandgap timer, turn on the FRO16K (VBAT -> FROCTLA[FRO\_EN] = 1) and enable the LDO RAM bandgap bit (VBAT -> LDOCTLA[BG\_EN] = 1).

#### 6.1.2 VBAT LDO RAM retention and SRAM retention array

When the smart power switch controls all power domains, the application running on the device resets the execution when the VBAT switches off and on. As a result, the application context is lost due to the loss of power on the system. To manage this use case, the smart power switch includes an LDO that can supply an 8 kB SRAM array dedicated to retain the application data when the VBAT is turned off. This feature enables quick recovery after the POR sequence of the device when the smart power switch turns on again.

In general, the LDO RAM retention regulator can be used to keep the power of the SRAM retention at any time or through any Low-power mode in which the application data is lost. However, all access to the SRAM retention address range is not allowed while the LDO RAM is powering this memory. Otherwise, any attempt to access the memory triggers a fault condition. The 8 kB SRAM retention array address range is from 0x2001\_A000 to 0x2001\_BFFF, which corresponds to the STCM5 in the KW47 device. The STCM5 supports the ECC in the KW47 devices.

#### 6.1.2.1 VBAT LDO RAM enable sequence

To enable the VBAT LDO RAM retention regulator, perform the following steps:

- 1. Enable the VBAT FRO16K oscillator: VBAT -> FROCTLA[FRO\_EN] = 1.

- 2. Enable the LDO RAM bandgap bit: VBAT -> LDOCTLA[BG\_EN] = 1.

- 3. To achieve the lowest power consumption, set the LDO RAM in Low-power refresh mode by enabling the following bit: VBAT -> LDOCTLA[REFRESH\_EN] = 1.

- 4. Enable the LDO RAM regulator: VBAT -> LDOCTLA[LDO\_EN] = 1.

- 5. Wait until the LDO\_RDY flag is set, polling the VBAT -> STATUSA[LDO\_RDY] bit.

#### 6.1.2.2 Powering the SRAM retention memory with VBAT LDO RAM regulator

As a default setting, the VDD\_CORE domain powers the SRAM retention memory. Therefore, if the application requires the use of a memory retention feature, the software must configure the proper registers to move the SRAM power supply from the VDD\_CORE domain to the VBAT LDO RAM regulator. As explained in Section 6.1.2, any attempt to read or write the SRAM retention memory while it is supplied with the LDO RAM regulator results in a fault. Therefore, the application data must be saved in the SRAM address range before switching the memory power supply.

To configure the VBAT LDO RAM regulator to supply the SRAM retention memory, perform the following steps:

1. Enable the VBAT LDO RAM. For more details, see Section 6.1.2.1.

**Power Management Hardware for the KW47**

- 2. Configure VBAT -> LDORAMC[ISO] = 1.

- 3. Configure VBAT -> LDORAMC[SWI] = 1.

Once the VBAT turns on, the software must reverse these steps to switch the SRAM memory power to the VDD CORE domain and be able to access the SRAM retention memory and load the application context.

- 1. Configure VBAT -> LDORAMC[SWI] = 0.