## **AN14685**

# PF9453 QFN schematic and layout guidelines Rev. 1.0 — 9 June 2025

**Application note**

#### **Document information**

| Information | Content                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------|

| Keywords    | PF9453, QFN, PMIC                                                                                     |

| Abstract    | This application note provides guidelines for schematic and good layout practices for PF9453 QFN PMIC |

PF9453 QFN schematic and layout guidelines

## 1 Introduction

This application note outlines schematic and PCB layout design guidelines for the PF9453 QFN Power Management IC (PMIC). While applicable to all PF9453 QFN variants (MPF9453AXMXXHN), the term PF9453HN is used throughout for simplicity.

The PF9453HN is a highly integrated PMIC designed to deliver a complete power management solution for NXP's i.MX91/93 processor families, as well as other industrial and IoT platforms with similar power requirements.

## 2 Packaging

The PF9453HN is designed for both consumer and industrial applications and is available in a 40-pin HVQFN package with a 5 mm × 5 mm body size and 0.4 mm pitch. Refer to Table 1 for the package drawing information.

Table 1. Package drawing information

| Package | Description                                                | Package outline drawing number |

|---------|------------------------------------------------------------|--------------------------------|

| HVQFN40 | 40-pin QFN, 5.0 mm x 5.0 mm with exposed pad, 0.4 mm pitch | SOT2231-1                      |

#### 3 PF9453HN reference schematic

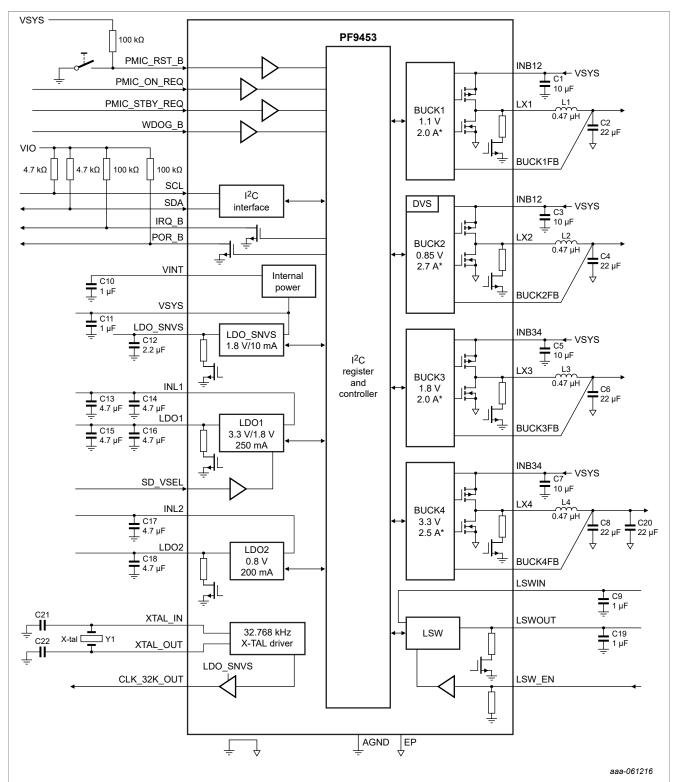

PF9453HN reference schematic with i.MX 91 processor is illustrated in Figure 1.

#### PF9453 QFN schematic and layout guidelines

Note\*: Output current of PF9453 regulators changes depending on the part number; refer to Table 1 in the PF9453DS Figure 1. PF9453HN (OTP configuration A1) application schematic

The schematic and design reference for PF9453HN can be found at the following link:

https://www.nxp.com/PF9453AHN-EVB

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

PF9453 QFN schematic and layout guidelines

## 4 Schematic design guidelines

This section describes the guidelines related to the schematic design process.

## 4.1 Pin connection guidelines

<u>Table 2</u> provides the recommended pin connections for the PF9453HN. These guidelines help ensure that the PF9453HN operates correctly.

Note: VIN refers to Input Voltage of the PMIC.

Table 2. PF9453HN pin connection guidelines

|             | -    |                              | 3                                                                                                                   |                                                                                                                |                                                                       |

|-------------|------|------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Pin Symbol  | Pin  | Pin Type                     | Pin Function                                                                                                        | Recommended Connection                                                                                         | Recommended connection when not used                                  |

| LDO2        | 1    | Power                        | LDO2 output                                                                                                         | Bypass with a 4.7μF/6.3V to GND                                                                                | Leave floating                                                        |

| INL2        | 2    | Power                        | LDO2 input                                                                                                          | Bypass with a 4.7µF/6.3V to GND                                                                                | Connect to VIN                                                        |

| BUCK2FB     | 3    | Analog input                 | BUCK 2 feedback                                                                                                     | Connect to the BUCK 2 output rail close to the load                                                            | Connect to INB12                                                      |

| LX2         | 4, 5 | Power                        | BUCK 2 switching node                                                                                               | Connect to a 0.47µH inductor                                                                                   | Leave floating                                                        |

| INB12       | 6, 7 | Power                        | BUCK 1 and BUCK 2 inputs                                                                                            | Bypass with two 10µF/6.3V ceramic capacitors                                                                   | Connect to VIN                                                        |

| LX1         | 8, 9 | Power                        | BUCK 1 switching node                                                                                               | Connect to a 0.47µH inductor                                                                                   | Leave floating                                                        |

| BUCK1FB     | 10   | Analog input                 | BUCK 1 feedback                                                                                                     | Connect to the BUCK 1 output rail close to the load                                                            | Connect to INB12                                                      |

| POR_B       | 11   | Digital<br>output            | Power On reset output                                                                                               | Place a pull-up resistor from $20k\Omega$ to $220k\Omega$ to a system I/O supply rail                          | Leave floating                                                        |

| SCL         | 12   | Digital<br>input             | I <sup>2</sup> C serial clock                                                                                       | Place a 4.7 k $\Omega$ pull-up resistor to a system I/O supply rail                                            | Place a 4.7 kΩ pull-<br>up resistor to a<br>system I/O supply<br>rail |

| SDA         | 13   | Digital<br>input /<br>output | I <sup>2</sup> C serial data                                                                                        | Place a 4.7 kΩ pull-up resistor to a system I/O supply rail                                                    | Place a 4.7 k $\Omega$ pullup resistor to a system I/O supply rail    |

| CLK_32K_OUT | 14   | Digital<br>output            | 32.768kHz clock CMOS output with LDO_SNVS power rail                                                                | Connect to the clock input signal of the processor or other peripheral                                         | Leave floating                                                        |

| PMIC_ON_REQ | 15   | Digital<br>input             | PMIC ON input from<br>application processor.<br>When it is asserted high,<br>the device starts power<br>on sequence | Connect to PMIC_ON_REQ pin from the processor. Pull-up via $8~k\Omega$ - 100 $k\Omega$ to LDO_SNVS if required | Place a 100k pull-<br>up resistor to LDO_<br>SNVS rail                |

| XTAL_IN     | 16   | Analog<br>input              | 32.768kHz crystal oscillator input                                                                                  | Connect to crystal oscillator and bypass with a capacitor to GND (18pF typically)                              | Connect to GND                                                        |

| XTAL_OUT    | 17   | Analog<br>output             | 32.768kHz crystal oscillator output                                                                                 | Connect to crystal oscillator and bypass with a capacitor to GND (18pF typically)                              | Leave floating                                                        |

AN14685

## PF9453 QFN schematic and layout guidelines

Table 2. PF9453HN pin connection guidelines...continued

| Pin Symbol Pin |                                                                                                                                                                                   | Pin Pin Type Pin Function |                                                                               | Recommended Connection                                                                         | Recommended connection when not used |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------|

| PMIC_RST_B     | 18                                                                                                                                                                                | Digital input             | PMIC reset input pin.<br>Once it is asserted low,<br>PMIC performs cold reset | Connect to reset signal from processor                                                         | Connect to VIN                       |

| IRQ_B          | 19                                                                                                                                                                                | Digital<br>output         | PMIC interrupt pin, open drain output requiring external pull up resistor     | Place a pull-up resistor from $20k\Omega$ to $220k\Omega$ to a system I/O supply rail          | Leave floating                       |

| WDOG_B         | 20                                                                                                                                                                                | Digital<br>input          | Watchdog reset input from application processor                               | Connect to watchdog reset signal from processor                                                | Connect to VIN                       |

| BUCK4FB        | 21                                                                                                                                                                                | Analog input              | BUCK 4 feedback                                                               | Connect to the BUCK 4 output rail close to the load.                                           | Connect to INB34                     |

| LX4            | 22,<br>23                                                                                                                                                                         | Power                     | BUCK 4 switching node                                                         | Connect to a 0.47µH inductor                                                                   | Leave floating                       |

| INB34          | 24,<br>25,<br>26                                                                                                                                                                  | Power                     | BUCK 3 and BUCK 4 inputs                                                      | Bypass with two typical 10µF/6.3V ceramic capacitors                                           | Connect to VIN                       |

| LX3            | 27, Power BUCK 3 switching node Connect to a 0.47μH inductor                                                                                                                      |                           | Leave floating                                                                |                                                                                                |                                      |

| BUCK3FB        | FB 29 Analog BUCK 3 feedback Connect to the BUCK 3 output ra                                                                                                                      |                           | Connect to the BUCK 3 output rail close to the load.                          | Connect to INB34                                                                               |                                      |

| LSW_EN         | N Digital Load switch enable input. Connect to processor I/O pin for load switch enable input down resistor                                                                       |                           |                                                                               | Leave floating                                                                                 |                                      |

| PMIC_STBY_REQ  | IC_STBY_REQ 31 Digital input Standby mode input from application processor. When it is asserted high, device enters STANDBY mode.  Connect to PMIC_STBY_REQ signal from processor |                           |                                                                               | Connect to GND                                                                                 |                                      |

| LSWIN          | 32                                                                                                                                                                                | Power                     | Load Switch input                                                             | Bypass with a 1µF/16V to GND                                                                   | Connect to GND                       |

| LSWOUT         | 33                                                                                                                                                                                | Power                     | Load Switch output                                                            | Bypass with a 1µF/16V to GND                                                                   | Leave floating                       |

| AGND           | 34                                                                                                                                                                                | GND                       | Analog GND                                                                    | It should be connected to GND plane through a via. Do not short directly to EPAD on top layer. | N/A                                  |

| SD_VSEL        | 35                                                                                                                                                                                | Digital input             | LDO1 voltage selection input.                                                 | Connect to processor I/O pin                                                                   | Connect to GND                       |

| VINT           | 36                                                                                                                                                                                | Power                     | Internal power supply output                                                  | Bypass with 1µF/16V to GND                                                                     | N/A                                  |

| VSYS           | 37                                                                                                                                                                                | Power                     | Internal power input                                                          | Bypass with a 1 μF/16V to GND, connect to VIN                                                  | N/A                                  |

| LDO_SNVS       | 38                                                                                                                                                                                | Power                     | LDO_SNVS output                                                               | Bypass with a 2.2µF/16V to GND                                                                 | Leave floating                       |

| LDO1           | 39                                                                                                                                                                                | Power                     | LDO1 output                                                                   | Bypass with 2 x 4.7μF/6.3V to GND                                                              | Leave floating                       |

| INL1           | 40                                                                                                                                                                                | Power                     | LDO1 input                                                                    | Bypass with 2 x 4.7µF/6.3V to GND                                                              | Connect to VIN                       |

| EPAD           | 41                                                                                                                                                                                | GND                       | Exposed pad                                                                   | Connect this pad to the inner and external GND planes through                                  | N/A                                  |

#### PF9453 QFN schematic and layout guidelines

Table 2. PF9453HN pin connection guidelines...continued

| Pin Symbol | Pin | Pin Type | Pin Function |                                                       | Recommended connection when not used |

|------------|-----|----------|--------------|-------------------------------------------------------|--------------------------------------|

|            |     |          |              | multiple vias to allow effective thermal dissipation. |                                      |

## 4.2 BUCK converter guidelines

This section describes guidelines for selecting passive components for each BUCK converter of the PF9453HN.

#### 4.2.1 Inductor selection for BUCK converters

Each BUCK converter in the **PF9453HN** typically uses a **0.47 μH inductor**, which must be appropriately rated for both **DC resistance (DCR)** and **saturation current**. The inductor's DCR directly impacts the converter's efficiency—therefore, selecting an inductor with **low DCR** is essential for achieving high efficiency.

The table below lists inductors with low DCR suitable for this application.

In addition to DCR, **AC losses**—which depend on the inductor's material and construction—can also significantly affect efficiency. For accurate assessment of AC losses in a specific use case, it is recommended to consult the inductor manufacturer.

Below are the equations needed to calculate the **peak-to-peak inductor ripple current** ( $\Delta I_L$ ) and **maximum inductor current** ( $I_{L,max}$ ), and how to choose a good inductor for a specific use case.

#### 4.2.1.1 Inductor current calculations

To select a suitable inductor, it's important to calculate both the peak-to-peak ripple current and the maximum inductor current. The process begins with determining the duty cycle (D) of the BUCK converter, taking into account conduction losses.

Equation 1 shows how to do this calculation.

$$D = \frac{Vout \left[ 1 + \frac{R_{eC}}{R} \right]}{Vin\_max} \tag{1}$$

#### Where:

- D = duty cycle

- Vout = BUCK output voltage (V)

- Vin\_max = Maximum BUCK Input voltage (V)

- $R = \text{Output load } (\Omega)$

- $R_{ec}$  = Equivalent resistance in conduction mode ( $\Omega$ )

As can be seen from the above equation, NXP recommends calculating the duty cycle (D) considering the **equivalent resistance in conduction mode** ( $R_{ec}$ ) to obtain an accurate result, <u>Equation 2</u> shows how to calculate ( $R_{ec}$ ).

$$R_{ec} = R_L + (D)(HS_R_{DSON}) + (1-D)(LS_R_{DSON})$$

(2)

Where:

• D = duty cycle

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

#### PF9453 QFN schematic and layout guidelines

- $R_L$  = Inductor series resistance ( $\Omega$ ).

- $HS_R = R_{DSON} = High$  Side P-FET Drain to Source Resistance during ON state ( $\Omega$ ).

- $LS_{DSON}$  = Low Side N-FET Drain to Source Resistance during ON state ( $\Omega$ ).

In addition to <u>Equation 2</u>, there is a simplified alternative in which the D value is replaced with an ideal value, output voltage (Vout) divided by input voltage (Vin), substituting in the previous <u>Equation 3</u> is obtained.

$$R_{ec} \approx R_L + \frac{Vout}{Vin\_max} x \, HS\_R_{DSON} + \left(1 - \frac{Vout}{Vin\_max}\right) x \, LS\_R_{DSON} \tag{3}$$

#### Where:

- $R_L$  = Inductor series resistance ( $\Omega$ ).

- $HS_R_{DSON}$  = High Side P-FET Drain to Source Resistance during ON ( $\Omega$ ).

- $LS_{-}R_{DSON}$  = Low Side N-FET Drain to Source Resistance during ON ( $\Omega$ ).

- Vout = BUCK output voltage (V).

- Vin\_max = Maximum BUCK Input voltage (V).

With the results obtained in the equations above the *peak-to-peak inductor ripple current* can be calculated with the <u>Equation 4</u>. Finally, by adding the maximum DC current expected in the specific use case, the <u>Equation 5</u> calculates the *maximum inductor current*.

$$\Delta I_L = \frac{(Vin\_max - Vout)D}{L \times f}$$

(4)

$$I_{L\_max} = I_{out\_max} + \frac{\Delta I_L}{2} \tag{5}$$

#### Where:

- f = Switching frequency (Hz)

- L = Inductance (H)

- $\Delta I_L$  = peak-to-peak inductor ripple current (A)

- $I_{L max}$  = Maximum inductor current (A)

- I<sub>out max</sub> = Maximum output DC current (A)

The saturation current of the inductor must be rated higher than the *maximum inductor current* as calculated with <u>Equation 5</u>. This is needed because during a heavy load transient the inductor current raises above the calculated value.

A conservative approach is to select the inductor current rating for the calculated maximum switching current ( $I_{out\ max}$ ).

#### 4.2.1.2 Recommended inductors for PF9453HN

Table 3 shows possible inductor list for each BUCK converter on PF9453HN.

Table 3. Tested inductor list

| BUCK             | Vendor |                    | Inductance<br>(µH) | Size (mm)            | DCR (mΩ) | Isat (A) | Inom (A) |

|------------------|--------|--------------------|--------------------|----------------------|----------|----------|----------|

| BUCK1,<br>BUCK2, | Murata | DFE252010P-R47M=P2 | 0.47               | 2.50 mm x<br>2.00 mm | 35       | 5.0      | 3.5      |

AN14685

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved

#### PF9453 QFN schematic and layout guidelines

Table 3. Tested inductor list...continued

| BUCK             | Vendor |                 | Inductance<br>(µH) | Size (mm)           | DCR (mΩ) | Isat (A) | Inom (A) |

|------------------|--------|-----------------|--------------------|---------------------|----------|----------|----------|

| BUCK3,<br>BUCK4. | Murata | DFE21CCNR47MELL | 0.47               | 2.00 mm x<br>1.2 mm | 29       | 4.8      | 4.1      |

#### 4.2.2 Output capacitor selection for BUCK converters

The fast-response adaptive constant ON-time control scheme of the BUCK converters implemented in the PF9453HN allows the use of small ceramic capacitors—typically 22 µF—without causing significant output voltage undershoot or overshoot during heavy load transients. Ceramic capacitors with low ESR (Equivalent Series Resistance) values help minimize output voltage ripple. The table below shows the recommended capacitors for a typical use case.

When ceramic output capacitors are used, their RMS ripple current rating generally meets the application requirements. For completeness, the RMS ripple current is calculated using Equation 6.

$$I_{RMS\_COUT} = \Delta I_L x \frac{1}{2\sqrt{3}} \tag{6}$$

#### Where:

- $I_{RMS\ COUT}$  = Output capacitor RMS ripple current (A)

- $\Delta I_L$  = Peak-to-peak inductor ripple current (A)

At high load currents—where the nominal load current exceeds half of the ripple current ( $\Delta I_L$ )—the inductor operates in Continuous Conduction Mode (CCM), and the PF9453HN switches to Pulse Width Modulation (PWM) mode. In this mode, the total output voltage ripple is the sum of:

- 1. The peak voltage caused by the output capacitor's ESR, and

- 2. The voltage ripple caused by the capacitor's charging and discharging.

Equation 7 provides a good approximation of the output voltage ripple:

$$\Delta Vout \approx \Delta I_L x \left( \frac{1}{8 \times Cout \times f} + ESR \right)$$

(7)

#### Where:

- Δ Vout = BUCK output ripple voltage (V)

- Cout = Output capacitance (F)

- ESR = Equivalent Series Resistance (Ω)

- $\Delta I_L$  = Peak to peak inductor ripple current (A)

- *f* = Switching frequency (Hz)

Table 4. Recommended output capacitors

| Ref     | Block | Pin          | Part number     | Impedance  z  (Ω) at 2Mhz. | Size [mm] | Value     |

|---------|-------|--------------|-----------------|----------------------------|-----------|-----------|

| C2      | BUCK  | BUCK1 Output | GRM158C80G226ME | 6.0mΩ                      | 1005      | 22 µF     |

| C4      | BUCK  | BUCK2 Output | GRM158C80G226ME | 6.0mΩ                      | 1005      | 22 µF     |

| C6      | BUCK  | BUCK3 Output | GRM158C80G226ME | 6.0mΩ                      | 1005      | 22 µF     |

| C8, C20 | BUCK  | BUCK4 Output | GRM158C80G226ME | 6.0mΩ                      | 1005      | 22 µF x 2 |

AN14685

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved

#### PF9453 QFN schematic and layout guidelines

The highest output voltage ripple occurs at the highest input voltage (V<sub>IN</sub>).

At low load currents—where the nominal current is less than half of the ripple current—the PF9453HN operates in Pulse Frequency Modulation (PFM) mode. In this mode, the output voltage ripple depends primarily on the output capacitance. For more details on ripple behavior in this mode, refer to the section <a href="Expected ripple in DCM mode">Expected ripple in DCM mode</a>.

## 4.2.3 Expected ripple in DCM mode

When the BUCK converter operates in Discontinuous Conduction Mode (DCM), the expected output voltage ripple can be estimated using <u>Equation 8</u>.

$$\Delta \ Vout \approx \frac{1}{Cout \ x \ 2} \ x \left( \frac{Vin\_max \cdot Vout}{L} \ x \ \frac{Vout}{Vin\_max \ x \ f} - ILoad \right) x \left( \frac{1}{f} \ - \frac{Iload \ x \ L}{Vin\_max \cdot Vout} \ - \frac{Iload \ x \ L}{Vout} \ \right) \ + ESR \left( \frac{Vin\_max \cdot Vout}{L} \ x \ \frac{Vout}{Vin\_max \ x \ f} \right)$$

(8)

#### Where:

- Cout = Output capacitance (F).

- Vout = BUCK output voltage (V).

- Vin\_max = Maximum BUCK Input voltage (V).

- ESR = Equivalent Series Resistance (Ω).

- L = Inductance (H).

- ILoad = Nominal output current (A)

- f = Switching frequency (Hz).

**Note:** The largest ripple occurs when the nominal output current approaches zero and the input voltage approaches its maximum value.

#### 4.2.4 Input capacitor selection for BUCK converters.

A low-ESR input capacitor is highly recommended for optimal input voltage filtering and to minimize interference with other circuits caused by high input voltage spikes—an inherent characteristic of BUCK converters. Each DC-DC converter requires a 10 µF ceramic input capacitor on its input pins. The input capacitance can be increased without limitation to further improve input voltage filtering.

See Table 5 for recommended input capacitors.

Table 5. Recommended input capacitors

| Ref    | Block           | Pin   |                 | Size<br>[mm] | Value     |

|--------|-----------------|-------|-----------------|--------------|-----------|

| C1, C3 | BUCK1 and BUCK2 | INB12 | GRM188R60J106ME | 1608         | 10 μF x 2 |

| C5, C7 | BUCK3 and BUCK4 | INB34 | GRM188R60J106ME | 1608         | 10 μF x 2 |

#### 4.3 Recommended capacitors for PF9453HN internal power and load switch pins

To ensure stable operation and minimize noise, the internal power input (VSYS), internal power supply output (VINT), and load switch pins (LSWIN and LSWOUT) must each be bypassed with low-ESR ceramic capacitors. The table below lists the recommended capacitor values and part numbers for these critical pins:

Table 6. Recommended capacitors for internal power and load switch pins

| Ref | Block | Pin  | Part number     | Size [mm] | Value |

|-----|-------|------|-----------------|-----------|-------|

| C10 | VINT  | VINT | GRM155R61C105KA | 1005      | 1 μF  |

| C11 | VSYS  | VSYS | GRM155R61C105KA | 1005      | 1 μF  |

AN14685 All information provided in this document is subject to legal disclaimers. © 2025 NXP B.V. All rights reserved

#### PF9453 QFN schematic and layout guidelines

Table 6. Recommended capacitors for internal power and load switch pins...continued

| Ref | Block | Pin    | Part number     | Size [mm] | Value |

|-----|-------|--------|-----------------|-----------|-------|

| C9  | LSW   | LSWIN  | GRM155R61C105KA | 1005      | 1 μF  |

| C17 | LSW   | LSWOUT | GRM155R61C105KA | 1005      | 1 μF  |

Each of these capacitors should be placed as close as possible to the corresponding pin to maximize effectiveness

## 4.4 Recommended capacitors for LDO input and output pins

All input and output pins of the LDOs must be bypassed with low-ESR ceramic capacitors to ensure stable voltage regulation and minimize output noise. <u>Table 7</u> lists the recommended capacitor values and part numbers for each LDO pin.

Table 7. Recommended LDO capacitors

| Ref      | Block           | Pin      | Part number     | Size [mm] | Value      |

|----------|-----------------|----------|-----------------|-----------|------------|

| C13, C14 | LDO1 input      | INL1     | GRM155R60J475ME | 1005      | 4.7 µF x 2 |

| C15, C16 | LDO1 output     | LDO1     | GRM155R60J475ME | 1005      | 4.7 µF x 2 |

| C17      | LDO2 input      | INL2     | GRM155R60J475ME | 1005      | 4.7 µF     |

| C18      | LDO2 output     | LDO2     | GRM155R60J475ME | 1005      | 4.7 µF     |

| C12      | LDO_SNVS output | LDO_SNVS | GRM155R61C225KE | 1005      | 2.2 µF     |

#### 4.5 Crystal driver components selection

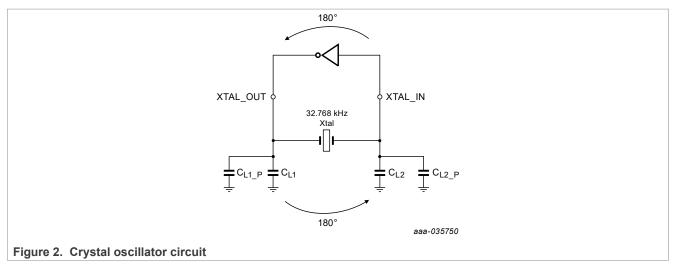

The crystal oscillator circuit (see <u>Figure 2</u>) uses two load capacitors, CL1 and CL2, which, together with the crystal's internal inductance, provide the necessary 180° phase shift for the feedback loop.

From the crystal's perspective, these capacitors are effectively in series through ground. Therefore, when using two identical capacitors, each must have a value that is twice the required load capacitance of the crystal. It's also important to account for PCB parasitic capacitance when calculating the appropriate capacitor values, as shown in Equation 9.

$$C_{Load} = \frac{C'_{L1} \times C'_{L2}}{C'_{L1} + C'_{L2}} \tag{9}$$

AN14685 All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

PF9453 QFN schematic and layout guidelines

Where:

1.  $C'_{L1} = C_{L1} + C_{L1\_P}$  where CL1\_P is PCB parasitic capacitance.

2.

$$C'_{L2} = C_{L2} + C_{L2}$$

where CL2\_P is PCB parasitic capacitance.

When using equal capacitors for  $C_{L1}$  and  $C_{L2}$  and a symmetric layout with equal parasitic capacitance on both crystal pins, the effective load capacitance is shown in Equation 10.

$$C_{Load} = \frac{C_{L1} + C_{L1_P}}{2} \tag{10}$$

#### Example:

If the crystal requires a 12.5 pF load and the estimated parasitic capacitance is 7 pF per pin, the required capacitor value can be calculated accordingly:

$$C_{L1} = 2 \times C_{Load} - C_{L1\_P} = (2 \times 12.5pf) - 7pf = 18pf$$

$C_{L2} = C_{L1} = 18pf$

Table 8 lists the recommended components for the crystal driver circuit.

Table 8. Recommended components for crystal

| Ref | Block | Pin                  | Part number       | Size<br>[mm]       | Value      |

|-----|-------|----------------------|-------------------|--------------------|------------|

| C18 | XTAL  | XTAL_IN              | GCM1555C1H180JA16 | 1005               | 18 pF      |

| C19 | XTAL  | XTAL_OUT             | GCM1555C1H180JA16 | 1005               | 18 pF      |

| Y1  | XTAL  | XTAL_IN and XTAL_OUT | ABS07-32.768KHZ-T | 3.2 mm x<br>1.5 mm | 32.768 kHz |

## 5 Layout design guidelines

#### 5.1 Placement

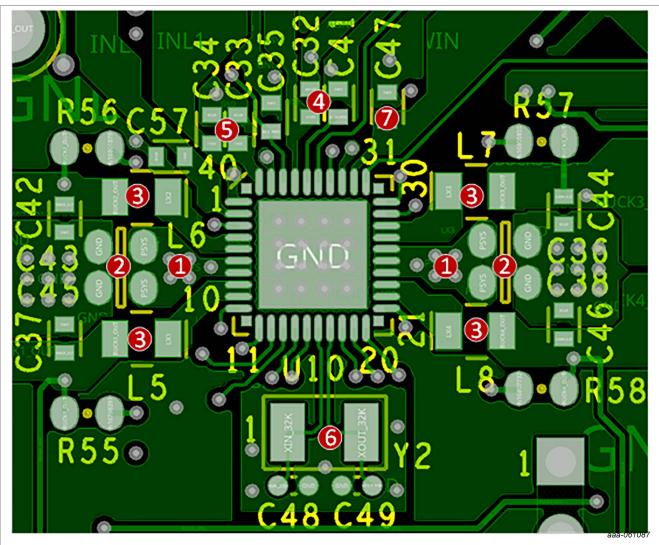

All power stage components should be placed as close as possible to the PMIC, with particular emphasis on input and output decoupling capacitors. To ensure optimal performance and minimal noise, follow this placement priority:

- 1. INB12 and INB34 vias Position these directly adjacent to the PMIC for efficient power delivery.

- 2. Input capacitors for the BUCK regulators Place as close as possible to the corresponding input pins.

- 3. Switching regulator inductors Locate next to the BUCK outputs to minimize loop area.

- 4. VSYS and VINT capacitors Position near their respective output pins.

- 5. LDO SNVS, LDO1, and LDO2 capacitors Place close to their associated LDO outputs.

- 6. Crystal and associated passive components Mount near the PMIC's crystal pins with short, symmetrical traces.

- 7. Load switch capacitors Place near the output of the load switches.

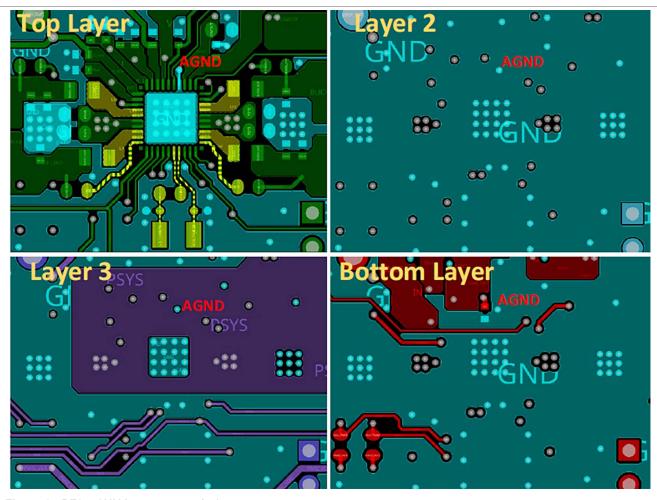

Refer to Figure 3 for detailed guidance.

PF9453 QFN schematic and layout guidelines

Figure 3. PF9453HN PCB layout example

#### 5.2 General routing guidelines

The recommended PCB stack-up for this PMIC consists of four layers:

- 1. Top signal/power layer

- 2. Ground plane

- 3. Power layer

- 4. Bottom signal layer

#### Grounding:

- Use a star grounding approach for the AGND signal, which serves as the return path for the VSYS network. Refer to Section 5.5 for more information.

- The exposed pad (EP) on the PF9455 QFN package is the main high-current ground return for all BUCK regulators. Place multiple vias directly under the EP to connect to the ground plane, ensuring low impedance and adequate copper area.

High-speed and high-current nodes:

AN14685

#### PF9453 QFN schematic and layout guidelines

• INBxx and LXx nodes carry high current and have high dl/dt characteristics, making them potential sources of EMI. Keep these traces short and wide to reduce inductance and radiated noise.

• Minimize and isolate high dv/dt LXx node areas to reduce EMI emissions.

#### Feedback and control:

The control loop regulates the output voltage at the point where the feedback trace connects to the output rail.

For optimal load regulation, connect the feedback trace close to the load and route it away from noisy signals or layers to avoid interference.

#### Power routing:

- Place all power components on the same side of the board, and route their power traces on the same layer to minimize voltage drops.

- If routing power traces between layers is necessary, do so only in low di/dt paths and use multiple vias to reduce impedance and noise coupling.

#### 5.3 I2C, crystal and IO signals

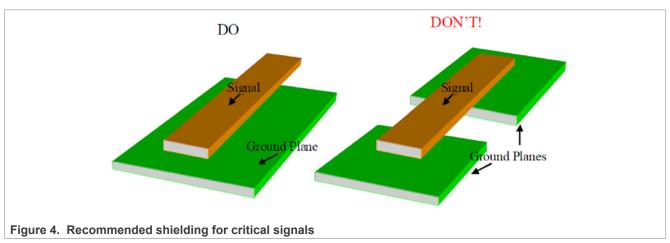

To prevent interference from nearby high-power or high-frequency signals, it is recommended to shield critical signal traces using ground planes placed on adjacent PCB layers. Ensure that the ground plane remains continuous and uniform along the entire length of the signal trace.

#### 5.4 BUCK regulators

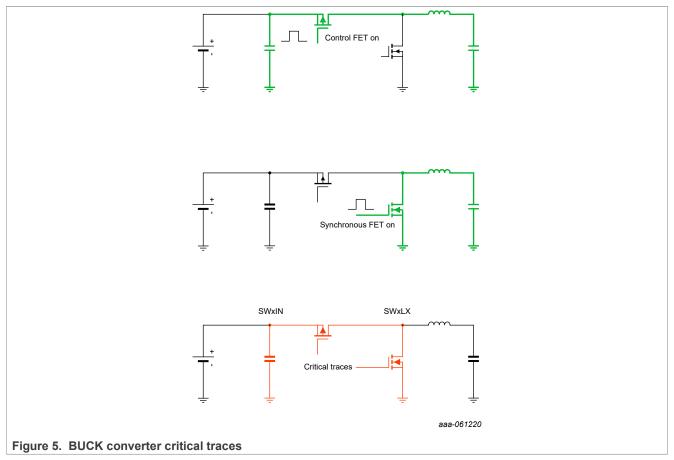

In a BUCK converter configuration, the length of the critical traces must be kept to a minimum. Critical traces refer to current paths with high dl/dt.

<u>Figure 5</u> illustrates the current paths in a BUCK converter during the ON and OFF periods of the switching cycle. These critical traces are those that conduct only during either the ON or the OFF period, as highlighted in red.

#### PF9453 QFN schematic and layout guidelines

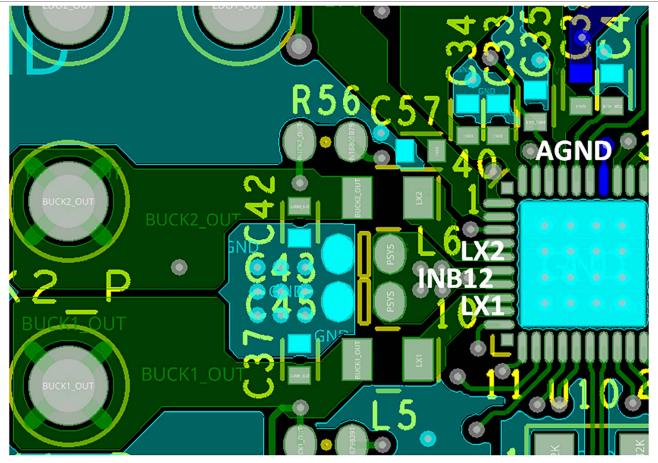

In the PF9453HN BUCK regulators, both the high-side and low-side MOSFETs are integrated within the package. Therefore, it is crucial to place the input capacitor as close as possible to the INBxx input pin and the ground.

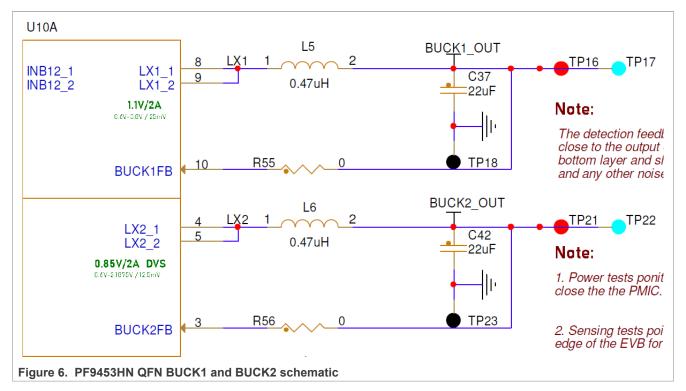

Figure 6 provides an example schematic of the BUCK regulator configuration.

#### PF9453 QFN schematic and layout guidelines

Figure 7 shows an example of layout for the BUCK regulators.

PF9453 QFN schematic and layout guidelines

Figure 7. PF9453HN BUCK1 and BUCK2 layout top layer

#### 5.5 Effective grounding

For optimal performance of the PF9453HN, the use of star grounding is essential.

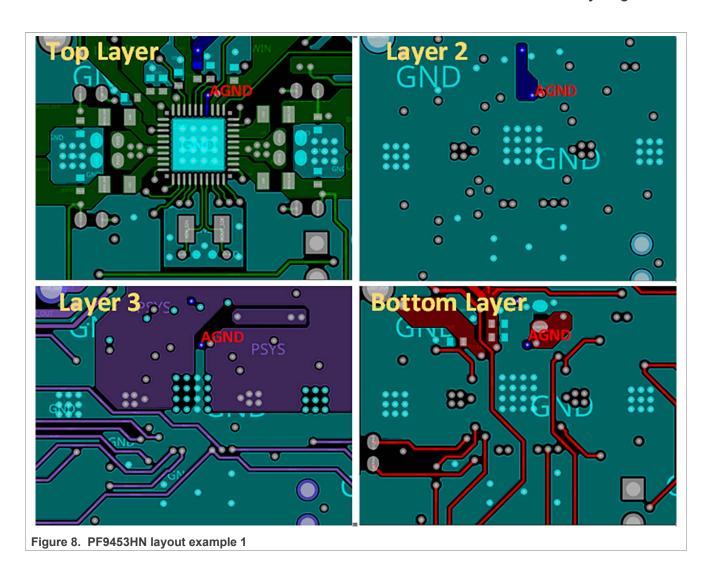

The exposed pad (EP) serves as the ground return (PGND) for all switching regulators and should be connected to the ground plane using multiple vias to ensure a low-impedance path. (See <u>Figure 8</u> and <u>Figure 9</u>.)

Pin 34 (AGND) is the signal ground and must be routed carefully to avoid coupling with high-current return paths. The following examples illustrate two effective star grounding implementations:

- Example 1:

- The AGND net (shown in dark blue) is completely isolated from the ground plane on the second layer. It connects directly to the ground pins of the input connector capacitors, maintaining a clean signal ground path.

- Example 2:

The AGND pin is connected to the ground plane on the second layer through a dedicated via. It is not connected through the EP, which helps prevent noise coupling from the switching regulator return currents that flow through the EP.

Refer to Figure 8 and Figure 9 for visual reference.

## PF9453 QFN schematic and layout guidelines

## PF9453 QFN schematic and layout guidelines

Figure 9. PF9453HN layout example 2

## 6 Revision history

#### Table 9. Revision history

| Document ID   | Release date | Description     |

|---------------|--------------|-----------------|

| AN14685 v.1.0 | 9 June 2025  | Initial version |

#### PF9453 QFN schematic and layout guidelines

## **Legal information**

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AN14685

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

## PF9453 QFN schematic and layout guidelines

## **Tables**

| Tab. 1.<br>Tab. 2. | Package drawing information2 PF9453HN pin connection guidelines | Tab. 6. | Recommended capacitors for internal power and load switch pins | 9  |

|--------------------|-----------------------------------------------------------------|---------|----------------------------------------------------------------|----|

| Tab. 3.            | Tested inductor list7                                           | Tab. 7. | Recommended LDO capacitors                                     | 10 |

| Tab. 4.            | Recommended output capacitors8                                  | Tab. 8. | Recommended components for crystal                             | 11 |

| Tab. 5.            | Recommended input capacitors9                                   | Tab. 9. | Revision history                                               | 18 |

| Figur              | es                                                              |         |                                                                |    |

| Fig. 1.            | PF9453HN (OTP configuration A1) application schematic3          | Fig. 6. | PF9453HN QFN BUCK1 and BUCK2 schematic                         | 15 |

| Fig. 2.            | Crystal oscillator circuit10                                    | Fig. 7. | PF9453HN BUCK1 and BUCK2 layout top                            |    |

| Fig. 3.            | PF9453HN PCB layout example12                                   |         | layer                                                          | 16 |

| Fig. 4.            | Recommended shielding for critical signals13                    | Fig. 8. | PF9453HN layout example 1                                      | 17 |

| Fig. 5.            | BUCK converter critical traces14                                | Fig. 9. | PF9453HN layout example 2                                      | 18 |

## PF9453 QFN schematic and layout guidelines

## **Contents**

| 1       | Introduction                           | 2  |

|---------|----------------------------------------|----|

| 2       | Packaging                              |    |

| 3       | PF9453HN reference schematic           |    |

| 4       | Schematic design guidelines            | 4  |

| 4.1     | Pin connection guidelines              |    |

| 4.2     | BUCK converter guidelines              | 6  |

| 4.2.1   | Inductor selection for BUCK converters | 6  |

| 4.2.1.1 | Inductor current calculations          | 6  |

| 4.2.1.2 | Recommended inductors for PF9453HN     | 7  |

| 4.2.2   | Output capacitor selection for BUCK    |    |

|         | converters                             | 8  |

| 4.2.3   | Expected ripple in DCM mode            | 9  |

| 4.2.4   | Input capacitor selection for BUCK     |    |

|         | converters                             | 9  |

| 4.3     | Recommended capacitors for PF9453HN    |    |

|         | internal power and load switch pins    | 9  |

| 4.4     | Recommended capacitors for LDO input   |    |

|         | and output pins                        | 10 |

| 4.5     | Crystal driver components selection    | 10 |

| 5       | Layout design guidelines               | 11 |

| 5.1     | Placement                              | 11 |

| 5.2     | General routing guidelines             | 12 |

| 5.3     | I2C, crystal and IO signals            | 13 |

| 5.4     | BUCK regulators                        |    |

| 5.5     | Effective grounding                    |    |

| 6       | Revision history                       | 18 |

|         | Legal information                      | 19 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.