# AN14664

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications Rev. 1.1 — 10 December 2025 Application note

#### **Document information**

| Information | Content                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14664, KW45, KW47, KW38, MCX W71, MCX W72                                                                           |

| Abstract    | This document describes some hardware and software solutions to minimize the peaks of current at the coin cell level. |

Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

# 1 Introduction

NXP Kinetis products (KW38/45/47 and MCX W71/72) are designed for Automotive, Industrial, and Internet of Things (IoT) applications, which may be supplied with coin cells. A typical example of a coin cell is CR2032.

This document describes some hardware and software solutions to minimize the peaks of current at the coin cell level. Such solutions are required due to the nature of the Bluetooth LE activity (a low-power mode to Active mode switching happens every few dozen milliseconds). The suitability of such a solution for an application depends on the radio power defined in the application.

These solutions are implemented on the KW4x evaluation boards. The schematics of the KW4x evaluation boards are available on <a href="https://www.nxp.com">www.nxp.com</a>. This information is also available in the KW4x / MCX W7x Minimum Bill of Materials (BoM) PDFs attached to the following pages:

- The best way to build a PCB first time right with KW45 (Automotive) or K32W1/MCXW71 (IoT/Industrial) -NXP Community

- The best way to build a PCB first time right with KW47 (Automotive) or MCX W72 (IoT/Industrial) NXP Community

# 2 Kinetis power configuration

KW4x / MCX W7x has a DC-DC converter embedded. This DC-DC converter can be set in Buck or Bypass mode. In DC-DC Buck mode, the output voltage can be set from 1.25 V to 2.5 V, depending on the radio output power (-30 dBm to +10 dBm). The Bluetooth LE sequence switches from a low-power mode (Deep-Sleep mode) to Active mode (Advertising, Connection, or Scan events). Switching the Kinetis product ON and OFF repeatedly may create peaks of current based on the defined radio output power.

The KW47 / MCX W72 products have the following new hardware features:

- The DC-DC Ramp can be trimmed to smooth the DC-DC output voltage to the desired value. This feature is implemented to avoid any peak of current at the coin cell level. KW45 / MCX W71 products do not have such a feature. Therefore, hardware recommendations are proposed to limit the peak of current below 10 mA, as recommended by coin cell manufacturers.

- The default POR DC-DC output voltage can be set in the bootloader. The default value is 1.8 V but it can be changed to 1.25 V or 1.35 V. For a coin cell application, the preferred value is 1.25 V.

These two features are not available in the KW45 / MCX W71 products. To reduce the peaks of current at the coin cell level and not to reduce the coin cell lifetime in these products, extra BoM is required.

#### 3 Hardware solutions

<u>Table 1</u> summarizes the hardware solutions for reducing peaks of current at the coin cell level. The suitability of a solution for an application depends on the radio power defined in the application.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

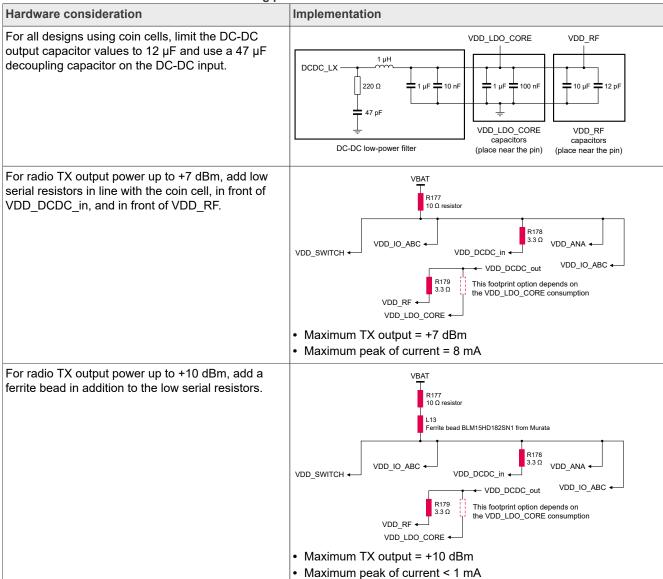

Table 1. Hardware considerations for reducing peaks of current

# 4 KW45 – Application configurations

This section describes the recommendations for minimizing the peaks of current on the coin cell while using the NXP Kinetis KW45 / MCX W71 products.

The radio TX output power defines the DC-DC output voltage. In a low-power mode, the DC-DC output voltage is set to 1.25 V. In Active mode (Advertising, Connection, or Scan events), the DC-DC output voltage is set as follows:

- 1.25 V for TX <= +0 dBm

- 1.8 V for +0 dBm < TX <= +7 dBm

- 2.5 V for TX > +7 dBm

Switching the DC-DC output from 1.25 V to 1.8 V or 2.5 V causes the charging/discharging of the capacitor bank and creates peaks of current. It is explained in detail for an application in the subsections that follow using these three use cases:

AN14664

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

- Radio TX output power <= +0 dBm

- +0 dBm < radio TX output power <= +7 dBm

- Radio TX output power > +7 dBm

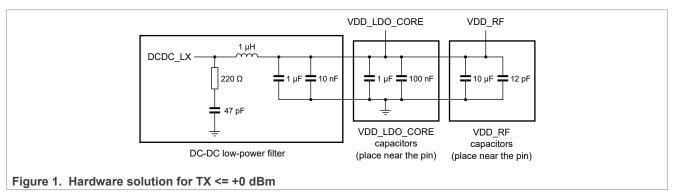

# 4.1 Radio TX output power <= +0 dBm (DCDC output = 1.25 V)

When an application requires radio TX output power only up to +0 dBm, the DC-DC output voltage is set to 1.25 V. A low-power mode also needs the same voltage (1.25 V). Therefore, no peak of current occurs when a Bluetooth LE event switches from a low-power mode to Active mode. However, this use case has a constraint at power-on reset (POR). By default, at POR and at each reset, the DC-DC output voltage is equal to 1.8 V. Therefore, the bootloader must be updated to set the default DC-DC output voltage to 1.25 V. This way, only one peak occurs when the battery is replaced with another battery. No peak occurs during application reset.

The KW45B41Z-EVK schematics recommend using the following capacitors:

- A 1 μF decoupling capacitor at each of the DC-DC output and VDD\_LDO\_CORE

- A 10 μF capacitor at VDD\_RF

Use these capacitance values for a coin cell application. It avoids overloading the DC-DC output.

The proposed hardware solution is shown in Figure 1.

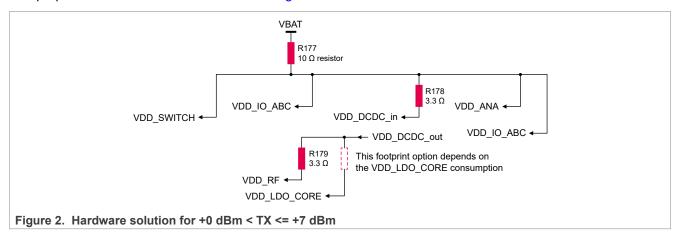

# 4.2 +0 dBm < radio TX output power <= +7 dBm (DCDC output = 1.8 V)

When an application requires radio TX output power from +0.1 dBm up to +7 dBm, the DC-DC output voltage is set to 1.8 V. Because a low-power mode uses 1.25 V voltage, a voltage gap exists between a low-power mode and Active mode. If no action is taken to fix this issue, peaks of current occur when switching from a low-power mode to Active mode.

One software solution is to set the DC-DC output voltage to 1.8 V during a low-power mode. This simple solution avoids the peaks of current but reduces the battery life (due to consumption of 1.8 V instead of 1.25 V). Therefore, this solution is not a good solution.

Another solution, which is a preferred solution, is to add components on the PCB to reduce the peaks of current. A simple hardware solution is to add three low serial resistors as follows:

- A 10  $\Omega$  resistor in line with the coin cell

- A 3.3 Ω resistor in front of VDD\_DCDC\_in

- Another 3.3 Ω resistor in front of VDD\_RF

Also, one footprint can be added (if necessary) in line with VDD\_LDO\_CORE.

These values can be fine-tuned if the overall current at VBAT is too high and can create a voltage drop that is large enough to reach the brownout (reset threshold) of the KW45 device.

AN14664

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

When used with the SDK LP\_peripheral and LP\_central applications, the proposed resistor values do not reach the reset threshold in voltage (VBAT = 2.4 V minimum) and temperature (-40 °C to +125 °C). The maximum peak of current measured is 8 mA.

In this use case (radio TX output power level), the POR creates a peak of current when the battery is replaced with another battery. This use case implementation has negligible impact on the total battery life.

The proposed hardware solution is shown in Figure 2.

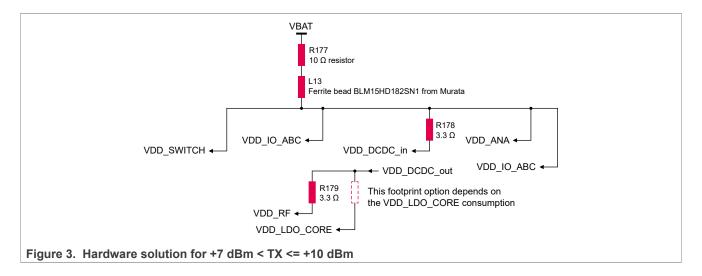

# 4.3 Radio TX output power > +7 dBm (DCDC output = 2.5 V)

When an application requires radio TX output power from +7.1 dBm to +10 dBm, the DC-DC output voltage is set to 2.5 V. Because a low-power mode uses 1.25 V voltage, a voltage gap exists between a low-power mode and Active mode. If no action is taken to fix this issue, peaks of current occur when switching from a low-power mode to Active mode.

One software solution is to set the DC-DC output voltage to 2.5 V during a low-power mode. This simple solution avoids the peaks of current but reduces battery life significantly (due to consumption of 2.5 V instead of 1.25 V). Therefore, this solution is not a good solution.

Another solution, which is a preferred solution, is to add a ferrite bead to the second hardware solution described in Section 4.2. Therefore, the hardware solution involves adding the following components:

- A ferrite bead (for example, BLM15HD182SN1 from Murata) and a low serial resistor (10 Ω) in line with the coin cell

- A 3.3  $\Omega$  resistor in front of VDD DCDC in

- Another 3.3  $\Omega$  resistor in front of VDD RF

Also, one footprint can be added (if necessary) in line with VDD LDO CORE.

These values can be fine-tuned if the overall current at VBAT is too high and can create a voltage drop that is large enough to reach the brownout (reset threshold) of the KW45 device. In this solution, the maximum peak of current measured is below 1 mA.

When used with the SDK LP\_peripheral and LP\_central applications, the proposed resistor values do not reach the reset threshold in voltage (VBAT = 2.4 V minimum) and temperature (-40 °C to +125 °C). The maximum peak of current measured is 8 mA.

In this use case (radio TX output power level), the POR creates a peak of current when the battery is replaced with another battery. This use case implementation has negligible impact on the total battery life.

The proposed hardware solution is shown in Figure 3.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

# 5 KW47 – Application configurations

KW47 / MCX W72 products have two new hardware features that help reduce/suppress the peaks of current when switching from a low-power mode to Active mode in Bluetooth LE events (Advertising, Connection, or Scan events).

# 5.1 DC-DC Ramp trim

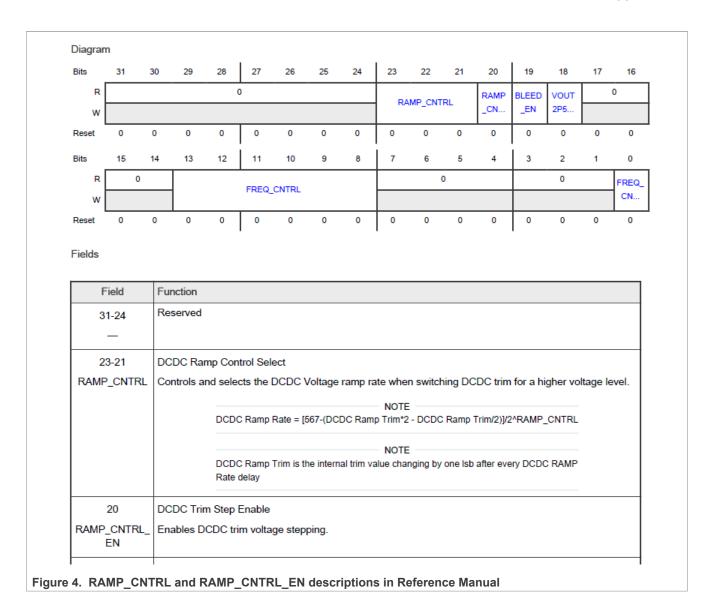

A new feature, *DC-DC Ramp trim*, allows you to smooth the DC-DC output voltage to the desired voltage value. This feature is implemented to avoid any peak of current at the coin cell level. It is implemented using the RAMP\_CNTRL and RAMP\_CNTRL\_EN bit fields of the DCDC Configuration (DCDC\_CFG) register of the KW47 device.

By default, this feature is disabled. SDK applications LP\_peripheral and LP\_central provide an option to enable this feature. It can be enabled using the <code>gBoardDcdcRampTrim\_c</code> parameter in the <code>board\_platform.h</code> file as follows:

```

/*! \brief Increase DCDC voltage with a ramp to avoid peak of current when

DCDC output is set to higher voltage.

\details gBoardDcdcRampTrim c can vary between 0 and 7

gBoardDcdcRampTrim c = 0 means feature disabled

gBoardDcdcRampTrim c = 1 is the smoothest ramp

gBoardDcdcRampTrim c = 7 is the steepest ramp

\note Cannot be applied when switching between low-power DCDC configuration

and active configuration.

The DCDC ramp feature is only functional when the SPC is configured in

Normal drive strength.

The NBU core will handle the switch to the targeted

DCDC output voltage. The targeted voltage will depend on

the TX output power requested by the application.

After exiting low-power, the NBU core will request the high power mode.

After that, it will wait for the transition to be over and the

targeted voltage to be reached before resuming any other activities.

The smoothest the ramp is, the longer the low-power exit procedure will

take time. The value 3 is a good trade-off between peak of current and

low-power exit duration.

```

AN14664

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

```

//#define gBoardDcdcRampTrim c 3

/*! \brief Enable the high power mode configuration to activate the

dynamic DCDC output voltage switching when TX output power is less

or equal to 7dBm.

* \details The NBU requires higher DCDC output voltage for radio transmits for

output power between OdBm and 7dBm. It will adapt the

DCDC output voltage depending the required TX power.

- benefit : The DCDC output voltage does not have to increase

as much as needed by the Tx ouput power requested when only the

main power domain is active.

* \note limitation : NBU cannot switch to 2.5V by itself via

high power mode voltage, a setting on SPC is also required.

NBU will not be able to handle TX power higher than 7dBm as it requires

2.5V on the DCDC output voltage.

* /

//#define gBoardDcdcEnableHighPowerModeOnNbu d 1

```

Figure 4 shows the RAMP CNTRL and RAMP CNTRL EN descriptions in KW47 Reference Manual.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

#### 5.2 Peak current measurement results

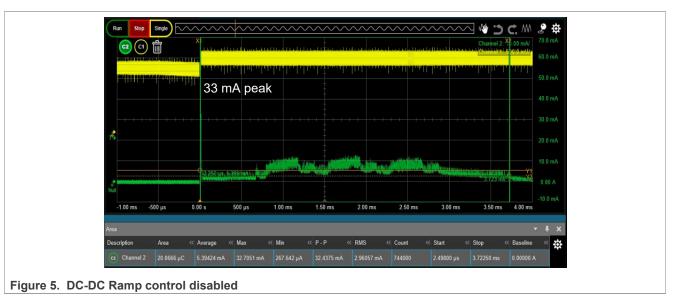

This section describes how peak current can be reduced by changing the DC-DC Ramp trim configuration. When the DC-DC Ramp control is disabled, the maximum peak current is 33 mA, as shown in Figure 5.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

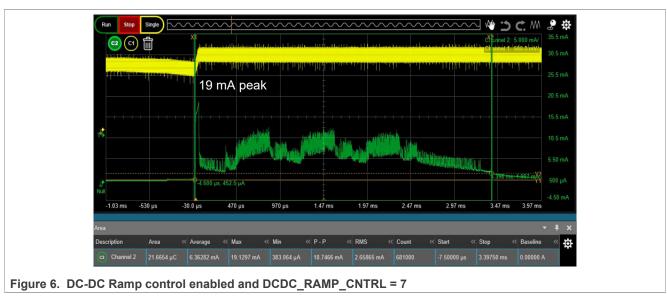

When the DC-DC Ramp control is enabled and DCDC\_RAMP\_CNTRL = 7, the maximum peak current is 19 mA, as shown in Figure 6.

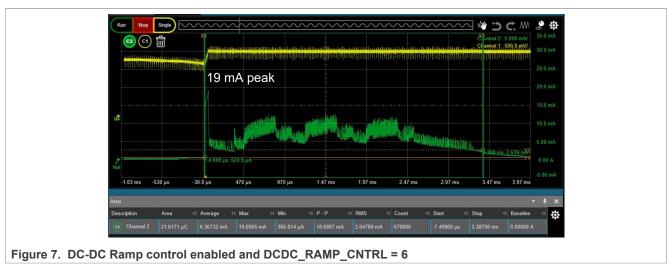

When the DC-DC Ramp control is enabled and DCDC\_RAMP\_CNTRL = 6, the maximum peak current is still 19 mA, as shown in <u>Figure 7</u>.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

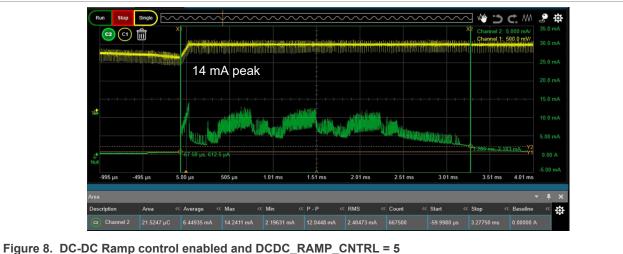

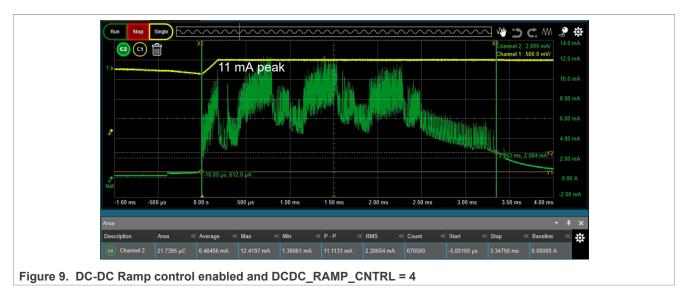

When the DC-DC Ramp control is enabled and DCDC\_RAMP\_CNTRL = 5, the maximum peak current is 15 mA, as shown in Figure 8.

When the DC-DC Ramp control is enabled and DCDC\_RAMP\_CNTRL = 4, the maximum peak current is 11 mA, as shown in Figure 9.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

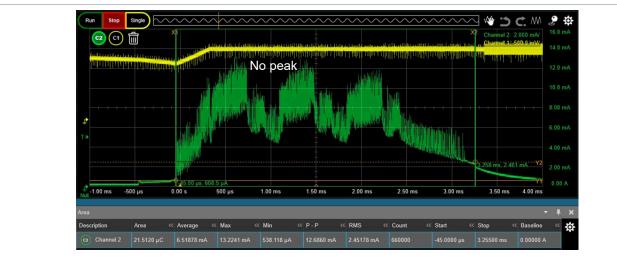

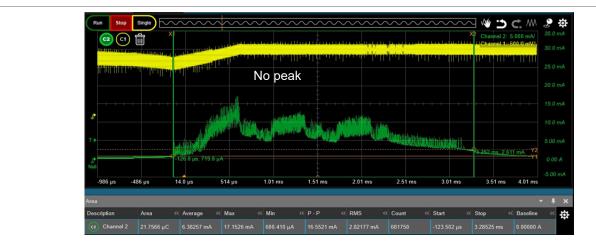

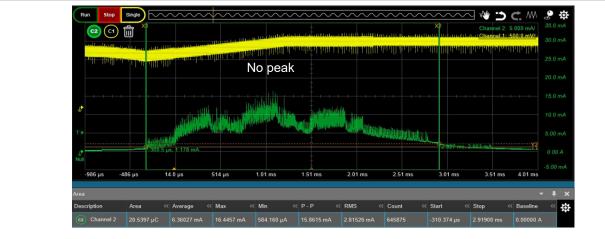

When the DC-DC Ramp control is enabled and DCDC\_RAMP\_CNTRL <= 3, no peak current occurs, as shown in <u>Figure 10</u>, <u>Figure 11</u>, and <u>Figure 12</u>.

Figure 10. DC-DC Ramp control enabled and DCDC\_RAMP\_CNTRL = 3

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

Figure 11. DC-DC Ramp control enabled and DCDC\_RAMP\_CNTRL = 2

Figure 12. DC-DC Ramp control enabled and DCDC\_RAMP\_CNTRL = 1

<u>Table 2</u> provides the peak current and other measurement results for different DC-DC Ramp trim configurations.

Table 2. Measurement results

| RAMP_CNTRL_EN and RAMP_CNTRL | Peak current<br>level (mA) | Peak duration (µs) | DC-DC Ramp<br>duration (μs) | Advertising duration (ms) | Advertising energy (μC) |

|------------------------------|----------------------------|--------------------|-----------------------------|---------------------------|-------------------------|

| EN = 0, CNTRL = x            | 33 mA                      | 16                 | Not applicable              | 3.724                     | 20.06                   |

| EN = 1, CNTRL = 7            | 19 mA                      | 40                 | 40                          | 3.395                     | 21.66                   |

| EN = 1, CNTRL = 6            | 19 mA                      | 40                 | 40                          | 3.392                     | 21.62                   |

| EN = 1, CNTRL = 5            | 14 mA                      | 97                 | 97                          | 3.347                     | 21.52                   |

| EN = 1, CNTRL = 4            | 11 mA                      | 185                | 185                         | 3.362                     | 21.73                   |

| EN = 1, CNTRL = 3            | No peak                    | No impact on TX    | 365 < preprocessing time    | 3.302                     | 21.51                   |

| EN = 1, CNTRL = 2            | No peak                    | First TX impacted  | 765 > preprocessing time    | 3.305                     | 21.75                   |

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

Table 2. Measurement results...continued

| RAMP_CNTRL_EN and RAMP_CNTRL | Peak current<br>level (mA) | Peak duration (µs) | DC-DC Ramp<br>duration (μs) | Advertising duration (ms) | Advertising energy (μC) |

|------------------------------|----------------------------|--------------------|-----------------------------|---------------------------|-------------------------|

| EN = 1, CNTRL = 1            | No peak                    | 2x TX impacted     | 1518 > preprocessing time   | 3.235                     | 20.53                   |

| EN = 1, CNTRL = 0            | No peak                    | 2x TX impacted     | 1562 > preprocessing time   | 3.290                     | 20.77                   |

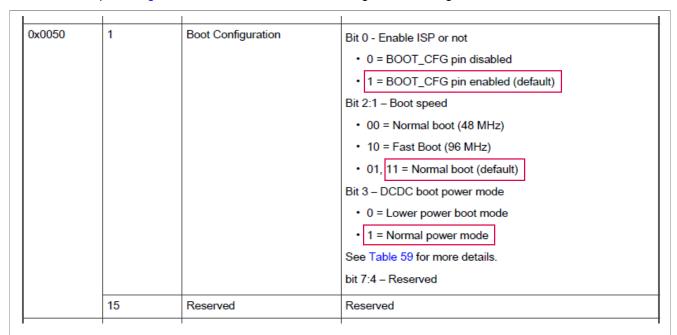

# 5.3 IFR default DC-DC output voltage

The default power-on reset (POR) DC-DC output voltage can be set in the bootloader. The default value is 1.8 V but it can be changed to 1.25 V or 1.35 V. 1.25 V is the preferred voltage for a coin cell application.

The DC-DC glitch at POR can be resolved by changing the default information register (IFR) DC-DC output voltage from 1.8 V to 1.25 V or 1.35 V.

In the IFR, the default voltage value is 1.8 V. You can change it to either 1.25 V or 1.35 V, depending on the selected boot speed. Figure 13 shows the default boot configuration settings from KW47 Reference Manual.

Figure 13. Default boot configuration settings from Reference Manual

# 6 Acronyms

Table 3 lists the acronyms used in this document.

Table 3. Acronyms

| Table of Actionyme |                      |  |  |

|--------------------|----------------------|--|--|

| Acronym            | Description          |  |  |

| ВоМ                | Bill of materials    |  |  |

| IFR                | Information register |  |  |

| LE                 | Low Energy           |  |  |

AN14664 All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

Table 3. Acronyms...continued

| Acronym | Description    |

|---------|----------------|

| POR     | Power-on reset |

# 7 Note about the source code in the document

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2025 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 8 Revision history

Table 4 summarizes the revisions to this document.

Table 4. Revision history

| Document ID   | Release date     | Description            |

|---------------|------------------|------------------------|

| AN14664 v.1.1 | 10 December 2025 | Initial public release |

| AN14664 v.1.0 | 7 May 2025       | Initial NDA release    |

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

# **Legal information**

# **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace \ensuremath{\mathsf{B.V.}}\xspace - \ensuremath{\mathsf{NXP}}\xspace \ensuremath{\mathsf{B.V.}}\xspace$  is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

**Bluetooth** — the Bluetooth wordmark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by NXP Semiconductors is under license.

Kinetis — is a trademark of NXP B.V.

# Coin Cell Hardware Recommendations for Kinetis Bluetooth LE Applications

# **Contents**

| 1   | Introduction                          | 2  |

|-----|---------------------------------------|----|

| 2   | Kinetis power configuration           | 2  |

| 3   | Hardware solutions                    |    |

| 4   | KW45 - Application configurations     | 3  |

| 4.1 | Radio TX output power <= +0 dBm       |    |

|     | (DCDC output = 1.25 V)                | 4  |

| 4.2 | +0 dBm < radio TX output power <= +7  |    |

|     | dBm (DCDC output = 1.8 V)             | 4  |

| 4.3 | Radio TX output power > +7 dBm (DCDC_ |    |

|     | output = 2.5 V)                       | 5  |

| 5   | KW47 - Application configurations     | 6  |

| 5.1 | DC-DC Ramp trim                       |    |

| 5.2 | Peak current measurement results      | 8  |

| 5.3 | IFR default DC-DC output voltage      | 13 |

| 6   | Acronyms                              |    |

| 7   | Note about the source code in the     |    |

|     | document                              | 14 |

| 8   | Revision history                      |    |

|     | Legal information                     |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.