# AN13646

# ICODE 3 TagTamper - Tamper loop design hints Rev. 1 — 29 March 2024

**Application note**

### **Document information**

| Information | Content                                                                                |

|-------------|----------------------------------------------------------------------------------------|

| Keywords    | ICODE 3 TagTamper, Tamper loop, Tamper loop design, guidelines                         |

| Abstract    | Provides guidelines for the design of a tamper loop for the ICODE 3 TagTamper product. |

ICODE 3 TagTamper - Tamper loop design hints

### 1 Introduction

ICODE 3 TagTamper features a tamper evidence function. The TagTamper feature is used to identify an unauthorized access, or the manipulation of a product, package or system. Tampering attempts are detected and permanently stored in the memory of ICODE 3 TagTamper. The information can optionally be reported to the cloud. If the TagTamper feature is enabled, the opened or closed status is mirrored in the tag's response (NDEF Message).

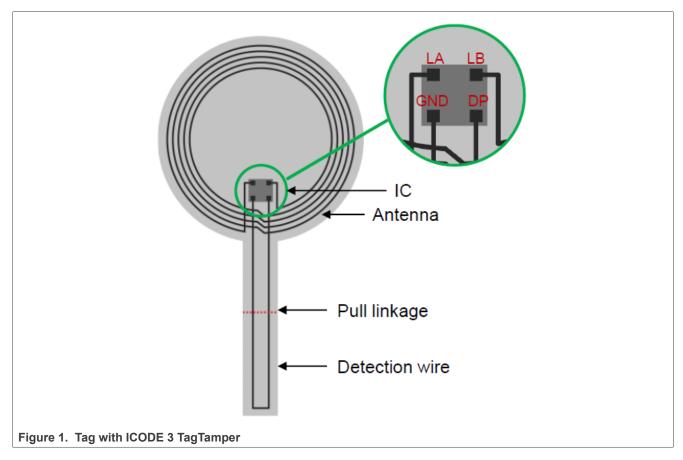

The ICODE 3 TagTamper IC includes four connection pads (<u>Figure 1</u>). The antenna is connected to the LA and LB pads of the IC. The TagTamper detection wire (Tamper loop) is connected to the tamper pads DP and GND. The connection of the TagTamper detection wire is checked at each startup of ICODE 3 TagTamper.

A command can be used to read the status of the TagTamper wire. The response of ICODE 3 TagTamper to the command is based on the open/close status of the Tamper loop. For more details on the command, refer to [1].

ICODE 3 TagTamper - Tamper loop design hints

# 2 Design guidelines

This section provides some guidelines for the design of a tamper loop.

Note: To verify the functionality of your application, run the final characterization of your samples.

### 2.1 Requirements and conditions

When designing a Tamper loop, consider the following:

- 1. Requirement 1 ON/OFF resistance value:

- To detect the Tamper loop as closed, keep R<50  $\Omega$ .

- To detect the Tamper loop as opened, keep R>1 MΩ.

- 2. Requirement 2 The induced voltage on the Tamper loop must not exceed 0.5 V (peak).

ICODE 3 TagTamper - Tamper loop design hints

### 2.2 Other considerations

### 2.2.1 Tamper loop material

The Tamper loop is made of a conductive material. The material and length of the loop must comply with requirement 1 (Section 2.1).

### 2.2.2 Overlapping area

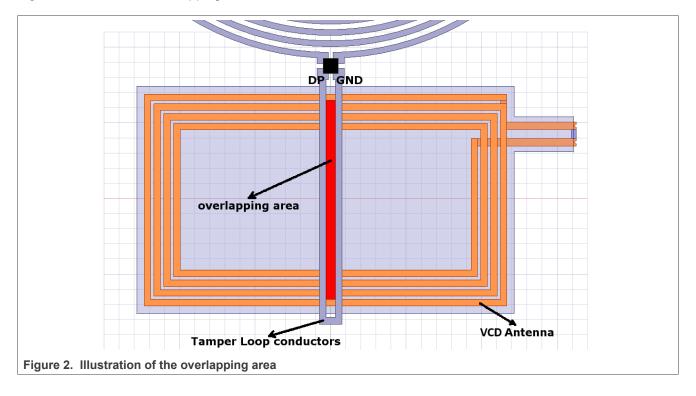

The overlapping area is at the intersection of the Tamper loop conductors and the outer track of the vicinity coupling device (VCD) antenna.

Figure 2 illustrates the overlapping area.

ICODE 3 TagTamper - Tamper loop design hints

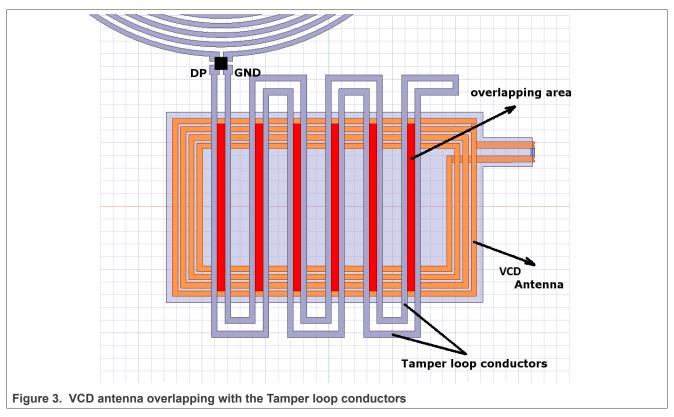

<u>Figure 3</u> shows a different design with a long Tamper wire. The overlapping area is calculated by adding the lengths of the Tamper loop conductors that intersect with the VCD antenna track.

If using a VCD antenna size Class 6, the sum of all the overlapping areas must not exceed 2.5 cm<sup>2</sup>. See <u>Table 1</u> for other VCD antenna sizes.

### 2.2.3 VCD antenna sizes and mapped field strengths

<u>Table 1</u> provides the values of the VCD field strengths and allowed overlapping areas for various antenna sizes.

Table 1. VCD field strength

| Antenna size                                       | H <sub>MAX</sub> [A/m (rms)] | Allowed overlapping area [cm <sup>2</sup> ] |

|----------------------------------------------------|------------------------------|---------------------------------------------|

| Mobile devices' average/<br>estimated antenna size | 1.5                          | 15                                          |

| Class 1                                            | 5                            | 6                                           |

| Class 2                                            | 8.5                          | 5.5                                         |

| Class 3                                            | 8.5                          | 5.5                                         |

| Class 4                                            | 12                           | 3.8                                         |

| Class 5                                            | 14                           | 3.3                                         |

| Class 6                                            | 18                           | 2.5                                         |

ICODE 3 TagTamper - Tamper loop design hints

### 2.2.4 Layout considerations

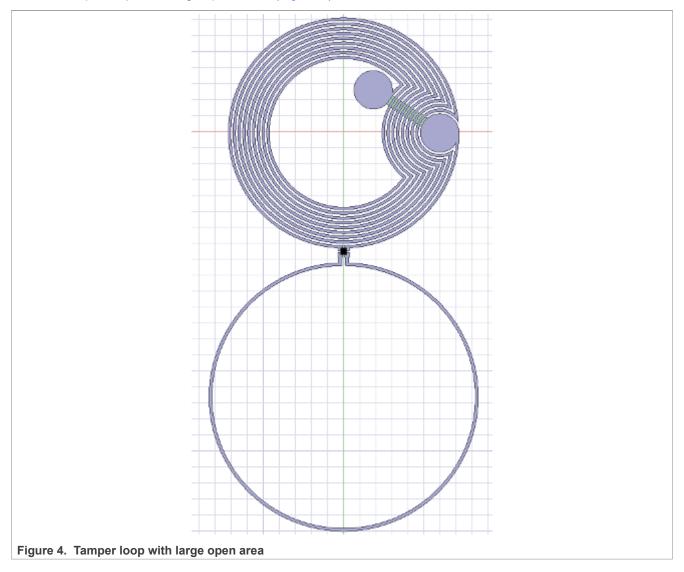

• Avoid Tamper loops with large open areas (Figure 4).

ICODE 3 TagTamper - Tamper loop design hints

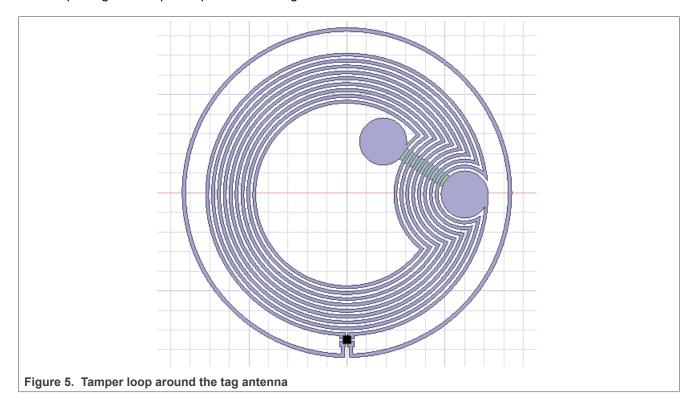

• Avoid placing the Tamper loop around the tag antenna.

ICODE 3 TagTamper - Tamper loop design hints

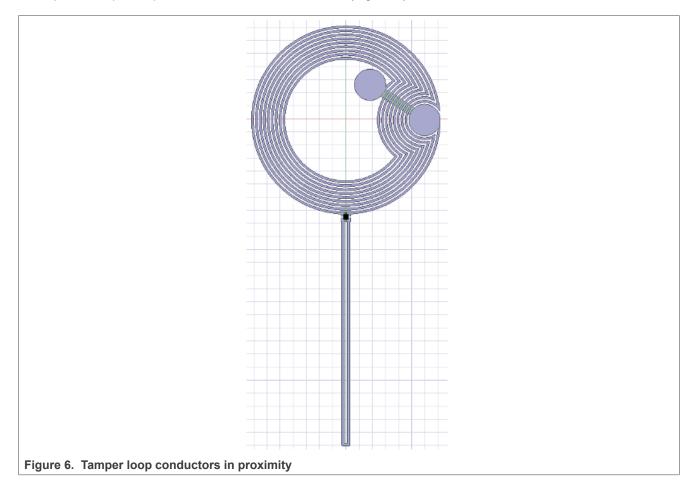

• Keep the Tamper loop conductors close to each other (Figure 6).

ICODE 3 TagTamper - Tamper loop design hints

# 3 References

[1] Data sheet – SL2S3003/SL2S3003TT ICODE 3 (TagTamper) (link)

ICODE 3 TagTamper - Tamper loop design hints

# 4 Revision history

### Table 2. Revision history

| Document ID   | Release date  | Description     |

|---------------|---------------|-----------------|

| AN13646 v.1.0 | 29 March 2024 | Initial version |

#### ICODE 3 TagTamper - Tamper loop design hints

# **Legal information**

### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

${f NXP}$  — wordmark and logo are trademarks of NXP B.V.

$\label{eq:looperand} \textbf{ICODE} \ \ \text{and} \ \ \textbf{I-CODE} \ \ \ \ \text{are trademarks of NXP B.V.}$

AN13646

# ICODE 3 TagTamper - Tamper loop design hints

# **Tables**

| Tab. 1.                       | VCD field strength5        | Tab. 2.                       | Revision history10               |

|-------------------------------|----------------------------|-------------------------------|----------------------------------|

| Figur                         | es                         |                               |                                  |

| Fig. 1.<br>Fig. 2.<br>Fig. 3. | Tag with ICODE 3 TagTamper | Fig. 4.<br>Fig. 5.<br>Fig. 6. | Tamper loop with large open area |

# ICODE 3 TagTamper - Tamper loop design hints

### **Contents**

| 1     | Introduction                                 | 2  |

|-------|----------------------------------------------|----|

| 2     | Design guidelines                            |    |

| 2.1   | Requirements and conditions                  |    |

| 2.2   | Other considerations                         | 4  |

| 2.2.1 | Tamper loop material                         | 4  |

| 2.2.2 | Overlapping area                             | 4  |

| 2.2.3 | VCD antenna sizes and mapped field strengths |    |

| 2.2.4 | Layout considerations                        |    |

| 3     | References                                   | 9  |

| 4     | Revision history                             | 10 |

|       | Legal information                            |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.