PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

Rev. 1.0 — 14 June 2021

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PTN38007 PTN38003A, PTN3816, PTN3944, PTN5150A, PTN5110, NX5P3090, USB Type-C, CC Logic, Orientation Detection, USB3.2, SuperSpeed, DisplayPort, USB4 v1.0, Thunderbolt3 redriver |

| Abstract    | This application note presents design guidelines for PTN38007/38003A/3816/3944 in a system.                                                                                       |

# PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

#### **Revision history**

| Rev   | Date     | Description     |

|-------|----------|-----------------|

| v.1.0 | 20210614 | Initial version |

## 1 Introduction

PTN38007 is a high-performance Type-C USB3.2/ DP1.4/Thunderbolt3/USB4 v1.0 combo linear redriver that is optimized for USB3.2, DisplayPort 1.4 and Thunderbolt3/ USB4 v1.0 applications on either the Downstream Facing Port (DFP) or Upstream Facing Port (UFP) application.

PTN38007 can be used in different system configurations (DFP, UFP or Dongle), and can be configured through  $I^2C$ . This document discusses in detail how each design can be achieved, in terms of schematics and layout.

## 2 Connections to a Type-C Receptacle or a Type-C Plug

PTN38007 can be used in a DFP, UFP, or Dongle configuration. In each configuration, each pin has its specific connection in the system.

### 2.1 DFP system with Type-C receptacle

In a DFP system, a USB3/USB4 v1.0/DisplayPort/Thunderbolt controller is placed on the left side of the PTN38007, and a Type-C receptacle is placed on the right side of PTN38007. <u>Table 1</u> illustrates the connection in a DFP system.

| DP Cont | oller    | USB3/US<br>Controlle |          |      | PTN38007                |      | Type-C Re | ceptacle |

|---------|----------|----------------------|----------|------|-------------------------|------|-----------|----------|

| Normal  | Reversed | Normal               | Reversed |      |                         |      | Pin #     | Pin name |

| ML0     | ML3      | SSRX2                | SSRX1    | B_IO |                         | DRX2 | A11/A10   | RX2      |

| ML1     | ML2      | SSTX2                | SSTX1    | A_IN | B_ION<br>B_ION<br>DRX2P | DTX2 | B3/B2     | TX2      |

| ML2     | ML1      | SSTX1                | SSTX2    | C_IN | A_INP DTX2P             | DTX1 | A2/A3     | TX1      |

| ML3     | MLO      | SSRX1                | SSRX2    | D_IO |                         | DRX1 | B10/B11   | RX1      |

Table 1. Connection in a DFP system

## 2.2 UFP system with Type-C receptacle

In a UFP system, a Type-C receptacle is placed on the left side of the PTN38007, and a USB3/USB4 v1.0/DisplayPort/Thunderbolt controller is placed on the right side of PTN38007. <u>Table 2</u> illustrates the connection in a UFP system.

| Type-C Receptacle |          | PTN38007 |  | USB3/USB4 v1.0<br>Controller |        | DP Cont  | DP Controller |          |

|-------------------|----------|----------|--|------------------------------|--------|----------|---------------|----------|

| Pin #             | Pin name |          |  |                              | Normal | Reversed | Normal        | Reversed |

| A2/A3             | TX1      | B_IO     |  | DRX2                         | SSTX1  | SSTX2    | ML3           | ML0      |

| B10/B11           | RX1      | A_IN     |  | DTX2                         | SSRX1  | SSRX2    | ML2           | ML1      |

| A11/A10           | RX2      | C_IN     |  | DTX1                         | SSRX2  | SSRX1    | ML1           | ML2      |

| B3/B2             | TX2      | D_IO     |  | DRX1                         | SSTX2  | SSTX1    | MLO           | ML3      |

#### Table 2. Connection in a UFP system

## 2.3 UFP dongle with Type-C plug

Similar to a UFP system, a UFP dongle has a USB3/USB4 v1.0/DisplayPort/Thunderbolt controller placed on the right side of PTN38007, but a Type-C plug is placed on the left side of the PTN38007. <u>Table 3</u> illustrates the connection in a UFP dongle system. (This design is based on normal orientation with CC1 connected to PD controller, and only CC1 pin is connected to PD controller).

Table 3. Connection in a UFP dongle system

| Type-C plug |                |         | PTN38007               |        | USB3/USB4 v1.0<br>controller |          | DP controller |          |

|-------------|----------------|---------|------------------------|--------|------------------------------|----------|---------------|----------|

| Pin #       | Pin # Pin Name |         | ] [                    |        |                              | Reversed | Normal        | Reversed |

| A11/A10     | RX2            | B_IO    |                        | DRX2   | SSTX2                        | SSTX1    | ML0           | ML3      |

| B3/B2       | TX2            | A_IN    |                        |        | SSRX2                        | SSRX1    | ML1           | ML2      |

| A2/A3       | TX1            | C_IN    |                        | DTX1   | SSRX1                        | SSRX2    | ML2           | ML1      |

| B10/B11     | RX1            | D_IO    |                        | DRX1   | SSTX1                        | SSTX2    | ML3           | ML0      |

| A8          | SBU1           | AUXP    |                        | ><br>> |                              |          | AUXP          |          |

| B8          | SBU2           | AUXN    |                        |        |                              |          | AUXN          |          |

| A5          | CC1            | Connect | to PD controller's CC1 | I      |                              |          |               |          |

| B5          | CC2            | VCONN   | or NC                  |        |                              |          |               |          |

## 2.4 Type-C cable with Type-C plugs on both sides

A Type-C cable has plugs on both sides of PTN38007. <u>Table 4</u> illustrates the connection in a cable. For DisplayPort interface, since the signal is unidirectional (from source to sink only), it is important to plug left side of the cable to a host PC, and plug right side of the cable to a device or monitor.

# PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

| Type-C plug | Type-C plug (to host) |            | PTN38007       |       |          | (to device) |

|-------------|-----------------------|------------|----------------|-------|----------|-------------|

| Pin #       | Pin name              |            | F 11130007     | Pin # | Pin name |             |

| A11/A10     | RX2                   | B_IO       |                | DRX2  | A2/A3    | TX1         |

| B3/B2       | TX2                   | A_IN       |                | DTX2  | B10/B11  | RX1         |

| A2/A3       | TX1                   | C_IN       | A INP DTX2P    | DTX1  | A11/A10  | RX2         |

| B10/B11     | RX1                   | D_IO       |                | DRX1  | B3/B2    | TX2         |

| A8          | SBU1                  | AUXP       |                |       | B8       | SBU2        |

| B8          | SBU2                  | AUXN       |                |       | A8       | SBU1        |

| A5          | CC1                   | Connect ac | ross the cable | I     | B5       | CC2         |

| B5          | CC2                   | VCONN or   | NC             |       | A5       | CC1         |

#### Table 4. Type-C cable connection

#### 2.4.1 High-speed switches

PTN38007 itself does not have any built-in switch to multiplex USB3/USB4 v1.0/ DisplayPort/Thunderbolt signals. The controllers or application processors should include a high-speed crossbar switch that is capable of multiplexing different signal standards to four differential input pins of PTN38007. If the controllers or application processors don't have a crossbar switch integrated, NXP has the following high-speed switches available for selection:

- To cover up to 10 Gbps (USB3.2 Gen 2, DisplayPort HBR3)

- Simple 2:1 switch: CBTU02043, CBTL01023, CBTL02043, CBTL04083

Integrated Type-C switch: CBTL08GP053

- To cover up to 20 Gbps (USB4 v1.0, DisplayPort v2.0, Thunderbolt 3, PCIe Gen 3)

Simple 2:1 switch: CBTU02043, CBTU02044

#### 2.4.2 AC capacitor location

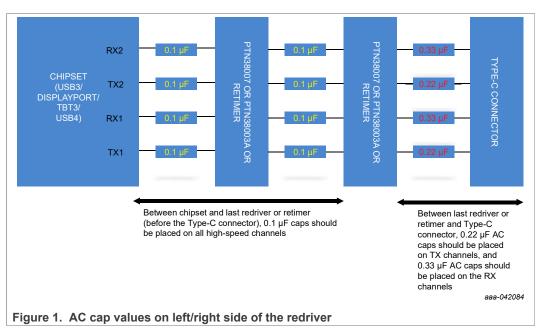

PTN38007's TX or RX DC common mode voltage might be different from the chipset's or device's DC common mode voltage; AC caps should be placed on all high-speed lanes on both left and right sides of PTN38007. Between the chipset and last redriver or retimer before the Type-C connector, 0.1  $\mu$ F capacitors should be placed on the high-speed lanes. Between last redriver or retimer and Type-C connector, 0.22  $\mu$ F capacitors should be placed on the RX channels.

AN13260

### 2.5 High-speed P and N signal assignment

PTN38007's high-speed lanes are agnostic to the polarity of the signal, and it is okay to swap the P and N signal polarity to achieve better layout result. However, when the polarity the left side is inverted, the polarity of the corresponding signal pair on the right side should be inverted at the same time.

### 2.6 AUXP and AUXN signal connection

PTN38007's AUX monitor circuit is used to decode AUX transactions, and connections to a DisplayPort's AUX channel polarity should follow the pin name assignments. In the case of SBU signals on the type-C connector, the AUXP and AUXN polarity changes according to the orientation of the cable plugging in.

|                      | DFP Type-C connector       | UFP Type-C connector       |

|----------------------|----------------------------|----------------------------|

| Normal Orientation   | SBU1 = AUXP<br>SBU2 = AUXN | SBU1 = AUXN<br>SBU2 = AUXP |

| Reversed Orientation | SBU1 = AUXN<br>SBU2 = AUXP | SBU1 = AUXP<br>SBU2 = AUXN |

| Table 5. AUX | polarity hardwar  | e wiring connection  | orientation |

|--------------|-------------------|----------------------|-------------|

|              | polarity flatuwar | e winning connection | Unenta      |

Usually the AUX P and N polarity hardware wiring connection follows the normal orientation in <u>Table 5</u>, and PTN38007's  $I^2C$  register 0x04 bit 3 can be used to follow the orientation of the cable plugging in, which is register 0x04 bit 4. When in normal orientation, set Reg[0x04].Bit[4:3]=[0, 0]; when in reversed orientation, set Reg[0x04].Bit[4:3]=[1, 1].

| 3 | b'0 | AUX snooping polarity control bit                                          |

|---|-----|----------------------------------------------------------------------------|

|   |     | <ul> <li>When 0, AUXP/AUXN signal polarities follow pin naming:</li> </ul> |

|   |     | – Pin 18 = AUXP                                                            |

|   |     | – Pin 17 = AUXN                                                            |

|   |     | When 1, AUXP/AUXN signal polarities are reverse of the pin naming:         |

|   |     | – Pin 17 = AUXP                                                            |

|   |     | – Pin 18 = AUXN                                                            |

For PTN3816, the AUX polarity assignment is NOT reversible, because there is no  $I^2C$  control to set the orientation of the AUX signaling. User should always connect AUX's positive signal to AUXP pin, and AUX's negative signal to AUXN pin.

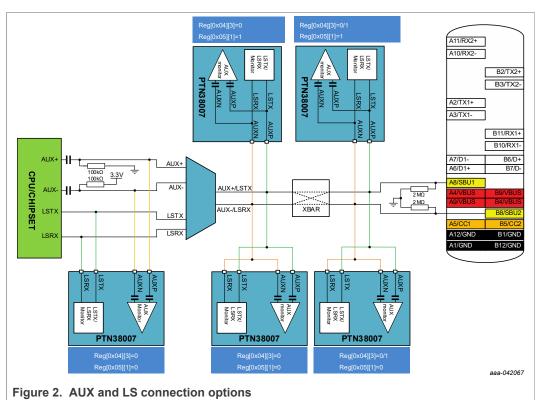

### 2.7 AUX and LS connections options

There are various ways AUX and LS can connect to PTN38007 for snooping purposes. PTN38007 has two registers to configure AUX polarity, and pin sharing of AUX and LS signals.

• Reg[0x04][3] controls the polarity of AUXP/N

| 3 | b'0 | AUX snooping polarity control bit                                                      |

|---|-----|----------------------------------------------------------------------------------------|

|   |     | <ul> <li>When 0, AUXP/AUXN signal polarities follow pin naming:</li> </ul>             |

|   |     | – Pin 18 = AUXP                                                                        |

|   |     | – Pin 17 = AUXN                                                                        |

|   |     | <ul> <li>When 1, AUXP/AUXN signal polarities are reverse of the pin naming:</li> </ul> |

|   |     | – Pin 17 = AUXP                                                                        |

|   |     | – Pin 18 = AUXN                                                                        |

• Reg[0x05][1] allows the use of AUXP/AUXN pins for both AUX/LS inputs

|     | 1 | b'0 | AUX/LS snooping pin muxing                                                   |

|-----|---|-----|------------------------------------------------------------------------------|

|     |   |     | When 0, AUX and LS snooping are done through separate interface pairs.       |

|     |   |     | <ul> <li>AUX snooping using AUXP/AUXN pins</li> </ul>                        |

|     |   |     | <ul> <li>LS snooping using LSTX/LSRX pins</li> </ul>                         |

|     |   |     | When 1, AUX and LS snooping are done through the same AUXP/AUXN pins.        |

|     |   |     | <ul> <li>AUXP/AUXN snooping using AUXP/AUXN pins</li> </ul>                  |

|     |   |     | <ul> <li>LS snooping using AUXP/AUXN pins</li> </ul>                         |

|     |   |     | PTN38007 decodes the protocols based on the respective mode that is enabled. |

| - L |   |     |                                                                              |

Depending on these bit settings, AUX/LS connections are illustrated in Figure 2.

AN13260 Application note

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

### 2.8 PTN3816 main lane assignments

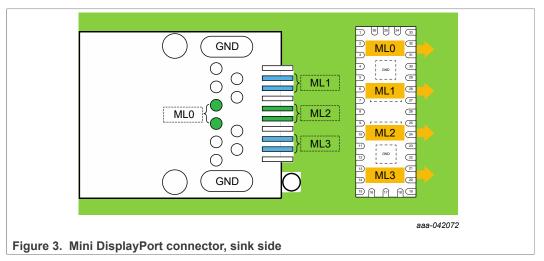

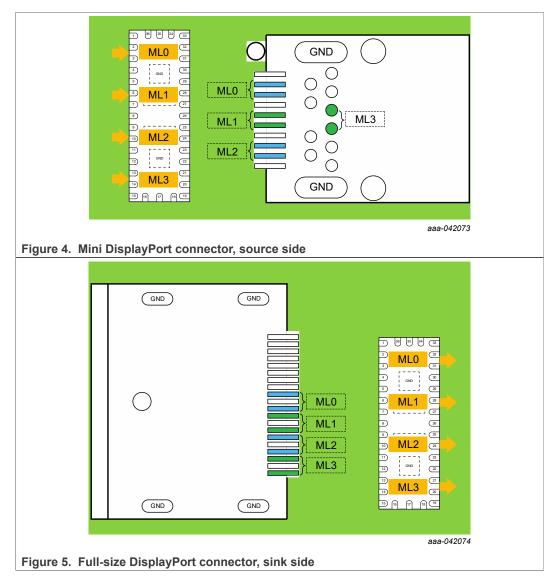

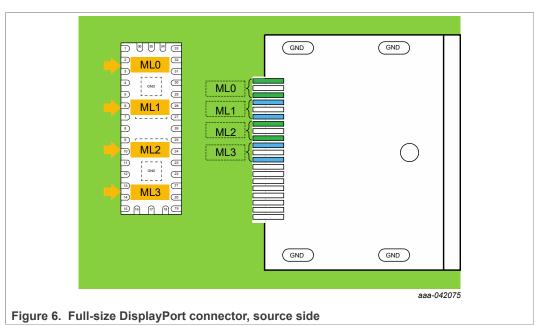

DisplayPort's main lane number assignments are not interchangeable. Corresponding lanes are turned off or placed in low power mode when the link is in D3 mode or number of operating lanes are less than four. When setting LANE\_ORDER to 0, PTN3816's lane number assignment should match with the DisplayPort connector's lane assignment.

AN13260 Application note

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

#### 2.9 Number of power supply decoupling capacitors required

PTN38007 has five power supply pins. VCCA/VCCB/VCCC/VCCD are analog power supplies to each transmitter/receiver path. VDD pin is the power supply to the digital circuits. Ideally, there should be a 0.1  $\mu$ F decoupling capacitor on each power supply pin; if there is limitation on number of capacitors that can be placed for each PTN38007 on the PCB, at least two capacitors should be used.

#### 2.10 ADDR resistor tolerance

PTN38007's I<sup>2</sup>C slave address can be configured through resistor options on the ADDR pin. During manufacturing, if it is very difficult to have exact resistor value placed in the BOM, the following table shows a range of resistors values that can be placed at the ADDR pin to achieve the same setting result.

| I <sup>2</sup> C Address | Datasheet recommendation             | Minimum | Maximum |

|--------------------------|--------------------------------------|---------|---------|

| 0x33                     | Connect to 1.8 V directly            | 0 Ω     | 1.1 kΩ  |

| 0x32                     | Connect to 1.8 V with 56 $k\Omega$   | 50.4 kΩ | 61.6 kΩ |

| 0x31                     | Connect to 1.8 V with 200 k $\Omega$ | 180 kΩ  | 220 kΩ  |

| 0x30                     | Connect to GND directly              | 0 Ω     | Open    |

Table 6. ADDR pin resistor options

### 2.11 ESD recommendation

The following ESD devices are used on NXP's PTN38007/PTN3944 evaluation boards:

- PESD3V3R1BSF

- PESD2V8R1BSF

ESD protection diodes are placed between PTN38007 and the AC caps on the USB Type-C connector facing side. For more details about the ESD products, please contact Nexperia for more information.

## 2.12 PCIe mode I<sup>2</sup>C address assignments

There are 32 possible  $I^2C$  slave addresses that can be assigned to PTN3944, including eight of which are reserved slave addresses in the  $I^2C$  standard. User should avoid using the reserved  $I^2C$  slave addresses. Below is a list of  $I^2C$  address assignments to each PCIe bus' TX/RX group that are being predefined on the PTN3944 Add-In Card. This is not mandatory, but if the user follows the assignments, the GUI can be used.

Table 7. PCIe mode l<sup>2</sup>C address assignments

|             |           | ADDR4 | ADDR3 | ADDR2 | ADDR/ADDR1          | 7-Bit<br>Address | 7-Bi | t Addre | SS |   |   |   |   |

|-------------|-----------|-------|-------|-------|---------------------|------------------|------|---------|----|---|---|---|---|

| BUS0        | TX[0:3]   | 0     | 0     | 0     | VDD1V8 (0x33)       | 23               | 0    | 1       | 0  | 0 | 0 | 1 | 1 |

| x16         | TX[4:7]   | 0     | 0     | 0     | 56K Pull Up (0x32)  | 22               | 0    | 1       | 0  | 0 | 0 | 1 | 0 |

|             | TX[8:11]  | 0     | 0     | 0     | 200K Pull Up (0x31) | 21               | 0    | 1       | 0  | 0 | 0 | 0 | 1 |

|             | TX[12:15] | 0     | 0     | 0     | GND (0x30)          | 20               | 0    | 1       | 0  | 0 | 0 | 0 | 0 |

|             | RX[0:3]   | 0     | 0     | 1     | VDD1V8 (0x33)       | 2B               | 0    | 1       | 0  | 1 | 0 | 1 | 1 |

|             | RX[4:7]   | 0     | 0     | 1     | 56K Pull Up (0x32)  | 2A               | 0    | 1       | 0  | 1 | 0 | 1 | 0 |

|             | RX[8:11]  | 0     | 0     | 1     | 200K Pull Up (0x31) | 29               | 0    | 1       | 0  | 1 | 0 | 0 | 1 |

|             | RX[12:15] | 0     | 0     | 1     | GND (0x30)          | 28               | 0    | 1       | 0  | 1 | 0 | 0 | 0 |

| BUS1        | TX[0:3]   | 0     | 1     | 0     | VDD1V8 (0x33)       | 33               | 0    | 1       | 1  | 0 | 0 | 1 | 1 |

| x16         | TX[4:7]   | 0     | 1     | 0     | 56K Pull Up (0x32)  | 32               | 0    | 1       | 1  | 0 | 0 | 1 | 0 |

|             | TX[8:11]  | 0     | 1     | 0     | 200K Pull Up (0x31) | 31               | 0    | 1       | 1  | 0 | 0 | 0 | 1 |

|             | TX[12:15] | 0     | 1     | 0     | GND (0x30)          | 30               | 0    | 1       | 1  | 0 | 0 | 0 | 0 |

|             | RX[0:3]   | 0     | 1     | 1     | VDD1V8 (0x33)       | 3B               | 0    | 1       | 1  | 1 | 0 | 1 | 1 |

|             | RX[4:7]   | 0     | 1     | 1     | 56K Pull Up (0x32)  | 3A               | 0    | 1       | 1  | 1 | 0 | 1 | 0 |

|             | RX[8:11]  | 0     | 1     | 1     | 200K Pull Up (0x31) | 39               | 0    | 1       | 1  | 1 | 0 | 0 | 1 |

|             | RX[12:15] | 0     | 1     | 1     | GND (0x30)          | 38               | 0    | 1       | 1  | 1 | 0 | 0 | 0 |

| BUS2<br>x16 | TX[0:3]   | 1     | 0     | 0     | VDD1V8 (0x33)       | 63               | 1    | 1       | 0  | 0 | 0 | 1 | 1 |

|             | TX[4:7]   | 1     | 0     | 0     | 56K Pull Up (0x32)  | 62               | 1    | 1       | 0  | 0 | 0 | 1 | 0 |

|             | TX[8:11]  | 1     | 0     | 0     | 200K Pull Up (0x31) | 61               | 1    | 1       | 0  | 0 | 0 | 0 | 1 |

|             | TX[12:15] | 1     | 0     | 0     | GND (0x30)          | 60               | 1    | 1       | 0  | 0 | 0 | 0 | 0 |

|             | RX[0:3]   | 1     | 0     | 1     | VDD1V8 (0x33)       | 6B               | 1    | 1       | 0  | 1 | 0 | 1 | 1 |

|             | RX[4:7]   | 1     | 0     | 1     | 56K Pull Up (0x32)  | 6A               | 1    | 1       | 0  | 1 | 0 | 1 | 0 |

|             | RX[8:11]  | 1     | 0     | 1     | 200K Pull Up (0x31) | 69               | 1    | 1       | 0  | 1 | 0 | 0 | 1 |

|             | RX[12:15] | 1     | 0     | 1     | GND (0x30)          | 68               | 1    | 1       | 0  | 1 | 0 | 0 | 0 |

| BUS3        | TX[0:3]   | 1     | 1     | 0     | VDD1V8 (0x33)       | 73               | 1    | 1       | 1  | 0 | 0 | 1 | 1 |

| x16         | TX[4:7]   | 1     | 1     | 0     | 56K Pull Up (0x32)  | 72               | 1    | 1       | 1  | 0 | 0 | 1 | 0 |

|             | TX[8:11]  | 1     | 1     | 0     | 200K Pull Up (0x31) | 71               | 1    | 1       | 1  | 0 | 0 | 0 | 1 |

|             | TX[12:15] | 1     | 1     | 0     | GND (0x30)          | 70               | 1    | 1       | 1  | 0 | 0 | 0 | 0 |

|             | RX[0:3]   | 1     | 1     | 1     | VDD1V8 (0x33)       | 7B               | 1    | 1       | 1  | 1 | 0 | 1 | 1 |

|             | RX[4:7]   | 1     | 1     | 1     | 56K Pull Up (0x32)  | 7A               | 1    | 1       | 1  | 1 | 0 | 1 | 0 |

|             | RX[8:11]  | 1     | 1     | 1     | 200K Pull Up (0x31) | 79               | 1    | 1       | 1  | 1 | 0 | 0 | 1 |

|             | RX[12:15] | 1     | 1     | 1     | GND (0x30)          | 78               | 1    | 1       | 1  | 1 | 0 | 0 | 0 |

## 3 Redriver placement

Depending on the use cases, PTN38007/PTN3816/PTN3944 should be placed with some pre-channel length and post-channel length in the system. The following sections depicts the most common configurations.

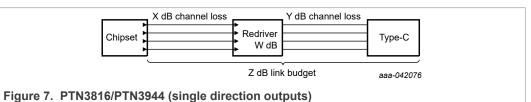

### 3.1 PTN3816/PTN3944 (single direction outputs)

- Pre-Channel (X) length: minimum: 2 inches, maximum 9 inches.

- Post-Channel (Y) length: about 1.5-2.0 inches

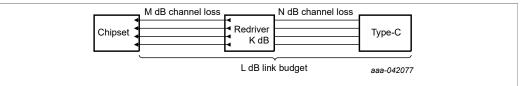

## 3.2 PTN3816/PTN3944 (single direction inputs)

Figure 8. PTN3816/PTN3944 (single direction inputs)

- Pre-Channel (N) length: about 1.5-2.0 inches

- Post-Channel (M) length: minimum: 2 inches, maximum 9 inches.

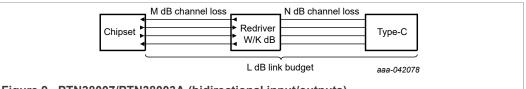

### 3.3 PTN38007/PTN38003A (bidirectional input/outputs)

Figure 9. PTN38007/PTN38003A (bidirectional input/outputs)

- Pre-Channel (M) length: minimum: 2 inches, maximum 9 inches.

- Post-Channel (N) length: about 1.5-2.0 inches

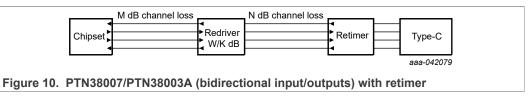

## 3.4 PTN38007/PTN38003A (bidirectional input/outputs) with retimer

- Pre-Channel (M) length: minimum: 2 inches, maximum 9 inches.

- Post-Channel (N) length: minimum: 2 inches, maximum 9 inches.

## 4 Layout guidelines

## 4.1 General differential layout guideline

Please refer to <u>AN10798</u> for general differential layout guidelines.

High-speed transmission lines need to be designed with impedance matching in mind. These traces should be designed with  $90\Omega$  differential impedance. Signal trace length within the same differential pair should be equal. If it is difficult to achieve exact same length within the same differential pair, the mismatch in length should be minimized to no more than 3 mils.

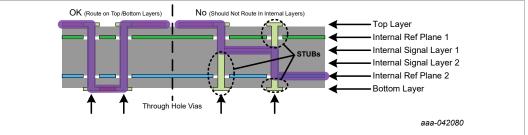

High-speed signals should be routed over the top or bottom layer of a multi-layer PCB because signals travel faster on the buried microstrips than striplines. These signals should also not to be routed on the internal power/ground layers, or in the internal signal layers to avoid stubs created by the vias.

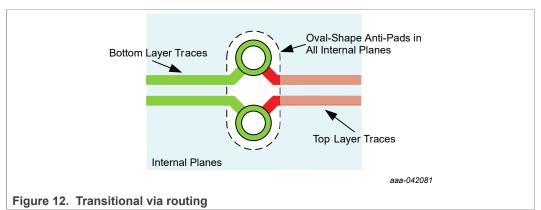

Solid internal reference ground planes should be designed immediately underneath or above the high-speed transmission lines. The distance between the two differential traces should be kept equal as long as possible. Try to avoid vias in the transmission lines themselves. If it is required to use a via, make sure the trace branches to the vias are symmetrical, and oval-shape anti-pads should be used on all internal planes for transitional vias as shown below.

## 4.2 High-speed signal routing

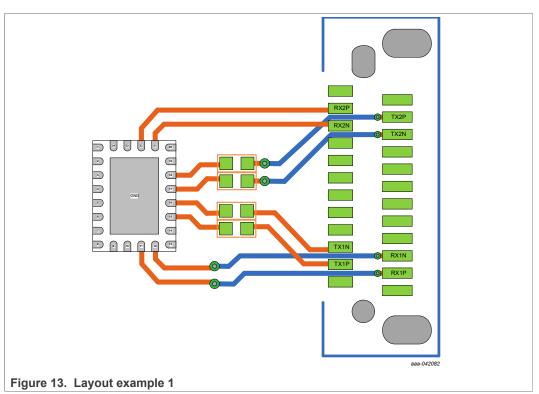

PTN38007 pin assignments are defined in such a way that connection to Type-C connector can be minimized. High-speed traces should be routed between PTN38007 and Type-C connector with minimum layer transition. Whenever possible, route signals on the same layer.

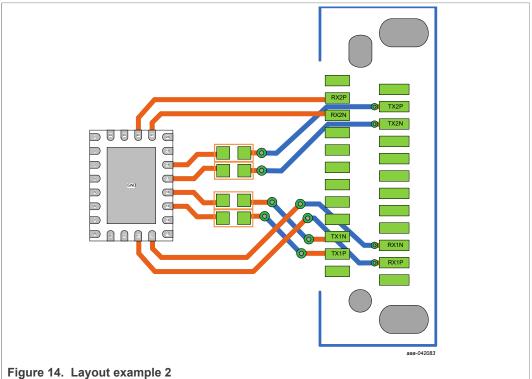

In the layout example below, orange color traces are on the top layer, and blue traces are on the bottom layer. The AC caps can be placed on the same side as PTN38007, close to the chip. For traces connecting to RX2 and TX1 on the Type-C connector, the trace can be routed all on the top layer. For traces connecting to TX2 and RX1 on the Type-C connectors, because it is very difficult to fan out these signals only on the top layer, and vias are usually required. Try to minimize the total number of vias used on the traces. Usually two vias for each trace should be enough to complete the routing.

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

In the next layout example below, even the RX1 signal pairs are routed with minimum number of vias, but the vias are not placed at the optimum position. This layout causes TX1 signal traces to have 2 extra vias that will impact the signal integrity. This should be avoided.

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

### 4.3 Impedance matching across the AC capacitors

When these AC-Coupling capacitors are placed on the high-speed signals, impedance of the trace changes across these AC-Coupling capacitors. To minimize the impedance change, a void in the adjacent reference ground plane is required. The size of the void should be the same size of the capacitor's pad size.

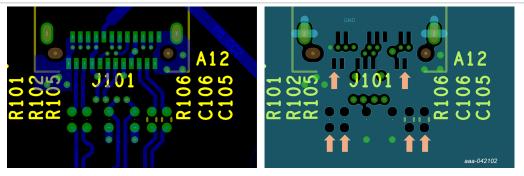

In the below figure, the picture on the left side illustrates the top layer routing, with component pads showing in green color. The picture on the right side illustrates the inner ground layer. Directly under the component pads that are connected to high-speed signals, a void with same shape and same size of the pad are created in the inner ground layer. This void can also be applied under connector pads, or PTN38007's high-speed signal pin pads.

Figure 15. Top layer routing (left), inner ground layer (right)

# PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

## 5 Legal information

### 5.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 5.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or

the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security - Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

Tab. 5.

Tab. 6. Tab. 7.

## **Tables**

| Tab. 1. | Connection in a DFP system         |  |

|---------|------------------------------------|--|

|         | Connection in a UFP system 4       |  |

| Tab. 3. | Connection in a UFP dongle system4 |  |

| Tab. 4. | Type-C cable connection5           |  |

## **Figures**

| Fig. 1. | AC cap values on left/right side of the      |   |

|---------|----------------------------------------------|---|

|         | redriver                                     | ô |

| Fig. 2. | AUX and LS connection options                | 8 |

| Fig. 3. | Mini DisplayPort connector, sink side        | 8 |

| Fig. 4. | Mini DisplayPort connector, source side      | 9 |

| Fig. 5. | Full-size DisplayPort connector, sink side   | 9 |

| Fig. 6. | Full-size DisplayPort connector, source      |   |

|         | side10                                       | С |

| Fig. 7. | PTN3816/PTN3944 (single direction            |   |

|         | outputs)12                                   | 2 |

| Fig. 8. | PTN3816/PTN3944 (single direction inputs) 12 | 2 |

| Fig. 9.  | PTN38007/PTN38003A (bidirectional input/     |    |

|----------|----------------------------------------------|----|

|          | outputs)                                     | 12 |

| Fig. 10. | PTN38007/PTN38003A (bidirectional input/     |    |

|          | outputs) with retimer                        | 12 |

| Fig. 11. | High-speed signal routing                    | 13 |

| Fig. 12. | Transitional via routing                     | 13 |

| Fig. 13. | Layout example 1                             | 14 |

| Fig. 14. | Layout example 2                             | 14 |

| Fig. 15. | Top layer routing (left), inner ground layer |    |

|          | (right)                                      | 15 |

AUX polarity hardware wiring connection

PCIe mode I2C address assignments ......11

PTN38007/38003A/3816/3944 USB Type-C USB3.2, DisplayPort v2.0, Thunderbolt 3, and USB4 v1.0 combo redriver design guidelines

## Contents

| 1     | Introduction                              | 3  |

|-------|-------------------------------------------|----|

| 2     | Connections to a Type-C Receptacle or a   |    |

|       | Type-C Plug                               | 3  |

| 2.1   | DFP system with Type-C receptacle         | 3  |

| 2.2   | UFP system with Type-C receptacle         |    |

| 2.3   | UFP dongle with Type-C plug               |    |

| 2.4   | Type-C cable with Type-C plugs on both    |    |

|       | sides                                     | 4  |

| 2.4.1 | High-speed switches                       | 5  |

| 2.4.2 | AC capacitor location                     | 5  |

| 2.5   | High-speed P and N signal assignment      | 6  |

| 2.6   | AUXP and AUXN signal connection           | 6  |

| 2.7   | AUX and LS connections options            | 7  |

| 2.8   | PTN3816 main lane assignments             | 8  |

| 2.9   | Number of power supply decoupling         |    |

|       | capacitors required                       |    |

| 2.10  | ADDR resistor tolerance                   | 10 |

| 2.11  | ESD recommendation                        |    |

| 2.12  | PCIe mode I2C address assignments         | 11 |

| 3     | Redriver placement                        | 11 |

| 3.1   | PTN3816/PTN3944 (single direction         |    |

|       | outputs)                                  |    |

| 3.2   | PTN3816/PTN3944 (single direction inputs) | 12 |

| 3.3   | PTN38007/PTN38003A (bidirectional input/  |    |

|       | outputs)                                  | 12 |

| 3.4   | PTN38007/PTN38003A (bidirectional input/  |    |

|       | outputs) with retimer                     | 12 |

| 4     | Layout guidelines                         |    |

| 4.1   | General differential layout guideline     |    |

| 4.2   | High-speed signal routing                 | 13 |

| 4.3   | Impedance matching across the AC          |    |

|       | capacitors                                |    |

| 5     | Legal information                         | 16 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 14 June 2021 Document identifier: AN13260