# AN13238 How to Trigger and Detect Transmission Errors for LPC51U68 I2C

Rev. 0 - 04/2021

Application Note

# 1 Introduction

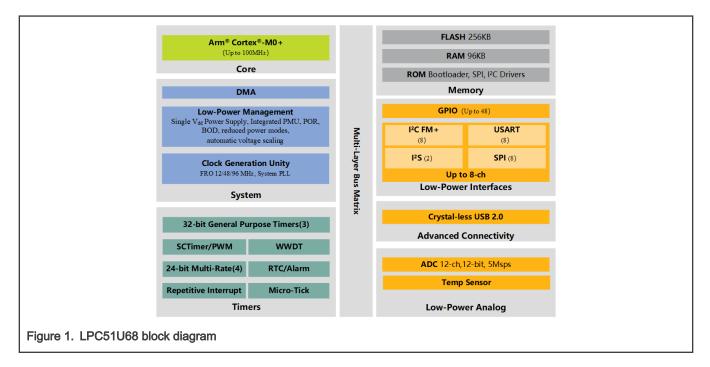

The LPC51U68 based on Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ is a low-cost, low-power consumption, 32-bit Micro Controller Unit (MCU) family. It operates at frequencies of up to 100 MHz and supports up to 256 KB on-chip flash memory and up to 96 KB total SRAM composed of up to 64 KB main SRAM, plus an additional 32 KB SRAM. The on-chip peripherals in LPC51U68 includes one DMA controller, 48 General-Purpose I/O (GPIO) pins , one CRC engine, one 12-bit ADC, one 32-bit Real-Time Clock (RTC), one multiple-channel Multi-Rate 24-bit Timer (MRT), one Windowed WatchDog Timer (WWDT), eight Flexcomm interfaces which can be selected by software to be a USART, SPI, or I<sup>2</sup>C interface.

The LPC51U68 I<sup>2</sup>C bus contains the following features:

- Independent Master, Slave, and Monitor functions.

- Supporting the following bus speeds:

- Standard mode, up to 100 kbits/s

- Fast-mode, up to 400 kbits/s

- Fast-mode Plus, up to 1 Mbits/s (on pins PIO0\_23 and 24 or PIO0\_25 and 26 that include specific I<sup>2</sup>C support)

- High speed mode, 3.4 Mbits/s as a Slave only (on pins PIO0\_23 and 24 or PIO0\_25 and 26 that include specific I<sup>2</sup>C support)

- · Supporting both Multi-master and Multi-master with Slave functions

- · Supporting multiple I<sup>2</sup>C slave addresses in the hardware

- · Qualifying one slave address with a bit mask or an address range to respond to multiple I<sup>2</sup>C bus addresses

- · 10-bit addressing supported with software assistance

- Supporting System Management Bus (SMBus).

- · Separated DMA requests for Master, Slave, and Monitor functions

- Waking up the device from deep-sleep mode, as no chip clocks are required to receive and compare an address as a Slave

- · Automatic modes optionally allow less software overhead for some use cases

This document describes how to trigger and detect I<sup>2</sup>C transmission errors including Start/Stop error, Arbitration Loss, SCL time-out, Event time-out on LPC51U68. I<sup>2</sup>C transmission errors are triggered by introducing external glitch which is also called as interference.

#### Contents

| 1   | Introduction1                          |

|-----|----------------------------------------|

| 2   | I2C bus introduction2                  |

| 3   | System overview3                       |

| 4   | Hardware configurations5               |

| 5   | I2C transmission error type6           |

| 5.1 | Start/Stop error6                      |

| 5.2 | Arbitration loss6                      |

| 5.3 | Time-out6                              |

| 6   | Glitch generation for I2C transmission |

|     | error7                                 |

| 6.1 | Glitch generation for Start/Stop       |

|     | error                                  |

| 6.2 | Glitch generation for arbitration      |

|     | loss                                   |

| 6.3 | Glitch generation for SCL time-out     |

|     | 9                                      |

| 6.4 | Glitch generation for event time-      |

|     | out10                                  |

| 7   | I2C transmission error detection 12    |

| 7.1 | SDK support12                          |

| 7.2 | Time-out threshold calculation16       |

| 7.3 | Event time-out detection               |

| 7.4 | Detection output17                     |

| 8   | How to use LPC51U68 I2C glitch         |

| -   | generation and detection demo19        |

| 9   | Summary                                |

| -   |                                        |

# 2 I2C bus introduction

I<sup>2</sup>C is an 8-bit, bidirectional, serial multi-master bus. It supports four modes including:

- · Standard mode up to 100 kbit/s

- · Fast mode up to 400 kbit/s

- Fast mode Plus up to 1 Mbit/s

- · High speed mode up to 3.4 Mbit/s

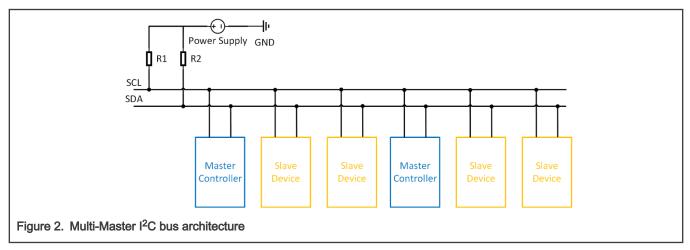

As shown in Figure 2, I<sup>2</sup>C uses a Serial Clock Line (SCL) and a Serial Data Line (SDA) for data transfer. The SCL and SDA of master devices and slave devices are connected to the SCL and SDA of I<sup>2</sup>C bus. For more details about I<sup>2</sup>C bus specification, see  $l^2C$ -bus specification and user manual (document UM10204).

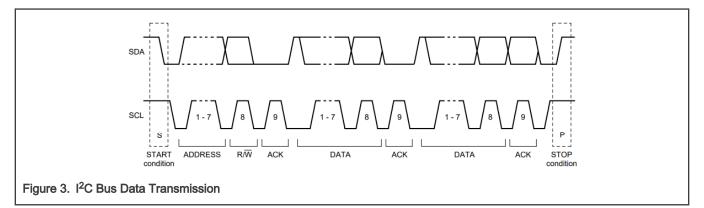

The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function. The master device initiates a transfer, generates clock signal, addresses the slave device, and terminates a transfer. Figure 3 illustrates the timing of  $I^2C$  bus data transmission.

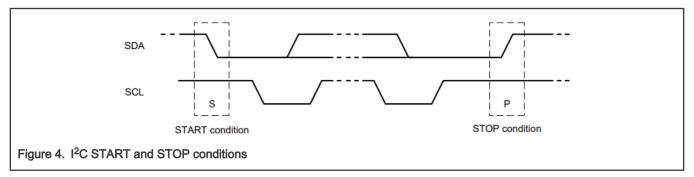

As shown in Figure 4, I<sup>2</sup>C transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

## 3 System overview

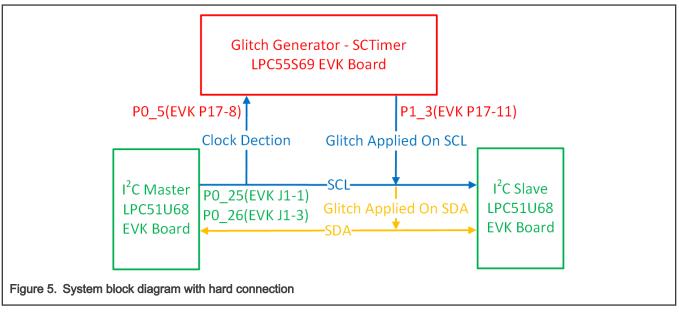

As shown in Figure 5, the system described in this document consists of three parts including one master, one slave and one glitch generator.

The master and slave perform normal data transfer. They are implemented by two LPCXpresso51U68 (OM40005) evaluation boards.

The glitch generator is used to interfere with normal I<sup>2</sup>C data transmission, resulting in transmission errors including Start/Stop error, Arbitration Loss, SCL time-out, Event time-out. The glitch generator is implemented by LPCXpresso55s69 (Revision A) evaluation board.

The glitch generator is implemented by the state machine generated by LPC55S69 SCTimer.

NOTE

The glitch generator detects the serial clock on the SCL line and applies glitch on the SCL line or the SDA line according to the type of  $I^2C$  transmission errors.

For specific details of I<sup>2</sup>C transmission errors, see I2C transmission error type.

# 4 Hardware configurations

Table 1, Table 2, and Table 3 describe the detailed hardware configurations of I<sup>2</sup>C master, I<sup>2</sup>C slave and glitch generator.

| Part     | Port | Pin | Mark on Evk board | Alternative function       | Description                       |

|----------|------|-----|-------------------|----------------------------|-----------------------------------|

|          | 0    | 25  | J1-1              | FC4_RTS_ <b>SCL</b> _SSEL1 | SCL line                          |

|          | 0    | 26  | J1-3              | FC4_CTS_ <b>SDA</b> _SSEL0 | SDA line                          |

| LPC51U68 | 0    | 29  | J2-5              | PIO0_29                    | Start/Stop error<br>indicator LED |

|          | 0    | 2   | J8-1              | PIO0_2                     | Event time-out<br>indicator LED   |

|          | 0    | 3   | J8-3              | PIO0_3                     | other errors<br>indicator LED     |

Table 1. I<sup>2</sup>C Master hardware configurations

Table continues on the next page...

| Part | Port | Pin | Mark on Evk board | Alternative function | Description                       |

|------|------|-----|-------------------|----------------------|-----------------------------------|

|      | 1    | 9   | J8-5              | PIO1_9               | SCL time-out<br>indicator LED     |

|      | 1    | 10  | J8-8              | PIO1_10              | Arbitration Loss<br>indicator LED |

Table 1. I<sup>2</sup>C Master hardware configurations (continued)

Table 2. I<sup>2</sup>C Slave hardware configurations

| Part     | Port | Pin | Mark on Evk board | Alternative function       | Description |

|----------|------|-----|-------------------|----------------------------|-------------|

| LPC51U68 | 0    | 25  | J1-1              | FC4_RTS_ <b>SCL</b> _SSEL1 | SCL line    |

| LFCJ1000 | 0    | 26  | J1-3              | FC4_CTS_ <b>SDA</b> _SSEL0 | SDA line    |

Table 3. I<sup>2</sup>C Glitch generator hardware configurations

| Part     | Port | Pin | Mark on Evk board | Alternative function | Description                             |

|----------|------|-----|-------------------|----------------------|-----------------------------------------|

| LPC55S69 | 0    | 5   | P17-8             | SCT0_GPI5            | Detect clock on<br>SCL line             |

|          | 1    | 3   | P17-11            | SCT0_OUT4            | Apply glitch on SCL<br>line or SDA line |

# 5 I2C transmission error type

#### 5.1 Start/Stop error

According to PC-bus specification and user manual (document UM10204), all transactions begin with a START (S) and are terminated by a STOP (P). The bus is considered to be busy after a START condition. The bus is considered to be free again a certain time after a STOP condition. In other words, if a Start or Stop condition is detected when bus is busy, it can be considered as a **Start/Stop error**.

#### 5.2 Arbitration loss

According to PC-bus specification and user manual (document UM10204), arbitration which is only applicable to multi-master ensures that only one master is allowed to control bus and the data transfer is not corrupted, if more than one master simultaneously tries to control the bus. After the Start condition being issued, arbitration is then required to determine which master will complete its transmission.

The arbitration is performed bit by bit. For a specific bit, each bus master must check whether the bit data to be sent matches the current SDA line status or not. If they match, continue to compare the next bit until the last bit. Otherwise, the master will lose control of the bus, that is, an **Arbitration Loss**.

#### 5.3 Time-out

LPC51U68 I<sup>2</sup>C supports time-out feature and supports two timeout types, SCL time-out and Event time-out.

SCL time-out is reflected by the **SCLTIMEOUT** flag in the STAT register and is asserted when the SCL signal remains low longer than the time configured in the **TIMEOUT** register.

Event time-out is reflected by the **EVENTTIMEOUT** flag in the STAT register, the time between bus events governs the time-out check. These events include Start, Stop, and all changes on the  $I^2C$  clock (SCL). This time-out is asserted when the time between any of these events is longer than the time configured in the TIMEOUT register.

# 6 Glitch generation for I2C transmission error

SCTimer is used to implement glitch generator. As the peripheral is only available in NXP MCUs, the state configurable timer (SCTimer/PWM) is available on all LPC55S69 devices. It can work like traditional timer as a timer/counter. However, the state machine function can be used to detect serial clock on SCL line, which is the most outstanding feature of SCTimer/PWM and greatly enhances the configuration and control flexibility of LPC devices.

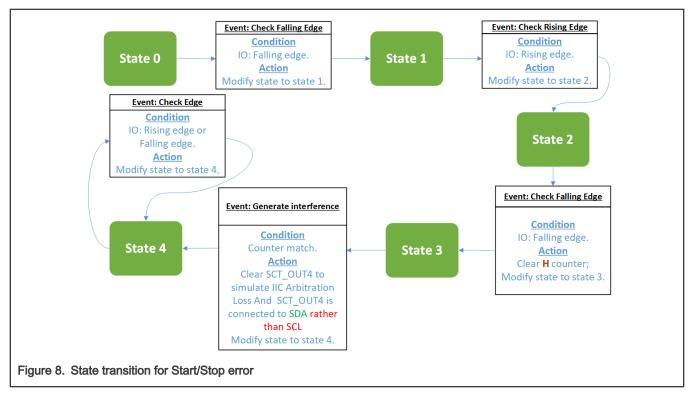

## 6.1 Glitch generation for Start/Stop error

According to the description on Start/Stop error in I2C transmission error type, the bus is busy after the master issues a Start condition. Therefore, a Start or Stop condition is generated when the bus is busy is regarded as a Start/Stop error.

Figure 8 shows the state transition diagram for Start/Stop error. **State 3** has checked the second rising edge of the I<sup>2</sup>C serial clock and then delays for a period of time, during the SCL high level period, pull down SDA. A Start condition is generated when I<sup>2</sup>C bus is busy since the master is addressing slave devices. Therefore, a Start/Stop error occurs.

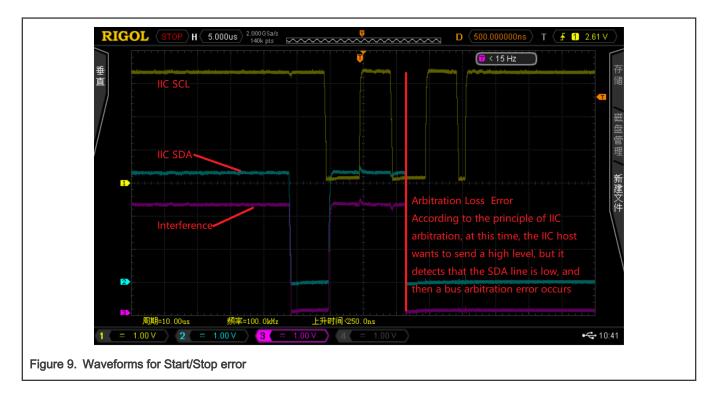

Figure 9 shows the waveforms captured from SCL line, SDA line and glitch generator output. Due to the output of the glitch generator, a Start condition is generated during the high level of the second I<sup>2</sup>C serial clock, which is consistent with the setting of the state machine.

## 6.2 Glitch generation for arbitration loss

According to the description on Arbitration Loss in I2C transmission error type, in the case of multi-master, when certain data bit to be sent by the master is inconsistent with the state of the SDA bus, the master loses control of the bus. At this time, an Arbitration Loss occurs.

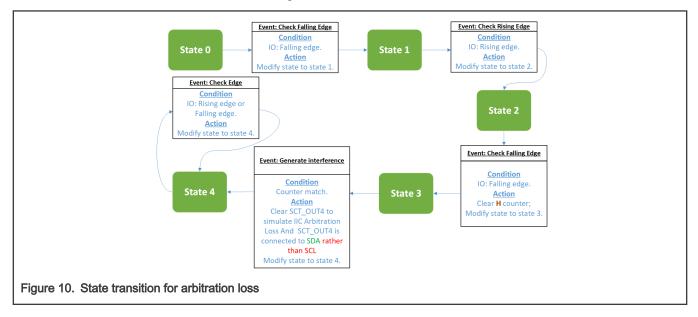

Figure 10 shows the state transition diagram for Arbitration Loss. **State 2** has checked the second falling edge of the I<sup>2</sup>C serial clock and then delays for a period of time, during the SCL low level period, pull down SDA. The slave address is configured as 0x7E and is sent in Most Significant Bit (MSB) mode. In other words, the master wants to send a logic high to SDA during the second serial clock. However, the current state of SDA is logic low. Therefore, an Arbitration Loss occurs.

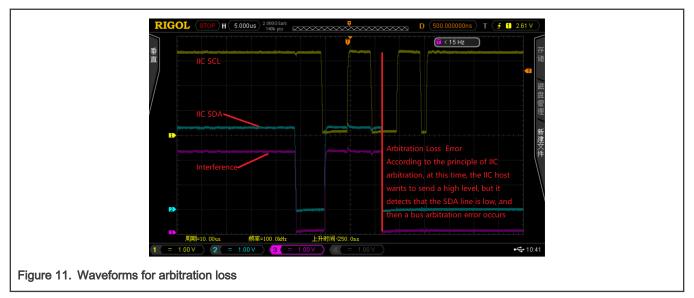

Figure 11 shows the waveforms captured from SCL line, SDA line and glitch generator output. Due to the output of the glitch generator, a mismatch between address bit status which master wants to send and current state of SDA line is generated during the low level of the second I<sup>2</sup>C serial clock, which is consistent with the setting of the state machine.

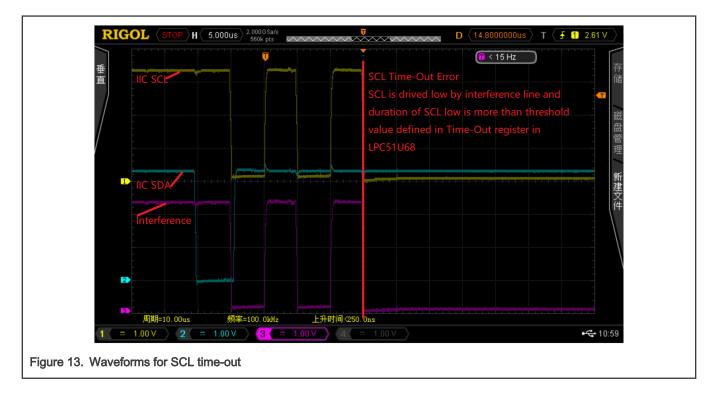

#### 6.3 Glitch generation for SCL time-out

According to the description on SCL time-out in I2C transmission error type, when the SCL signal remains low level longer than the time configured in the TIMEOUT register, an SCL time-out occurs.

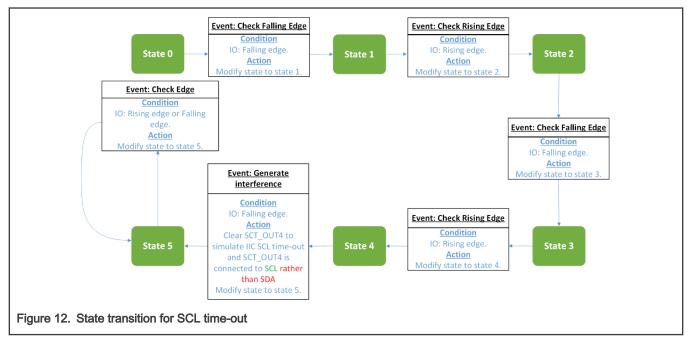

Figure 12 shows the state transition diagram for SCL time-out. **State 4** has checked the third falling edge of the I<sup>2</sup>C serial clock and pull down SCL. Since SCL will always be driven low and the duration of low level will be longer than the time configured in the TIMEOUT register, an SCL time-out occurs.

Figure 13 shows the waveforms captured from SCL line, SDA line and glitch generator output. Due to the output of the glitch generator, SCL is kept at low level, which is consistent with the setting of the state machine.

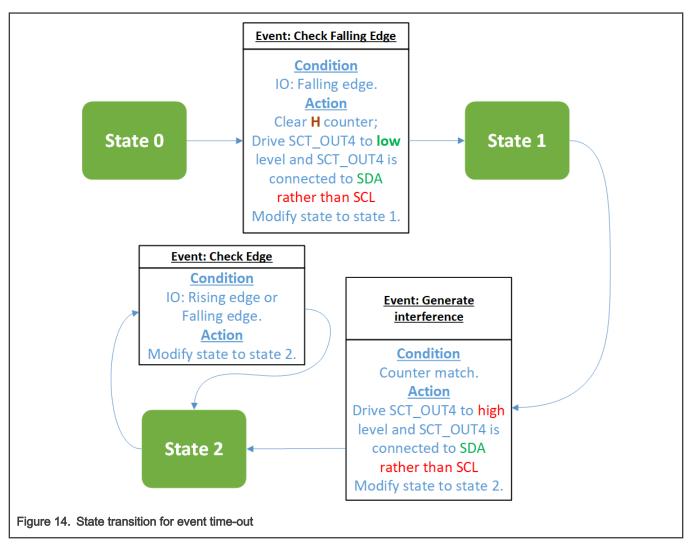

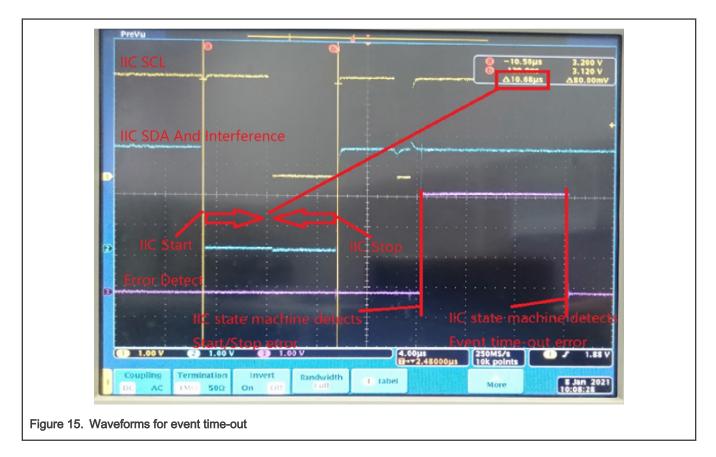

#### 6.4 Glitch generation for event time-out

According to the description on Event time-out in I2C transmission error type, when the time interval between any of bus events is longer than the time configured in the TIMEOUT register, an Event time-out occurs.

Figure 14 shows the state transition diagram for Event time-out. **State 0** drives SDA to low level when has checked the first falling edge of the I<sup>2</sup>C serial clock and then delays for a period of time, drives SDA to high level during SCL high level. This is a Stop condition.

Figure 15 shows the waveforms captured from SCL line, SDA line and glitch generator output. Due to the output of the glitch generator, the time interval between two adjacent Start/Stop events is 10.68  $\mu$ s. It is longer than the time with the value of 10.67  $\mu$ s configured in the TIMEOUT register, as described in Time-out threshold calculation.

Error Detect line in Figure 15 is used to indicate the detection to Start/Stop error and Event time-out. This line is initialized to low level. One rising edge appears on this line when Start/Stop error occurs and one falling edge appears on this line when Event time-out occurs.

# 7 I2C transmission error detection

#### 7.1 SDK support

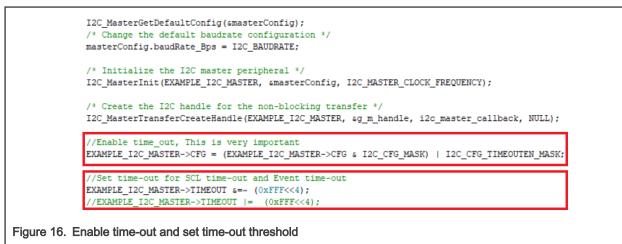

The SDK version used in this document is 2.8.2. The SDK with this version doesn't support  $I^2C$  transmission error detection. To detect  $I^2C$  transmission errors, follow the steps below and all modifications are specific to  $I^2C$  master.

- 1. Download LPC51U68 SDK version 2.8.2.

- 2. Open I<sup>2</sup>C master demo project located in *lboardsllpcxpresso51u68*/*driver\_examples*/*i2clinterrupt\_b2b\_transfer*/*master*.

- 3. By default, the I<sup>2</sup>C timeout function is disabled and needs to be enabled by software. In addition, set the timeout threshold of the TIMEOUT register to the minimum.

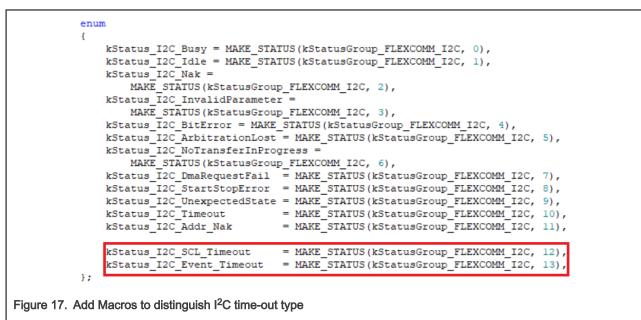

4. The macro kStatus\_I2C\_Timeout in the SDK can't distinguish whether it is SCL time-out or Event time-out. For this reason, two macros are added to distinguish time-out types, as shown in the red square box in Figure 17.

By default, the interrupt flag of the I<sup>2</sup>C master in the SDK does not include SCL time-out and Event time-out. It is necessary to add supports for these two time-out types in the red square box.

```

/*! @brief Common sets of flags used by the driver. */

enum _i2c_flag_constants

{

kI2C_MasterIrqFlags = I2C_INTSTAT_MSTPENDING_MASK |

I2C_INTSTAT_MSTARBLOSS_MASK |

I2C_INTSTAT_MSTSTSTPERR_MASK |

I2C_INTSTAT_EVENTTIMEOUT_MASK,

LI2C_INTSTAT_SCLTIMEOUT_MASK,

kI2C_SlaveIrqFlags = I2C_INTSTAT_SLVPENDING_MASK |

I2C_INTSTAT_SLVDESEL_MASK,

};

Figure 18. I<sup>2</sup>C master interrupt flag support

```

6. Add processing branches for SCL time-out and Event time-out in the I2C\_RunTransferStateMachine function.

```

if ((status & I2C STAT EVENTTIMEOUT MASK) != 0U)

{//Event time-out

GPIO PinWrite(GPIO, 0, 2u, 0);

I2C_MasterClearStatusFlags(base, I2C_STAT_EVENTTIMEOUT_MASK);

base \rightarrow MSTCTL = 0;

I2C MasterEnable(base, false);

I2C MasterEnable(base, true);

base->CFG = (base->CFG & I2C CFG MASK) & (~I2C CFG TIMEOUTEN MASK);

base->CFG = (base->CFG & I2C CFG MASK) | I2C CFG TIMEOUTEN MASK;

return kStatus_I2C_Event_Timeout;

ł

if ((status & I2C_STAT_SCLTIMEOUT_MASK) != 0U)

{//SCL time-out

I2C_MasterClearStatusFlags(base, I2C_STAT_SCLTIMEOUT_MASK);

base \rightarrow MSTCTL = 0;

I2C MasterEnable(base, false);

I2C MasterEnable(base, true);

base->CFG = (base->CFG & I2C_CFG_MASK) & (~I2C_CFG_TIMEOUTEN_MASK);

base->CFG = (base->CFG & I2C_CFG_MASK) | I2C_CFG_TIMEOUTEN_MASK;

return kStatus_I2C_SCL_Timeout;

ŀ

Figure 19. Add processing branches for I<sup>2</sup>C time-out

```

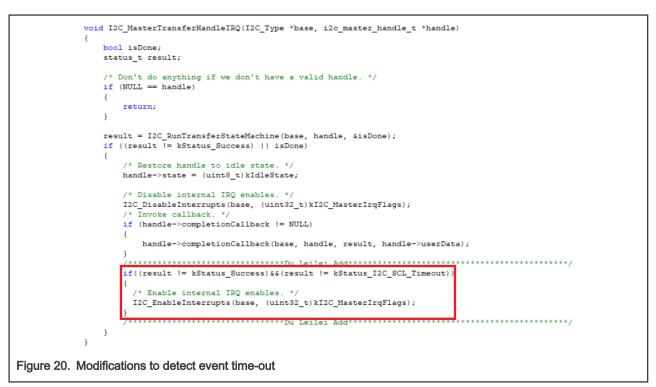

7. This step is very important for detecting I<sup>2</sup>C Event time-out. If this step is missing, Event time-out can't be detected. The reason for this step is described in Event time-out detection.

8. Add I<sup>2</sup>C error output function to I<sup>2</sup>C interrupt callback function marked as i2c master callback.

```

static void i2c_master_callback(

I2C_Type *base,

i2c master handle t *handle,

status t status,

void *userData

١

ł

/* Signal transfer success when received success status. */

if (status == kStatus Success)

{//IIC transfer success

g_MasterCompletionFlag = true;

}

else

{//IIC transfer generates error

//output IIC error type

showErrorInfo(status);

}

}

Figure 21. Add I<sup>2</sup>C error display function

```

```

void showErrorInfo(uint32 t status)

{

switch(status)

{

case kStatus_I2C_StartStopError:

ł

GPIO PinWrite(GPIO, PORTØ IDX, START STOP RED PIN, 0);

//PRINTF("This is IIC Start/Stop error, error code:%d.\r\n", status);

break:

case kStatus_I2C_ArbitrationLost:

{

GPIO_PinWrite(GPIO, PORT1_IDX, ARBITRATION_LOST_GREEN_PIN, 0);

//PRINTF("This is IIC Arbitration Lost error, error code:%d.\r\n", status);

}

break:

case kStatus_I2C_SCL_Timeout:

{

GPIO_PinWrite(GPIO, PORT1_IDX, SCLTIMEOUT_BLUE_PIN, 0);

//PRINTF("This is IIC SCL Time-out error, error code:%d.\r\n", status);

}

break;

case kStatus_I2C_Event_Timeout:

{

GPI0_PinWrite(GPI0, PORT0_IDX, EVENTTIMEOUT_LED_PIN, 0);

//PRINTF("Tis is IIC Event Time-out error,error code:%d.\r\n",status);

break;

case kStatus_I2C_UnexpectedState:

{

GPI0_PinWrite(GPI0, PORT0_IDX, UNEXPECTED_LED_PIN, 0);

//PRINTF("This is IIC UnexpectedState error,error code:%d.\r\n",status);

break;

default:

{

PRINTF("This is IIC unknown error.error code:%d.\r\n".status);

}

}

}

Figure 22. I<sup>2</sup>C error output function

```

#### 7.2 Time-out threshold calculation

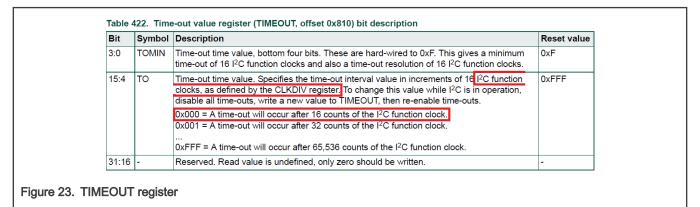

The I<sup>2</sup>C timeout threshold is determined by timeout register marked as **TIMEOUT**. Figure 23 shows the descriptions of the TIMEOUT register bit field and I<sup>2</sup>C function clock.

Figure 24 shows the bit field arrangement of the CLKDIV register.

| Bit   | Symbol | Description                                                                                                                                                                                            | Reset value |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 15:0  | DIVVAL | This field controls how the Flexcomm Interface clock (FCLK) is used by the I <sup>2</sup> C functions that need an internal clock in order to operate. See <u>Section 26.7.2.1 "Rate calculations"</u> | 0x0         |

|       |        | $0x0000 = I^2C$ clock divider provides FCLK divided by 1.<br>$0x0001 = I^2C$ clock divider provides FCLK divided by 2.<br>$0x0002 = I^2C$ clock divider provides FCLK divided by 3.                    |             |

|       |        | $0xFFFF = I^2C$ clock divider provides FCLK divided by 65,536.                                                                                                                                         |             |

| 31:16 | -      | Reserved. Read value is undefined, only zero should be written.                                                                                                                                        | -           |

#### Figure 24. CLKDIV register

As shown in Figure 16, the bit field [15:4] in the TIMEOUT register is set to 0.

As shown in Figure 23, the timeout threshold is 16  $I^2C$  function clocks, and the  $I^2C$  function clock is determined by the value of the CLKDIV register and the  $I^2C$  module clock.

As shown in Figure 25, the I<sup>2</sup>C module clock frequency is set to 12 MHz in this document, and CLKDIV is 7.

As described above, the timeout threshold can be calculated as follows:

- I<sup>2</sup>C clock divider value is CLKDIV + 1 = 8

- $I^2C$  function clock is 12MHz / 8 = 1.5 MHz

- I<sup>2</sup>C timeout threshold is 16\*(1/(1.5 MHz)) = 16 \* ((2/3) μs) = 10.67 μs

#### 7.3 Event time-out detection

As described in I2C transmission error type. Event time-out is asserted when the time interval between any of bus events is longer than the time configured in the TIMEOUT register. Bus events include Start, Stop, and all changes on the I<sup>2</sup>C clock (SCL).

A key point is that Event time-out may be accompanied by Start/Stop error, and Start/Stop error precedes Event time-out. Therefore, I<sup>2</sup>C interrupt can't be disabled after Start/Stop error is detected, otherwise Event time-out will not be detected. This is why the I<sup>2</sup>C interrupt is enabled in Step 7 in SDK support.

#### 7.4 Detection output

This document supports two ways to observe detection output of I<sup>2</sup>C transmission error:

- · To print the I<sup>2</sup>C transmission error type to the console on the PC side through UART

- To light up the LEDs connected to different IO pins when different types of I<sup>2</sup>C transmission errors occur

Table 1 describes the correspondence between I<sup>2</sup>C transmission error type and IO pin.

Figure 25 shows the normal transmission between  $I^2C$  master and  $I^2C$  slave. Master sends data bytes from  $0 \times 00$  to  $0 \times 1f$  and receives data bytes which are the same as the data bytes sent to slave.

Figure 26, Figure 27, Figure 28, and Figure 29 show the detection outputs for Start/Stop error, Arbitration Loss, SCL time-out and Event time-out.

I2C Communication Error Research Master. Master will send data : 0x 0 0x 1 0x 2 0x 3 0x 40x 5 0x 6 0x 7 0x 8 0x 9 Ox a Ox b Ox c Ox d Ox e 0x f 0x13 0x10 0x11 0x12 0x14 0x15 0x16 0x17 0x18 0x19 Ox1a Ox1b Ox1c Ox1d Ox1e  $0 \times 1 f$ EXAMPLE I2C\_MASTER->CLKDIV<-->7 CLKDIV IIC module clock frequency<—>12000000 odni k frequency data Receive sent 0x 2 0x 3 0x6 0x7 0x 0 0x 1 0x 40x 5 0x d 0x f 0x 9 Ox b 0x 8 Ox a Ox c Ox e 0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 Ox1a Ox1b Ox1d Ox1e 0x19 Ox1c 0x1fEnd of I2C example . Figure 25. Normal I<sup>2</sup>C transmission I2C Communication Error Research Master. Master will send data : 0x 2 0x 3  $0 \ge 0 \ge 0 \ge 1$ 0x 40x 5 0x 6 0x 7 0x f Ox d 0x 8 0x 9 Ox a Ox b Ox c Ox e 0x100x11 0x12 0x13 0x14 0x150x16 0x17 0x18 0x19 Ox1a Ox1b Ox1c 0x1d Ox1e 0x1f EXAMPLE I2C MASTER->CLEDIV(->7 This is IIC Start/Stop error, error code:2608. Tis is IIU Event Time-out error,error code:2613. Figure 26. Detection output for Start/Stop error

I2C Communication Error Research Master. Master will send data :  $0 \ge 0$ 0x 2 0x 3 0x 1 0x4 0x5 0x 6 0x 7 Ox c Ox d 0x 8 0x 9 Ox a Ox b Ox e 0x f 0x10 0x12 0x13 0x14 0x15 0x16 0x17 0x11 0x18 0x19 Ox1a Ox1b Ox1c Ox1d Ox1e Ox1f EXAMPLE I2C MASTER->CLKDIV<->7 This is IIC Arbitration Lost error, error code:2605. Tis is IIC Event Time-out error, error code:2613. Figure 27. Detection output for arbitration loss I2C Communication Error Research Master. Master will send data :  $0 \times 0$ 0x 2 0x 3 0x 7 0x 1 0x 40x 5 0x 6 0x 8 0x 9 Ox a Ox b Ox c Ox d Ox e Ox f 0x12 0x13 0x15 0x10 0x11 0x140x16 0x17 0x18 0x19 Ox1a Ox1b Ox1c Ox1d Ox1e 0x1fEXAMPLE I2C MASTER->CLEDIV<->7 This is IIC SCL Time-out error,error code:2612 Figure 28. Detection output for SCL time-out I2C Communication Error Research Master. Master will send data :  $0 \ge 0$ 0x 1 0x 2 0x 3 0x 40x 5 0x 6 0x 7 0x 8 0x 9 Ox a Ox b Ox c Ox d Oxe Ox f 0x10 0x11 0x12 0x13 0x140x15 0x16 0x17 0x18 Ox1b Ox1d 0x19 Ox1a Ox1c Ox1e  $0 \times 1 f$ EXAMPLE T2C MASTER->CLEDIV(->7 This is IIC Start/Stop error, error code:2608. Tis is IIU Event Time=out error, error code:2613. Figure 29. Detection output for event time-out

# 8 How to use LPC51U68 I2C glitch generation and detection demo

To use this demo, perform the following steps:

- 1. Establish hardware environment for this demo as described in Hardware configurations.

- 2. Open I<sup>2</sup>C master code project located in *I2C\_Transfer\_With\_Error\_Detection\boards\lpcxpresso51u68\driver\_examples\i2c\interrupt\_b2b\_transfer\master\mdk* and compile it to generate an executable file.

- Open I<sup>2</sup>C slave code project located in *I2C\_Transfer\_With\_Error\_Detection\boards\lpcxpresso51u68\driver\_examples\i2c\interrupt\_b2b\_transfer\slave\mdk and* compile it to generate an executable file.

- 4. Open glitch generator code project located in *I2C\_Glitch\_Generator\boards\lpcxpresso55s69\driver\_examples\sctimer\edge\_check\_match\cm33\_core0\mdk* and compile it to generate an executable file.

- Program executable file for I<sup>2</sup>C master, I<sup>2</sup>C slave and glitch generator to corresponding evaluation boards mentioned in System overview.

- 6. Open two UART terminals on PC side corresponding to master and slave. The settings are as below:

- Baudrate:115200

- Data bits:8

- · Parity Check: No

- Flow Control: No

- 7. Run the following in sequence:

- a. Glitch generator application

- b. I<sup>2</sup>C slave application

- c. I<sup>2</sup>C master application

# 9 Summary

This document introduces:

- I<sup>2</sup>C bus

- · composition of the system

- · role of each component

- primary transmission errors of I<sup>2</sup>C bus including Start/Stop error, Arbitration Loss, SCL time-out and Event time-out

- · how to design glitch generator using SCTimer state machine

- · how to detect I<sup>2</sup>C transmission errors triggered by glitch

- how to use generation and detection demo for the I<sup>2</sup>C transmission error

Demo code projects are attached to this document. For more technical details, see AN13238SW.

How To Reach Us Home Page: nxp.com Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2021.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 04/2021 Document identifier: AN13238

# arm