**AN11219** Programming the PCA200x family of watch ICs Rev. 1 – 4 September 2012

**Application note**

## **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | PCA2000, PCA2001, PCA2002, PCA2003, Calibration                                                                                                                                                                                                                                                                                                                                                                                               |

| Abstract | The PCA200x are CMOS integrated circuits for battery operated wrist<br>watches with a 32 kHz quartz crystal as the timing element and a bipolar<br>1 Hz stepping motor. The quartz crystal oscillator and the frequency<br>divider are optimized for minimum power consumption. A timing accuracy<br>of 1 ppm is achieved with a programmable, digital frequency adjustment.<br>This document describes how the calibration can be performed. |

## **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| v.1 | 20120904 | Initial version |

# **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN11219

All information provided in this document is subject to legal disclaimers.

## 1. Introduction

The PCA200x are CMOS integrated circuits for battery operated wrist watches with a 32 kHz quartz crystal as the timing element and a bipolar 1 Hz stepping motor. The quartz crystal oscillator and the frequency divider are optimized for minimum power consumption. A timing accuracy of 1 ppm is achieved with a programmable, digital frequency adjustment.

To obtain the minimum overall power consumption for the watch, an automatic motor pulse adaptation function is provided. The circuit supplies only the minimum drive current, which is necessary to ensure a correct motor step. Changing the drive current of the motor is achieved by chopping the motor pulse with a variable duty cycle. The pulse width and the range of the variable duty cycle can be programmed to suit different types of motors.

A pin RESET is provided which can be used for stopping the motor, for accurate time setting, and for accelerated testing of the watch.

The PCA2000 has a battery End Of Life (EOL) warning function. If the battery voltage drops below the EOL threshold voltage (which can be programmed for silver oxide or lithium batteries), the motor steps change from one pulse per second to a burst of four pulses every 4 seconds. The EOL function is not present in PCA2001, PCA2002 and PCA2003.

## 2. Functional description

## 2.1 Motor pulse

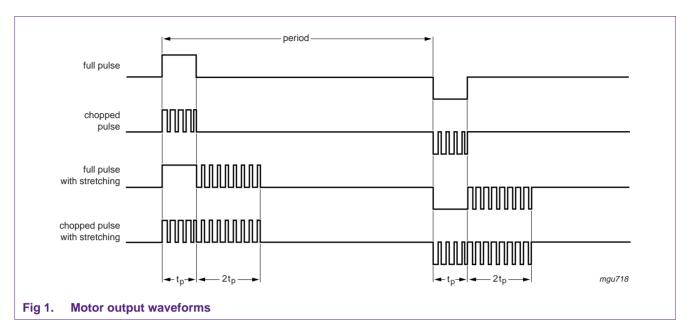

The motor driver delivers pulses with an alternating polarity. The output waveform across the motor terminals is illustrated in Figure 1. Between the motor pulses, both terminals are connected to  $V_{DD}$  which means that the motor is short-circuit.

The following parameters can be programmed in a One Time Programmable (OTP) memory:

- Output periods of 1 s, 5 s, 10 s, 20 s, and 30 s

- Pulse width  $(t_p)$  between 0.98 ms and 7.8 ms in steps of 0.98 ms

- Full or chopped (75 %) output pulse

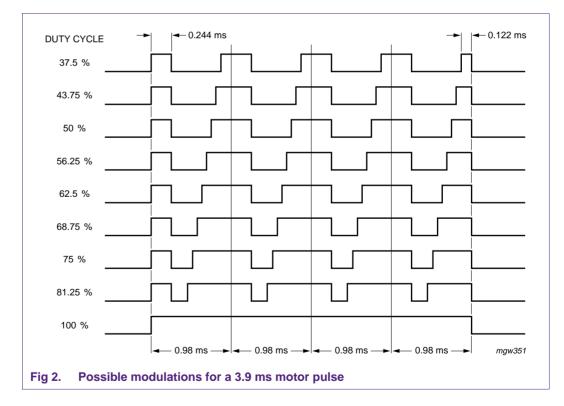

- Pulse stretching: An enlargement pulse added to the primary motor pulse. This enlargement pulse has a duty cycle of 25 % and a width which is twice the programmed motor pulse width. The repetition period for the chopping pattern is 0.98 ms. Figure 2 shows an example for a 3.9 ms pulse.

# AN11219

Programming the PCA200x family of watch ICs

Figure 2 shows an example for a 3.9 ms pulse.

## 2.2 Time calibration

The quartz oscillator frequency would be exactly 32.768 kHz if the oscillator load capacitance would fit exactly the requirements of the crystal. The quartz oscillator frequency is internally divided by 1024 and is nominally

$f_{nom} = 32.768 \text{ kHz} / 1024 = 32 \text{ Hz}$ . This frequency can be measured at pin RESET as a square wave signal ( $f_0$ ).

The guartz crystal oscillator has an integrated capacitance of 5.2 pF, which is lower than the specified load capacitance ( $C_1$ ) of 8.2 pF for the quartz crystal. Therefore, the oscillator frequency is typically 60 ppm higher than 32.768 kHz (corresponding to about 3 minutes too fast per month). This positive frequency offset is compensated by removing the appropriate number of 8192 Hz pulses in the divider chain (maximum 127 pulses), every 1 or 2 minutes. The time correction is given in Table 1.

| Calibration | Correction per step (n = 1) Correction per step (n = 127) |                 |     | ep (n = 127)    |

|-------------|-----------------------------------------------------------|-----------------|-----|-----------------|

| period      | ppm                                                       | seconds per day | ppm | seconds per day |

| 1 minute    | 2.03                                                      | 0.176           | 258 | 22.3            |

| 2 minutes   | 1.017                                                     | 0.088           | 129 | 11.15           |

#### Table 1. **Time calibration**

After measuring the effective oscillator frequency, the number of correction pulses must be calculated and stored together with the calibration period in the OTP memory (see Section 3 on page 12).

Before programming the calibration word A (state 3) which contains the number of 8192 Hz pulses to be removed and the calibration period, first the motor pulse parameters must be programmed using word B (state 4).

Since the programming is done using an OTP, a register bit can be changed from 0 to 1, but once programmed to 1 it can't be set back to 0.

An automatic test sequence might have two phases:

- Program the IC in accordance with the mechanism used, followed by calibration

- Verify that the IC has been correctly programmed (optional for large series production)

## 2.3 Reset

At pin RESET an output signal with the frequency fo is provided. Connecting pin RESET to V<sub>DD</sub> stops the motor drive and opens the motor switches. After releasing pin RESET, the first motor pulse is generated exactly one period later with the opposite polarity to the last pulse before stopping. The debounce time for the reset function is between 31 ms and 62 ms.

Connecting pin RESET to V<sub>SS</sub> activates the test mode. In this mode the motor output frequency is 32 Hz, which can be used to test the mechanical function of the watch.

## 2.4 Programming possibilities

## 2.4.1 PCA2000 and PCA2001

The programming data is organized in an array of four 8-bit words (see Table 2):

Word A — for the time calibration,

Words B and C — for setting of the motor pulses and

Word D — for the type recognition.

| Table 2. | PCA2000 and | <b>PCA2001</b> | register | overview |

|----------|-------------|----------------|----------|----------|

|----------|-------------|----------------|----------|----------|

| Word | Bit                                    |            |       |                                  |                                 |                     |                     |     |

|------|----------------------------------------|------------|-------|----------------------------------|---------------------------------|---------------------|---------------------|-----|

|      | 1                                      | 2          | 3     | 4                                | 5                               | 6                   | 7                   | 8   |

| A    | number of 8192 Hz pulses to be removed |            |       |                                  | calibration period              |                     |                     |     |

| В    | lowest stage:                          | duty cycle | stage |                                  | highest<br>stage:<br>duty cycle | pulse<br>stretching | factory test bi     | its |

| С    | pulse width                            |            |       | ne delay betwe<br>detection puls |                                 | EOL voltage         | factory test<br>bit |     |

| D    | type                                   |            |       |                                  | factory test b                  | oits                | <u>і</u>            |     |

#### Table 3. PCA2000 and PCA2001 description of word A bits

| Bit           | Value  | Description                                                                                     |  |  |

|---------------|--------|-------------------------------------------------------------------------------------------------|--|--|

| Inhibition ti | me     |                                                                                                 |  |  |

| 1 to 7        | -      | adjust the number of the 8192 Hz pulses to be removed;<br>bit 1 is the MSB and bit 7 is the LSB |  |  |

| Calibration   | period |                                                                                                 |  |  |

| 8             | 0      | 1 minute                                                                                        |  |  |

|               | 1      | 2 minutes                                                                                       |  |  |

|               |        |                                                                                                 |  |  |

#### Table 4. PCA2000 and PCA2001 description of word B bits

| Bit           | Value               | Description         |

|---------------|---------------------|---------------------|

| Duty cycle lo | owest driving stage | 9                   |

| 1 to 2        | 00                  | 37.5 %              |

|               | 01                  | 43.75 %             |

|               | 10                  | 50 %                |

|               | 11                  | 56.25 %             |

| Number of d   | riving stages       |                     |

| 3 to 4        | 00                  | 3                   |

|               | 01                  | 4                   |

|               | 10                  | 5                   |

|               | 11                  | 6 <mark>[1]</mark>  |

| Duty cycle h  | ighest driving stag | le                  |

| 5             | 0                   | 75 % <sup>[2]</sup> |

|               | 1                   | 100 %               |

Pulse stretching

All information provided in this document is subject to legal disclaimers.

| Table 4. | PCA2000 and PCA2001 | description of word B bits continued |

|----------|---------------------|--------------------------------------|

|          |                     |                                      |

| Bit               | Value | Description                                              |

|-------------------|-------|----------------------------------------------------------|

| 6                 | 0     | no pulse stretching                                      |

|                   | 1     | pulse of $2 \times t_p$ and duty cycle of 25 % are added |

| Factory test bits |       |                                                          |

| 7 to 8            | -     | -                                                        |

[1] Including the highest driving stage, which one has no motor step detection.

[2] If the maximum duty cycle of 75 % is selected, not all programming combinations are possible since the second highest level must be smaller than the highest driving level.

| Bit                                | Value | Description           |

|------------------------------------|-------|-----------------------|

| Pulse width t <sub>p</sub>         |       |                       |

| 1 to 3                             | 000   | 0.98 ms               |

|                                    | 001   | 1.95 ms               |

|                                    | 010   | 2.93 ms               |

|                                    | 011   | 3.91 ms               |

|                                    | 100   | 4.88 ms               |

|                                    | 101   | 5.86 ms               |

|                                    | 110   | 6.84 ms               |

|                                    | 111   | 7.81 ms               |

| Time delay t <sub>d(max)</sub> [1] |       |                       |

| 4 to 6                             | 000   | 3.91 ms               |

|                                    | 001   | 4.88 ms               |

|                                    | 010   | 5.86 ms               |

|                                    | 011   | 6.84 ms               |

|                                    | 100   | 7.81 ms               |

|                                    | 101   | 8.79 ms               |

|                                    | 110   | 9.77 ms               |

|                                    | 111   | 10.74 ms              |

| EOL voltage of the battery         |       |                       |

| 7                                  | 0     | 1.38 V (silver-oxide) |

|                                    | 1     | 2.5 V (lithium)       |

| Factory test bit                   |       |                       |

| 8                                  | -     | -                     |

## Table 5. PCA2000 and PCA2001 description of word C bits

[1] Between positive and negative detection pulses.

## 2.4.2 PCA2002

The programming data is organized in an array of four 8-bit words (see Table 6).

Word A — for the time calibration,

Word B — for setting of the motor pulses,

Word C - is not used with PCA2002 and

| Word D — | for the type | recognition. |

|----------|--------------|--------------|

|----------|--------------|--------------|

| Table 6. | PCA2002 | register | overview |

|----------|---------|----------|----------|

|----------|---------|----------|----------|

| Word | Bit      |              |              |            |                     |   |               |                     |

|------|----------|--------------|--------------|------------|---------------------|---|---------------|---------------------|

|      | 1        | 2            | 3            | 4          | 5                   | 6 | 7             | 8                   |

| A    | number   | of 8192 Hz p | oulses to be | e removed  |                     |   |               | calibration period  |

| В    | pulse wi | dth          |              | output per | iod                 |   | duty<br>cycle | pulse<br>stretching |

| С    | -        | -            | -            | -          | -                   | - | -             | -                   |

| D    | type     |              |              |            | factory<br>test bit | - | -             | -                   |

There are four words, only words A and B can be programmed. The meaning of the individual bits is given in Table 7 and Table 8.

**Application note**

|               | CA2002 descriptio | II OI WOI'U A DILS                                                                           |

|---------------|-------------------|----------------------------------------------------------------------------------------------|

| Bit           | Value             | Description                                                                                  |

| Inhibit time  |                   |                                                                                              |

| 1 to 7        | -                 | adjust the number of the 8192 Hz pulses to be removed; bit 1 is the MSB and bit 7 is the LSB |

| Calibration p | period            |                                                                                              |

| 8             | 0                 | 1 minute                                                                                     |

|               | 1                 | 2 minutes                                                                                    |

## Table 7. PCA2002 description of word A bits

| Bit           | Value         | Description                                                         |

|---------------|---------------|---------------------------------------------------------------------|

| Pulse width t |               | •                                                                   |

| 1 to 3        | 000           | 0.98 ms                                                             |

|               | 001           | 1.95 ms                                                             |

|               | 010           | 2.93 ms                                                             |

|               | 011           | 3.91 ms                                                             |

|               | 100           | 4.88 ms                                                             |

|               | 101           | 5.86 ms                                                             |

|               | 110           | 6.84 ms                                                             |

|               | 111           | 7.81 ms                                                             |

| Output perio  | d (s)         |                                                                     |

| 4 to 6        | 000           | 1                                                                   |

|               | 001           | 5                                                                   |

|               | 010           | 10                                                                  |

|               | 011           | 20                                                                  |

|               | 100           | 30                                                                  |

| Duty cycle of | f motor pulse |                                                                     |

| 7             | 0             | 75 %                                                                |

|               | 1             | 100 %                                                               |

| Pulse stretch | ning          |                                                                     |

| 8             | 0             | no pulse stretching                                                 |

|               | 1             | a pulse width of $2 \times t_p$ and a duty factor of 25 % are added |

## Table 8. PCA2002 description of word B bits

## 2.4.3 PCA2003

The programming data is organized in an array of four 8-bit words (see Table 9):

Word A — for the time calibration,

Words B and C - for setting of the motor pulses and

Word D — for the type recognition.

## Table 9. PCA2003 register overview

| Word | Bit           | t              |                                                                                   |                                  |                |                  |                     |                    |  |

|------|---------------|----------------|-----------------------------------------------------------------------------------|----------------------------------|----------------|------------------|---------------------|--------------------|--|

|      | 1             | 2              | 3                                                                                 | 4                                | 5              | 6                | 7                   | 8                  |  |

| A    | number of 81  | 92 Hz pulses t | o be removed                                                                      |                                  |                |                  |                     | calibration period |  |

| В    | lowest stage: | duty cycle     | number of driving stages highest pulse output period stage: duty stretching cycle |                                  |                |                  |                     |                    |  |

| С    | pulse width   |                |                                                                                   | ne delay betwe<br>detection puls |                | output<br>period | factory test<br>bit |                    |  |

| D    | type          |                |                                                                                   | 1                                | factory test b | oits             |                     |                    |  |

## Table 10. PCA2003 description of word A bits

| Bit               | Value | Description                                                                                     |

|-------------------|-------|-------------------------------------------------------------------------------------------------|

| Inhibition time   |       |                                                                                                 |

| 1 to 7            | -     | adjust the number of the 8192 Hz pulses to be removed;<br>bit 1 is the MSB and bit 7 is the LSB |

| Calibration perio | d     |                                                                                                 |

| 8                 | 0     | 1 minute                                                                                        |

|                   | 1     | 2 minutes                                                                                       |

## Table 11. PCA2003 description of word B bits

| Bit          | Value                | Description                                              |

|--------------|----------------------|----------------------------------------------------------|

| Duty cycle l | owest driving stage  | 9                                                        |

| 1 to 2       | 00                   | 37.5 %                                                   |

|              | 01                   | 43.75 %                                                  |

|              | 10                   | 50 %                                                     |

|              | 11                   | 56.25 %                                                  |

| Number of c  | triving stages       |                                                          |

| 3 to 4       | 00                   | 3                                                        |

|              | 01                   | 4                                                        |

|              | 10                   | 5                                                        |

|              | 11                   | 6 <u>[1]</u>                                             |

| Duty cycle h | nighest driving stag | je                                                       |

| 5            | 0                    | 75 % <mark>[2]</mark>                                    |

|              | 1                    | 100 %                                                    |

| Pulse stretc | hing                 |                                                          |

| 6            | 0                    | no pulse stretching                                      |

|              | 1                    | pulse of $2 \times t_p$ and duty cycle of 25 % are added |

| Output perio | bd                   |                                                          |

| 7 to 8       | 00                   | 1 s                                                      |

|              | 01                   | 5 s                                                      |

|              | 10                   | 10 s                                                     |

|              | 11                   | 20 s                                                     |

All information provided in this document is subject to legal disclaimers.

- [1] Including the highest driving stage, which one has no motor step detection.

- [2] If the maximum duty cycle of 75 % is selected, not all programming combinations are possible since the second highest level must be smaller than the highest driving level.

| Bit          | Value      | Description                          |  |

|--------------|------------|--------------------------------------|--|

| Pulse width  | tp         |                                      |  |

| 1 to 3       | 000        | 0.98 ms                              |  |

|              | 001        | 1.95 ms                              |  |

|              | 010        | 2.93 ms                              |  |

|              | 011        | 3.91 ms                              |  |

|              | 100        | 4.88 ms                              |  |

|              | 101        | 5.86 ms                              |  |

|              | 110        | 6.84 ms                              |  |

|              | 111        | 7.81 ms                              |  |

| Time delay f | d(max) [1] |                                      |  |

| 4 to 6       | 000        | 3.91 ms                              |  |

|              | 001        | 4.88 ms                              |  |

|              | 010        | 5.86 ms                              |  |

|              | 011        | 6.84 ms                              |  |

|              | 100        | 7.81 ms                              |  |

|              | 101        | 8.79 ms                              |  |

|              | 110        | 9.77 ms                              |  |

|              | 111        | 10.74 ms                             |  |

| Output perio | bd         |                                      |  |

| 7            | 0          | bit 7 and 8 of word B active         |  |

|              | 1          | 30 s, bit 7 and 8 of word B inactive |  |

| Factory test | bit        |                                      |  |

| 8            | -          | -                                    |  |

## Table 12. PCA2003 description of word C bits

[1] Between positive and negative detection pulses.

## 2.5 Type recognition

Byte D is read only and is to determine which type of the PCA200x family is used in a particular application.

## Table 13. Description of word D bits

| Bit              | Value | Description |

|------------------|-------|-------------|

| Type recognition |       |             |

| 1 to 4           | 0000  | PCA2002     |

|                  | 1000  | PCA2000     |

|                  | 0100  | PCA2001     |

|                  | 1100  | PCA2003     |

# 3. Programming procedure

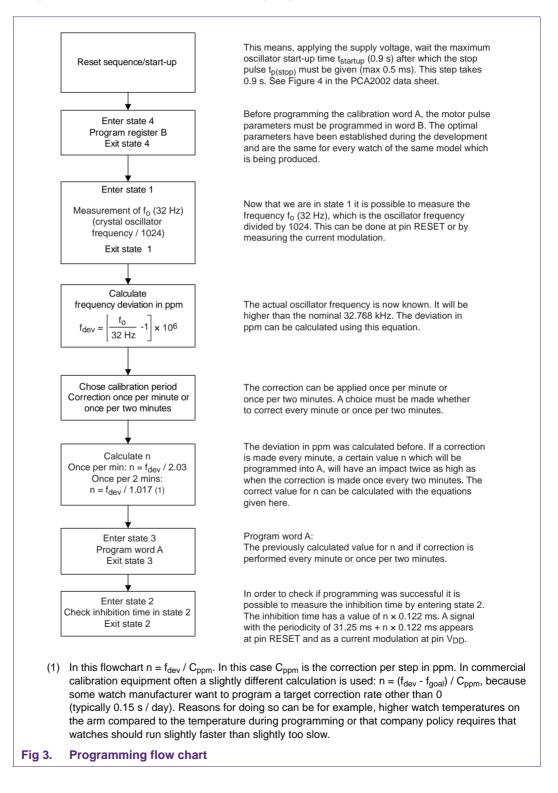

The flow chart in <u>Figure 3</u> indicates the programming procedure of the PCA2002. Details are given in the description on the following pages.

AN11219

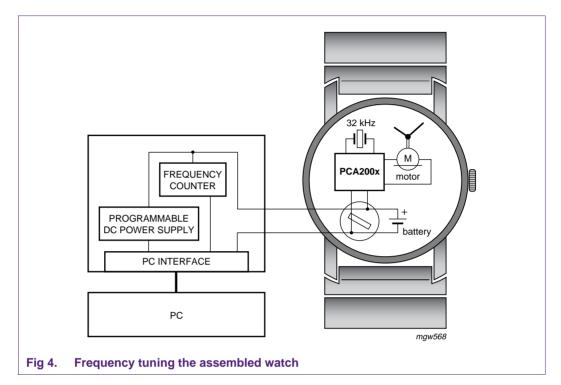

For a watch, it is essential that the timing calibration can be made after the watch has been fully assembled. In this situation, the supply pins are often the only terminals which are still accessible. Figure 4 shows the set-up for programming<sup>1</sup> the assembled watch.

Executing a power-on-reset, writing to the OTP cells and performing the related functional checks is achieved in the PCA200x by modulating the supply voltage. The necessary control circuit consists basically of a voltage level detector, an instruction counter which determines the function to be performed and an 8-bit shift register, which allows programming the OTP cells of an 8-bit word in one step and which acts also as a data pointer for checking the OTP content.

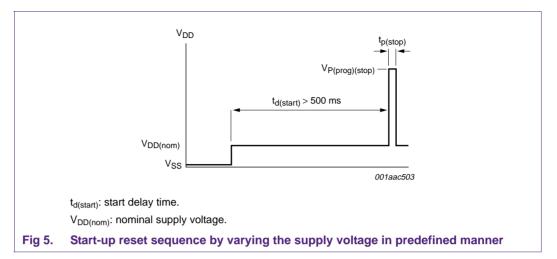

In order to ensure that the oscillator starts up correctly after powering up the watch, a reset sequence must be executed. The reset sequence is given in Figure 5.

**Important:** The programming procedure requires a stable oscillator, which means that a waiting time, determined by the start-up time of the oscillator, is necessary after power-up of the circuit. The maximum oscillator start-up time of the oscillator is 0.9 s. In Figure 5 " $t_{d(start)} > 500$  ms" is indicated. In most cases this is enough but it may be necessary to reserve up to 900 ms for the oscillator start-up. This reset sequence is only required after power-up and not in between the various programming stages. That means that it is required just once during a normal programming procedure.

All information provided in this document is subject to legal disclaimers

<sup>1.</sup> As far as NXP CWG knows, the two Swiss companies, Witschi and Femto, offer commercial programmers.

The control circuit consists of an instruction counter which determines the function to be performed and an 8-bit shift register, which allows programming the OTP cells of an 8-bit word in one step and which acts also as a data pointer for checking the OTP content. There are six different states. In a normal programming procedure, these states are not accessed in sequence from 1 to 6. The different states are:

- State 1 measurement of  $f_o$  (32Hz), the oscillator frequency divided by 1024

- State 2 measurement of the inhibition time

- State 3 write/check word A

- State 4 write/check word B

- State 5 check word C (for PCA2002 don't care since no meaning)

- State 6 check word D (type recognition)

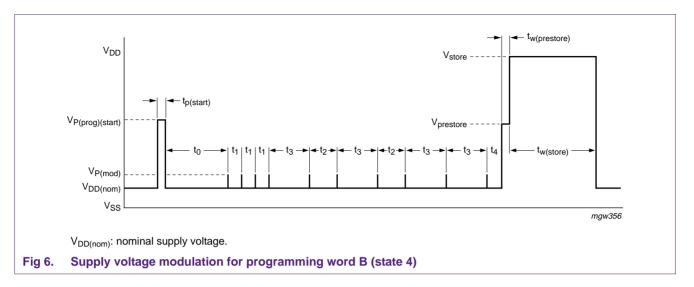

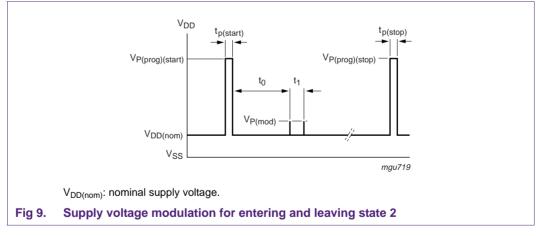

Every instruction state is switched on with a programming start pulse,  $V_{P(prog)(start)}$  with duration  $t_{p(start)}$ . This is the only way to enter the programming mode. For details about voltage levels and duration of the various pulses, please refer to the data sheets. After this large pulse, an initial waiting time  $t_0$  is required. The programming instructions are then entered by modulating the supply voltage with small pulses (amplitude  $V_{P(mod)}$ ) and pulse width  $t_{mod}$ ). The first small pulse defines the start time, the following pulses perform three different functions depending on the time delay ( $t_d$ ) from the preceding pulse (see Figure 6, Figure 7, Figure 8 and Figure 9):

- t<sub>d</sub> = t<sub>1</sub> (0.7 ms) increments the instruction counter

- $t_d = t_2$  (1.7 ms) clocks the shift register with data = logic 0

- $t_d = t_3$  (2.7 ms) clocks the shift register with data = logic 1

After the  $V_{P(prog)(start)}$  pulse, the instruction counter is in state 1 and the data shift register is cleared.

As mentioned above there is only one method to enter the programming mode, but there are two different methods to leave the programming mode:

1. The instruction stated ends with a second pulse to  $V_{P(\text{prog})(\text{stop})}$  or with the pulse to  $V_{\text{store}}.$

2. If no pulse to V<sub>P(prog)(stop)</sub> or V<sub>store</sub> is given, the instruction states are terminated automatically two seconds after the last supply modulation pulse.

Examples are given below.

## 3.1 Enter state 4, program register B and exit state 4

Before programming the calibration word A, the motor pulse parameters must be programmed in word B. This means that state 4 is needed. The optimal parameters depend on the mechanism that is being used and during development of the watch the best settings for the mechanism must be established. These are then the same for every watch of the same model that is being produced.

In general, in order to program a memory word (here memory word B), the following steps need to be performed:

- 1. Start with a  $V_{P(prog)(start)}$  pulse, wait for the time period  $t_0$  and then set the instruction counter to the word to be written ( $t_d = t_1$ ). After  $t_0$  the first small pulse puts the IC in state 1. Every consecutive waiting time  $t_d = t_1$  followed by a small pulse increases the state;

- Enter the data to be stored into the shift register (t<sub>d</sub> = t<sub>2</sub> or t<sub>3</sub>), LSB first (bit 8) and MSB last (bit 1);

- 3. Applying the two-stage programming pulse V<sub>prestore</sub> followed by V<sub>store</sub> stores the word. The delay between the last data bit and the pre-store pulse V<sub>prestore</sub> is  $t_d = t_4$ . Store the word by raising the supply voltage to V<sub>store</sub>; the delay between the last data bit and the store pulse is  $t_d$ .

The example below in Figure 6 shows programming of B = 110101 (the sequence is LSB first and MSB last)<sup>2</sup>. It performs the following functions:

- Start;

- Setting the instruction counter to state 4 (word B);

- Entering data word 110101 into the shift register (sequence: LSB first, MSB last);

- Writing the OTP cells for word B.

<sup>2.</sup> This example is only valid for PCA2000 and PCA2001; for PCA2002 the sequence would be 11001001, programming a pulse width of 6.8 ms, an output period of 10 s, a duty cycle of 75 %. and a pulse stretching of 1.

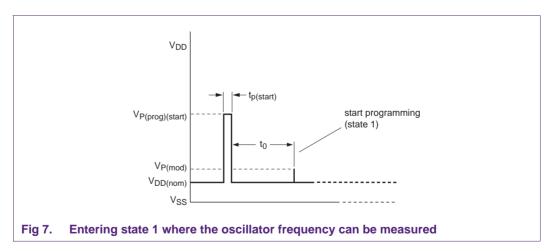

## 3.2 Enter state 1, measure the oscillator frequency and leave state 1

Now that the motor pulse parameters have been programmed, it is possible to calibrate the watch. This is done by first measuring the actual oscillator frequency. From there the required number of inhibition pulses can be calculated. In short, enter state 1, measure the frequency  $f_o$  (which is the oscillator frequency divided by 1024) and leave state 1. State 1 starts with a pulse to  $V_P$  and ends with a second pulse to  $V_P$  as indicated below.

In order to enter state 1 the following step needs to be performed:

1. Start with a  $V_{P(prog)(start)}$  pulse, wait for the time period  $t_0$  and then give a small pulse.

This is indicated in Figure 7.

The frequency  $f_o$  can either be monitored directly at pin RESET or as a modulation of the supply current (a modulating resistor of 30 k $\Omega$  is connected between V<sub>DD</sub> and V<sub>SS</sub> when the signal at pin RESET is HIGH, increasing the supply current accordingly).

Leave state 1 by giving a pulse to  $V_{P(prog)(stop)}$ . If no such pulse is given, state 1 is left automatically two seconds after the last supply modulation pulse.

# 3.3 Calculate the frequency deviation of the oscillator in ppm, and the value of n

The actual oscillator frequency is now known. It was purposely set higher than 32.768 kHz. The frequency adjustment is made by introducing longer seconds at certain intervals (pulses from the quartz are inhibited at those intervals). During the inhibition sequence one 32 Hz-period at the pin RESET is increased by n x 0.122 ms. Here n is the number that is programmed in the OTP. The programmed inhibition time can later easily be measured in state 2, see Section 3.5.

The frequency deviation in ppm can be calculated as follows:

$$f_{dev} = \left(\frac{f_o}{32 \,\mathrm{Hz}} - I\right) \times 10^6 \tag{1}$$

The correction can be applied once per minute or once per two minutes (calibration period). This is a choice that has to be made.

If a correction is made ever minute a certain value n which will be programmed into word A will have an impact twice as high as when the correction is made only once every two minutes. The correct value for n (the number of 8192 Hz pulses to be inhibited) can be calculated with the following formulas (see also Table 1):

- Correction once per minute:  $n = f_{dev}/2.03$

- Correction once per two minutes:  $n = f_{dev}/1.017$

The calculated value n must be programmed into register A, together with the calibration period in the next step.

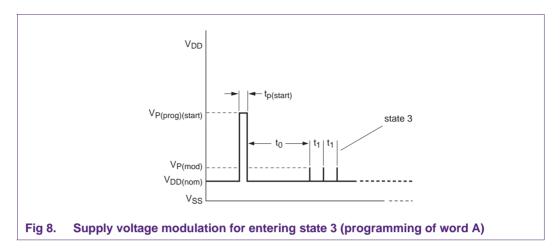

## 3.4 Enter state 3, program word A and leave state 3

In general, in order to program a memory word (here memory word A), the following steps need to be performed:

- 1. Start with a  $V_{P(prog)(start)}$  pulse, wait for the time period  $t_0$  and then set the instruction counter to the word to be written ( $t_d = t1$ ). After  $t_0$  the first small pulse puts the IC in state 1. Every consecutive waiting time  $t_d = t1$  followed by a small pulse increases the state;

- Enter the data to be stored into the shift register (t<sub>d</sub> = t<sub>2</sub> or t<sub>3</sub>), LSB first (bit 8) and MSB last (bit 1);

- 3. Applying the two-stage programming pulse V<sub>prestore</sub> followed by V<sub>store</sub> stores the word. The delay between the last data bit and the pre-store pulse V<sub>prestore</sub> is  $t_d = t_4$ . Store the word by raising the supply voltage to V<sub>store</sub>; the delay between the last data bit and the store pulse is  $t_d$ .

After state 3 has been entered the programming of the word and leaving state 3 is as indicated in the example of Figure 8.

## 3.5 Check the inhibition time in State 2

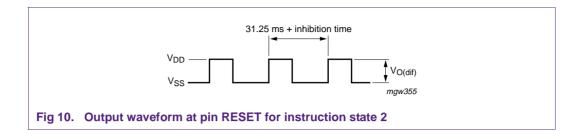

In order to check whether programming was successful it is possible to measure the inhibition time. Also the inhibition time can either be monitored directly at pin RESET or as a modulation of the supply current (a modulating resistor of 30 k $\Omega$  is connected between V<sub>DD</sub> and V<sub>SS</sub> when the signal at pin RESET is HIGH, increasing the supply current accordingly). The inhibition time is measured in state 2. The inhibition time has a value of  $n \times 0.122$  ms (reciprocal of 8192 Hz). A signal with the periodicity of 31.25 ms +  $n \times 0.122$  ms appears at pin RESET and as a current modulation at pin V<sub>DD</sub>, see Figure 9 and Figure 10. The 31.25 ms is the reciprocal of 32 Hz.

Figure 9 above indicates how to enter and leave state 2. Figure 10 below indicates the output waveforms that appear at pin RESET in state 2.

## 4. References

- [1] AN10439 Wafer Level Chip Size Package

- [2] AN10706 Handling bare die

- [3] PCA2000; PCA2001 32 kHz watch circuit with programmable adaptive motor pulse; product data sheet

- [4] **PCA2002** 32 kHz watch circuit with programmable output period and pulse width; product data sheet

- [5] **PCA2003** 32 kHz watch circuit with programmable adaptive motor pulse and pulse period; product data sheet

# 5. Legal information

## 5.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

## 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# 6. Tables

| Table 1.  | Time calibration                          |

|-----------|-------------------------------------------|

| Table 2.  | PCA2000 and PCA2001 register overview6    |

| Table 3.  | PCA2000 and PCA2001 description of word A |

|           | bits                                      |

| Table 4.  | PCA2000 and PCA2001 description of word B |

|           | bits                                      |

| Table 5.  | PCA2000 and PCA2001 description of word C |

|           | bits7                                     |

| Table 6.  | PCA2002 register overview                 |

| Table 7.  | PCA2002 description of word A bits9       |

| Table 8.  | PCA2002 description of word B bits9       |

| Table 9.  | PCA2003 register overview10               |

| Table 10. | PCA2003 description of word A bits10      |

| Table 11. | PCA2003 description of word B bits10      |

| Table 12. | PCA2003 description of word C bits11      |

| Table 13. | Description of word D bits11              |

# 7. Figures

| Fig 1.  | Motor output waveforms4                             |

|---------|-----------------------------------------------------|

| Fig 2.  | Possible modulations for a 3.9 ms motor pulse 4     |

| Fig 3.  | Programming flow chart                              |

| Fig 4.  | Frequency tuning the assembled watch13              |

| Fig 5.  | Start-up reset sequence by varying the supply       |

|         | voltage in predefined manner14                      |

| Fig 6.  | Supply voltage modulation for programming word B    |

|         | (state 4)16                                         |

| Fig 7.  | Entering state 1 where the oscillator frequency can |

|         | be measured                                         |

| Fig 8.  | Supply voltage modulation for entering state 3      |

|         | (programming of word A)18                           |

| Fig 9.  | Supply voltage modulation for entering and leaving  |

|         | state 2                                             |

| Fig 10. | Output waveform at pin RESET for instruction        |

|         | state 2                                             |

# 8. Contents

| 1     | Introduction 3                                  |

|-------|-------------------------------------------------|

| 2     | Functional description 3                        |

| 2.1   | Motor pulse 3                                   |

| 2.2   | Time calibration 5                              |

| 2.3   | Reset 5                                         |

| 2.4   | Programming possibilities                       |

| 2.4.1 | PCA2000 and PCA2001                             |

| 2.4.2 | PCA2002 7                                       |

| 2.4.3 | PCA2003 9                                       |

| 2.5   | Type recognition 11                             |

| 3     | Programming procedure 12                        |

| 3.1   | Enter state 4, program register B and exit      |

|       | state 4 15                                      |

| 3.2   | Enter state 1, measure the oscillator frequency |

|       | and leave state 1 16                            |

| 3.3   | Calculate the frequency deviation of the        |

|       | oscillator in ppm, and the value of n 17        |

| 3.4   | Enter state 3, program word A and leave         |

|       | state 3 17                                      |

| 3.5   | Check the inhibition time in State 2 18         |

| 4     | References                                      |

| 5     | Legal information 20                            |

| 5.1   | Definitions                                     |

| 5.2   | Disclaimers                                     |

| 5.3   | Trademarks 20                                   |

| 6     | Tables                                          |

| 7     | Figures 22                                      |

| 8     | Contents                                        |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

### © NXP B.V. 2012.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 4 September 2012 Document identifier: AN11219