# LPC SPIFI外设

## SPIFI-NXP-MICROCONTROLLERS

Last Updated: Apr 8, 2022

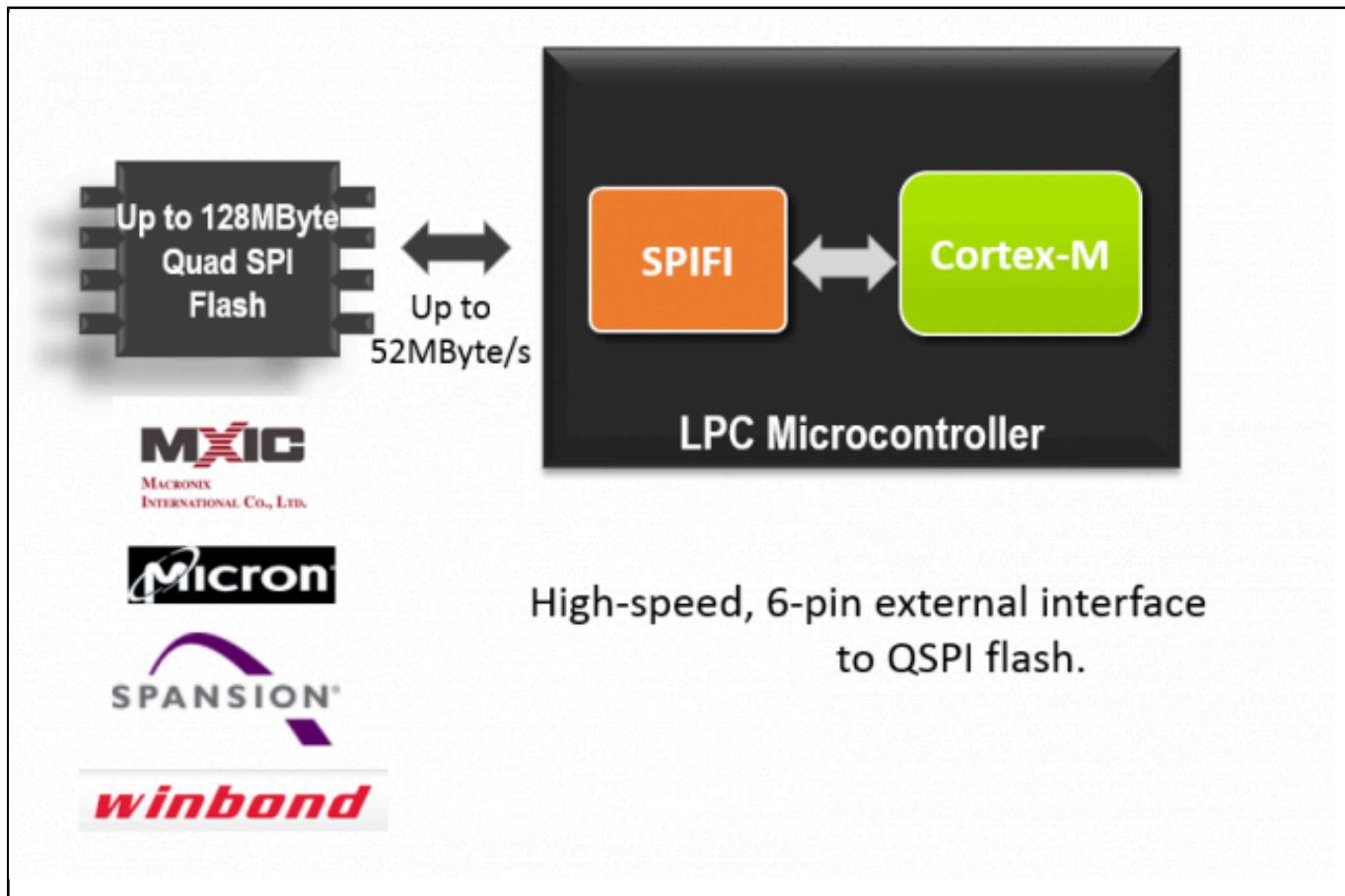

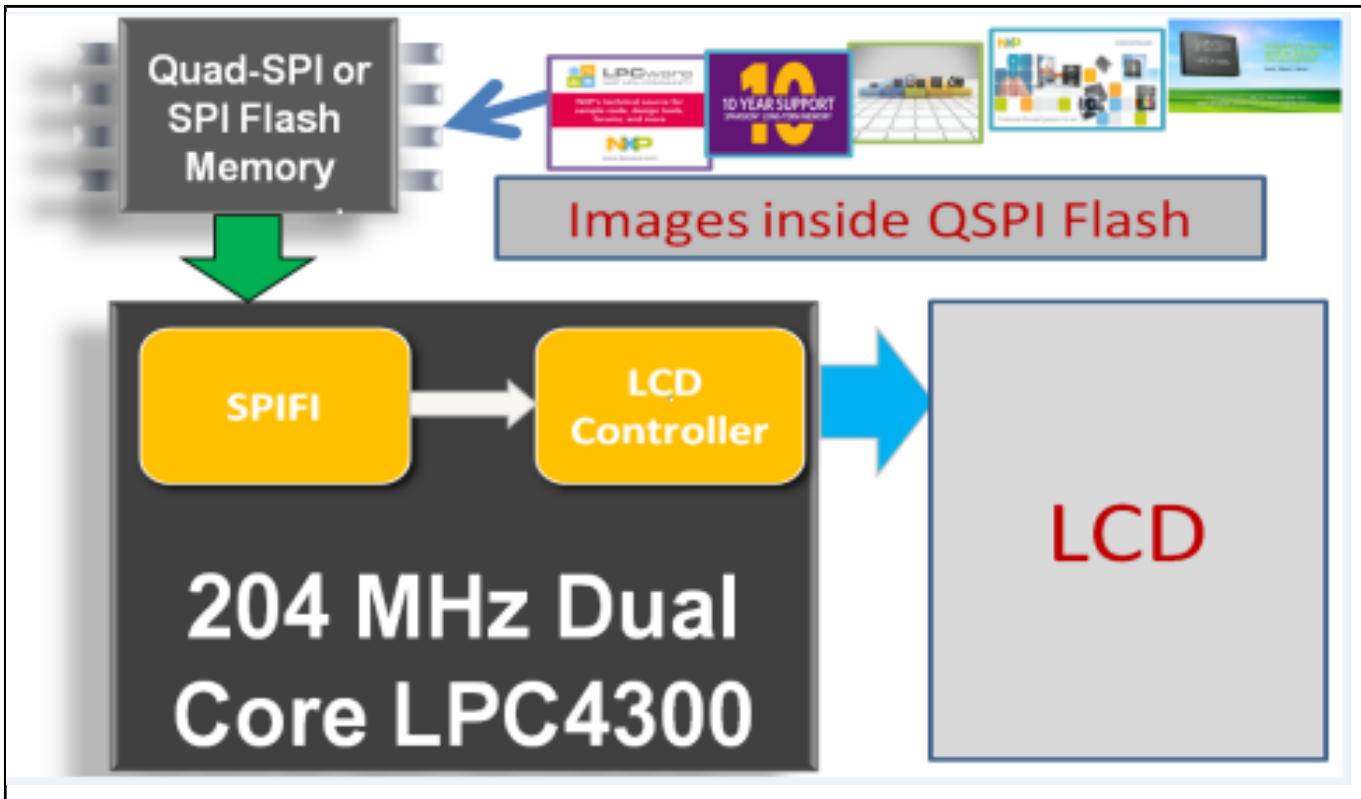

**SPI**闪存接口(**SPIFI**)允许低引脚数的串行闪存存储器连接到一个基于**ARM**的**LPC**存储器，与高引脚数的并行闪存存储器相比，性能损失很小。启动时几个命令配置接口后，通过处理器和/或**DMA**通道可以使用字节、半词、词访问来存取整个闪存内容。擦除和编程由简单的一组命令来处理。

很多**SPI**闪存器件使用串行命令来安装/初始化器件，然后转到双命令或四命令实现正常运行。不同的串行闪存供应商和器件接受或要求不同的命令和命令格式。**SPIFI**拥有足够的灵活性，可以兼容众多市场领先的器件，而且能扩展，以确保兼容未来的器件。

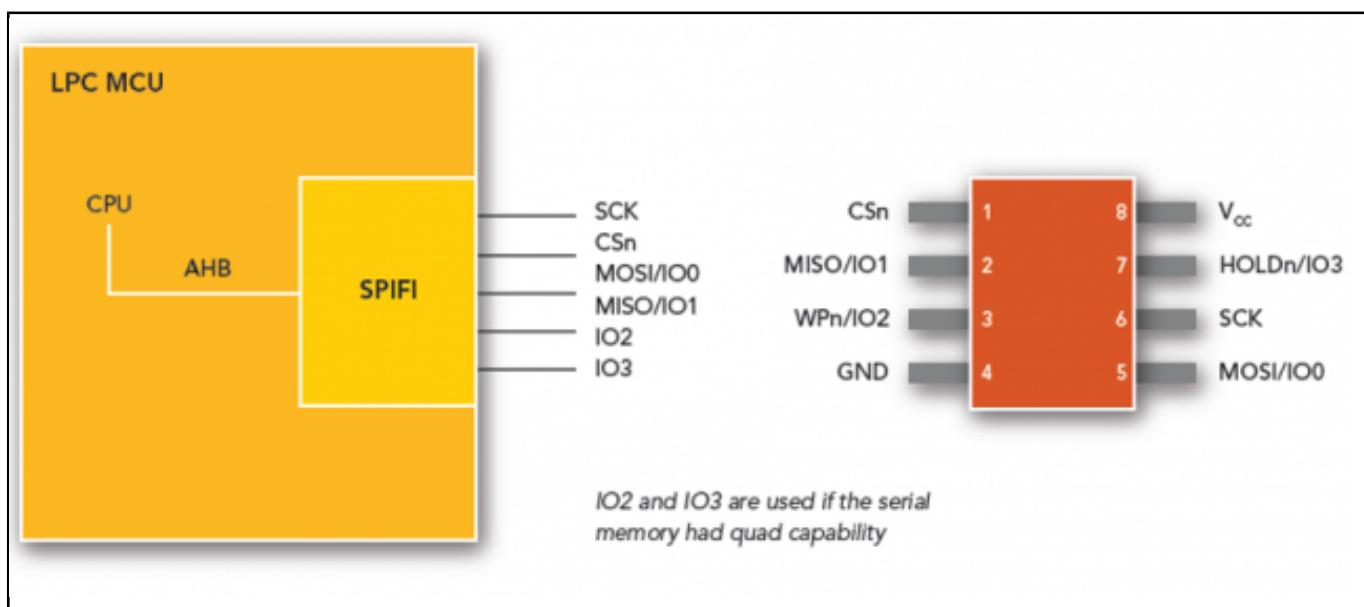

**SPIFI**在半双工模式中实现了基本**SPI**、双**SPI**和四**SPI**，在该模式中，**SPIFI**总是在每一帧开始时将一个命令发送到一个串行闪存存储器。在写命令时，**SPIFI**在帧中发送所有数据，而在读命令时，**SPIFI**发送命令，然后串行闪存将数据发送到**SPIFI**。当软件读取存储器映射的串行闪存区域时，**SPI**闪存器件响应软件发送的或**SPI**自动发送的命令。命令分为操作码、地址、中间数据和数据等字段。地址、中间数据和数据字段是可选的，具体取决于操作码。一些器件包括操作码可以隐含在读命令的模式，以实现更高性能。数据字段可进一步分为输入和输出数据字段，具体取决于操作码。

### LPC-SPIFI-PERIPHERAL-BD1 Block Diagram

### LPC-SPIFI-PERIPHERAL-BD2 Block Diagram

### LPC-SPIFI-PERIPHERAL-BD3 Block Diagram

View additional information for [LPC SPIFI外设](#).

**Note:** The information on this document is subject to change without notice.

---

[www.nxp.com](http://www.nxp.com)

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.