# 带有复位和中断的8位I<sup>2</sup>C总线和SMBus、电平变换、低压GPIO

## PCA9574

Last Updated: Dec 16, 2024

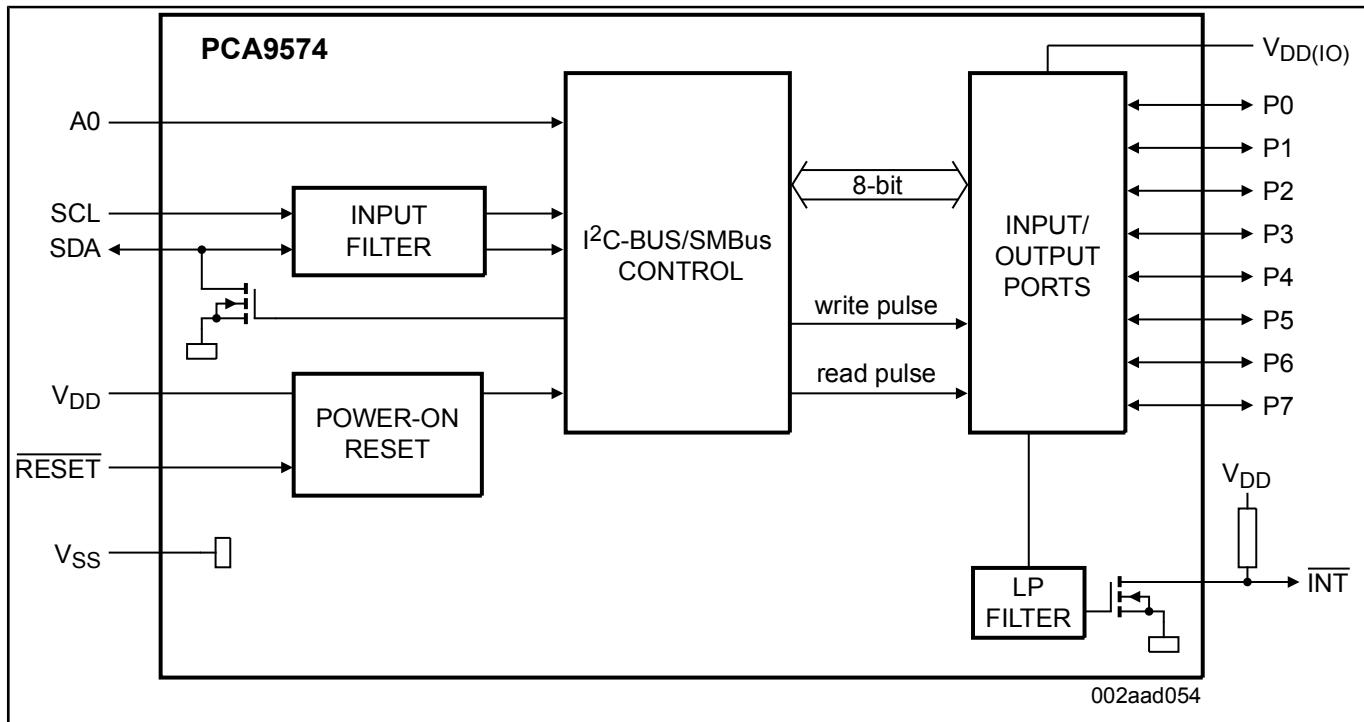

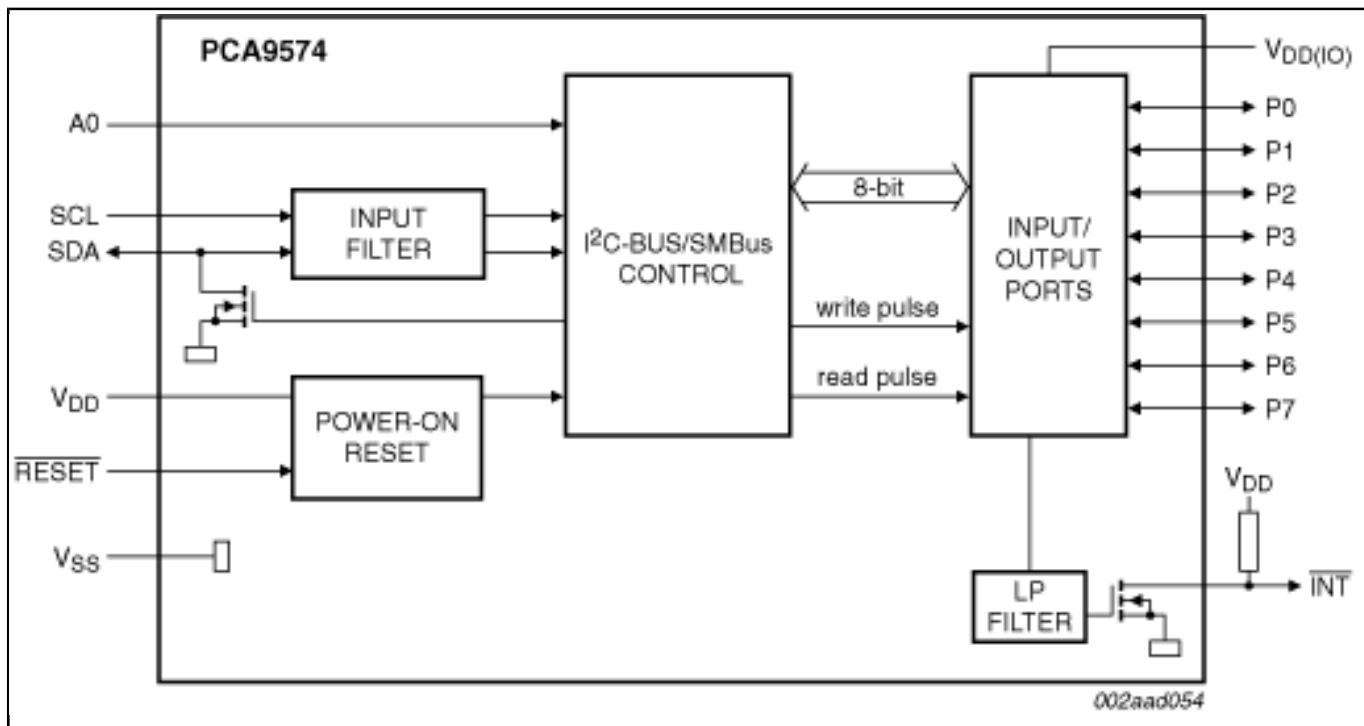

**PCA9574**是一款CMOS器件，为低压处理器和手持电池供电移动应用提供8位通用并行输入/输出(GPIO)扩展，是为增强恩智浦的I<sup>2</sup>C总线I/O扩展器系列而开发的。改进内容包括更低的供电电流、1.1V至3.6V的更低工作电压、允许在任何1.1V和3.6V之间进行电压电平变换的双和独立电源轨、400kHz时钟频率和更小的封装。任何八个I/O端口均可配置为相互独立的输入或输出且默认启动为输入。在保持互连最小化的同时需要额外的I/O时，I/O扩展器提供简易的解决方案；例如，在用于连接传感器、按钮、键区等的电池供电移动应用和翻盖设备中。除提供灵活的GPIO设置外，还简化了运行在一个电压级别上的处理器与工作在不同（通常更高）电压级别的I/O器件之间的连接。PCA9574具备内置电平切换功能，使这些器件在需要在不兼容I/O之间进行通信的混合信号环境中极其灵活。PCA9574的核心可工作于低至1.1V的电压上而I/O可工作于1.1V至3.6V的范围内。还为I/O提供带有可编程片上上拉或下拉功能的总线保持。

系统控制器可通过写入I/O配置寄存器位将I/O用作输入或输出。每个输入或输出的数据保留在对应的输入或输出寄存器中。通过极性反转寄存器（高电平有效或低电平有效操作）可反转读取寄存器的极性。通过对相应的寄存器进行编程可选择总线保持功能或上拉/下拉功能。总线保持功能在未主动驱动I/O总线时提供有效的逻辑电平。当未选择总线保持功能时，通过对上拉/下拉配置寄存器进行编程可将I/O端口配置为上拉或下拉。

开漏中断输出引脚(INT)允许监视输入引脚并在每次一个输入端口发生变化时指定，除非该端口已屏蔽（默认 = 屏蔽）。“GPIO All Call”命令允许同时对多个PCA9574进行编程，即使它们有不同的独立I<sup>2</sup>C总线地址。当需要以相同的指令对多个器件进行编程时或如果需要同时打开或关闭输出，这能进行最佳的代码编程。内部上电复位(POR)或硬件复位引脚(RESET)会将八个I/O初始化为输入、将寄存器设为其默认值并初始化器件状态机。当逻辑电源(VDD)关闭时，I/O组保持在其默认状态中。

一个地址选择引脚允许在同一I<sup>2</sup>C总线上以两个不同的地址连接最多两个PCA9574器件。

PCA9574提供TSSOP16和HVQFN16封装，并规定-40° C至+85°C的工业温度范围。

## PCA9574 Block Diagram

## PCA9574BS, PCA9574PW Block Diagram

View additional information for [带有复位和中断的8位I<sup>2</sup>C总线和SMBus、电平变换、低压GPIO](#).

**Note:** The information on this document is subject to change without notice.

---

**www.nxp.com**

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.