# 高性能双核处理器

## MPC8641D

Last Updated: Dec 18, 2024

MPC8641设备“不建议用于新设计”，请使用替换系列Power Architecture (T208x)和Arm Architecture (LS2044)。

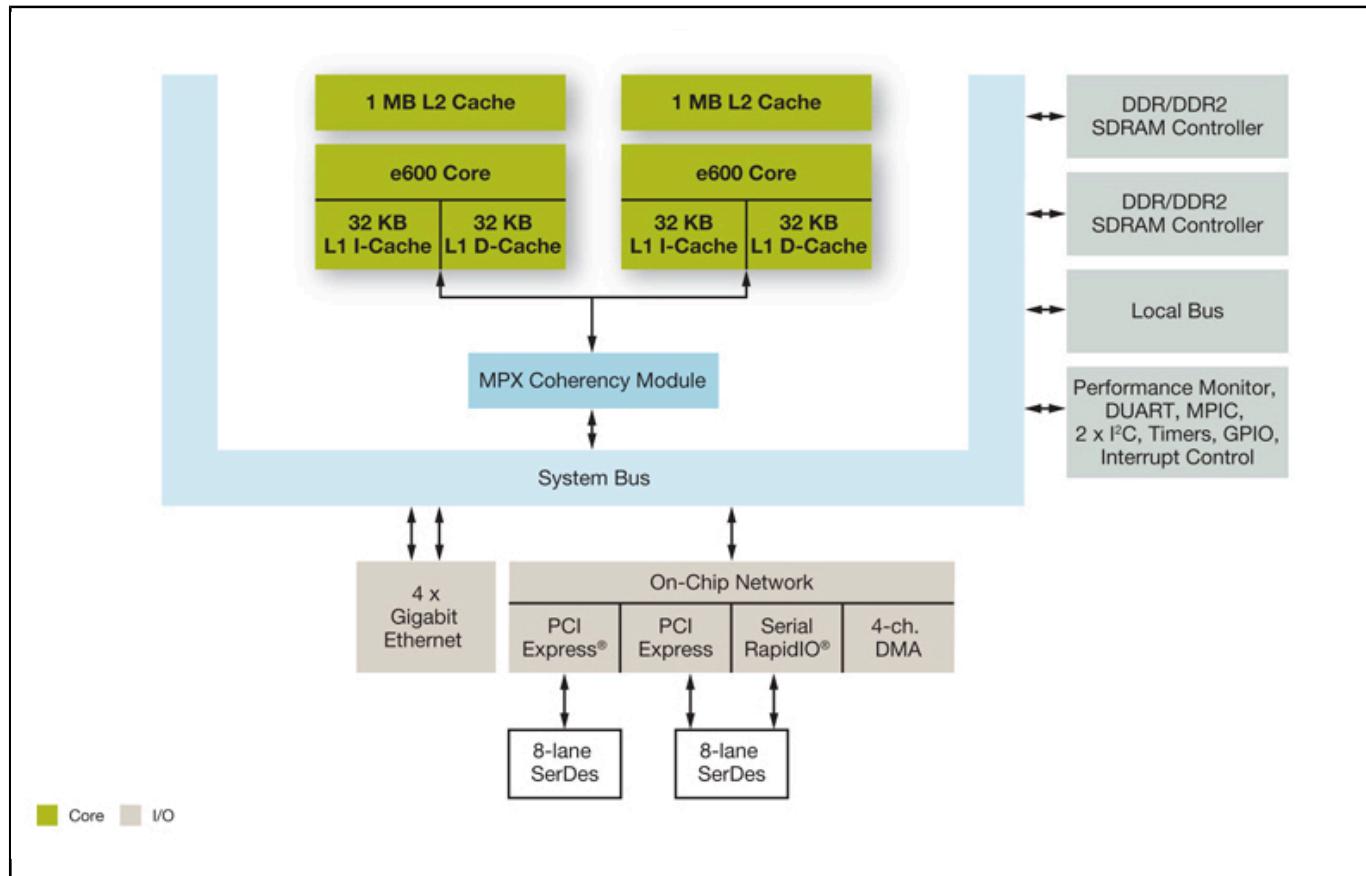

MPC8641D使用两个高性能超标量e600内核，运行频率最高可达1.5 GHz。这个三发机采用紧凑的7阶管道，对有不可预知的支线的代码特别有效。它避免了与清理错误预测支线上的长管道相关的较大延迟。不可预知的支线是由大量随机到达的不同类型的数据包驱动的典型代码路径。这些处理器支持系统总线上最多8个无序指令，允许向前进，即使在等待先前指令完成时也可往前处理(即，接入所需的主存储器)。e600采用板载128位向量处理器进行高效的数据移动(用于将TCP有效载荷从内核空间复制到用户空间)和数学函数的运算，这些数学函数相当于一个DSP。

每个内核都有一个较大的背面L2缓存，这使e600获得了高带宽，处理器和L2缓存之间延迟很低。因为每个内核都有它自己的L2缓存，当两个内核运行独立的操作系统而数据共享有限时，这个设备特别有效。对于在两个内核之间共享数据的应用，还提供数据共享低延迟功能。

该设备采用双64位(带ECC则为72位) DDR2存储控制器，可满足两个内核的带宽要求。存储控制器可以分配给每个内核，以增强操作系统的隔离，或者可以在内核之间共用，可确保最有效的存储器带宽。可以在两个存储控制器之间交叉进行存取，增加了目标存储器区域中打开的页面数量，降低了存储器存取的平均延迟。还可选启用实施单错误纠正和双错误检测的纠错码，确保存储控制器上的误码得到纠正，或者至少报告给内核。这是任何高可用性应用的一个要求。

有两个灵活的高性能I/O端口。双8通道PCI Express端口充分利用具有高性能串行点到点链路的遗留PCI，该链路通常用来连接各种其他板载高性能设备。4通道串行RapidIO端口，具有低软件开销、配置简单、硬件纠错等特点，支持存储器映射和基于数据包的事务处理，非常适合作为背板接口。

有4个以太网控制器，可支持10 Mbps、100 Mbps和1000 Mbps。以太网控制器具有先进的功能：TCP和UDP校验和加速、QoS支持以及分组报头处理。每个以太网控制器可以转换为一种FIFO模式，实现高效ASIC连接。

**MPC8641D**支持灵活的软件实施：对称多核处理(**SMP**)和非对称多核处理。采用SMP，一个操作系统可运行两个内核，但从编程角度看是开发人员在为一个单核编写程序。采用非对称多核处理，同一操作系统的或两个完全独立的操作系统这两个实例都可以在两个内核上运行，基本上不会感知到彼此。

## MPC8641D Block Diagram Block Diagram

View additional information for [高性能双核处理器](#).

**Note:** The information on this document is subject to change without notice.

---

[www.nxp.com](http://www.nxp.com)

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.